UNIVERSITÉ DU QUÉBEC

MÉMOIRE PRÉSENTÉ À

L'UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

COMME EXIGENCE PARTIELLE

DE LA MAÎTRISE EN GÉNIE ÉLECTRIQUE

PAR

CHOKRI NEILI

CONCEPTION ET IMPLÉMENTATION SUR FPGA DE STRUCTURES

MULTIPLEXES DE LA FFT EN PIPELINE

SEPTEMBRE 2017

Université du Québec à Trois-Rivières

Service de la bibliothèque

Avertissement

L'auteur de ce mémoire ou de cette thèse a autorisé l'Université du Québec à Trois-Rivières à diffuser, à des fins non lucratives, une copie de son mémoire ou de sa thèse.

Cette diffusion n'entraîne pas une renonciation de la part de l'auteur à ses droits de propriété intellectuelle, incluant le droit d'auteur, sur ce mémoire ou cette thèse. Notamment, la reproduction ou la publication de la totalité ou d'une partie importante de ce mémoire ou de cette thèse requiert son autorisation.

## Résumé

La transformée discrète de Fourier (DFT - *Discrete Fourier Transform*) représente une méthode de base en traitement numérique des signaux pour l'analyse des signaux numériques. Son exécution en technologie d'intégration à très grande échelle représente un problème non trivial quand il s'agit de respecter les contraintes de l'application en termes de consommation de puissance, coût d'implémentation et vitesse de calcul.

Ce travail présente l'évaluation d'une nouvelle formulation de la FFT, en vue d'une implémentation plus efficace que les propositions conventionnelles. Cette nouvelle formulation comprend de nouvelles conceptions pour des processeurs élémentaires (BPE - *Butterfly Processing Element*) selon les radix-r utilisés.

L'originalité du projet provient du multiplexage des multiplicateurs complexes des coefficients de Fourier (TWF – *Twiddle Factor*) dans la conception des BPE radix-*r*. Les résultats présentés dans ce mémoire concernent le radix-4 et radix-8 de l'implémentation de la nouvelle conception de BPE radix-*r* sur FPGA. L'évaluation des performances des implémentations se base sur plusieurs critères, à savoir, débit de la BPE, latence, fréquence d'horloge et un critère performances globale.

Ces résultats se comparent favorablement aux plus récents articles de références sur le sujet utilisant la structure pipeline et parallèle de la FFT. Les résultats présentent un gain de 130% en fréquence par rapport à la référence pour  $N=256$ , ce qui permet d'améliorer la performance MS/s/Slice de 116%. Le gain en fréquence ou en performance devient plus

grand quand on utilise la technologie de Virtex-7, en effet, pour  $N=256$ , on enregistre un gain de 173% en termes de fréquence et de 209% en termes de performance.

Finalement, ce projet permet de valider l'efficacité de la nouvelle formulation de la FFT, en termes de performances de puissances de calcul et de rapidité pour une l'utilisation dans des applications différentes.

## ***Remerciements***

*Je tiens à adresser mes sincères remerciements à Monsieur Daniel Massicotte, professeur régulier au département génie électrique et directeur du Laboratoire des Signaux et Systèmes Intégrés(LSSI), qui, en tant que Directeur de recherche, s'est toujours montré à l'écoute et très disponible tout au long de la réalisation de ce mémoire. Ses conseils pertinents avec écoute, amabilité et patience ont permis à mon travail d'aboutir et de voir le jour.*

*À ma très chère mère affable, honorable, aimable : Tu représentes pour moi le symbole de la bonté par excellence, la source de tendresse et l'exemple du dévouement qui n'a pas cessé de m'encourager et de prier pour moi.*

*À mon cher père : Aucune dédicace ne saurait exprimer l'amour, l'estime, le dévouement et le respect que j'ai toujours eu pour vous. Rien au monde ne vaut les efforts fournis jour et nuit pour mon éducation et mon bien-être.*

*À mes deux petits frères : Les mots ne suffisent guère pour exprimer l'attachement, l'amour et l'affection que je porte pour vous.*

*À ma sœur : Ton amour m'a aidé à grandir et devenir quelqu'un de bien, car tu es mon exemple. Ton amour m'a aidé à surmonter bien d'épreuves difficiles, car tu es mon exemple. Ton amour m'a aidé à avancer en toutes circonstances, car tu es mon exemple.*

*À mon épouse : Avec toi, j'ai appris à sourire, à partager, j'ai appris à donner et à recevoir, j'ai appris que la vie vaut la peine d'être vécue, si l'amour est présent. Tes sacrifices, ton soutien moral et matériel, ta gentillesse sans égal, ton profond attachement m'ont permis de réussir mes études. Que Dieu réunisse nos chemins pour un long commun serein.*

*À tous mes collègues et amis. À tous ceux qui avec de chaleur et d'amour se sont dévoués pour ma réussite et mon bonheur, je dédie ce travail.*

# *Table des matières*

|                                                              |           |

|--------------------------------------------------------------|-----------|

| <i>RÉSUMÉ</i> .....                                          |           |

| <i>REMERCIEMENT</i> .....                                    |           |

| <i>TABLE DES MATIÈRES</i> .....                              |           |

| <i>LISTE DES FIGURES</i> .....                               |           |

| <i>LISTE DES TABLEAUX</i> .....                              |           |

| <i>LISTE DES ABRÉVIATIONS</i> .....                          |           |

| <br>                                                         |           |

| <b>1. CHAPITRE I</b> .....                                   | <b>1</b>  |

| 1.1    Problématique .....                                   | 3         |

| 1.2    Objectif .....                                        | 6         |

| 1.3    Méthodologie .....                                    | 6         |

| 1.4    Organisation du mémoire.....                          | 9         |

| <br>                                                         |           |

| <b>2. CHAPITRE II</b> .....                                  | <b>11</b> |

| 2.1    Transformée de Fourier Discrète .....                 | 12        |

| 2.2    La Transformée Rapide de Fourier.....                 | 14        |

| 2.2.1    Algorithmes conventionnels .....                    | 15        |

| 2.2.2    Approche diviser-pour-régner .....                  | 16        |

| 2.2.3    Radix-2 .....                                       | 19        |

| 2.2.4    Radix-4 .....                                       | 22        |

| 2.3    Architecture parallèle pour le calcul de la FFT ..... | 23        |

| 2.4    Architectures pipelines pour le calcul de la FFT..... | 25        |

| 2.4.1    Single-path Delay Feedback SDF .....                | 26        |

| 2.4.2    Single-path Delay Commutator SDC .....              | 28        |

| 2.4.3    Multi-path Delay Commutator MDC .....               | 29        |

| 2.5    Effet de Quantification .....                         | 33        |

| 2.5.1    Erreur de quantification .....                      | 34        |

|       |                                                                                                       |    |

|-------|-------------------------------------------------------------------------------------------------------|----|

| 2.6   | Différentes approches d'implémentation de la FFT .....                                                | 34 |

| 2.6.1 | <i>Processeur FFT pipeliné localement</i> .....                                                       | 34 |

| 2.6.2 | <i>Processeur FFT pour les applications WPAN à base de OFDM</i> .....                                 | 37 |

| 2.6.3 | <i>Radix-<math>2^4</math> FFT à haute performance pour les applications MIMO-OFDM</i> .....           | 40 |

| 2.6.4 | <i>Processeur FFT pour les systèmes UWB</i> .....                                                     | 41 |

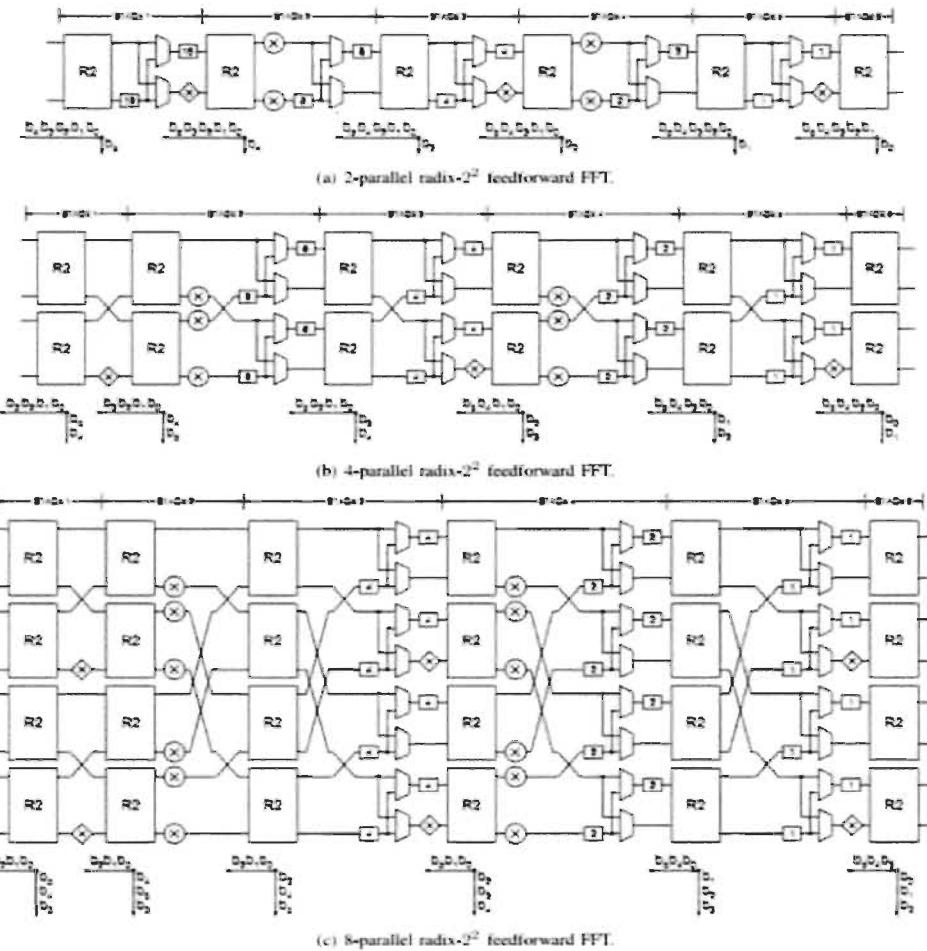

| 2.6.5 | <i>Radix-<math>2^k</math> feedforward FFT pipelinées</i> .....                                        | 43 |

| 3.    | <i>CHAPITRE III</i> .....                                                                             | 47 |

| 3.1   | Éléments nécessaires pour implémenter la FFT .....                                                    | 48 |

| 3.1.1 | <i>Étapes de conception</i> .....                                                                     | 48 |

| 3.1.2 | <i>Structure pipeline de la FFT</i> .....                                                             | 50 |

| 3.1.3 | <i>Conception et architecture pipeline radix-<math>2^2</math> et radix-<math>2^3</math> FFT</i> ..... | 52 |

| 3.2   | Synthèse des résultats d'implémentation .....                                                         | 69 |

| 3.2.1 | <i>Critères d'évaluation</i> .....                                                                    | 69 |

| 3.2.2 | <i>Résultats d'implémentation</i> .....                                                               | 72 |

| 3.2.3 | <i>Synthèse et analyse des Résultats</i> .....                                                        | 78 |

| 4.    | <i>CHAPITRE IV</i> .....                                                                              | 84 |

| 5.    | <i>Références</i> .....                                                                               | 87 |

# Liste des figures

|                                                                                               |    |

|-----------------------------------------------------------------------------------------------|----|

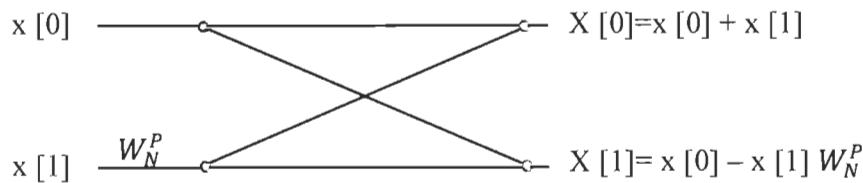

| <i>Figure 1 Structure DIT Butterfly .....</i>                                                 | 19 |

| <i>Figure 2 Structure DIF Butterfly .....</i>                                                 | 20 |

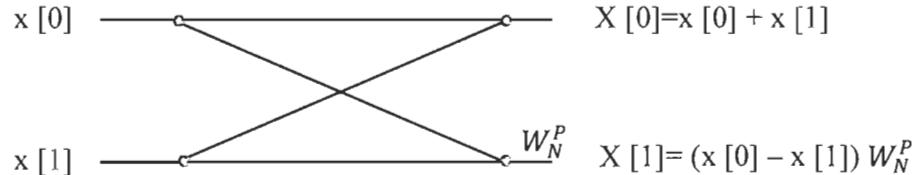

| <i>Figure 3 Diagramme de la FFT à base de BPE radix-2 de type DIT .....</i>                   | 20 |

| <i>Figure 4 Diagramme de la FFT à base de BPE radix-2 de type DIF .....</i>                   | 21 |

| <i>Figure 5 BPE du radix-4 DIT .....</i>                                                      | 22 |

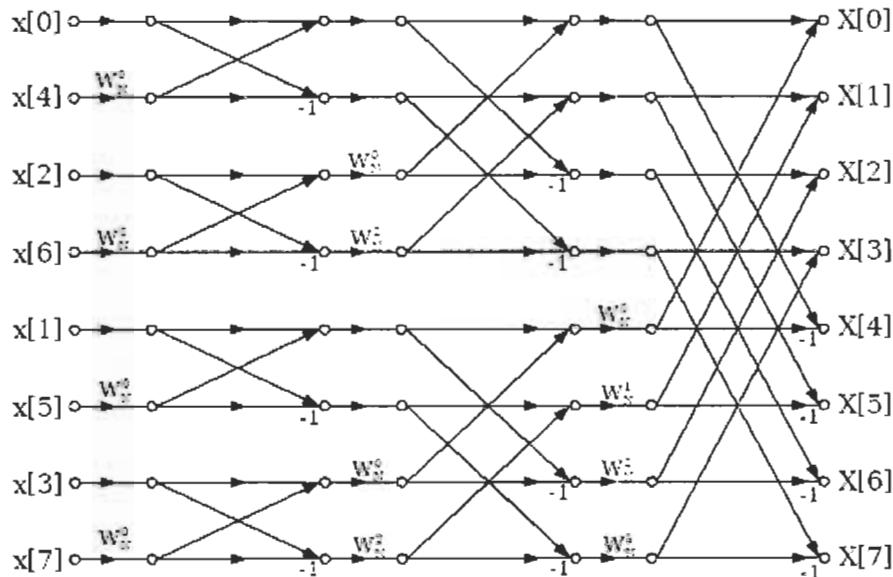

| <i>Figure 6 Architecture parallèle du radix-2 (<math>N=8</math>) .....</i>                    | 23 |

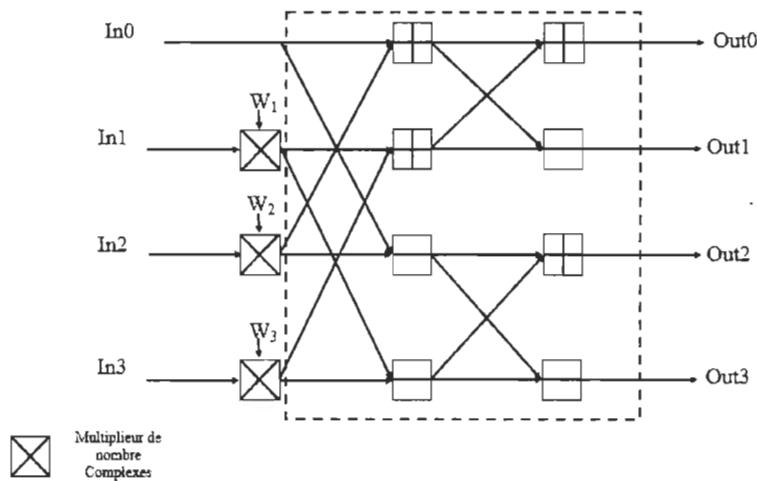

| <i>Figure 7 Architecture parallèle du radix-4 (<math>N=16</math>) .....</i>                   | 24 |

| <i>Figure 8 Architecture parallèle du SRFFT-4/2 (<math>N=32</math>) .....</i>                 | 24 |

| <i>Figure 9 Architecture pipeline de base [YJ03] .....</i>                                    | 25 |

| <i>Figure 10 Architecture R2SDF (<math>N = 16</math> points) .....</i>                        | 27 |

| <i>Figure 11 Architecture R4SDF (<math>N = 16</math> points) .....</i>                        | 27 |

| <i>Figure 12 Architecture R4SDC (<math>N = 256</math> points) .....</i>                       | 29 |

| <i>Figure 13 Architecture R4MDC (<math>N = 64</math> points) .....</i>                        | 30 |

| <i>Figure 14 Architecture MC-MRMDC (<math>k = 4</math>, <math>N = 64</math> points) .....</i> | 31 |

| <i>Figure 15 Quelques méthodes de représentations en virgule fixe .....</i>                   | 33 |

| <i>Figure 16 Architecture radix-16 LPPL [GA89] .....</i>                                      | 36 |

| <i>Figure 17 Architecture R2SD2F pipeliné pour DFT à 16 points [GA89] .....</i>               | 36 |

| <i>Figure 18 Diagramme Block d'un 2048-FFT processeur [SN10] .....</i>                        | 37 |

| <i>Figure 19 Structure du module 1[SN10] .....</i>                                            | 38 |

| <i>Figure 20 Diagramme Block du module 4[SN10] .....</i>                                      | 39 |

|                                                                                                                                             |    |

|---------------------------------------------------------------------------------------------------------------------------------------------|----|

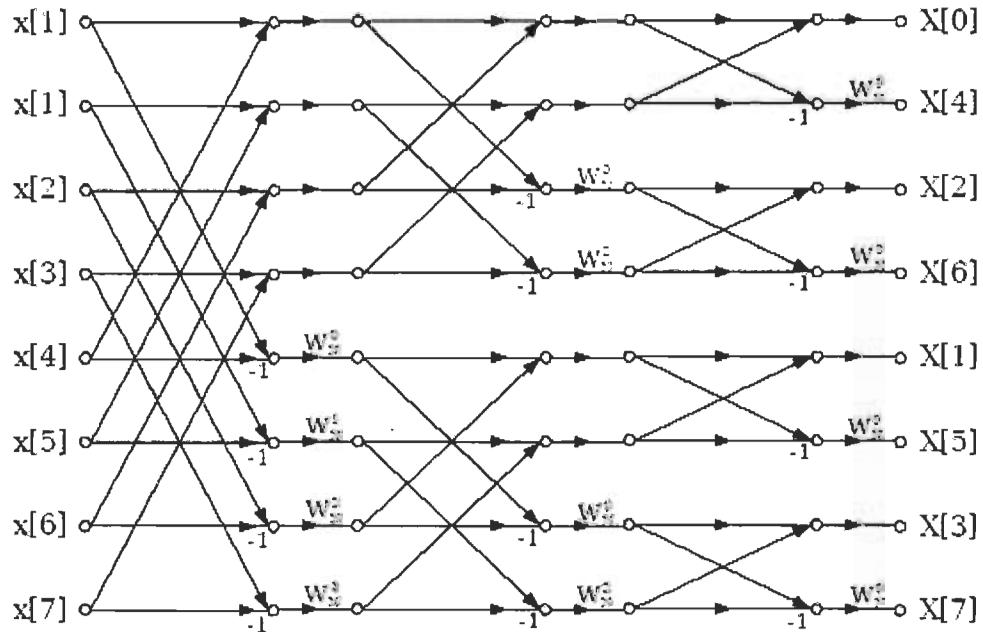

| <i>Figure 21 4-parallel data-path d'un processeur radix-<math>2^4</math> MDF FFT/IFFT à 128/64-points [HL08]</i> .....                      | 41 |

| <i>Figure 22 Processeur SDF FFT radix-<math>2^4</math> parallèle proposé [SI08]</i> .....                                                   | 42 |

| <i>Figure 23 Structures des unités BPE (Types 1, 2, et 3) [SI08]</i> .....                                                                  | 43 |

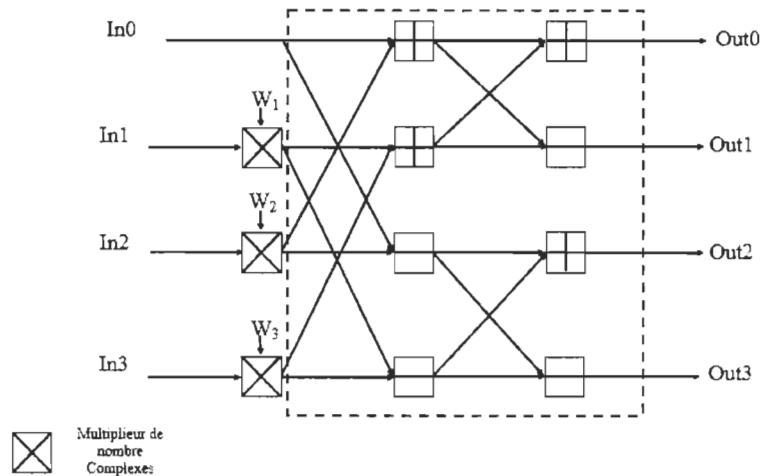

| <i>Figure 24 Architecture radix-<math>2^2</math> feedforward à 4 entrées parallèles pour le calcul de DIF FFT de 16-points [MG13]</i> ..... | 44 |

| <i>Figure 25 Architecture radix-<math>2^2</math> feedforward proposée pour le calcul de la DIF FFT de 64-points [MG13]</i> .....            | 45 |

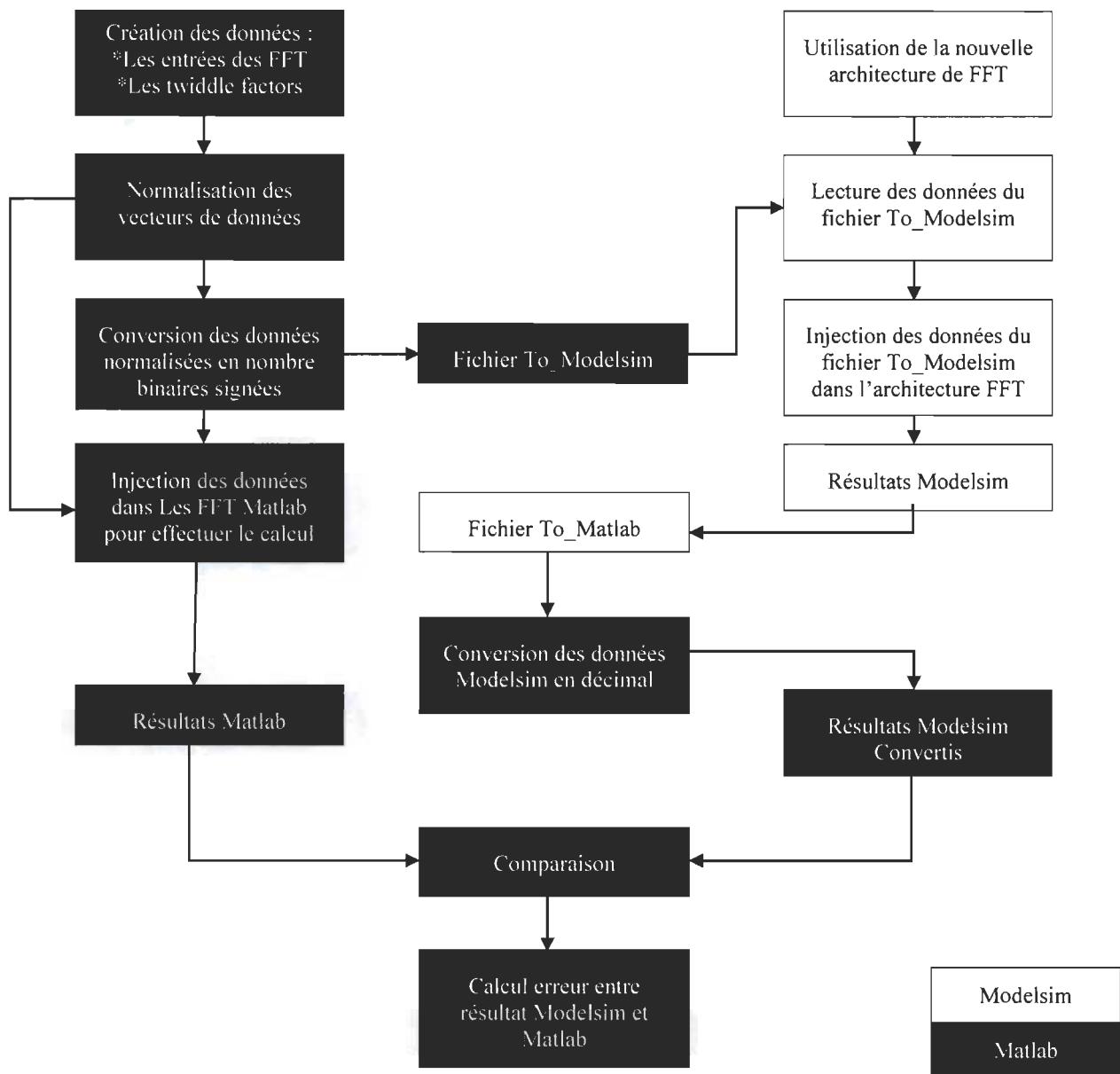

| <i>Figure 26 Diagramme de la méthode de co-simulation Matlab-Modelsim</i> .....                                                             | 51 |

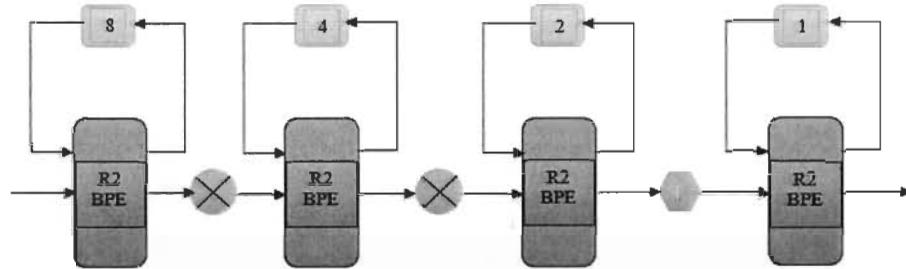

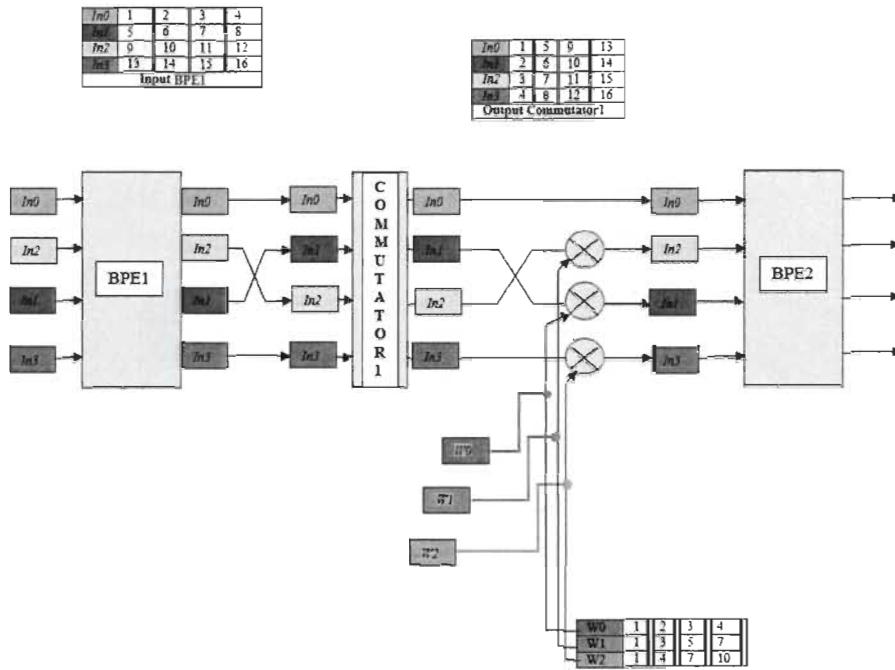

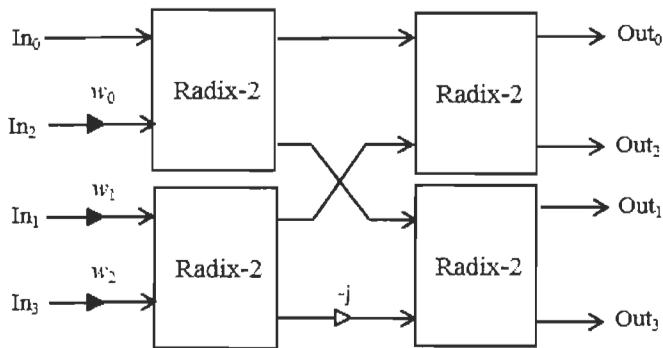

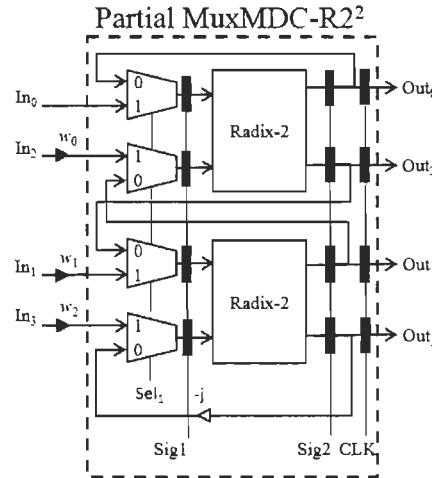

| <i>Figure 27 Architecture pipeline radix-<math>2^2</math> MDC de type DIF à deux étages N=16 [MJ14]</i> .....                               | 53 |

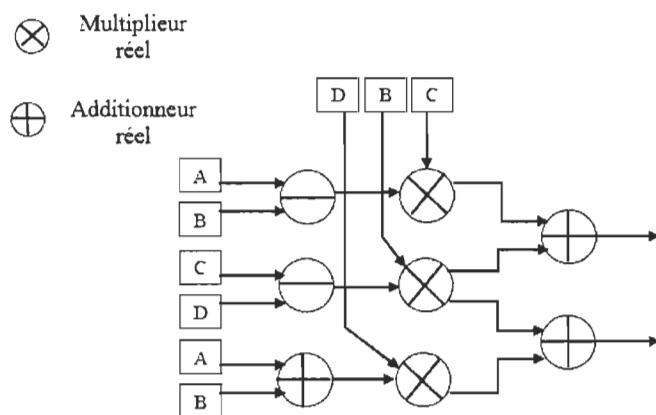

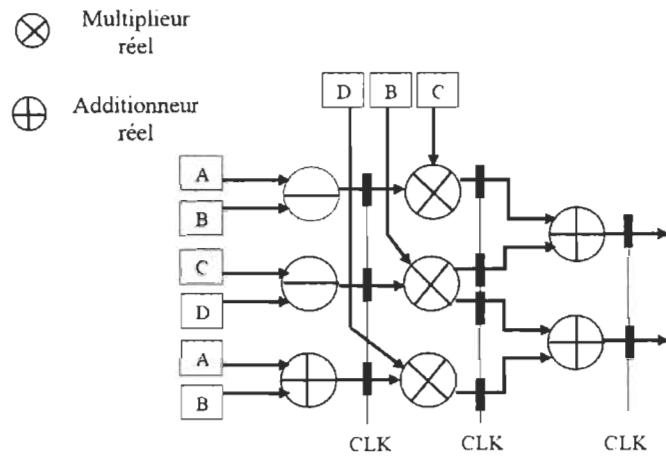

| <i>Figure 28 (MDC-R22) BPE Conventionnelle de radix-<math>2^2</math></i> .....                                                              | 54 |

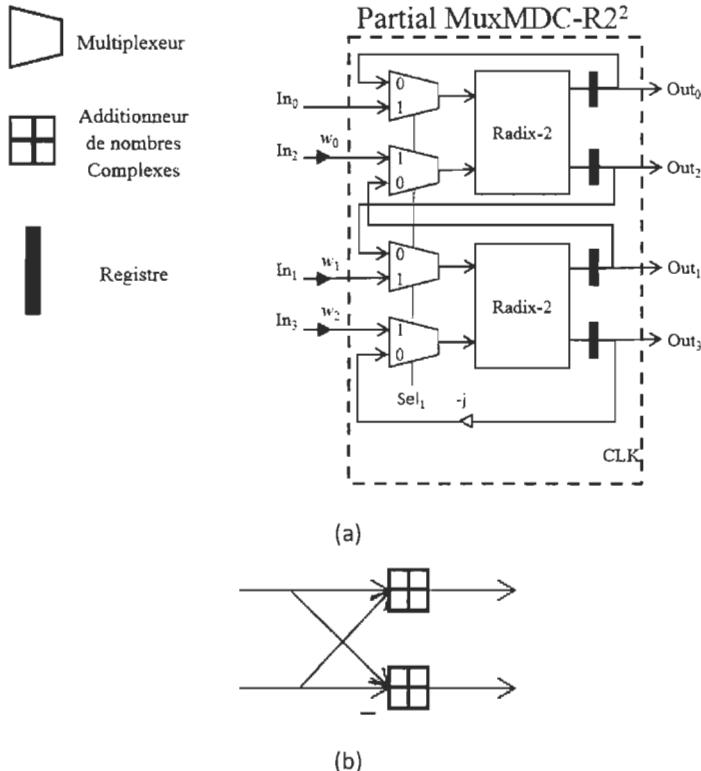

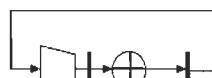

| <i>Figure 29 (a) BPE_MUX proposée (b) diagramme de blocs de circuit du réseau d'additionneur complexe radix-2 [MJ14]</i> .....              | 55 |

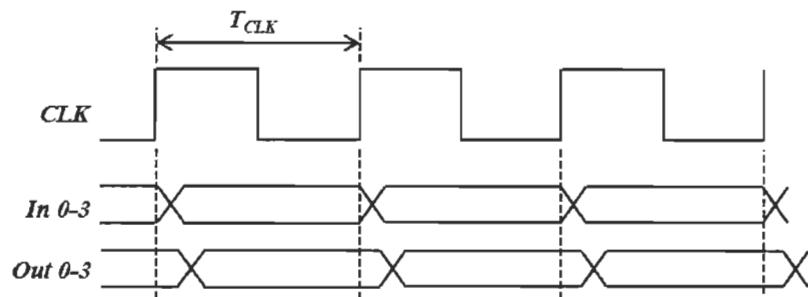

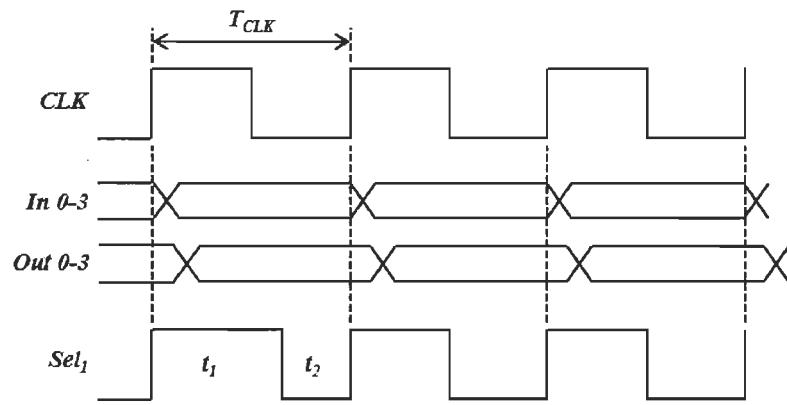

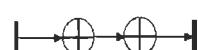

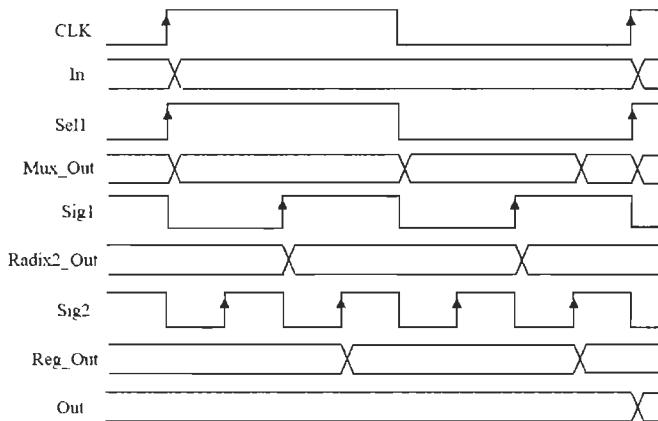

| <i>Figure 30 Timing block diagramme de la figure 31[MJ14]</i> .....                                                                         | 55 |

| <i>Figure 31 Timing block diagramme de la figure 32[MJ14]</i> .....                                                                         | 56 |

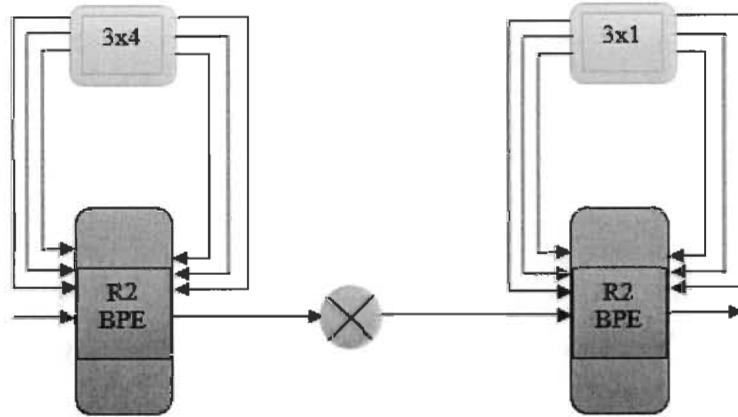

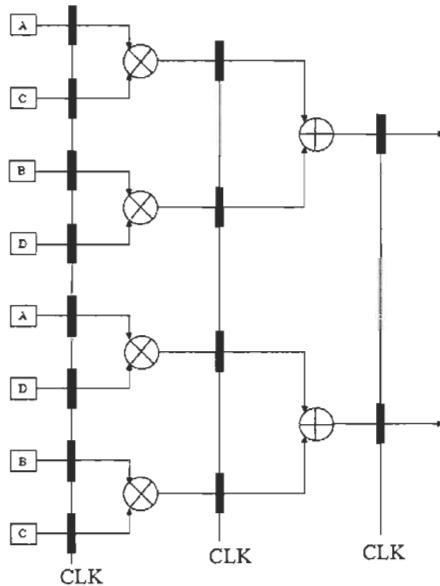

| <i>Figure 32 BPE Conventionnelle de radix-23 [MJ14]</i> .....                                                                               | 56 |

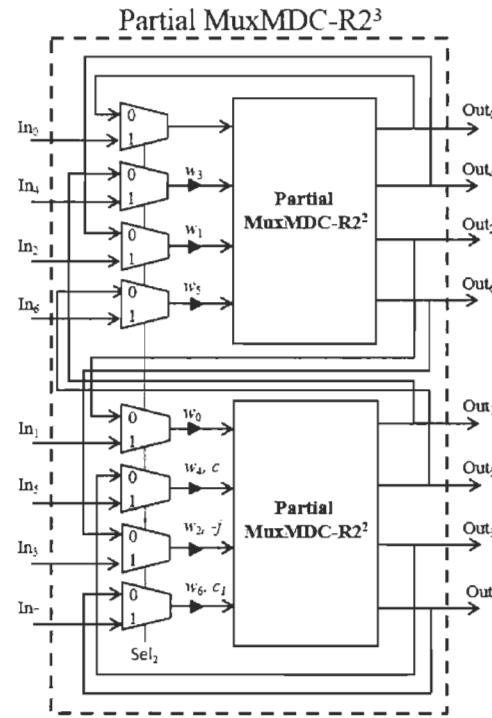

| <i>Figure 33 BPE Multiplexée (BPE_MUX) proposée de radix-23 [MJ14]</i> .....                                                                | 57 |

| <i>Figure 34 Architecture d'une BPE de radix-4 [HS12]</i> .....                                                                             | 57 |

| <i>Figure 35 Chemin Critique d'une BPE_MUX de radix-<math>2^3</math> implémentée.....</i>                                                   | 58 |

| <i>Figure 36 Représentation des signaux de contrôle dans la structure Partial MuxMDC-R2<math>^2</math></i> .....                            | 60 |

|                                                                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <i>Figure 37 Comparaison entre les Chemins critiques des BPE implémentés a) BPE_MUX<br/>(figure 29a) et b) BPE conventionnelle (figure 28).....</i> | 60 |

| <i>Figure 38 Data flow diagramme de la structure Partial MuxMDC-R2<sup>2</sup> implémentée .....</i>                                                | 61 |

| <i>Figure 39 Représentation de la latence du Partial MuxMDC-R2<sup>2</sup> implémentée .....</i>                                                    | 62 |

| <i>Figure 40 Structure interne de multiplieur de nombres complexes non pipeliné optimisé .</i>                                                      | 63 |

| <i>Figure 41 Structure interne de multiplieur de nombres complexes pipeliné optimisé .....</i>                                                      | 64 |

| <i>Figure 42 Structure implémentée du Multiplieur de nombres complexes utilisant 4<br/>multiplieurs réels.....</i>                                  | 65 |

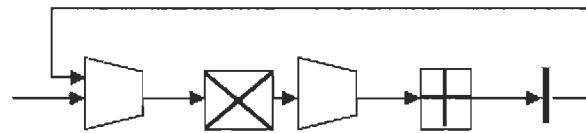

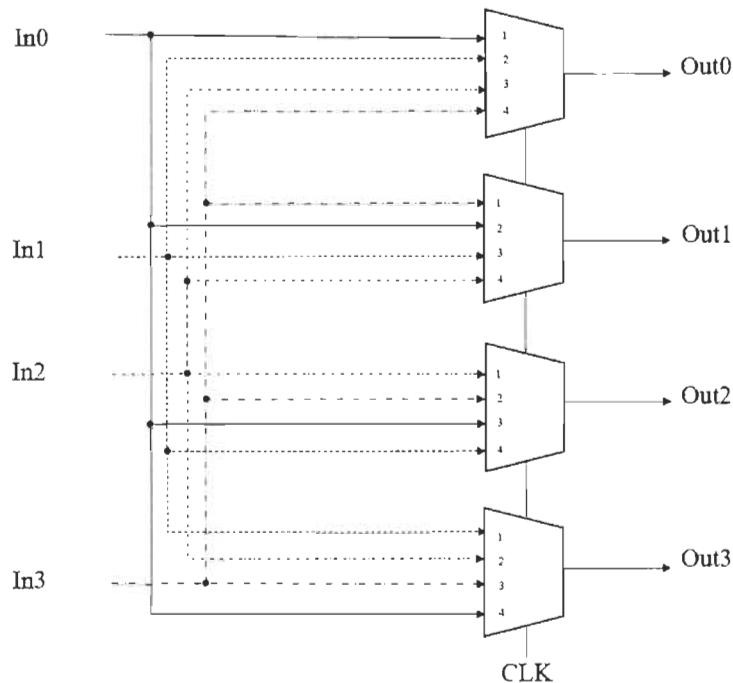

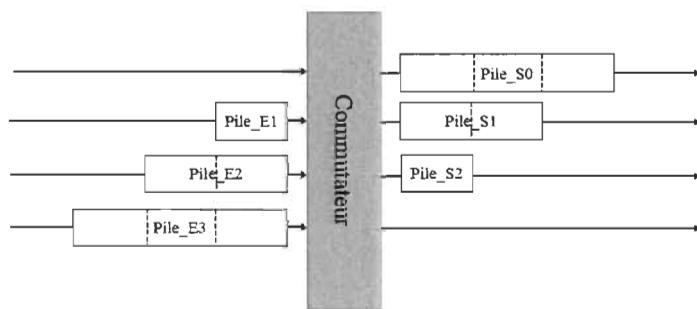

| <i>Figure 43 Structure interne de commutateur .....</i>                                                                                             | 66 |

| <i>Figure 44 Représentation des délais liés au module du Commutateur pour une FFT de 16<br/>points .....</i>                                        | 66 |

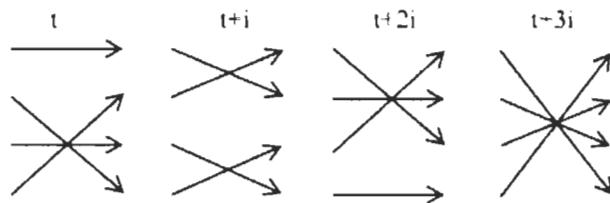

| <i>Figure 45 Les transformations de commutateur .....</i>                                                                                           | 67 |

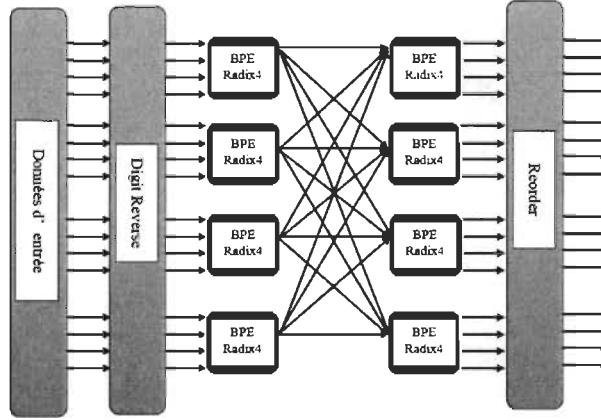

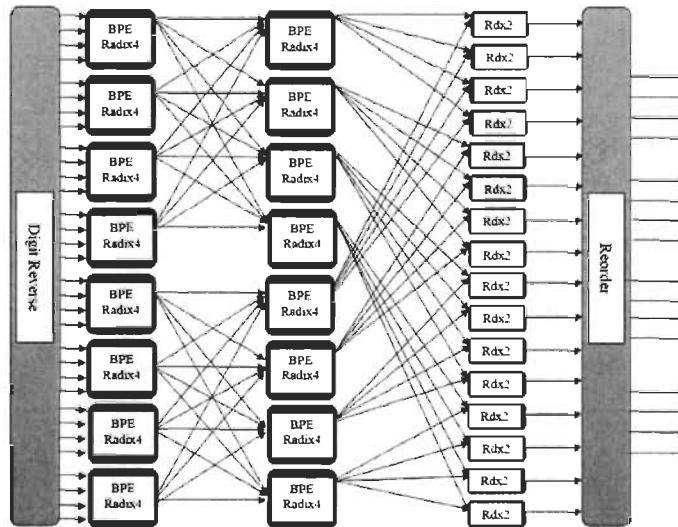

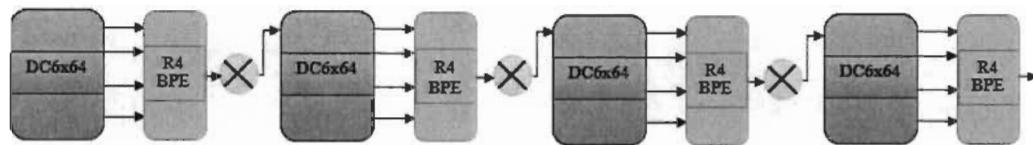

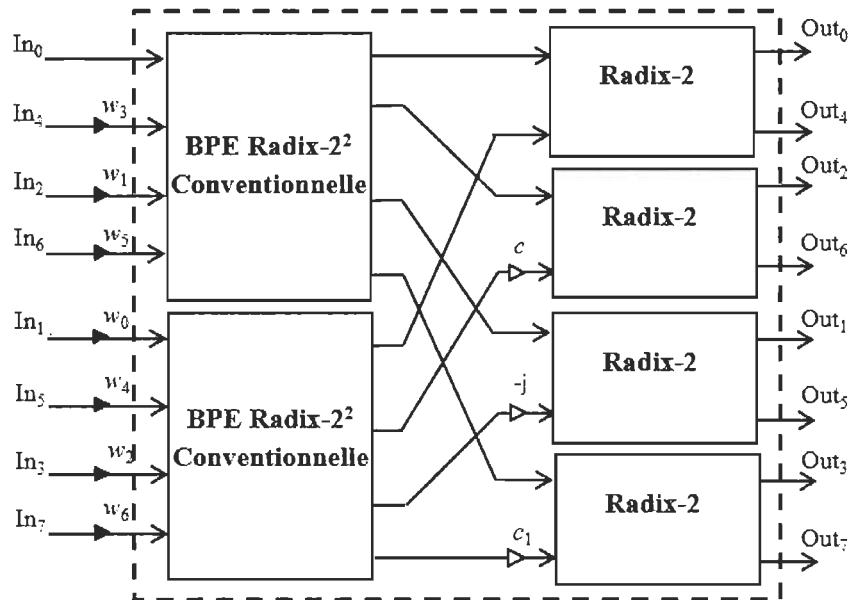

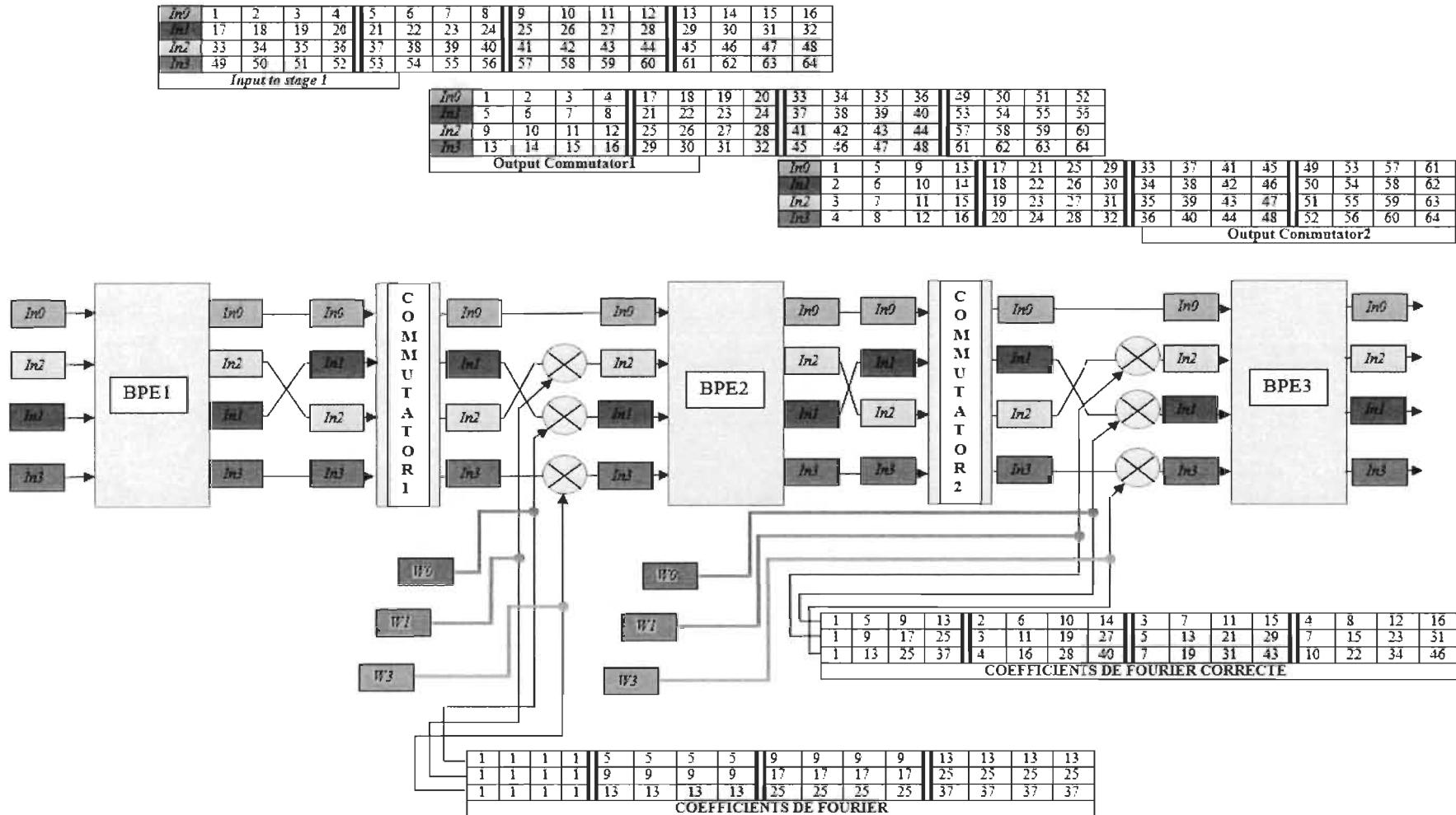

| <i>Figure 46 Architecture pipeline radix-4 MDC de type DIF sur 3 étages N=64 points ....</i>                                                        | 68 |

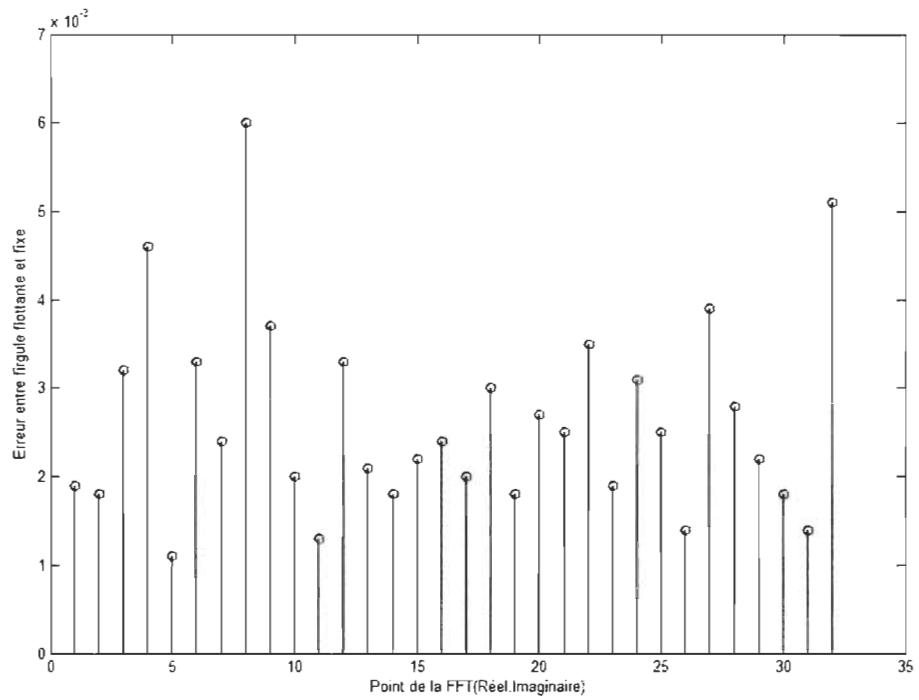

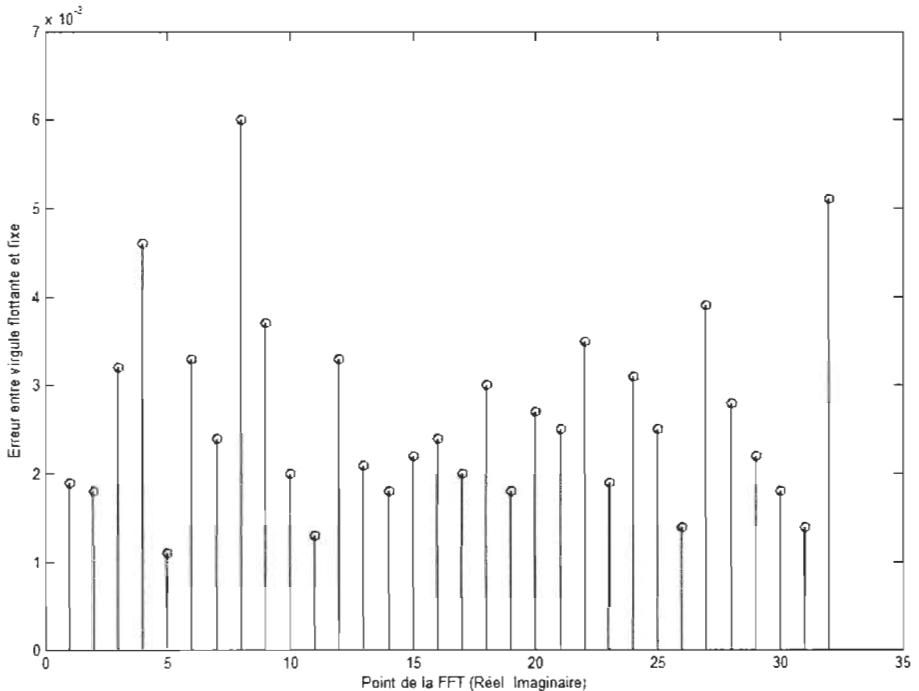

| <i>Figure 47 Erreur entre virgule fixe et flottante d'une FFT de taille 16 utilisant BPE_MUX<br/>.....</i>                                          | 70 |

| <i>Figure 48 Erreur entre virgule fixe et flottante d'une FFT de taille 16 utilisant BPE<br/>conventionnelle.....</i>                               | 70 |

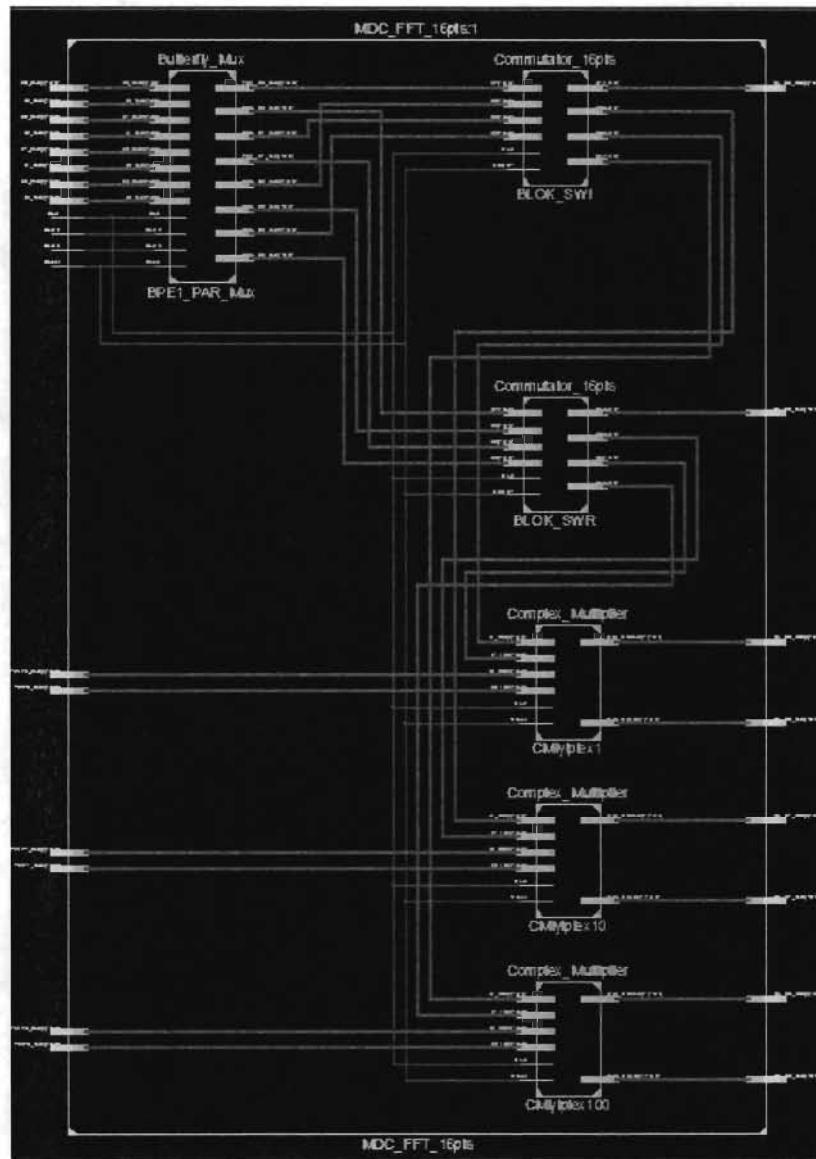

| <i>Figure 49 Schéma technologique complet du R4MDC à 16 points.....</i>                                                                             | 81 |

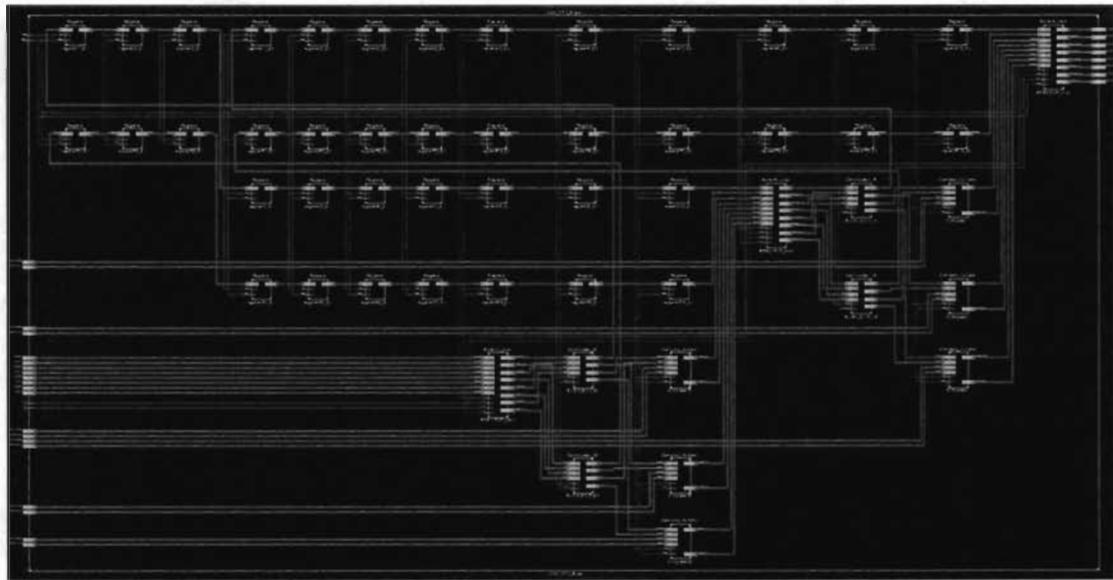

| <i>Figure 50 Schéma technologique complet du R4MDC à 64 points.....</i>                                                                             | 82 |

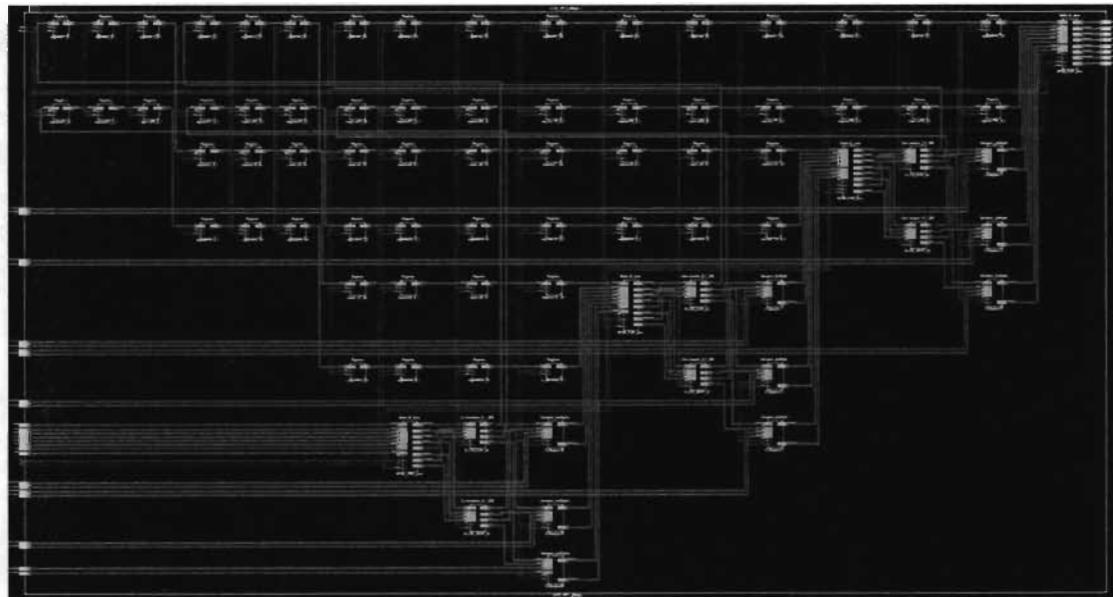

| <i>Figure 51 Schéma technologique complet du R4MDC à 256 points.....</i>                                                                            | 82 |

| <i>Figure 51 Schéma technologique complet du R4MDC à 256 points.....</i>                                                                            | 82 |

# Liste des tableaux

|                                                                                                                                                                               |    |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <i>Tableau 1 Comparaison du nombre d'opérations dans un calcul direct de la DFT et dans la FFT [AV03]</i> .....                                                               | 16 |

| <i>Tableau 2 Nombre d'opérations d'une FFT de 4096 points pour différents radix</i> .....                                                                                     | 22 |

| <i>Tableau 3 Comparaison en termes d'exigences matérielles entre différentes architectures FFT pipelines [SL07]</i> .....                                                     | 32 |

| <i>Tableau 4 Outils de conception</i> .....                                                                                                                                   | 49 |

| <i>Tableau 5 Comparaison des nombres de ressources utilisées par BPE MUX et convontionnelle</i> .....                                                                         | 59 |

| <i>Tableau 6 Comparaison de l'utilisation des ressources nécessaires pour le calcul de la FFT</i> .....                                                                       | 59 |

| <i>Tableau 7 Distribution des registres dans les Commutateurs pour la FFT de radix-2<sup>2</sup></i> ....                                                                     | 67 |

| <i>Tableau 8 Comparaison d'implémentation sur Virtex-5 des FFT radix-2<sup>2</sup> utilisant la BPE MUX et la BPE Conventionnelle (Stratégie : Timing Performance)</i> .....  | 74 |

| <i>Tableau 9 Comparaison d'implémentation sur Virtex-5 des FFT radix-2<sup>2</sup> utilisant la BPE MUX et la BPE Conventionnelle (Stratégie : Area Reduction)</i> .....      | 74 |

| <i>Tableau 10 Comparaison d'implémentation sur Virtex-5 des FFT radix-2<sup>2</sup> utilisant la BPE MUX et la BPE Conventionnelle (Stratégie : Balanced)</i> .....           | 75 |

| <i>Tableau 11 Comparaison d'implémentation sur Virtex-7 des FFT radix-2<sup>2</sup> utilisant la BPE MUX et la BPE Conventionnelle (Stratégie : Timing Performance)</i> ..... | 75 |

|                                                                                                                                                                              |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <i>Tableau 12 Comparaison d'implémentation sur Virtex-7 des FFT radix-2<sup>2</sup> utilisant la BPE MUX et la BPE Conventionnelle (Stratégie : Area Reduction) .....</i>    | 76 |

| <i>Tableau 13 Comparaison d'implémentation sur Virtex-7 des FFT radix-2<sup>2</sup> utilisant la BPE MUX et la BPE Conventionnelle (Stratégie : Balanced) .....</i>          | 76 |

| <i>Tableau 14 Comparaison des performances de l'implémentation de la FFT utilisant des Multiplieurs de nombres complexes conventionnels pipelinés et non pipelinés .....</i> | 77 |

| <i>Tableau 15 Comparaison des performances de l'implémentation de la FFT utilisant des Multiplieurs de nombres complexes optimisés pipelinés et non pipelinés .....</i>      | 77 |

| <i>Tableau 16 Comparaison de résultats d'implémentation sur Virtex-5 entre BPE MUX et conventionnelle (Avec Multiplieurs) de radix-2<sup>3</sup>.....</i>                    | 77 |

| <i>Tableau 17 Résultats d'implémentation des FFT radix2<sup>2</sup> selon la référence [MG13] .....</i>                                                                      | 78 |

| <i>Tableau 18 Synthèse de l'évaluation des performances du FFT radix-2<sup>2</sup> .....</i>                                                                                 | 78 |

## ***Liste des abréviations***

|                 |                                                                |

|-----------------|----------------------------------------------------------------|

| <i>OFDM</i>     | <i>Orthogonal Frequency Division Multiplexing</i>              |

| <i>FFT</i>      | <i>Fast Fourier Transform</i>                                  |

| <i>FPGA</i>     | <i>Field Programmable Gate Array</i>                           |

| <i>DFT</i>      | <i>Discrete Fourier Transform</i>                              |

| <i>DIT</i>      | <i>Decimation In Time</i>                                      |

| <i>DIF</i>      | <i>Decimation In Frequency</i>                                 |

| <i>LSSI</i>     | <i>Laboratoire des Signaux et Systèmes Intégrés</i>            |

| <i>VHDL</i>     | <i>Very High Description Language</i>                          |

| <i>SFG</i>      | <i>Signal Flow Graph</i>                                       |

| <i>BPE</i>      | <i>Butterfly Processing Element</i>                            |

| <i>R2MDC</i>    | <i>Radix2 Multipath Delay Commutator</i>                       |

| <i>SQNR</i>     | <i>Signal Quantization Noise Ratio</i>                         |

| <i>DSP</i>      | <i>Digital Signal Processin</i>                                |

| <i>SRFFT</i>    | <i>Split Radix Fast Fourier Transform</i>                      |

| <i>VLSI</i>     | <i>Processing Element</i>                                      |

| <i>SDF</i>      | <i>Single-path Delay Feedback</i>                              |

| <i>SDC</i>      | <i>Single-path Delay Commutator</i>                            |

| <i>MDC</i>      | <i>Multi-path Delay Commutator</i>                             |

| <i>MC-MRMDC</i> | <i>Multi Channel - Mixed Radix Multi-path Delay Commutator</i> |

|               |                                                   |

|---------------|---------------------------------------------------|

| <i>LPPL</i>   | <i>Locally Pipelined Processor</i>                |

| <i>HRSMA</i>  | <i>High-Radix and Shared Memory Architecture</i>  |

| <i>R2SD2F</i> | <i>Radix-2 Single Deep Delay Feedback</i>         |

| <i>WPAN</i>   | <i>Wireless Personal Area Network</i>             |

| <i>OFDM</i>   | <i>Orthogonal Frequency Division Multiplexing</i> |

# ***CHAPITRE I***

---

## ***INTRODUCTION***

---

La transformée de Fourier, qui est une méthode reconnue pour l'analyse fréquentielle ou spectrale, est un outil essentiel pour l'implémentation et la conception de nombreuses techniques numériques de traitement des signaux et des données [JR07]. Cette technologie se trouve dans plusieurs applications directes comme l'analyse harmonique des vibrations et des signaux musicaux, dans le codage à débit réduit de la musique et de la parole, la reconnaissance vocale, l'amélioration de la qualité des images, leur compression, les transmissions numériques, les nouveaux systèmes de radiodiffusion et de télédiffusion, dans

## CHAPITRE I - INTRODUCTION

---

les applications biomédicales (scanner, imagerie par résonance magnétique nucléaire), en astronomie (synthèse d'image par interférométrie), en modélisation de propagation d'ondes, en analyse spectrale pour l'étude de structures moléculaires ainsi qu'en cristallographie [JR07]. La transformé de Fourier peut être aussi un élément important dans les méthodes envisagées en informatique quantique pour la factorisation de nombres.

La transformation de Fourier discrète (TFD) est l'équivalent discret de la transformation de Fourier continue qui est utilisée pour le traitement du signal analogique.

C'est un outil qui permet d'analyser un signal temporel quelconque de manière discrète (on va donc échantillonner le signal) dans l'espace fréquentiel pour étudier la puissance de chaque fréquence qui compose le signal [JR07].

La transformation de Fourier rapide (en anglais : FFT ou *Fast Fourier Transform*) est un algorithme plus avancé pour le calcul de la transformation de Fourier discrète (TFD). Elle se base sur des éléments de traitement en papillon (BPE – *Butterfly Processing Element*) à radix- $r$  ou en français radical- $r$  ou base- $r$ , où  $r$  usuel sont 2, 4 et 8. Sa complexité s'exprime en  $O(N \log N)$  nombre d'opérations avec  $N$  et  $r$  représentent respectivement, le nombre de points traité par la transformée et le radix- $r$  de la transformation rapide, alors que la complexité de l'algorithme TFD s'exprime de l'ordre de  $O(N^2)$ . Ce qui résulte, pour  $N=1024$ , le temps de calcul de l'algorithme rapide peut être  $\sim 100$  fois plus court que le calcul utilisant la formule de définition de la TFD.

Cette méthode a été publiée pour la première fois en 1965 par James Cooley et John Tukey, ce qui a lancé définitivement l'utilisation massive de la FFT en traitement du signal en

# CHAPITRE I - INTRODUCTION

---

générale et dans les technologies plus spécifique comme la télécommunication. Cet algorithme reste toujours utilisé dans les applications de traitement numérique du signal en particulier dans les analyseurs de spectre. Il est également à la base des algorithmes de multiplication rapide (Schönhage et Strassen, 1971), et des techniques de compression numérique ayant mené au format d'image JPEG (1991).

L'objectif essentiel de la présente étude porte sur l'implémentation au niveau matériel de l'exécution de la BPE de la FFT, l'élément principal pour augmenter les performances en termes de réduction des ressources et d'augmentation de la vitesse des calculs pour répondre aux exigences des nouvelles technologies. La cible matérielle visée dans le cadre de ce mémoire sont les FPGA (*Field Programmable Gate Array*). Les FPGA sont de plus en plus utilisés dans différentes technologies pour sa reconfigurabilité et mise en marché rapide des nouvelles technologies. Leur flexibilité, rapidité et capacité à recevoir des architectures parallèles les rendent intéressantes pour l'implémentation de la FFT.

## 1.1 Problématique

Pour être capable de calculer une TFD on doit utiliser  $N^2$  nombre d'opérations (multiplications et additions), avec  $N$  représente la taille de la transformée. La taille de  $N$  ainsi que le nombre d'opérations continuent toujours à augmenter avec l'évolution des diverses applications des systèmes de communications [MJ09]. Plusieurs algorithmes ont été élaborés dans les années récentes dont le but est pour diminuer le nombre d'opérations de la TFD. Ces algorithmes sont connus sous le nom d'algorithmes FFT.

## CHAPITRE I - INTRODUCTION

---

En effet, l'algorithme de la FFT permet la possibilité d'exécuter rapidement la DFT sur processeur électronique. Le premier algorithme FFT développé par Cooley-Tukey est connu sous le nom de radix-2 DIT (*Décimation In Time*), il requiert  $M \log_2 N$  nombre d'opérations au lieu de  $N^2$  pour le calcul direct de la DFT [JWC65], où ‘ $r$ ’ représente le radix. On remarque bien la diminution concrète du nombre d'opérations à effectuer. Une nouvelle approche de calcul appelé 'papillon' connu sous le nom 'Butterfly Computation' a été introduite par cet algorithme.

Avec l'augmentation constante de la vitesse d'exécution des différents nouveaux systèmes ainsi que le débit (*Throughput*) des données exigées à l'entrée et le cout croissant de l'accès à la mémoire, concevoir des BPE pour la FFT est devenu l'objectif principal de plusieurs recherches dans le domaine du traitement de signal. À travers ces nouvelles architectures, on essaye toujours d'utiliser la moindre des ressources matérielles tout en réduisant la consommation de puissance. En effet, on peut trouver une grande variance d'algorithmes qui ont été développés et étudiés pour améliorer davantage la manière d'implémentation des FFT, parmi ces algorithmes on trouve le radix-2 introduit par (Cooley-Tukey), le Split radix Algorithm [TYS10], Winograd Fourier Transform Algorithm (WFTA) [SW75] et bien d'autres.

Grâce à l'architecture simplifiée de leur BPE, les radix-2 et radix-4 conventionnels sont considérés comme les algorithmes les plus utilisés en industrie, ce qui leur donne un avantage par rapport aux algorithmes FFT de radix plus élevé. Plus on utilise un radix élevé, plus le nombre des opérations arithmétiques pour calculer une FFT de  $N$  points diminue,  $O(M \log_r N)$ . En outre, avec un radix élevé, l'architecture de la BPE pour exécuter la FFT devient plus complexe et exigeante en termes de calcul arithmétique, de connexions, et de

## CHAPITRE I - INTRODUCTION

---

nombres du délai du chemin critique (*Critical Path Delay*). En contrepartie, plus le radix est élevé, moins d'itérations sont nécessaire dans l'utilisation de la BPE (moins d'étage d'exécution de BPE), ce qui, dans l'ensemble du calcul de la FFT, réduit le nombre d'opérations arithmétiques, mais introduit une grande complexité en termes d'accès mémoires, de temps de calcul par BPE et de complexité du flot des données. Ceci ne veut pas dire que l'utilisation d'un radix élevé est toujours un désavantage puisque son utilisation nous permet de réduire le nombre de multiplications et de nombre d'étages pour exécuter la FFT, il y a donc un compromis à chercher dans la dimension du radix, des ressources et du temps de calcul pour l'exécution d'une FFT de taille  $N$ . En sachant, qu'une multiplication prend plus d'espace en silicium ou de ressources matérielles qu'une simple addition et que la diminution du nombre d'étages diminue la charge d'interconnexion et d'accès mémoires, l'utilisation de BPE de radix plus grand est bénéfique au niveau de l'implémentation matérielle [MJ09]. À condition que la complexité de la BPE permette de satisfaire les compromis dans la complexité d'implémentation et la vitesse.

Une nouvelle formulation de la FFT [MJ14], développée au sein du laboratoire LSSI (Laboratoire des Signaux et Systèmes Intégrés), permet l'utilisation d'une architecture innovante de BPE avec radix plus grand tout en gagnant un avantage en termes de vitesse de calcul et des ressources utilisées (ex : nombre de Slices et DSP48 des FPGA de Xilinx).

### 1.2 Objectif

L'objectif principal de ce projet est l'évaluation de la nouvelle formulation de la FFT en vue d'une implémentation plus efficace que les propositions conventionnelles et des plus récentes de la littérature. Cette évaluation est faite en termes de temps de calcul et de ressources matérielles d'implémentation en technologie FPGA. Les sous-objectifs permettant de rencontrer l'objectif principal sont :

- Étude des algorithmes FFT et leur implémentation.

- Étude de la nouvelle formulation de la FFT proposée dans les travaux du LSSI et publié dans [MJ14]. Plus spécifiquement les structures BPE radix-2, radix- $2^2$  et radix- $2^3$ .

- Étude des architectures FFT pipelines et parallèles, les avantages et les techniques d'implémentation.

- Modélisation, simulation et implémentation des nouvelles structures BPE (*Butterfly Processing Element*) dans des FFT de différentes grandeurs sur Matlab® et en VHDL pour évaluer leurs performances sur FPGA (Virtex-5, Virtex-7 ...) et comparer ensuite avec les derniers résultats dans la littérature.

### 1.3 Méthodologie

Afin de réaliser nos objectifs, notre méthode de travail consiste en premier lieu d'étudier les algorithmes conventionnels pour calculer la FFT comme : radix-2, radix- $2^2$  et radix- $2^3$ , ils

## CHAPITRE I - INTRODUCTION

---

serviront tout au long du projet pour comprendre les algorithmes de références puisqu'ils sont les plus utilisés en industrie.

Cette étude permettra de comprendre les différentes techniques d'implémentation des architectures MDC (*Multi path Delay Commutator*) et des BPE (*Butterfly Processing Element*) à partir des équations mathématiques qui régissent les algorithmes FFT conventionnels.

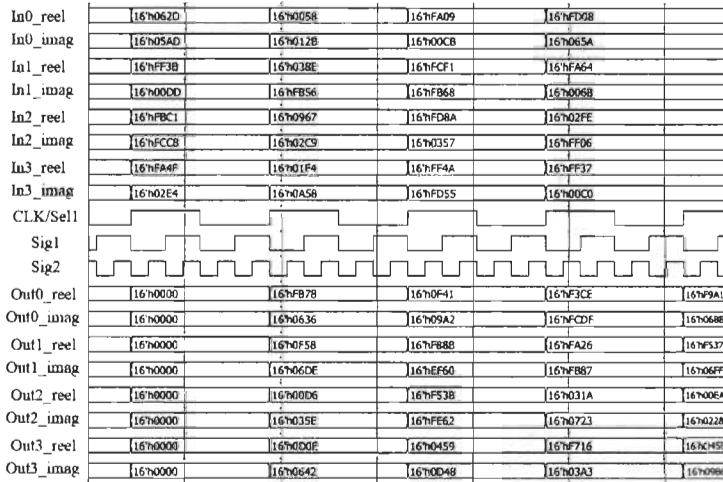

Pour bien comprendre leurs bons fonctionnements et leurs équations mathématiques qui les gèrent, on utilise Matlab® pour programmer les FFT conventionnels. L'outil Matlab® sera notre plateforme pour effectuer les vérifications et les évaluations sur tous les algorithmes qui seront programmés et implémentés durant le projet. Après étude de la nouvelle architecture de la BPE proposée par les travaux de 'Marwan Jaber' et 'Daniel Massicotte', nommé BPE\_MUX, on la programme cette fois sur notre plateforme Matlab®. On testera sur cette dernière, son bon fonctionnement en l'introduisant dans une architecture FFT complète.

Une fois cette étape complétée, on programmera la nouvelle BPE en VHDL. L'outil choisi pour faire la simulation VHDL est Modelsim (PE Edition 10.2a) de Mentor Graphics®. Cette nouvelle architecture programmée en VHDL sera testée sur Modelsim® avec des programmes 'testbench' conçus pour valider la structure VHDL du BPE afin de l'utiliser pour constituer le Processeur FFT. On effectue une co-simulation Matlab® / Modelsim®. La plateforme Matlab® est utilisée pour générer les données normées entre 1 et -1 (vecteurs d'entrée et Twiddle *Factors*) en virgules fixes (16 bits), ces données sont après utilisées pour les injecter dans la BPE programmée sur Matlab® et sur Modelsim®. L'erreur entre les sorties des BPE en virgules fixes sera comparée pour valider le bon fonctionnement du BPE.

## CHAPITRE I - INTRODUCTION

---

On s'attend à avoir des résultats de ces simulations dans le chapitre 3, où l'erreur doit être égale ou inférieure au bit le moins significatif. On se servira alors de cette nouvelle BPE pour construire les coprocesseurs FFT pour différentes grandeurs (16 points, 64 points et 256 points).

Les BPE des FFT programmées dans le projet ont une architecture pipeline. C'est grâce à leur bon compromis vitesse/surface qu'elles étaient choisies. L'architecture programmée est essentiellement R4MDC (*Radix4 Multipath Delay Commutator*) qui sera détaillée dans les chapitres 2 et 3.

Enfin, la synthèse FPGA de la nouvelle BPE (BPE\_MUX) ainsi que son implémentation FPGA sont effectuées sur Xilinx ISE 14.6. Les résultats obtenus démontreront l'efficacité réelle de la nouvelle formulation de la BPE en termes de vitesse de calcul et des ressources matérielles d'implémentation en technologie FPGA.

L'évaluation des algorithmes FFT pour différentes tailles est donc faite suivant quatre étapes : (i) étude théorique des algorithmes FFT, (ii) étude de la nouvelle formulation de la BPE proposée dans les travaux du LSSI [MJ14], (iii) étude des architectures FFT pipelines et parallèles et leur modélisation et enfin (iv) l'implémentation des BPE constituants les BPE de la FFT sur Matlab® et en VHDL pour évaluer leurs performances sur FPGA.

Cette étude des différentes architectures FFT pipelines et parallèles, était l'occasion parfaite pour approfondir nos connaissances dans ce domaine de recherche. Pour l'évaluation des différentes architectures FFT on les a directement modélisées en VHDL sans passer par un logiciel qui génère du code VHDL. La nouvelle architecture du BPE développée a été programmée avec la façon la plus optimale pour réduire sa complexité et obtenir des résultats acceptables en comparant avec la référence.

### 1.4 Organisation du mémoire

Ce mémoire est organisé comme suit :

Dans le Chapitre 2, on expliquera le principe de la TFD qui sera la base pour introduire la Transformée de Fourier Rapide (*Fast Fourier Transform : FFT*). La mathématique qui gère l'algorithme conventionnel et l'approche deviser pour régner de cette architecture sera donc expliquée.

On parlera après des FFT de radix-2 et de radix-4 puisqu'ils seront la base de travail de notre projet. Une brève définition des architectures parallèles sera après faite suivit par une étude des architectures pipelinées et l'effet de la quantification (virgule fixe) sur la conception de la FFT. Dans la dernière section de ce chapitre, on introduira une présentation des dernières recherches qui étaient faites dans ce domaine avec leurs différentes approches pour améliorer le fonctionnement de la FFT en tenant compte de différents paramètres.

Le chapitre 3 discutera l'implémentation sur FPGA de la BPE\_MUX proposée par Jaber&Massicotte (Simulation VHDL, Synthèse FPGA) avec toutes les étapes nécessaires pour atteindre le meilleur résultat de performance. On commencera le chapitre par introduire et expliquer la théorie derrière les différents éléments nécessaires pour l'implémentation de la FFT. On discutera après les résultats de synthèse selon les critères mis en place. Enfin, le chapitre 4 présentera la conclusion générale du projet de recherche.

## ***CHAPITRE II***

---

### ***IMPLÉMENTATION DE LA FFT – ÉTAT DE L’ART***

---

Avec l'évolution exponentielle des systèmes techniques avancés, le besoin d'une vitesse d'exécution et une complexité matérielle croissante ne cessent d'augmenter. D'où vient la nécessité de concevoir des architectures VLSI de coprocesseurs FFT qui répondent aux exigences de vitesse (haut débit binaire) et qui sont moins complexes en termes de ressources matérielles pour des raisons de coûts et de réduction de la consommation énergétique [YJ03].

Dans ce chapitre on étudiera les deux architectures les plus communes en termes d'efficacité d'implémentation de la FFT ; l'architecture parallèle et l'architecture pipeline ainsi que les

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L'ART

---

différentes approches pour les implémenter. Leurs caractéristiques, avantages et inconvénients seront aussi étudiés.

### 2.1 Transformée de Fourier Discrète

La Transformée de Fourier Discrète (TFD), (*DFT : Discrete Fourier Transform*) est un élément essentiel dans l'analyse, la conception et la mise en œuvre des algorithmes et systèmes du traitement du signal à temps discret. En physique numérique, on dispose presque toujours de signaux issus d'une acquisition électronique ou de résultats de mesures discrètes.

Ces signaux et résultats ne sont pas infinis, et généralement sont non périodiques. La TFD a été conçue pour traiter ce genre de données. Elle réalise une décomposition d'un signal tronqué (fini, de durée  $T$ ) et échantillonné (discret) en une série de Fourier, en le "périodisant", avec une période égale à  $T$ . La TFD nous permet donc de calculer de façon approchée les coefficients de Fourier des différentes harmoniques d'un signal quelconque et ainsi d'obtenir son spectre en fréquence.

Son application est donc utilisée dans plusieurs domaines technologiques tels que les télécommunications, le biomédical, le traitement séismique, etc. [YW07], [MJ08]

La DFT d'un signal discret  $x(n)$  peut-être directement calculée par l'équation (2.1),

$$X(n)^n = \sum_{n=0}^{N-1} x(n)W_N^{nk}, \quad k \in [0, \dots, N - 1] \quad (2.1)$$

Avec  $x(n)$  et  $X(n)$ , respectivement, représentent la séquence d'entrée et la séquence de sortie en nombre complexe et  $N$  est la longueur de la transformée. À partir de l'équation (2.1), on

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L'ART

---

constate que la complexité de calcul de la TFD s'exprime en  $O(N^2)$ , il augmente avec le carré de la longueur de la transformée et donc devient cher pour des  $N$  larges. Plusieurs additions et soustractions, en plus de quelques autres opérations, sont nécessaires donc pour réaliser une seule multiplication complexe. C'est pour ces raisons que la TFD n'est pas utilisée pour le traitement du signal temps réel. Puisque le processeur numérique est généralement limité par la taille de sa mémoire. La taille de la TFD  $N$  limite les calculs exécutés le processeur [WY07].

L'équation de définition de la DFT fournit une relation entre deux ensembles de  $N$  nombres complexes, en posant :

$$W_N^{nk} = e^{-j(2\pi/N)nk} \text{ avec } j^2 = -1 \quad (2.2)$$

$W_N^p$  est appelé Facteur de Fourier (*Twiddle Factors*), plusieurs propriétés caractéristiques de la représentation de ce coefficient sont utilisées [AV03], par exemple :

$$\begin{aligned} W_N^{kn} &= W_N^{k(n+N)} = W_N^{(k+N)n} \\ W_N^{2kn} &= W_{N/2}^{kn} \\ W_N^{k(N-n)} &= (W_N^{kn})^* \end{aligned} \quad (2.3)$$

Où  $x^*$  représente le complexe conjugué de la donnée complexe  $x$ .

Une forme matricielle montrée par l'équation (2.4) de la DFT peut être donc déduite.

$$x(k) = \begin{bmatrix} W_N^0 & W_N^0 & \cdots & W_N^0 \\ \vdots & \ddots & & \vdots \\ W_N^0 W_N^{(N-1)} & \cdots & W_N^{(N-1)(N-1)} \end{bmatrix} \begin{bmatrix} x(0) \\ \dots \\ x(N-1) \end{bmatrix} \quad (2.4)$$

Elle peut être représentée sous la forme matricielle suivante :

$$X(k) = [B_N][x_n] \quad (2.5)$$

Avec  $[B_N]$  la matrice des coefficients et  $[x_n]$  la matrice d'entrée de la TFD.

Donc la TFD est une décomposition d'un signal échantillonné, composé de sinusoïdes.

En exploitant les propriétés de symétrie et de périodicité de la TFD, plusieurs méthodes efficaces ont été développées pour calculer la TFD et ainsi diminuer significativement la charge de calcul.

### 2.2 La Transformée de Fourier Rapide

En introduisant le premier algorithme de la FFT en 1965, Cooley&Tukey ont été capable de réduire d'une façon remarquable le temps de calcul de la TFD d'une suite de nombre d'échantillons  $N$  qui est une puissance de 2, connu sous le nom de radix-2 [JC65]. Depuis, et encore dans les dernières années, les algorithmes de FFT ont été dans le centre d'intérêt pour de nombreuses recherches qui ont révolutionné le traitement numérique de signal (*DSP : Digital Signal Processing*). La réduction du nombre d'opérations nécessaires, en particulier le nombre des multiplications constituent leurs avantages essentiels et est devenu l'approche de base dans toutes les nouvelles applications.

La grande majorité des algorithmes sont basés sur un même principe qui consiste à décomposer le calcul de la TFD en plusieurs sous-ensembles de TFD de longueur plus petite.

En profitant des propriétés de symétrie et de périodicité suivant les équations (2.6) et (2.7) des facteurs de phases :

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L'ART

---

Symétrie :

$$\begin{aligned} W_N^{k+N/2} &= -W_N^k \\ (W_N^k)^* &= W_N^{-k} \end{aligned} \tag{2.6}$$

Périodicité :

$$W_N^{k+N} = W_N^k \tag{2.7}$$

Où (\*) désigne le complexe conjugué.

Malgré que le nombre des opérations serait réduit d'une façon remarquable, la complexité globale reste  $O(N^2)$  [OA75] et son flot des données demeure complexe dans l'implémentation.

Les algorithmes de FFT permettent de faire une DFT d'une manière efficace ainsi que de réduire la charge de calcul en termes de multiplications et additions à valeurs complexes à l'ordre  $O(N \log_2 N)$ . Il existe de nombreux algorithmes FFT qui découlent tous de l'approche diviser pour régner (*divide and conquer approach*).

### 2.2.1 Algorithmes conventionnels

Les algorithmes les plus connus et les plus utilisés sont les algorithmes FFT où  $N$  est une puissance entière de deux,  $N = 2^M$ , où  $M$  un entier. Grâce à ces algorithmes, il est possible de réduire le nombre d'opérations nécessaires à un ordre de grandeur de  $N \log_2(N) = N \times M$  [AV03].

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L'ART

---

Le tableau suivant donne un résumé des valeurs  $N^2$ ,  $N\log_2(N)$ ,  $N/\log_2(N)$  pour diverses valeurs de  $N$ . La dernière colonne montre de combien la vitesse de calcul peut être augmentée par l'utilisation de la FFT au lieu du calcul direct de TFD [AV03].

*Tableau 1 Comparaison du nombre d'opérations dans un calcul direct de la DFT et dans la FFT [AV03]*

| Taille de la TFD<br>$N$ | TFD     | FFT<br>$N\log_2(N)$ | Gain<br>$N/\log_2(N)$ |

|-------------------------|---------|---------------------|-----------------------|

|                         | $N^2$   |                     |                       |

| 2                       | 4       | 2                   | 2.00                  |

| 4                       | 16      | 8                   | 2.00                  |

| 8                       | 64      | 24                  | 2.67                  |

| 16                      | 256     | 64                  | 4.00                  |

| 32                      | 1024    | 160                 | 6.40                  |

| 64                      | 4096    | 384                 | 10.67                 |

| 128                     | 16384   | 896                 | 18.29                 |

| 256                     | 64536   | 2048                | 32.00                 |

| 512                     | 262144  | 4608                | 56.89                 |

| 1024                    | 1048576 | 10240               | 102.40                |

### 2.2.2 Approche diviser-pour-régner

L'idée de cette approche consiste à représenter les vecteurs  $X[k]$  et  $x(n)$  sur deux dimensions (cas du radix-2, radix-4, radix-8, etc...) ou bien plusieurs dimensions (cas du radix- $2^i$ , radix- $4^i$ ). L'algorithme de la FFT et ses variantes sont détaillés dans de nombreux ouvrages, notamment Proakis et Manolakis [JG96]. Le principe de base de l'algorithme consiste à

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L'ART

---

faire un changement de variable de l'indice  $n$  sur deux dimensions entières. Par exemple, avec  $M$  pour les colonnes et  $L$  pour les lignes, on a :

$$N=ML \quad (2.8)$$

$$N= Ml+m ; 0 \leq l \leq L-1, \text{ et } 0 \leq m \leq M-1 \quad (2.9)$$

$$k=Mp+q; 0 \leq p \leq L-1, \text{ et } 0 \leq q \leq M-1 \quad (2.10)$$

Avec ce changement de variable, les points de séquence à transformer seront représentés sous forme matricielle. Ainsi, l'équation de la DFT devient :

$$X[p, q] = \sum_{m=0}^{M-1} \sum_{l=0}^{L-1} X[1, m] W_N^{(Mp+q)(mL+1)} \quad (2.11)$$

Le terme  $W_N^{(Mp+q)(mL+1)}$  peut être simplifié de la manière suivante :

$$W_N^{(Mp+q)(mL+1)} = W_N^{MLmp} W_N^{mLq} W_N^{Mp l} W_N^{lq} \quad (2.12)$$

Toutefois selon (2.6) et (2.7)

$$W_N^{MLmp} = 1, W_N^{mLq} = W_M^{mq} = W_{N/L}^{mq} \text{ et } W_N^{Mp l} = W_L^{lp} = W_{N/M}^{lp}$$

De là on obtient l'équation :

$$X[p, q] = \sum_{l=0}^{L-1} \left\{ W_N^{lq} \left[ \sum_{m=0}^{M-1} X[1, m] W_M^{mq} \right] \right\} W_L^{lp} \quad (2.13)$$

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L'ART

---

L'équation (2.13) illustre le fonctionnement de la FFT. Soit la décomposition de la FFT à  $N$  points, en  $L$  FFT à  $M$  points. Pour résoudre l'équation (2.13), nous procérons d'abord à des TFD de  $M$  points correspondant à la sommation à l'intérieur entre crochets. Ensuite, la matrice résultante est multipliée point à point par les facteurs de phase  $W_L^{lp}$  et enfin des TFD sur  $L$  points sont effectuées en suivant l'autre dimension. En effectuant ces étapes, la complexité passe de l'ordre  $N^2$  à l'ordre  $N(M+L)$ . Nous pouvons aussi récursivement faire d'autres changements de variables, en prenant un nombre premier pour  $L$ . Par la suite, nous factorisons  $M$  jusqu'à obtenir seulement des TFD ayant des tailles de nombre premier [JG96]. L'algorithme divisor pour régner peut se résumer dans les étapes suivantes [JG96] :

- i. Calcul de  $M$ -point DFT,  $F(l, q)$  de chaque ligne selon l'équation (2.14).

$$F(l, q) = \sum_{m=0}^{M-1} X(1, m) W_M^{mq} \quad (2.14)$$

- ii. Multiplier le tableau résultant par le facteur de phase  $W_N^{lq}$ , en obtient  $G(l, q)$  défini par :

$$G(l, q) = W_N^{lq} F(l, q) \quad (2.15)$$

- iii. Finalement, calcul de  $L$ -points DFT de chaque colonne selon l'équation (2.16) :

$$X(p, q) = \sum_{l=0}^{L-1} G(l, q) W_L^{lp} \quad (2.16)$$

### 2.2.3 Radix-2

Radix-2 ou en français Radical-2 ou base-2, signifie que la taille  $N$  de la FFT à calculer soit à base de 2. Sa structure est très simple, appelée structure Butterfly (papillon) à cause de son schéma en forme de papillon, elle peut être aussi appelée BPE (*Butterfly Processing Element*). On peut différencier entre deux algorithmes : DIT (*Decimation In Time*, Décimation dans le temps) et DIF (*Decimation In Frequency*, Décimation en fréquence). D'une part, quand la division en Butterfly, commence du côté de l'entrée (signal temporel), on l'appelle DIT et d'autre part, quand division en Butterfly, se fait du côté de la fréquence, cet algorithme est appelé DIF.

Dans ce travail nous nous intéressons à la version DIT pour l'implémentation sur FPGA sachant que la version DIF est similaire.

Le radix-2 utilise la technique 'diviser pour régner' [JW65], donc à l'aide de cette technique, il divise la FFT en sous-système de  $N/2$  points, puis calcule chaque sous-système tout seul pour obtenir à la fin les composantes du spectre fréquentiel du signal.

Figure 1 Structure DIT Butterfly

La figure 1 représente le schéma d'une structure Butterfly DIT de la FFT. On remarque que cette structure, avec  $p = 0$ , représente exactement la relation qui existe entre les

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L'ART

---

échantillons à l'entrée  $x[0]$  et  $x[1]$  et les échantillons en sortie  $X[0]$  et  $X[1]$ , dans une TFD à 2 points. La figure 2 quant à elle, représente la structure d'une Butterfly DIF.

Figure 2 Structure DIF Butterfly

Les figures 1 et 2 représentent les deux structures Butterfly utilisées respectivement pour le DIT et DIF FFT. Pour le DIT, les facteurs de Fourier (TFW) sont multipliés par l'entrée  $x[1]$  puis le produit est, ou ajouté ou retranché, à  $x[0]$ . D'une autre part, pour le DIF les entrées  $x[0]$  et  $x[1]$  sont additionnées pour la première sortie puis pour la deuxième sortie,  $x[0]$  est soustraite de  $x[1]$  et on multiplie par le TWF.

Les figures 3 et 4 représentent les structures des deux algorithmes radix-2 DIT et DIF :

Figure 3 Diagramme de la FFT à base de BPE radix-2 de type DIT

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L'ART

---

Dans les figures 3 et 4, on représente la structure du radix-2 DIT et DIF pour 8 points.

Figure 4 Diagramme de la FFT à base de BPE radix-2 de type DIF

Pour une taille  $N=8$ , pour un radix-2, on a  $\log_2 N$  étages pour calculer la FFT, donc trois étages pour notre cas  $N=8$ . On a aussi  $N/2$  BPE à calculer par étage, soit 4 pour notre cas ici. Le radix-2, DIT ou DIF, réduit aussi l'ordre de calcul de  $N^2$  à  $N/2 \log_2 N$  multiplications complexes et de  $N^2-N$  à  $N \log_2 N$  additions complexes. Grâce à ces avantages, le radix-2 est l'algorithme FFT le plus utilisé actuellement. Il apparaît dans plusieurs articles de l'IEEE [YW07], [YT02], [YT04], grâce à sa simple architecture.

### 2.2.4 Radix-4

Le radix-4 est un algorithme FFT qui peut être utilisé dans le cas où on veut réduire le nombre de multiplications complexes d'environ 25% par rapport au radix-2 [TW97], [MB98]. Ceci est vrai dans le cas où la taille de la FFT est une puissance de 4.

La structure simplifiée du BPE radix-4, représenté dans la figure 5.

Figure 5 BPE du radix-4 DIT

Comme le montre le tableau 2, le nombre de multiplications complexes est réduit par rapport au radix-2 pour une taille de FFT plus grande.

Tableau 2 Nombre d'opérations d'une FFT de 4096 points pour différents radix

| Opérations                | Radix-2 | Radix-4 |

|---------------------------|---------|---------|

| Multiplications complexes | 22528   | 15360   |

| Additions complexes       | 49152   | 15360   |

| Accès mémoire             | 49152   | 24576   |

### 2.3 Architecture parallèle pour le calcul de la FFT

L'architecture parallèle est utilisée grâce à sa rapidité et son efficacité. Cette architecture est une reproduction directe du mappage du SFG (*Signal Flow Graph*) de la FFT. En effet,  $(N/r) \cdot \log N$  BPE sont nécessaires pour calculer cette architecture, ce qui prouve que son besoin en ressources matérielles augmente rapidement avec la taille  $N$  de la FFT.

La figure 6 représente l'implémentation de l'architecture parallèle du SFG radix-2 de type DIT (avec  $N=8$ ).

En plus de son énorme besoin de ressources matérielles, un des problèmes de cette architecture est la faible utilisation des BPE puisque les données d'entrée sont séquentielles tandis que les données de sorties sont générées en parallèle.

*Figure 6 Architecture parallèle du radix-2 ( $N=8$ )*

Ce problème peut être résolu si on alimente les entrées des BPE par  $N$  trames de données parallèles à chaque cycle d'horloge. On verra donc l'utilisation des BPE augmentée à 100% (figure 6). On constate aussi l'ajout de deux modules 'digit reverse' et 'reorder' qui assure que les données entrent et sortent dans le bon ordre pour l'obtention du bon calcul de la FFT,

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L’ART

---

[TW97]. La figure 7 montre un autre exemple de l’architecture parallèle, celui du radix-4 avec  $N=16$  points.

Figure 7 Architecture parallèle du radix-4 ( $N=16$ )

À partir de la figure 8, qui représente l’architecture parallèle du SRFFT (4/2) pour  $N=32$  points, on remarque que plus la taille  $N$  augmente, plus l’architecture prend d’espace dans le processeur. Ce problème limite à des petites tailles de FFT. Cependant, elle reste une des meilleures solutions d’implémentation si la taille de la FFT ne dépasse pas 64 points.

Figure 8 Architecture parallèle du SRFFT-4/2 ( $N=32$ )

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L’ART

---

D’autres avantages pour cette architecture peuvent être cités dont :

- L’implémentation efficace sur FPGA (grâce à la structure parallèle Manhattan).

- Optimisation dans l’utilisation du Butterfly.

- Réduction du nombre des TWF.

- Fréquence d’horloge qui peut atteindre 400 MHz sur les nouvelles FPGA Virtex5 de Xilinx.

### 2.4 Architectures pipelines pour le calcul de la FFT

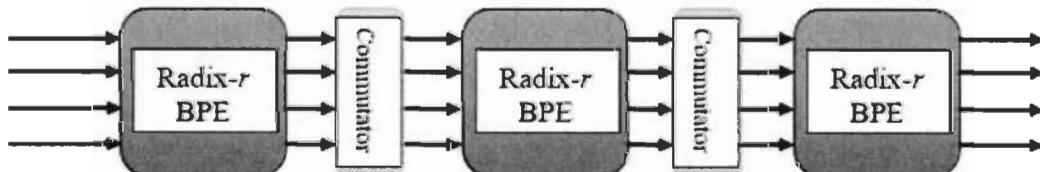

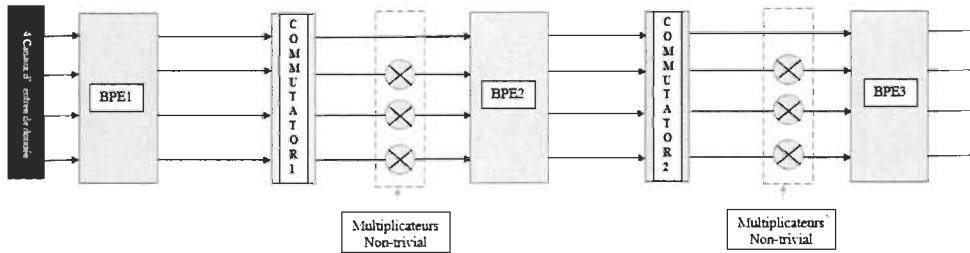

L’architecture en pipeline radix- $r$  FFT (figure 9) est caractérisée par un traitement continu des entrées séquentielles de la FFT. Une telle architecture est composée de  $\log_r N$  modules de calcul (MC), un par étage, qui correspondent aux opérateurs papillon. La valeur de  $r$  correspond au radix de l’algorithme utilisé. Chaque BPE traite  $N/r$  opérations successives. Par conséquent, la taille maximale réalisable pour ce type d’architecture est dictée par le nombre de MC. En effet, ce type d’architecture offre un bon compromis complexité matérielle/taux de traitement de données pour les systèmes de communication à haut débit [YJ03].

Figure 9 Architecture pipeline de base [YJ03]

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L’ART

---

Comme le montre la figure 9, l’architecture comporte un nombre de modules ‘Commutator’. Ces derniers réorganisent les données entre les BPE et contiennent les modules de délais. À chaque étage du pipeline, un BPE, calcule  $r$  donnés de valeurs complexes, puis génère  $r$  donnés intermédiaires à la sortie. On a donc un débit de données  $r$  fois la fréquence d’horloge. Pour un BPE de radix-2 qui fonctionne à R MHz, les données sont traitées à une fréquence de 2R MHz, puisque deux données sont traitées au cours de chaque période d’horloge. [YJ03].

Il existe plusieurs architectures en pipeline basé principalement selon deux points :

1. Le premier point de différence est le nombre de chemins de données utilisés pour traiter les échantillons. Il y a deux types d’architectures : i) à chemin unique (*Single-path; S*) et ii) à chemin multiple (*Multi-path; M*).

2. Le deuxième point de différence consiste en la stratégie de mémorisation pour créer les différents délais nécessaires à l’ordonnancement des échantillons.

Selon ces deux critères, nous pouvons diviser les architectures pipelines en trois types [SH98] :

- Radix- $r$  SDF: *Single-path Delay Feedback*.

- Radix- $r$  SDC: *Single-path Delay Commutator*.

- Radix- $r$  MDC: *Multi-path Delay Commutator*.

### 2.4.1 Single-path Delay Feedback SDF

L’architecture SDF (*Single-path Delay Feedback*) est largement utilisée pour les systèmes de télécommunications pour réduire la complexité matérielle. On peut trouver plusieurs

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L’ART

architectures SDF, tel que la R2SDF (*Radix-2 Single-path Delay Feedback*), la R4SDF, la R8SDF et la R $2^3$ SDF. Par exemple, l’architecture SDF est considérée comme la meilleure approche afin de calculer la FFT pour un système OFDM à un seul canal parce qu’elle requiert le moins de ressources matérielles et qu’elle possède une seule entrée et sortie ce qui la rend très appropriée pour un système SISO-OFDM (*Single Input Single Output Orthogonal Frequency Division Multiplex*), [HS09], [SL07]. La figure 10 et 11 ci-dessous, représente deux architectures SDF, la R2SDF et la R4SDF.

Figure 10 Architecture R2SDF ( $N = 16$  points)

Figure 11 Architecture R4SDF ( $N = 16$  points)

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L’ART

---

Les figures 10 et 11 représentent les architectures R2SDF et R4SDF respectivement pour  $N = 16$  points. Il est clair que l’architecture SDF utilise les registres de manières plus efficaces en stockant les sorties des BPE dans les registres à décalage de la chaîne à rétroaction. Dans l’architecture SDF, la séquence de données d’entrée passe par le chemin d’accès unique puis est réorganisée par l’unité de calcul BPE. À cause du chemin unique d’accès, un seul multiplicateur complexe est utilisé après chaque BPE. La complexité matérielle est donc faible. Toutefois, l’architecture fonctionne à une faible vitesse et le contrôle de synchronisation des données demeure complexe, [YJ03]. Puisque l’architecture SDF possède un seul chemin d’accès d’entrée et de sortie et a un faible débit binaire, plusieurs coprocesseurs FFT R4SDF doivent être utilisés pour un système multi canal. Par exemple, pour un système MIMO-OFDM à 4 canaux, quatre architectures R4SDF doivent être utilisées (une pour chaque canal). On constate que la complexité matérielle augmente avec le nombre de canaux du système [HS09].

### 2.4.2 *Single-path Delay Commutator SDC*

Malgré que cette architecture utilise le même nombre de multiplicateurs complexes que l’architecture pipeline SDF, elle utilise par contre un commutateur de délais qui possède une seule entrée et plusieurs sorties. Le nombre de sorties du commutateur varie selon le nombre d’entrées du BPE. La figure 12 représente une architecture pipeline R4SDC. À chaque coup d’horloge, les données sont injectées au BPE par le commutateur de délais. Ce dernier effectue ses calculs pour envoyer les résultats dans le chemin unique pour l’étage suivant.

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L’ART

Comme l’architecture SDF, l’architecture SDC opère à un faible débit binaire puisqu’elle possède un seul chemin d’accès d’entrée et de sortie.

Figure 12 Architecture R4SDC ( $N = 256$  points)

Donc, pour un système multi canal, elle a besoin de plusieurs coprocesseurs pour chaque canal du système ce qui augmente le besoin de cette architecture en ressources matérielles au cours de l’implémentation [YJ03], [HS09].

### 2.4.3 Multi-path Delay Commutator MDC

L’architecture radix- $r$  MDC (*Multi-path Delay Commutator*) est considérée comme l’une des conceptions les plus utilisées dans la mise en œuvre des systèmes de communication à haut débit. Un des éléments qui fait partie de cette architecture est le commutateur qui a pour rôle de permutez les données entre les étages de l’architecture, on trouve aussi des délais pour synchroniser ces mêmes données. Dépendamment de l’algorithme radix- $r$  utilisé, nous aurons  $r-1$  délais avant et après chaque module BPE. De plus, cette architecture nécessite  $r-1$  multiplicateurs par module BPE.

On peut trouver plusieurs variétés de cette architecture, nous trouvons par exemple le R2MDC et le R4MDC qui sont les architectures les plus populaires, on trouve aussi les radix supérieures comme le radix- $2^2$  et radix- $2^3$ . De plus, l’approche MDC est l’architecture la

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L’ART

plus adaptée dans les nouvelles applications puisqu’elle possède un multiple chemin d’entrées et de sorties [FB09]. Cette propriété permet aux modules FFT utilisant cette architecture d’opérer à haute vitesse avec un haut débit.

D’une autre part, cette architecture utilise plus de ressources matérielles. Une des méthodes utilisées pour réduire la consommation est d’aller plus haut dans le degré de la FFT implémentée.

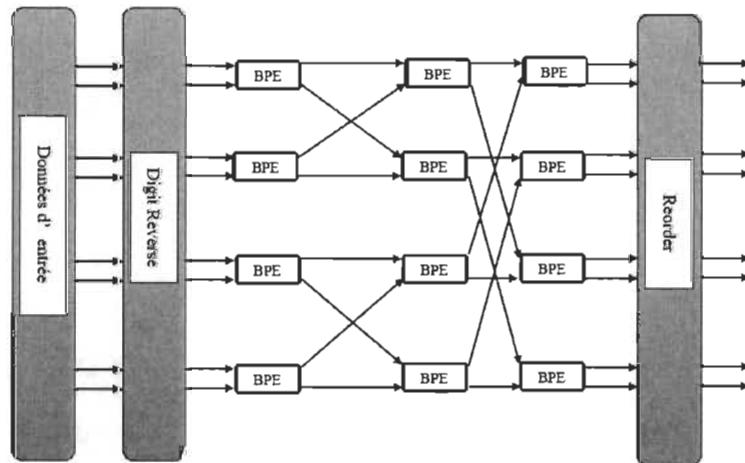

Figure 13 Architecture R4MDC ( $N = 64$  points)

La figure 13 représente l’architecture pipeline R4MDC à 4 canaux pour  $N=64$  points. Cette architecture utilise quatre chemins d’entrées en parallèle, et la même chose est trouvée en sortie. Le flux de données d’entrée et les données inter-étage sont contrôlés avec des commutateurs. Ces derniers sont implantés par de simples éléments de délais et un multiplexeur, ce qui réduit leurs complexités matérielles au cours de leurs implantations. Le rôle de ces commutateurs est de réorganiser les quatre flux d’entrées/sortie de données avant de les injecter dans l’étage suivant [YJ03].

La complexité matérielle du coprocesseur FFT de radix- $r$  MDC, avec  $r$  la valeur du radix, peut être réduite en utilisant d’autres algorithmes comme le Mixed-radix plus et le Split-radix [ES84] [SL07].

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L’ART

---

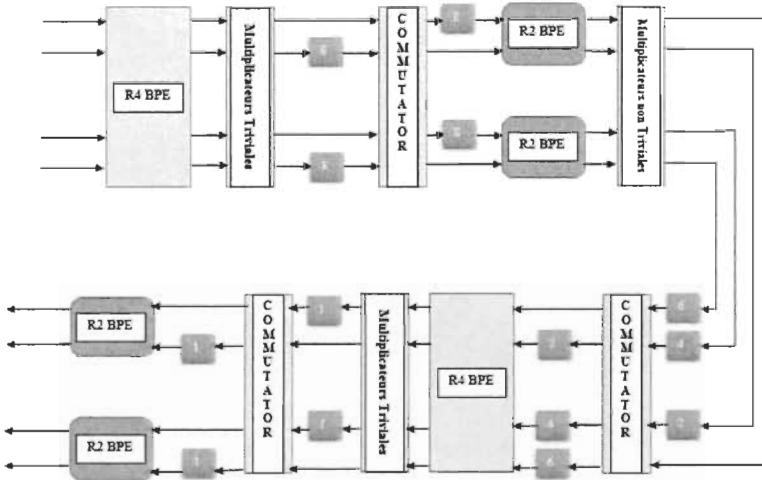

*Figure 14 Architecture MC-MRMDC ( $k = 4$ ,  $N = 64$  points)*

La figure 14 représente l’architecture MC-MRMDC (*Multi Channel - Mixed Radix Multipath Delay Commutator*) présentée dans [SL07] pour  $N = 64$  points et  $k = 4$ , où  $k$  est le nombre de canaux. Cette architecture, utilisant l’algorithme Mixed radix, permet de diminuer le nombre des ressources utilisées en diminuant le nombre de multiplications non-triviales.

En comparant les deux coprocesseurs radix-4 MDC et MC-MRMDC, on peut remarquer que le premier illustré dans la figure 13 utilise 6 multiplications non-triviales tandis que le deuxième illustré dans la figure 14 n’utilise que 4 multiplications non-triviales, [SL07].

Le tableau 3 contient une comparaison des exigences matérielles de plusieurs architectures FFT pipelines y compris le radix-2 2SDF, le radix-2<sup>3</sup> SDF et le MRMDC. La constante T désigne le nombre des additionneurs requis pour implémenter une multiplication triviale.

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L'ART

---

*Tableau 3 Comparaison en termes d'exigences matérielles entre différentes architectures FFT pipelines [SL07].*

|                          | Nombre de Processeurs (P) | Multiplieurs complexes/P | Additionneurs complexes/P | Taille Mémoire/P | Contrôle |

|--------------------------|---------------------------|--------------------------|---------------------------|------------------|----------|

| Radix2-SDF               | k                         | $\log_2 N - 1$           | $2\log_2 N$               | N-1              | Simple   |

| Radix4-SDF               | k                         | $\log_4 N - 1$           | $8\log_4 N$               | N-1              | Moyen    |

| Radix4-SDC               | k                         | $\log_4 N - 1$           | $3\log_4 N$               | 2N-2             | Complex  |

| Radix2 <sup>2</sup> -SDF | k                         | $\log_2 N - 1$           | $4\log_4 N$               | N-1              | Simple   |

| Radix2 <sup>3</sup> -SDF | k                         | $2(\log_8 N - 1)$        | $(62T)\log_8 N$           | N-1              | Moyen    |

| Radix2-MDC               | k/2                       | $\log_2 N - 2$           | $2\log_2 N$               | 3N/2-2           | Simple   |

| Radix4- MDC              | k/4                       | $3(\log_4 N - 1)$        | $8\log_4 N$               | 5N/2-4           | Simple   |

| MRMDC                    | k/4                       | $4(\log_8 N - 1)$        | $(12+3T)\log_8 N$         | 5N/2-4           | Simple   |

D'après le tableau 3, pour  $k = 4$  et  $N = 64$ , l'architecture MC-MRMDC sauve 2 multiplications non-triviales comparant à l'architecture radix-4 MDC et 76 additionneurs complexes comparant à l'architecture radix-2<sup>3</sup> SDF. On constate donc, qu'en utilisant l'architecture pipeline MDC, on utilise moins de processeurs. À titre d'exemple ; pour implémenter un système à 4 canaux ; on aura besoin de 4 processeurs utilisant l'architecture pipeline SDF au lieu d'un seul processeur utilisant l'architecture MDC. On réalise ainsi un grand gain en termes de ressources matérielles. Ce qui constitue la raison que la plupart des implémentations VLSI des coprocesseurs FFT tendent à utiliser l'architecture pipeline MDC. [SL07].

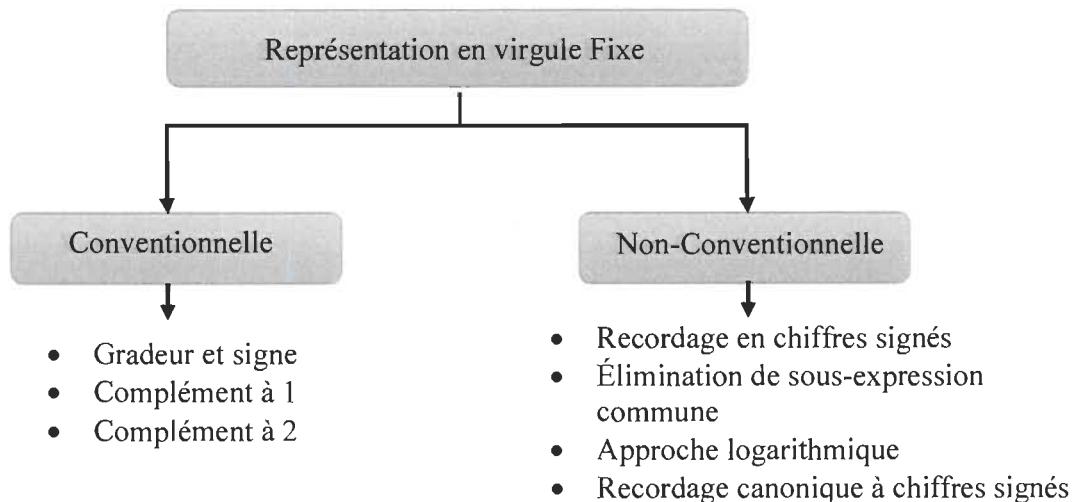

### 2.5 Effet de Quantification

Les unités de calcul en virgule flottante sont des unités trop complexes et présente un coût matériel trop important. Pour cette raison, le calcul est réalisé généralement avec des nombres représentés en virgule fixe afin de satisfaire les coûts en VLSI pour les implémentations FPGA. La figure 15 résume quelques méthodes de représentations en virgule fixe.

Généralement, l'arithmétique en virgule fixe est préférée pour les applications de DSP grâce à leurs avantages en termes de consommation d'énergie, de surface et de latence.

De plus, toutes ces performances dépendent de la représentation en virgule fixe utilisée, ainsi, un choix judicieux de la largeur binaire dans la conception FPGA peut entraîner des économies substantielles.

Figure 15 Quelques méthodes de représentations en virgule fixe

### 2.5.1 *Erreur de quantification*

Lorsqu'une FFT est effectuée en arithmétique à virgule fixe, des erreurs de quantification interviennent, liées à la longueur certainement finie des valeurs numériques codées à l'intérieur de la machine sous la forme de mots binaires. Elles impliquent une incertitude sur le résultat qui est ainsi affecté des sources de bruits.

Nous pouvons distinguer trois sources d'erreurs de quantification initiales selon [KM91] :

- L'erreur de quantification due au signal d'entrée liée à la résolution du convertisseur analogique-numérique.

- L'erreur de quantification due aux facteurs de Fourier  $W$  de la FFT.

- L'erreur de quantification dans les unités de calculs ; après multiplications et/ou les additions.

Ces trois types d'erreurs se propagent de l'entrée vers la sortie au sein du système et modifient la précision des calculs en sortie de l'application. Dans de nombreux cas, il est raisonnable de traiter les effets de troncatures et d'arrondis par un modèle statistique remplaçant chaque source d'erreur par un bruit blanc.

## 2.6 Différentes approches d'implémentation de la FFT

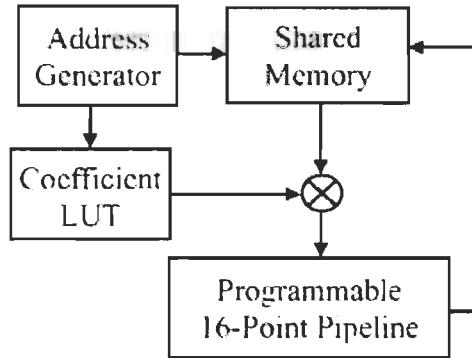

### 2.6.1 *Processeur FFT pipeliné localement*

L'architecture pipeline est largement utilisée dans de nombreuses applications [SS96], [TM92] à haut débit, mais pour le processeur FFT dans les applications embarquées en temps réel, un long pipeline consomme trop de silicium, d'où l'architecture [LH99] composée d'un

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L'ART

---

pipeline court et d'une mémoire partagée est plus adaptée. Cette structure nommée le processeur pipeliné localement (*Locally Pipelined Processor : LPPL*) ressemble à une architecture à radix élevé et à mémoire partagée (*High-Radix and Shared Memory Architecture : HRSMA*), mais différemment a l'HRSMA générale, son BPE à haute radix est implémentée avec un BPE à faible radix pipeliné ; par conséquent, il peut être réalisé avec un nombre de ressources matérielles acceptable et un débit élevé.

Comme le montre la figure 16, le BPE pipeliné et le générateur d'adresses à la mémoire partagée sont deux des éléments de base du processeur LPPL. Dans la conception d'architecture de pipeline [SS96], [EH84] - [SW01], l'architecture radix-4 tend à réduire les multiplicateurs à 50% par rapport à celle de radix-2, mais le nombre d'additionneurs qui augmente à 400% dans les BPE radix4 classiques (BPE4) fait disparaître cet avantage. Dans le radix-2 Single Deep Delay Feedback (R2SD2F), le BPE4 est formé par deux BPE radix-2 en cascade (BPE2), ce qui diminue l'utilisation des additionneurs par 50%, mais double l'utilisation de BPE de 25% à 50% avec maintenir le même nombre de multiplicateurs et registres comme le radix-4 Single-Path Delay Feedback (R4SDF [AM74]). Dans une autre approche, le radix-4 Single-Path Delay Commutator (R4SDC) proposé par [GA89] a réduit le nombre d'additionneurs contenus dans BPE4 de 8 à 3, mais a doublé les ressources utilisées pour les registres.

Pour la génération d'adresse, la méthode la plus populaire et la plus efficace sur le plan de la génération d'adresses de coefficients a été proposée par Cohen [DC76]. Selon cette méthode et d'autres approches similaires [YM99], [YM20], la génération d'adresse se produit par l'application de différents shifts pour traiter les lignes d'adresses, ce qui

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L’ART

correspond très bien à la caractéristique « *Frequent Coefficient Accessing* » et réduit également le temps d'accès pour obtenir les coefficients.

Figure 16 Architecture radix-16 LPPL [GA89]

Mais ce type d'algorithme a besoin de  $M-1$  ( $M=\log_2 N$ ) cycles pour calculer l'adresse de l'opérande, la latence est alors trop longue. Ma [YM94] et Luo [WZ94] ont fourni différents algorithmes de génération d'adresse rapide. Cependant, Ma [YM94] et Luo [WZ94] n'ont pas considéré la redondance de l'accès aux coefficients ce qui augmente notablement la consommation d'énergie de l'accès mémoire.

Figure 17 Architecture R2SD2F pipeliné pour DFT à 16 points [GA89]

Une autre approche appliquée au R2SD2F pipeliné pour LPPL est aussi proposée par mettre en cascade deux « “deep” feedback butterflies ». Dans une telle architecture, un pipeline de longueur 16 comprend quatre additionneurs et un multiplicateur. Les exigences des

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L’ART

opérateurs sont minimales par rapport aux autres modèles de pipelines, et l’efficacité de la performance du module de traitement peut atteindre jusqu’à 100%.

### 2.6.2 Processeur FFT pour les applications WPAN à base de OFDM

Une parmi les différentes approches pour implémenter la FFT consiste à concevoir un processeur de transformée de Fourier rapide (FFT) qui fournit un débit de débit élevé (*High Throughput Rate (TR)*) en appliquant l’approche pipeline de huit voies pour les applications de réseau sans fil (*Eight-data-Path Pipelined Approach for Wireless Aersonal Area Network*). Au cours de ces dernières années, des efforts ont été réalisés dans les applications WPAN (*Wireless Personal Area Network*) pour supporter une transmission élevée des données dans un environnement intérieur à courte distance (*Short Range Indoor Environment*).

Dans les développements précédents, la technologie « *Ultra Wide Band* » (UWB) a permis de fournir des débits de données allant jusqu’à 480 Mb/s. Cela signifie que le processeur FFT pour les systèmes WPAN avancés devrait fournir un TR élevé d’un minimum de 2.304 GS/s.

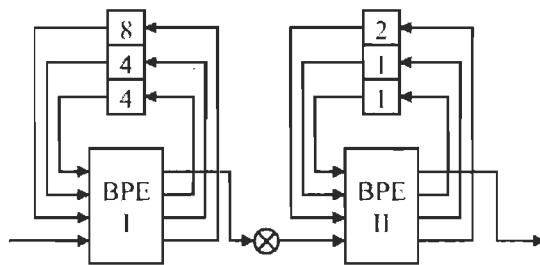

Figure 18 Diagramme Block d'un 2048-FFT processeur [SN10]

Pour cette raison, un processeur FFT de 2048 points basés sur l’approche « *Eight-Data-Path Pipelined Approach* » avec une méthode de réduction de ressources qui peut fournir un T.R élevé a été conçu pour atteindre 2,4 GS/s et un SQNR de 32,8 dB pour les applications

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L'ART

16-QAM (*16 Quadratic-Amplitude Modulation*).

Comme Montré à la figure 18. Il existe quatre modules basés sur l'algorithme radix- $2^4$  qui réduit le nombre de multiplications non triviales [MS08], [JY05]. Les données sont traitées en fonction de huit chemins de données avec un exposant partagé attribué à un groupe de huit valeurs de mantisse. Les détails de chaque module sont décrits comme suit.

### A. Module 1

Comme représenté sur la figure 19 le module 1 a une structure radix- $2^4$  avec quatre opérations de radix-2 divisées sur 4 étapes. Les données de la mantisse sont exploitées par une représentante Butterfly radix-2, il existe quatre unités BF2 à huit données et quatre FIFO à huit banques avec des tailles de mots de 1024, 512, 256 et 128, respectivement. L'unité BF2 effectue une addition et une soustraction de l'entrée pour l'opération radix-2 ou bypass huit chemins de données, et l'exposant est exploité par une seule donnée chemin. Le BF2 l'entrée pour les opérations d'entrée / sortie.

Figure 19 Structure du module 1 [SN10]

### B. Module 2

La structure du module 2 est similaire à celle du module 1 sauf que les tailles de données FIFO sont 64, 32, 16 et 8 mots, respectivement, pour les quatre étapes. En outre, la

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L'ART

---

multiplication au dernier stade est complétée par une unité de multiplication constante (Module 3) au lieu de huit multiplicateurs complexes généraux.

### C. Module 3

Les huit valeurs de données de sortie du module 2 doivent être simultanément multipliées par les TWF non triviales dans le module 3. Certains schémas de simplification ont été présentés en [YW05] et [KM04] en utilisant des nombres de multiplicateurs constants au lieu de multiplicateurs complexes.

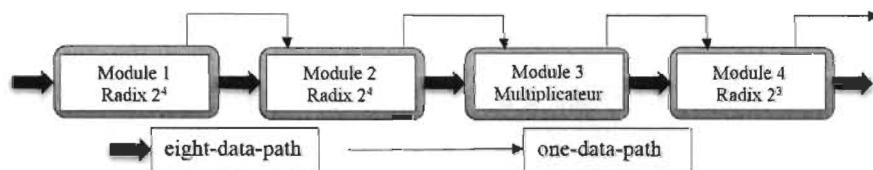

### D. Module 4

La phase finale pour l'opération radix- $2^3$  est réalisée dans le module 4, comme l'illustre la figure 20, c'est une mise en œuvre directe basé sur l'organigramme du signal radix- $2^3$  avec 24 additionneurs complexes et deux multiplicateurs constants pour les TWF triviaux.

Figure 20 Diagramme Block du module 4 [SN10]

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L’ART

---

### 2.6.3 Radix- $2^4$ FFT à haute performance pour les applications MIMO-OFDM

Orthogonal Frequency Division Multiplexing (OFDM) est une méthode de modulation connue pour sa capacité à atteindre une efficacité élevée et à faire face à la « *frequency selective fading and narrowband interference* ». [KM04]

Ainsi, un schéma de processeur FFT / IFFT à faible vitesse peut réduire la complexité des systèmes MIMO-OFDM [GL04] [DB04]. Et, puisque le taux de transmission de données des systèmes MIMO-OFDM ne cesse à augmenter, générer des symboles OFDM avec un débit élevé nécessite un algorithme et une architecture FFT à haute efficacité. [HL08]

L'algorithme radix- $2^4$  est décrit en détail dans [CC92]. L'algorithme peut prendre un multiplicateur complexe constant au lieu du multiplicateur complexe programmable.

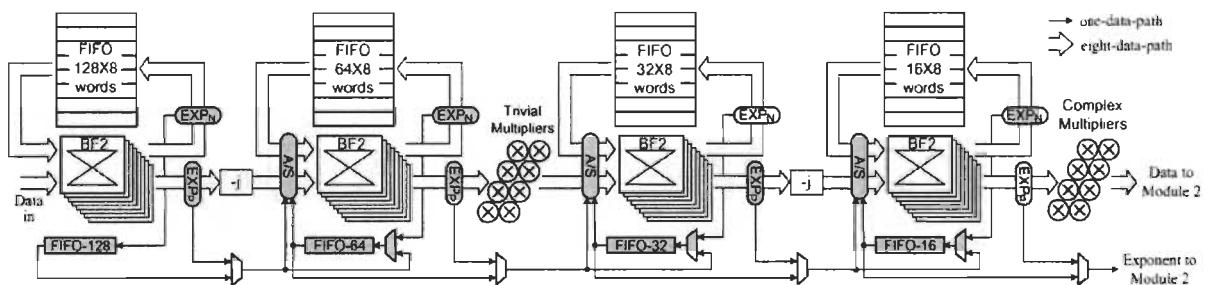

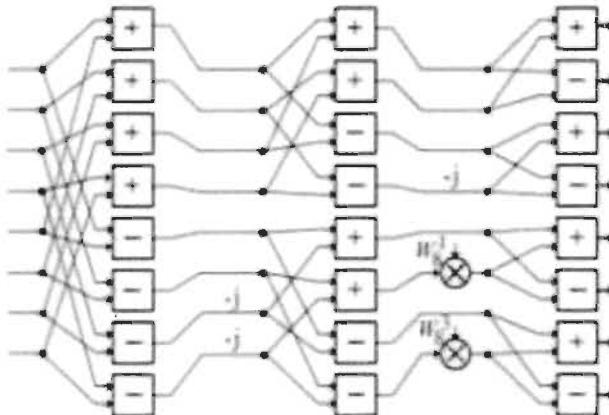

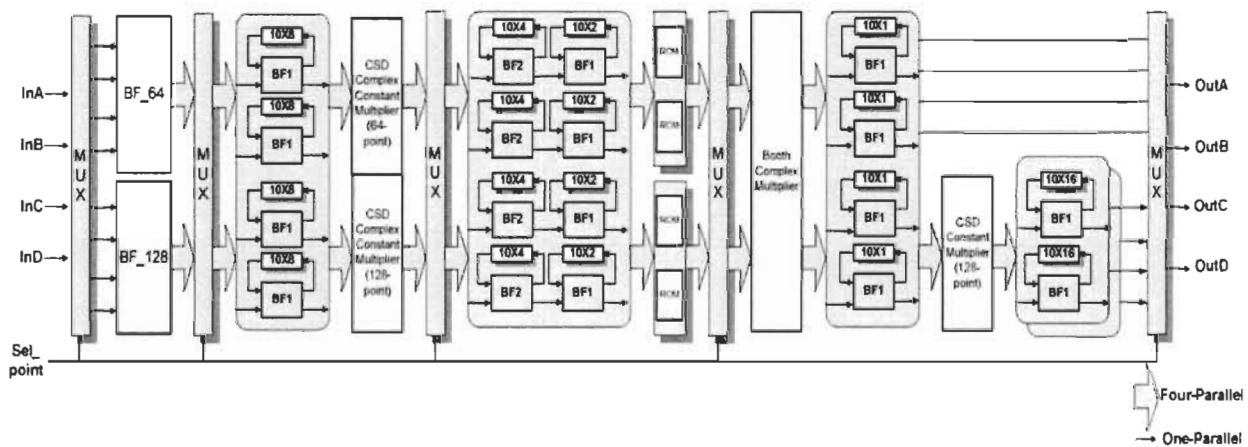

La figure 21 montre l'architecture du processeur R2 $^4$ MDF FFT / IFFT proposé avec quatre chemins de données parallèles à 128/64 points. La conception proposée peut soutenir l'opération de FFT / IFFT dans 128 points ou 64 points. Il se compose d'unités de mémoire, d'unités de Butterfly appelées BF\_64, BF\_128, BF1, BF2, de multiplicateurs de nombres complexes, multiplicateurs constants, multiplexeurs et additionneurs constants. [HL08]

L'architecture ‘4-parallel data-path’ présentée dans la figure 21 demande aussi quatre entrées et sorties qui exploitent séparément les données réelles et imaginaires. L’unité de Butterfly est le noyau de ce processeur FFT. Dans chaque Butterfly, deux types d’unités ont été conçus pour réaliser la multiplication par ‘j’. Le BF1 stocke toutes les  $(N / 2)^{\text{ème}}$  données d’entrée dans RAM. Pendant ce temps, la RAM maintient l'espace de mémoire tampon pour les données d’entrée suivantes. Le BF2 est identique à l’architecture BF1 sauf l’opération de  $(3N / 4)^{\text{ème}}$  données d’entrée multipliées par -j. [HL08]

## CHAPITRE II – IMPLÉMENTATION DE LA FFT – ÉTAT DE L'ART

Cette architecture proposée nous permet de traiter des données à grande vitesse avec une faible complexité matérielle grâce à l'application d'un multiplicateur à largeur fixe, qui maintient l'entrée et la sortie à une largeur de 10 bits à 30dB SQNR. En outre, le nombre de multiplicateurs complexes et des mémoires sont effectivement réduits en utilisant l'algorithme radix-2<sup>4</sup> MDF FFT.

Les résultats de performance montrent que la fréquence de traitement des données est aussi élevée que 560 Msample/s avec une petite augmentation en complexité matérielle. [HL08]

Figure 21 4-parallel data-path d'un processeur radix-2<sup>4</sup> MDF FFT/IFFT à 128/64-points [HL08]

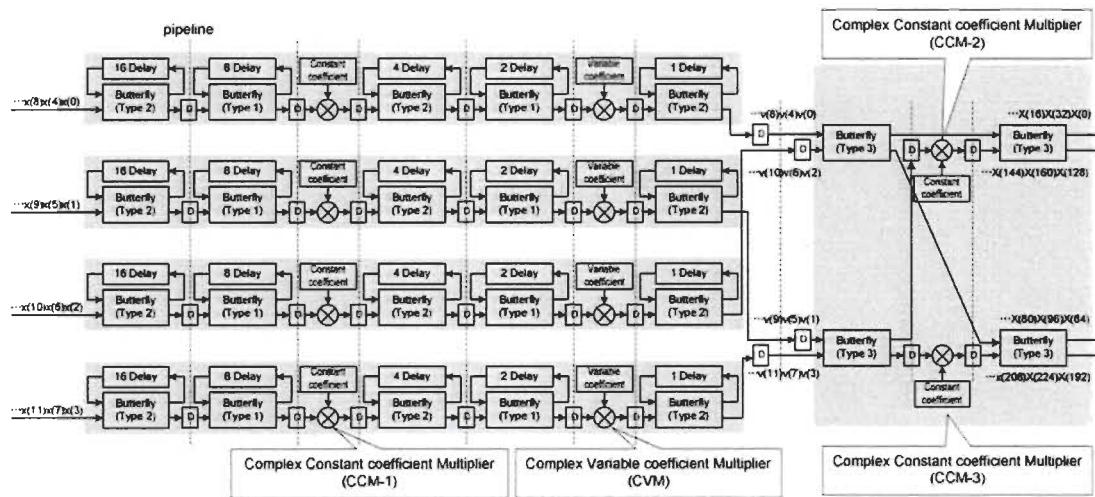

### 2.6.4 Processeur FFT pour les systèmes UWB

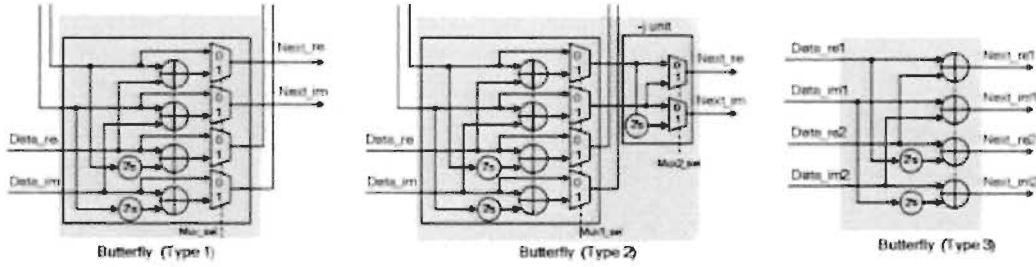

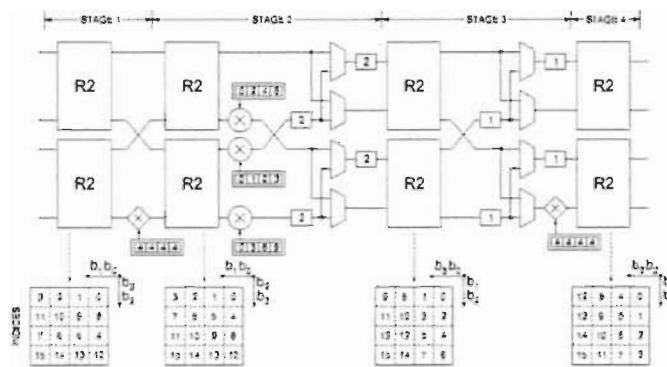

Dans les systèmes Multi-Band Orthogonal Frequency Division Multiplexing (MB-OFDM), l'horloge d'échantillonnage dans les convertisseurs analogiques-numériques (A/D) est de 528 MHz, ce qui est trop élevé pour concevoir le récepteur en utilisant les technologies de processus CMOS actuelles. Dans ce cas, une structure réceptrice parallèle y compris un bloc