UNIVERSITÉ DU QUÉBEC

MÉMOIRE PRÉSENTÉ À

L'UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

COMME EXIGENCE PARTIELLE

DE LA MAÎTRISE EN GÉNIE ÉLECTRIQUE

PAR

ISSAM SOUSSI

CONCEPTION D'UNE CHAINE EN BANDE DE BASE RECONFIGURABLE POUR

LE PROTOCOLE DE COMMUNICATION ZIGBEE

OCTOBRE 2015

Université du Québec à Trois-Rivières

Service de la bibliothèque

Avertissement

L'auteur de ce mémoire ou de cette thèse a autorisé l'Université du Québec à Trois-Rivières à diffuser, à des fins non lucratives, une copie de son mémoire ou de sa thèse.

Cette diffusion n'entraîne pas une renonciation de la part de l'auteur à ses droits de propriété intellectuelle, incluant le droit d'auteur, sur ce mémoire ou cette thèse. Notamment, la reproduction ou la publication de la totalité ou d'une partie importante de ce mémoire ou de cette thèse requiert son autorisation.

## Résumé

ZigBee est désormais la norme dominante pour les réseaux personnels sans fil et à faible vitesse à courte portée (LR-WPAN) et elle a de nombreuses applications dans le domaine de l'automatisation et l'automatisation industrielle.

La couche physique de ce protocole de communication sans fil comporte une chaîne en bande de base figée. Ce projet présente un modèle VHDL synthétisable d'un émetteur/récepteur en bande de base numérique (couche physique) tel que décrit dans la norme IEEE 802.15.4. Il est implémenté dans un circuit programmable FPGA et il est validé à travers une panoplie des tests réels.

L'émetteur/récepteur est capable de travailler avec : n'importe quel taux d'échantillonnage, différents taux de transmission, les deux bandes 915MHz ou 2.45 GHz, deux modulations possibles (QPSK et O-QPSK), et aussi nous pouvons jouer sur le nombre de bits de deux sorties pour l'adapter à la résolution du convertisseur numérique-analogique. La transmission d'une trame PPDU est gérée par un contrôleur suivant les modes suivants : arrêt, boucle, émission et réception. L'émetteur/récepteur est contrôlé par une interface graphique développée sur un ordinateur.

## Remerciements

Tout d'abord, je tiens à remercier mon directeur de recherche Mr Frédéric DOMINGUE et mon co-directeur Mr Adel Omar DAHMANE pour leurs aides et de la patience d'avoir dirigé mon mémoire mais aussi de m'avoir accueilli au sein de leurs laboratoire respectif et de m'avoir conseillé et épaulé durant ces trois années de maîtrise.

Je remercie les évaluateurs d'avoir bien voulu accepter la charge d'évaluateurs ainsi de juger ce mémoire.

Je tiens à remercier toute l'équipe du centre collégial de recherche et développement C2T3 pour me permettre d'utiliser les ressources matérielles du laboratoire RF.

Je voudrais profiter pour exprimer ma gratitude à tous ceux qui ont contribué à travers ces soutiens favorables pour faire ce modeste travail et aussi qui m'ont permis de bien rester sur la bonne voie tout au long de ce projet.

Je remercie aussi les professeurs de cours de l'Université pour l'excellente formation que j'ai acquis durant toute ma maîtrise à travers les travaux individuels et les projets de session.

Je tiens à remercier toute ma famille et ma femme pour leurs encouragements et leurs soutiens durant mes études.

## Table des matières

|                                                        |      |

|--------------------------------------------------------|------|

| Résumé .....                                           | ii   |

| Remerciements .....                                    | iii  |

| Table des matières .....                               | iv   |

| Liste des tableaux .....                               | viii |

| Liste des figures .....                                | ix   |

| Liste des symboles .....                               | xii  |

| Chapitre 1 - Introduction .....                        | 1    |

| 1.1 Les réseaux de capteurs sans fils .....            | 1    |

| 1.2 Le standard IEEE 802.15.4 .....                    | 2    |

| 1.3 Le protocole de communication ZigBee .....         | 3    |

| 1.4 Problématique .....                                | 5    |

| 1.5 Objectifs spécifiques .....                        | 6    |

| 1.6 Méthodologie .....                                 | 7    |

| 1.7 Organisation du mémoire .....                      | 8    |

| Chapitre 2 - La couche physique de IEEE 802.15.4 ..... | 9    |

| 2.1 Introduction .....                                 | 9    |

|                                                                                    |    |

|------------------------------------------------------------------------------------|----|

| 2.2 La composition de la couche physique pour la norme IEEE 802.15.4.....          | 9  |

| 2.2.1 La trame des données PPDU.....                                               | 10 |

| 2.2.2 La technique d'étalement du spectre par DSSS.....                            | 12 |

| 2.2.3 La modulation QPSK versus O-QPSK .....                                       | 15 |

| 2.2.4 Estimation de la fréquence et correction de la phase dans le récepteur ..... | 17 |

| 2.2.5 L'indicateur de puissance du signal reçu (RSSI) .....                        | 20 |

| 2.3 Les architectures spécifiées par la norme .....                                | 21 |

| 2.3.1 L'architecture de la chaîne en bande de base pour la bande 2.45 GHz .....    | 21 |

| 2.3.2 L'architecture de la chaîne en bande de base pour la bande 915 MHz.....      | 27 |

| 2.4 La reconfiguration par le circuit programmable FPGA .....                      | 29 |

| 2.5 Conclusion.....                                                                | 33 |

| Chapitre 3 - Chaîne de communication proposée .....                                | 34 |

| 3.1 Introduction .....                                                             | 34 |

| 3.2 La composition de la chaîne proposée.....                                      | 34 |

| 3.2.1 Le premier travail à faire.....                                              | 35 |

| 3.2.2 Le deuxième travail à faire.....                                             | 40 |

| 3.2.3 Le troisième travail à faire .....                                           | 42 |

| 3.3 Le flot de conception .....                                                    | 48 |

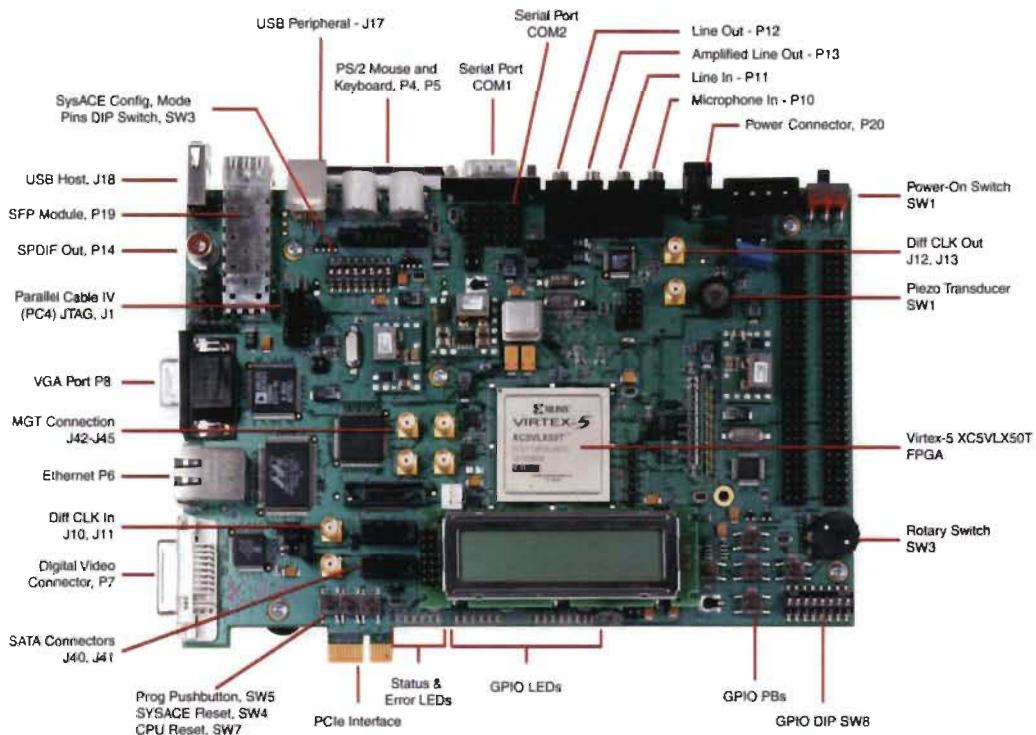

| 3.4 Le choix du matériel .....                                                     | 49 |

|                                                                                      |    |

|--------------------------------------------------------------------------------------|----|

| 3.5 Les tests réels à faire.....                                                     | 51 |

| 3.6 Conclusion.....                                                                  | 54 |

| Chapitre 4 - Résultats de simulation et de test .....                                | 55 |

| 4.1 Introduction .....                                                               | 55 |

| 4.2 Conception d'un émetteur en bande de base .....                                  | 55 |

| 4.2.1 Emetteur en bande de base sans diviseur d'horloge .....                        | 55 |

| 4.2.2 Emetteur en bande de base avec diviseur d'horloge .....                        | 57 |

| 4.3 Conception d'un émetteur / récepteur en bande de base .....                      | 62 |

| 4.3.1 Émetteur-récepteur sans connexion de deux chaînes.....                         | 62 |

| 4.3.2 Avec connexion de deux chaînes et avec le diviseur d'horloge .....             | 64 |

| 4.3.3 Emetteur / récepteur en bande de base à double bande.....                      | 69 |

| 4.4 Test de la boucle de retour pour l'application .....                             | 73 |

| 4.4.1 Le module adaptation de 4bits à 8bits.....                                     | 73 |

| 4.4.2 Test de la boucle de retour avec l'interface graphique .....                   | 74 |

| 4.5 La chaîne d'émission sur l'oscilloscope avec le contrôle par l'application ..... | 76 |

| 4.6 Test de la boucle de retour de la chaîne d'émission / réception .....            | 80 |

| 4.7 Banc de test global.....                                                         | 82 |

| 4.8 Test d'envoi d'une trame PPDU.....                                               | 87 |

| 4.8.1 Test de la chaine d'émission .....                                             | 87 |

|                                                           |     |

|-----------------------------------------------------------|-----|

| 4.8.2 Test de la trame sur l'émetteur / récepteur.....    | 91  |

| 4.9 Conclusion.....                                       | 93  |

| Chapitre 5 - Conclusion .....                             | 94  |

| Références.....                                           | 96  |

| Annexe A – L'algorithme de Kay et le module CORDIC .....  | 98  |

| Annexe B –Description des blocs internes.....             | 104 |

| Annexe C – Le matériel utilisé.....                       | 121 |

| Annexe D – Autres résultats de simulation et de test..... | 125 |

## Liste des tableaux

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| Tableau 1-1 : Bandes spécifiées par la norme IEEE 802.15.4 (adaptée de [1]).....    | 4  |

| Tableau 2-1 : La trame PPDU de la couche physique (adapté de [9]) .....             | 11 |

| Tableau 2-2 : Pour la bande 2.45 GHz utilisant O-QPSK (adapté de [1] et [9]) .....  | 12 |

| Tableau 2-3 : Pour les bandes 868/915 MHz avec O-QPSK (adaptée de [1] et [9]) ..... | 14 |

| Tableau 2-4 : Pour les bandes 868/915 MHz avec BPSK (adaptée de [1] et [9]).....    | 28 |

| Tableau 4-1 : Ressources occupées de l'émetteur.....                                | 56 |

| Tableau 4-2 : Ressources occupées de l'émetteur avec le diviseur .....              | 58 |

| Tableau 4-3 : Les ports à détecter pour l'émetteur avec diviseur .....              | 59 |

| Tableau 4-4 : Ressources occupées de l'émetteur / récepteur.....                    | 63 |

| Tableau 4-5 : Test des ports sur la carte.....                                      | 66 |

| Tableau 4-6 : Ressources occupées de l'E/R avec connexion et avec diviseur .....    | 66 |

| Tableau 4-7 : Les ports à détecter pour l'E/R avec diviseur .....                   | 67 |

| Tableau 4-8 : Ressources occupées de deux E/R avec sélection de la bande .....      | 71 |

| Tableau 4-9 Ressources occupées par le module de test.....                          | 76 |

| Tableau 4-10 : Ressources occupées par l'architecture .....                         | 80 |

## Liste des figures

|                                                                                           |    |

|-------------------------------------------------------------------------------------------|----|

| Figure 1.1 : Le modèle en couche (adaptée de [1]).....                                    | 2  |

| Figure 1.2 : L'acheminement du flux de données (adapté de [1]) .....                      | 5  |

| Figure 2.1 : Effet d'étalement avec DSSS (adaptée de [9]) .....                           | 13 |

| Figure 2.2 : Les changements de phase dans QPSK et O-QPSK (adaptée de [17]) .....         | 16 |

| Figure 2.3 : Résultat de la modulation du symbole zéro (adaptée de [13]) .....            | 17 |

| Figure 2.4 : Esquisse d'estimation et de correction de phase .....                        | 18 |

| Figure 2.5 : L'architecture pour la bande 2.45 GHz (adaptée de [12]).....                 | 21 |

| Figure 2.6 : La modulation O-QPSK (adaptée de [9] et [12]) .....                          | 23 |

| Figure 2.7 : Le filtrage de formation d'impulsion (adaptée de [9]) .....                  | 24 |

| Figure 2.8 : Le filtrage numérique (adaptée de [14]) .....                                | 24 |

| Figure 2.9 : L'architecture pour la bande 915 MHz (adaptée de [10]) .....                 | 27 |

| Figure 2.10 : La modulation BPSK.....                                                     | 28 |

| Figure 2.11 : Les tâches des applications en communication (adaptée de [9], [10] et [11]) | 29 |

| Figure 3.1 : L'architecture complète à implémenter (adaptée de [8] et [9]) .....          | 36 |

| Figure 3.2 Schéma global en émission.....                                                 | 37 |

| Figure 3.3 : Le corrélateur de réception (adaptée de [16]).....                           | 39 |

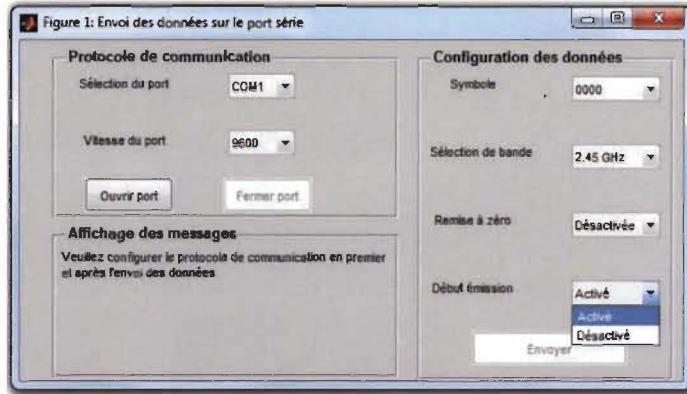

| Figure 3.4 : L'application développée sous GUIDE .....                                    | 41 |

| Figure 3.5 : La deuxième application développée sous GUIDE .....                          | 42 |

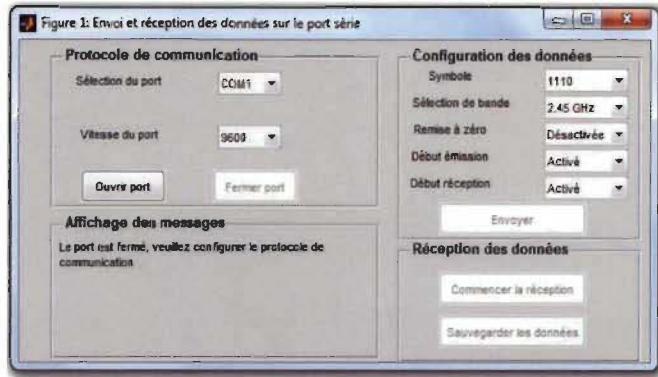

| Figure 3.6 : Le contrôl de l'émission et réception .....                                  | 43 |

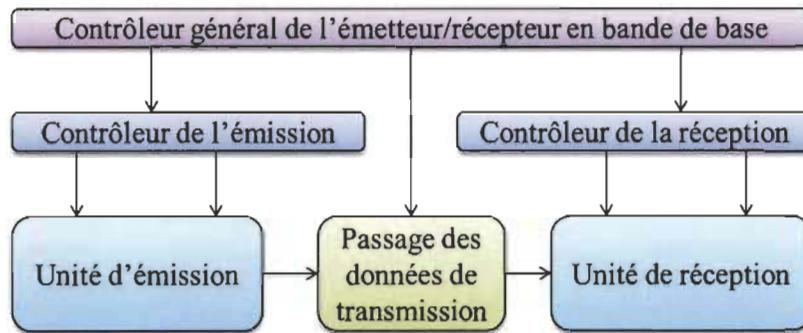

| Figure 3.7 : La machine à état finie du contrôleur général .....                          | 44 |

|                                                                                       |    |

|---------------------------------------------------------------------------------------|----|

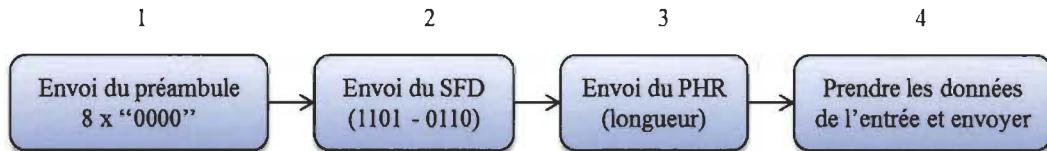

| Figure 3.8 : Les étapes du contrôleur de l'émission.....                              | 45 |

| Figure 3.9 : L'organigramme du contrôleur de réception .....                          | 45 |

| Figure 3.10 : Premier essai avec l'analyseur logique.....                             | 51 |

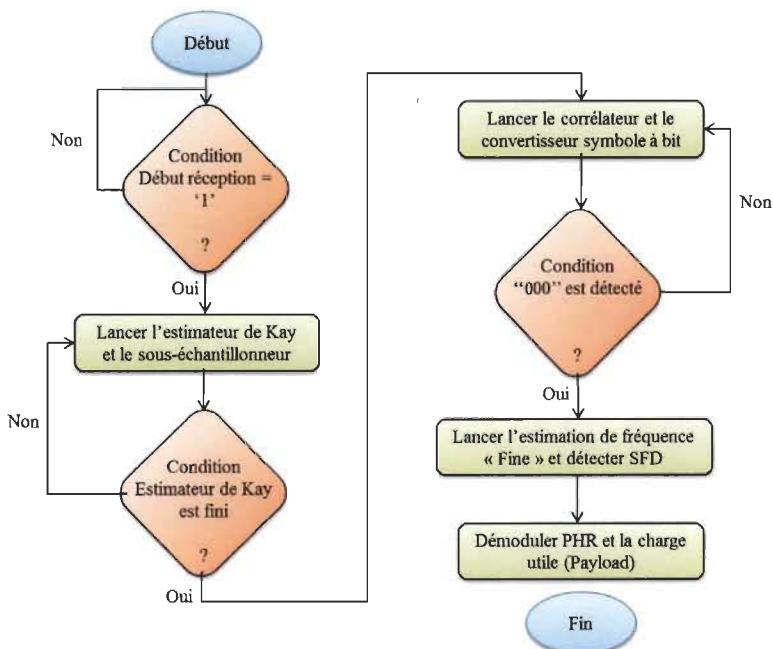

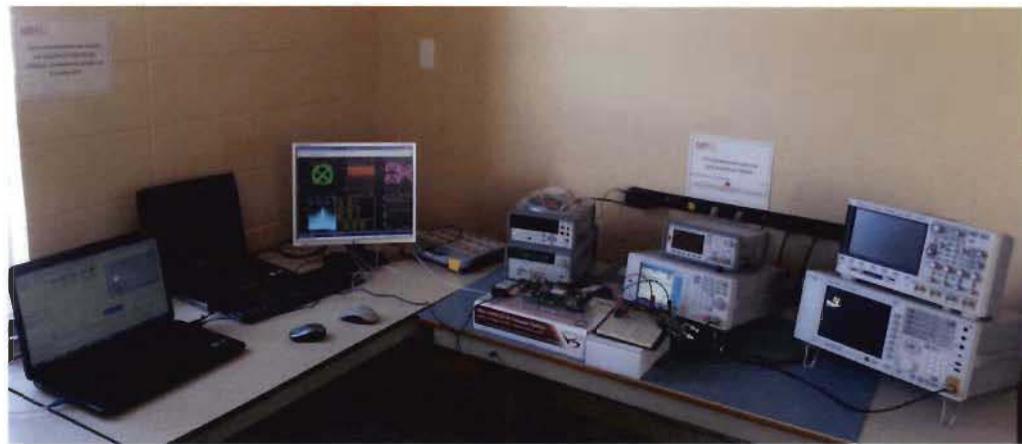

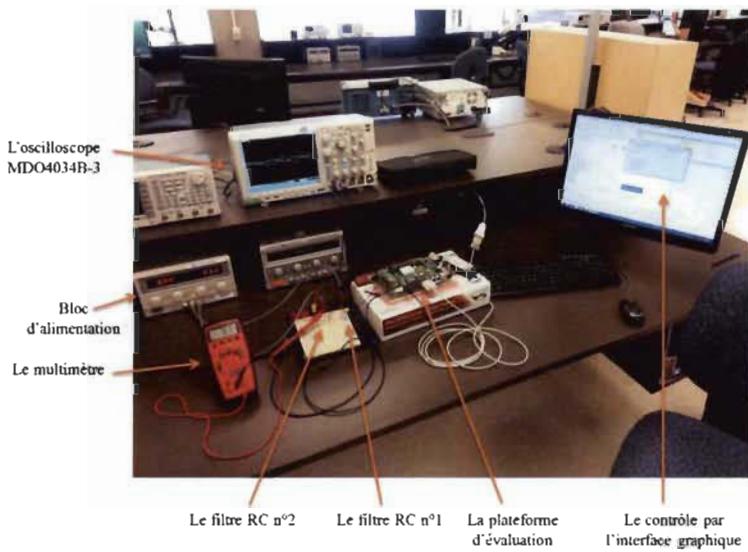

| Figure 3.11 : Banc de test global.....                                                | 52 |

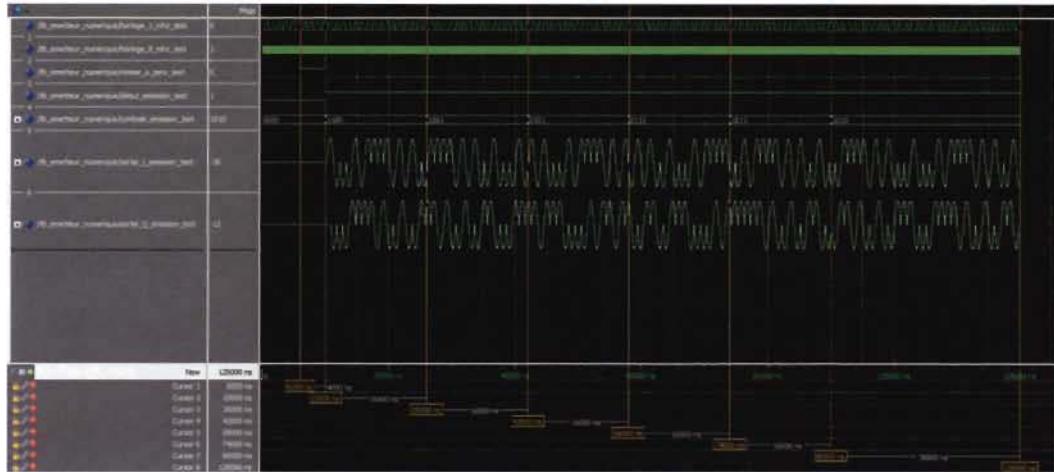

| Figure 4.1 : Simulation de l'émetteur sous ModelSim .....                             | 56 |

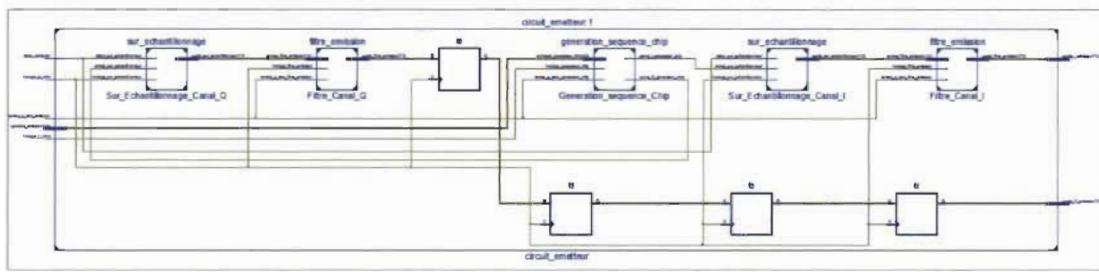

| Figure 4.2 : Le schématique de l'émetteur en bande de base.....                       | 57 |

| Figure 4.3 : Simulation de l'émetteur avec diviseur sous ModelSim .....               | 58 |

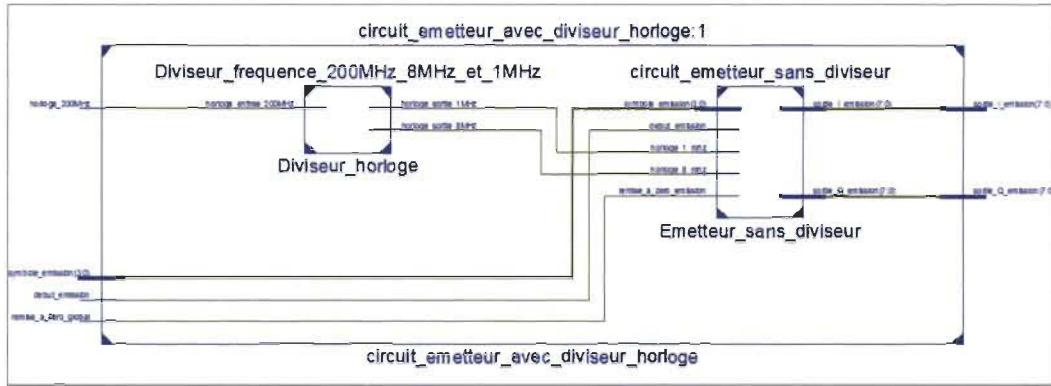

| Figure 4.4 : Le schématique de l'émetteur avec le diviseur.....                       | 59 |

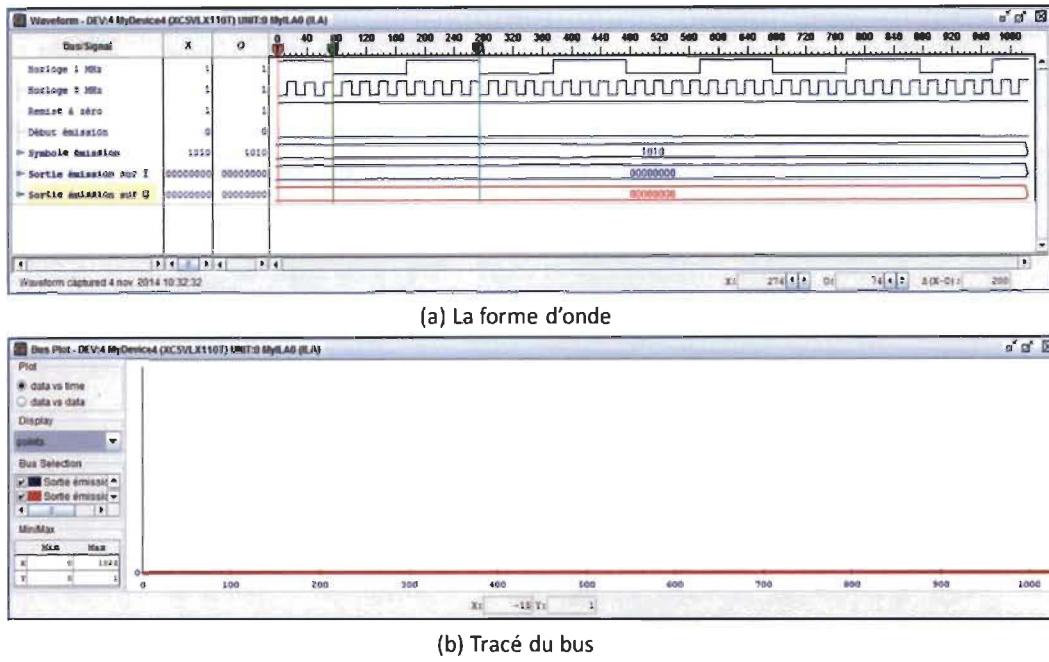

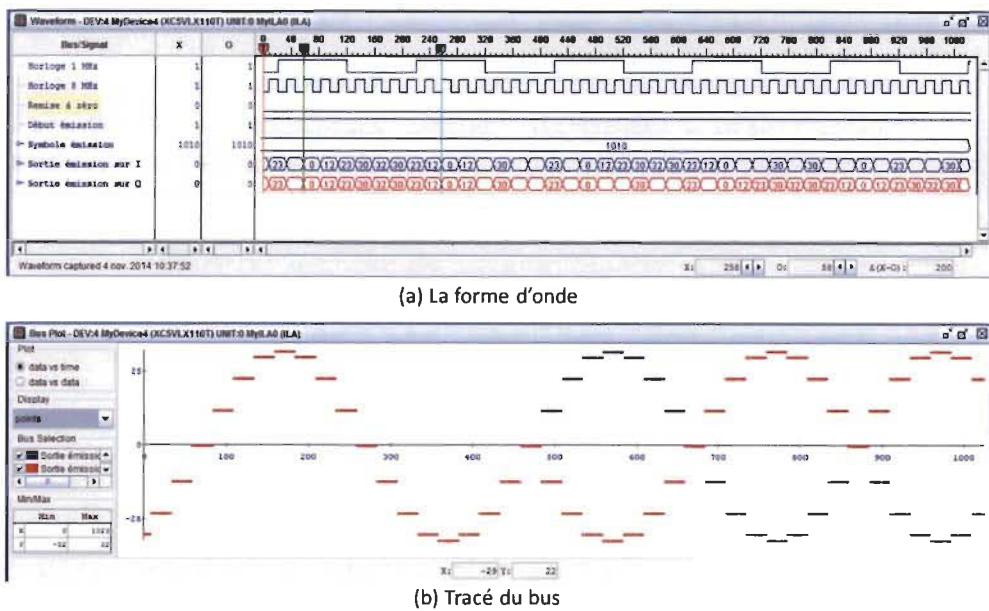

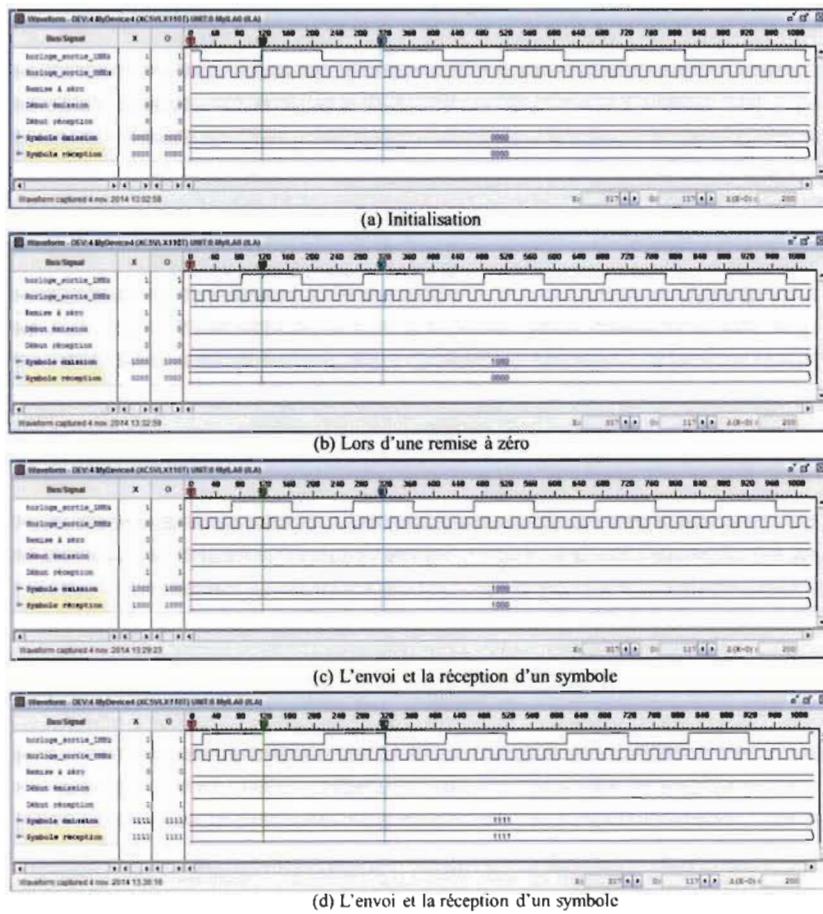

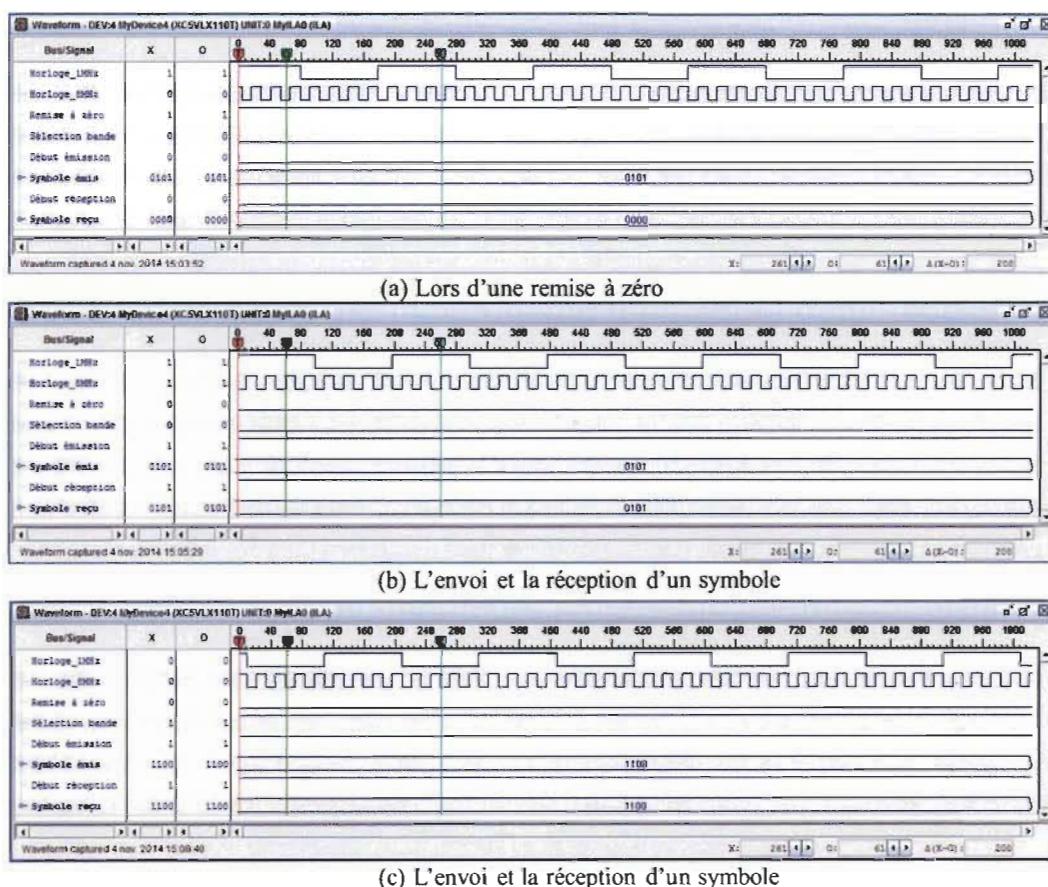

| Figure 4.5 : Lors d'une remise à zéro .....                                           | 60 |

| Figure 4.6 : Lors de l'envoi d'un symbole.....                                        | 60 |

| Figure 4.7 : Test d'envoi de la donnée.....                                           | 61 |

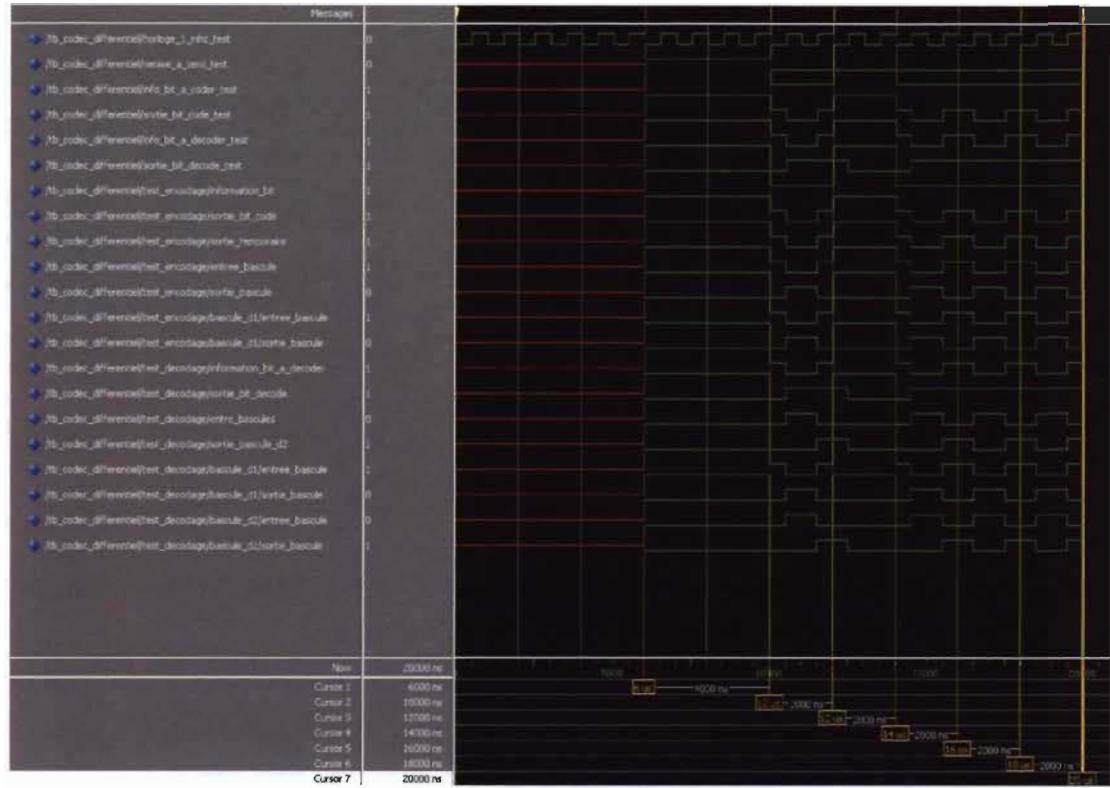

| Figure 4.8 : Simulation de l'émetteur récepteur sous ModelSim.....                    | 63 |

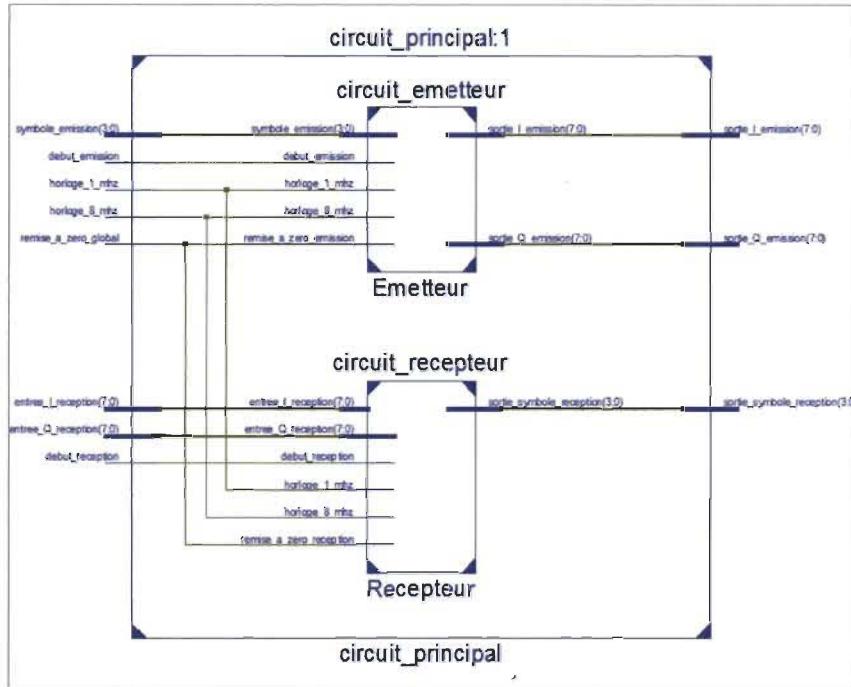

| Figure 4.9 : Le schématique de l'émetteur récepteur en bande de base.....             | 64 |

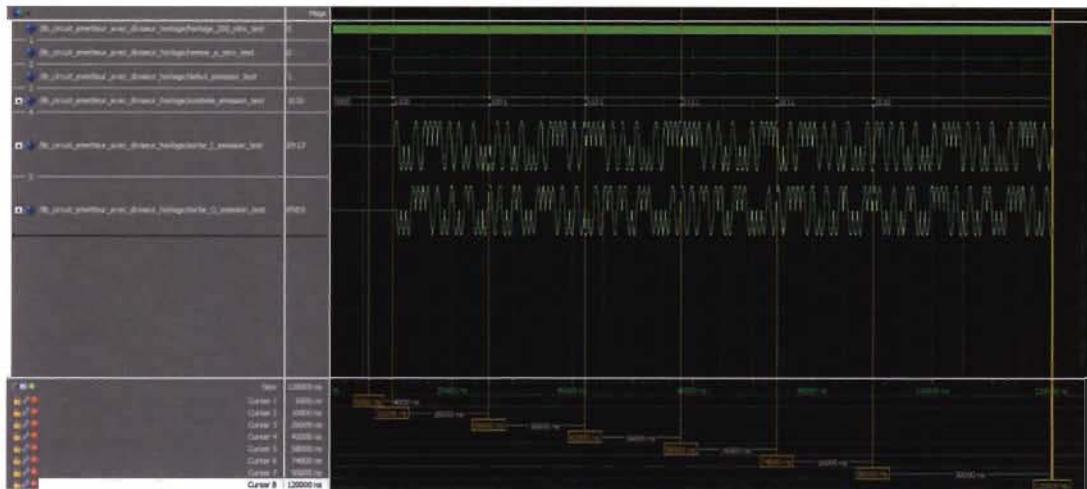

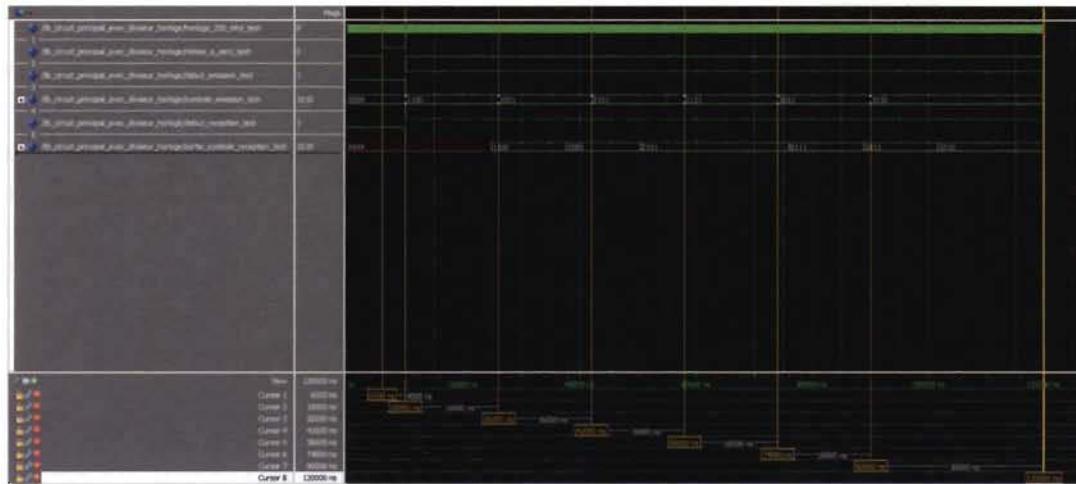

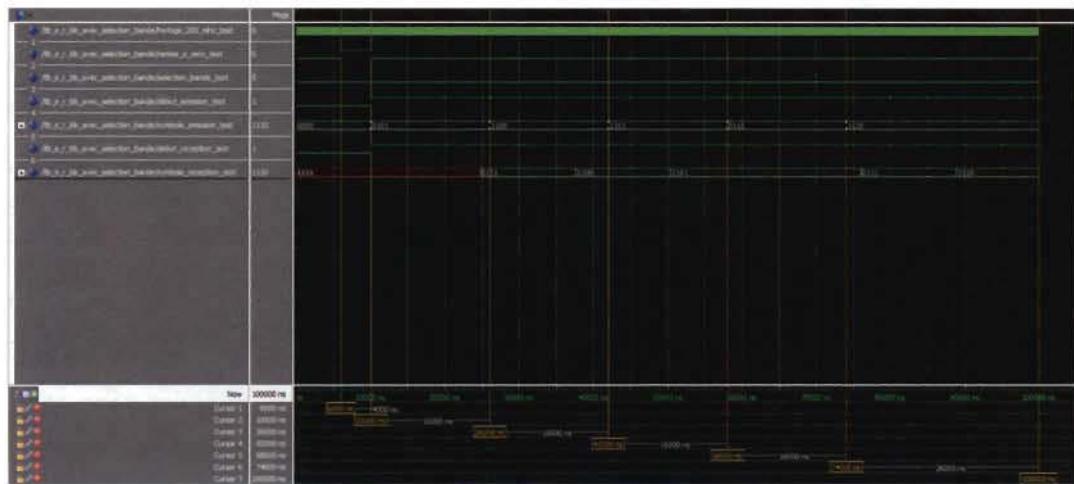

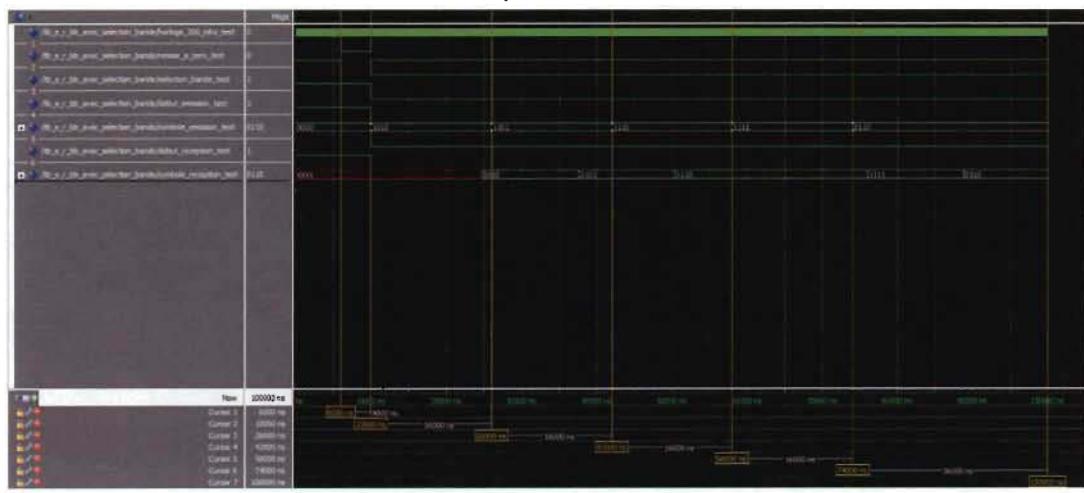

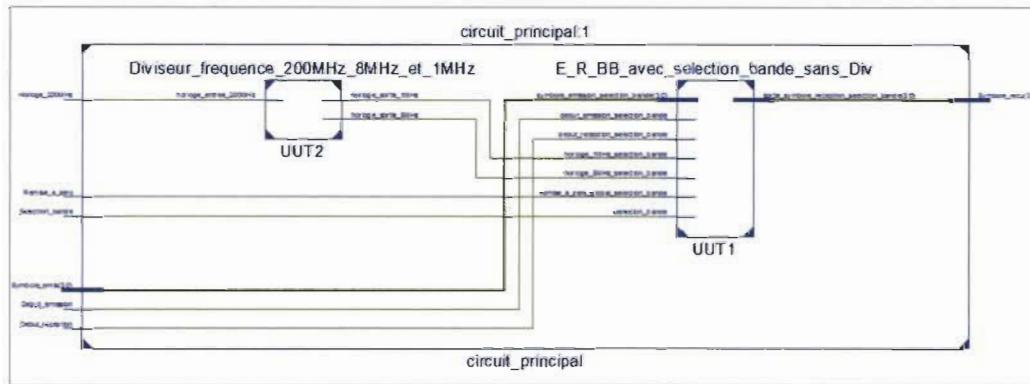

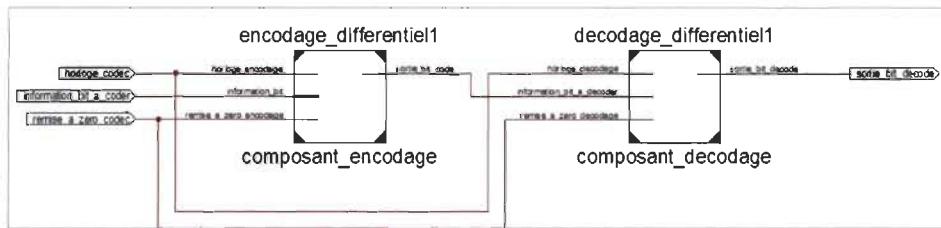

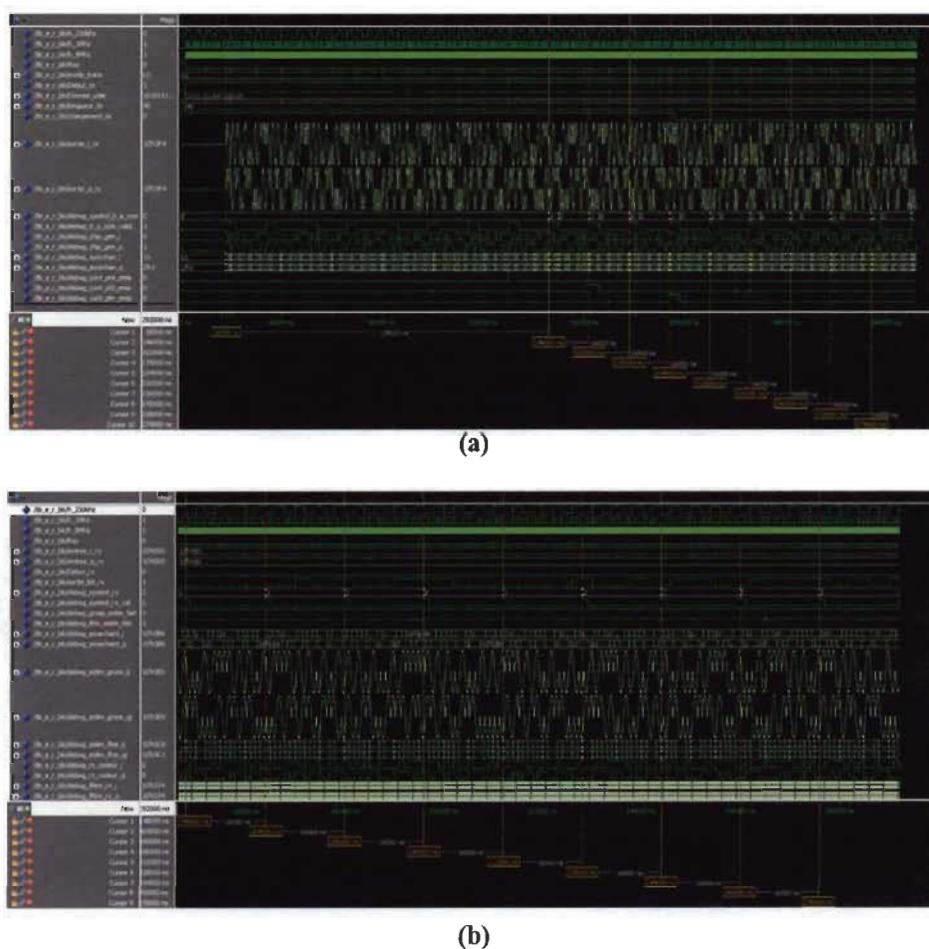

| Figure 4.10 : Simulation de l'E/R avec connexion et avec diviseur sous ModelSim ..... | 65 |

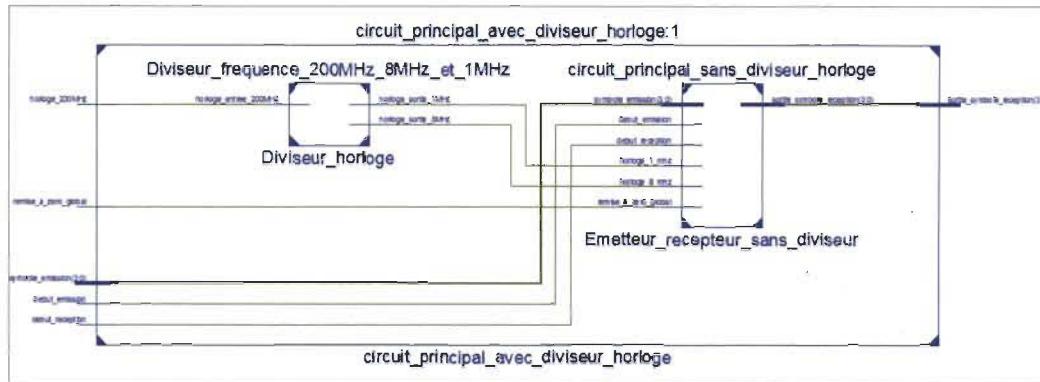

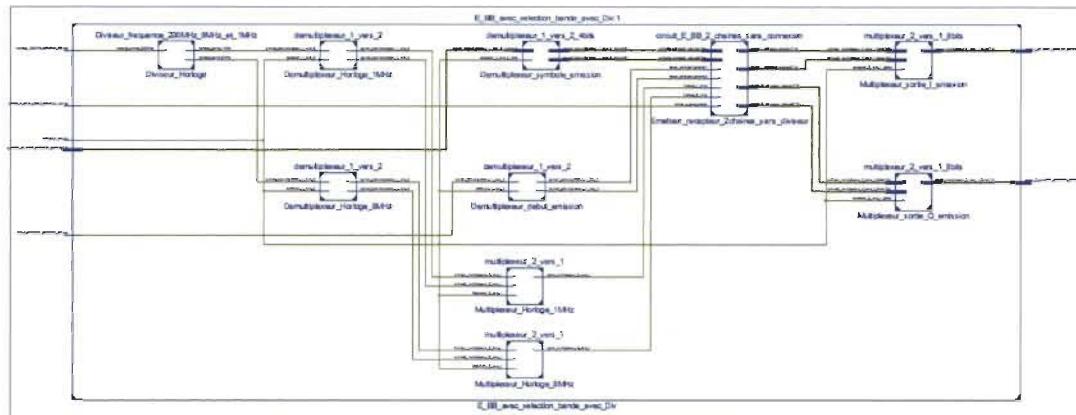

| Figure 4.11 : Le schématique de l'E/R avec connexion et avec diviseur .....           | 67 |

| Figure 4.12 : Les contrôles sur les entrées .....                                     | 68 |

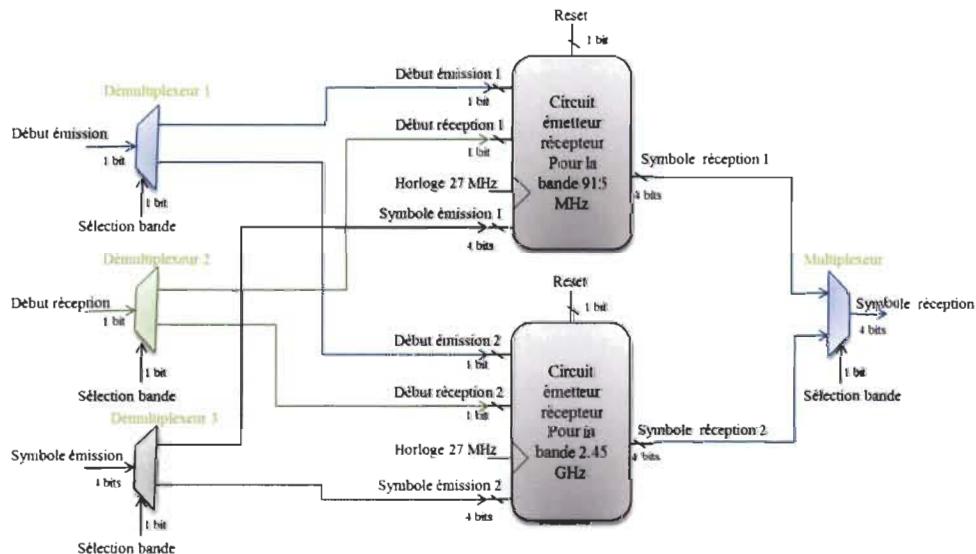

| Figure 4.13 : Architecture de deux E/R avec sélection de la bande utilisée .....      | 69 |

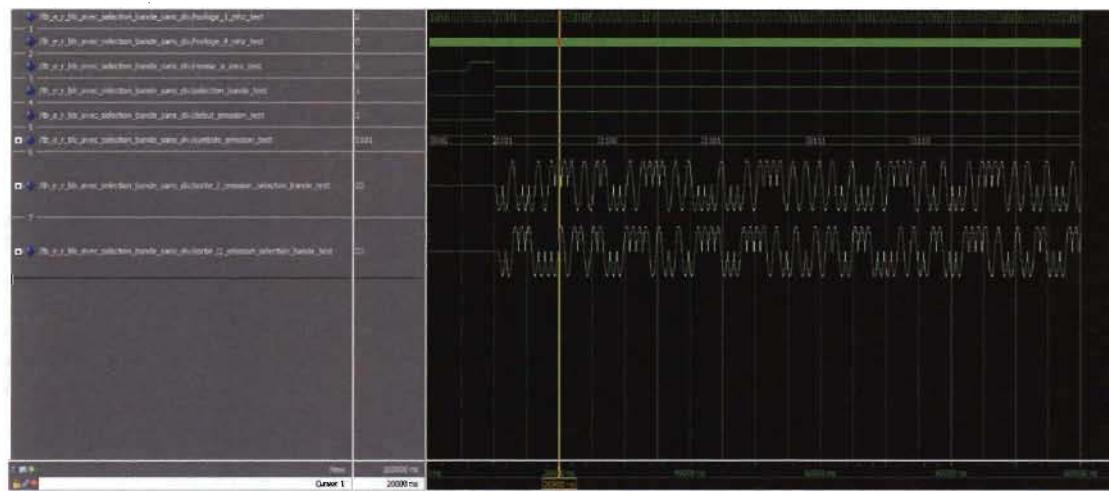

| Figure 4.14 : Simulation de deux E/R avec sélection de la première bande .....        | 70 |

| Figure 4.15 : Simulation de deux E/R avec sélection de la deuxième bande.....         | 70 |

| Figure 4.16 : Le schématique de deux E/R avec sélection de la bande .....             | 71 |

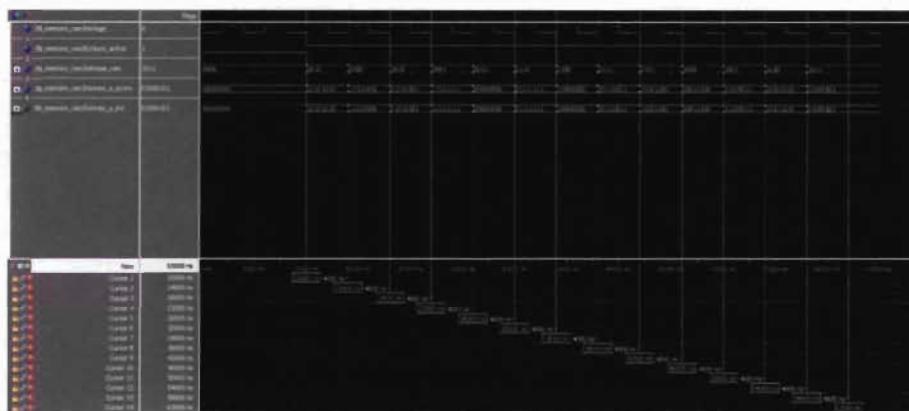

| Figure 4.17 : Test sous l'outil Chipscope Pro .....                                   | 72 |

| Figure 4.18 : Simulation du module adaptation 4 bits à 8 bits.....                    | 73 |

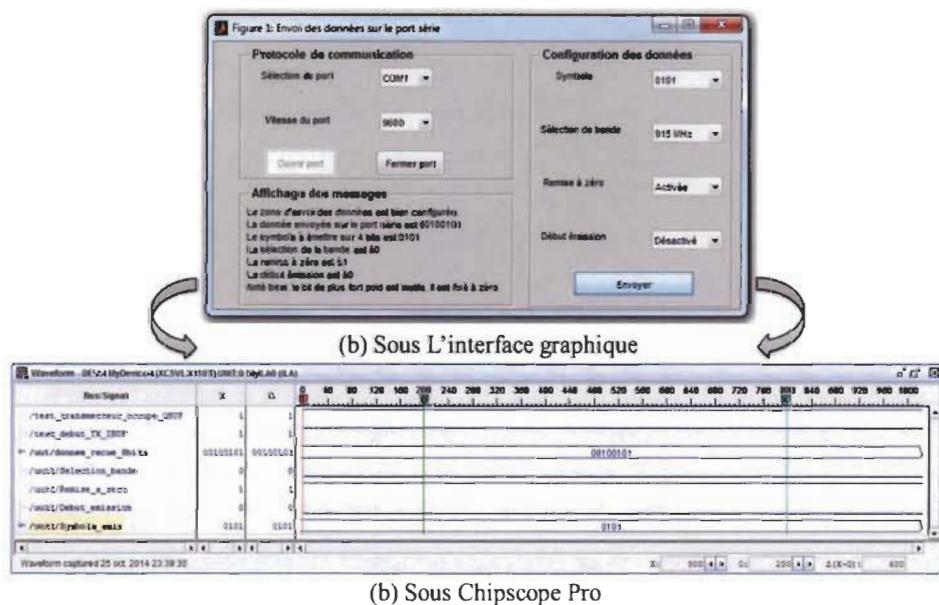

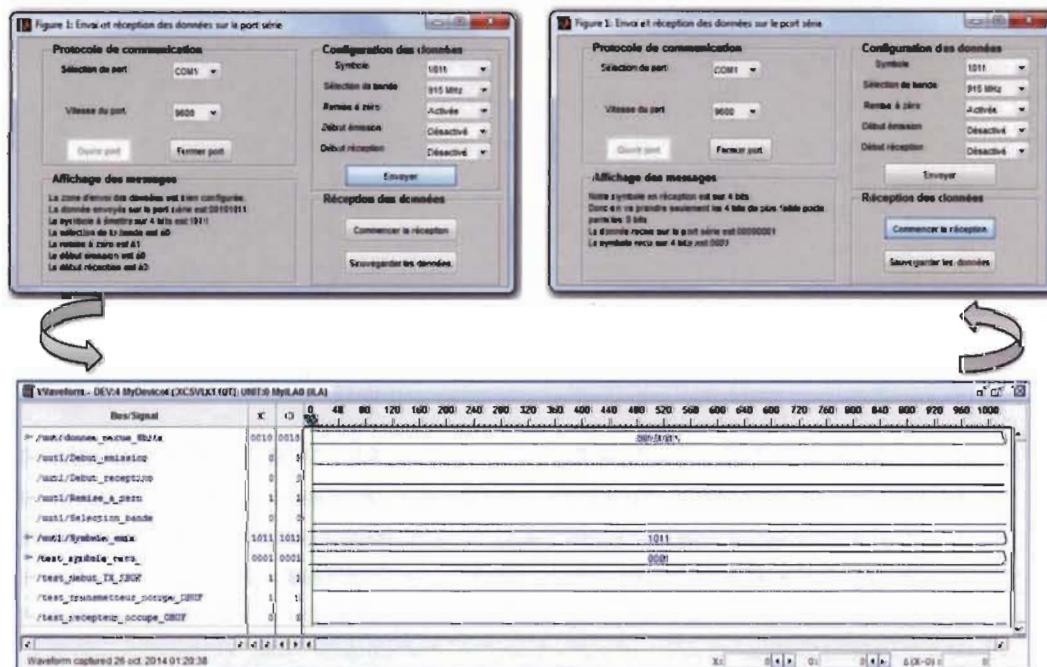

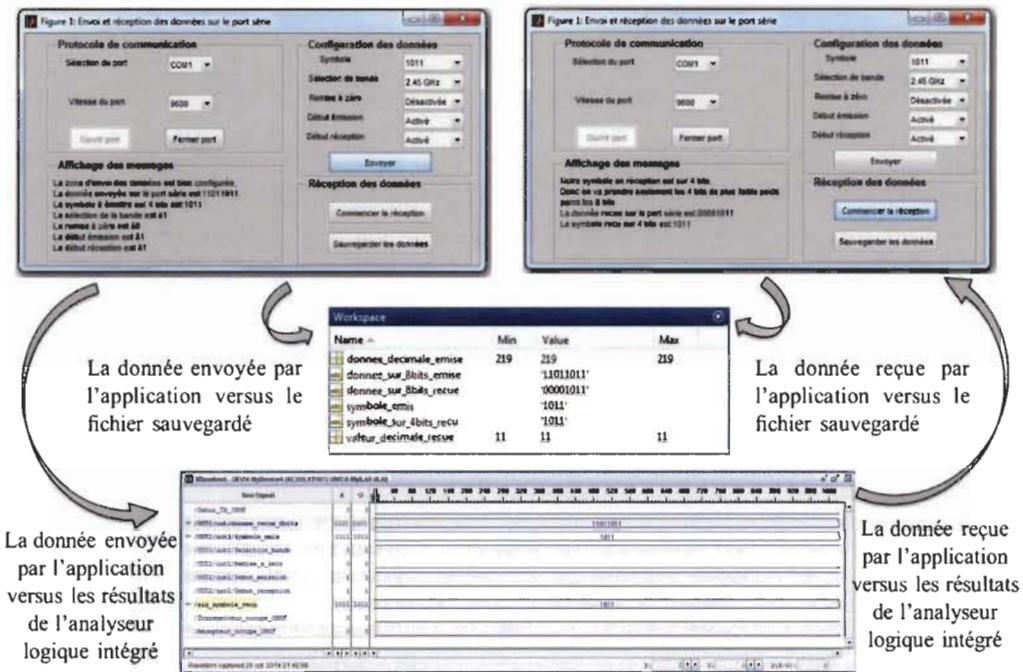

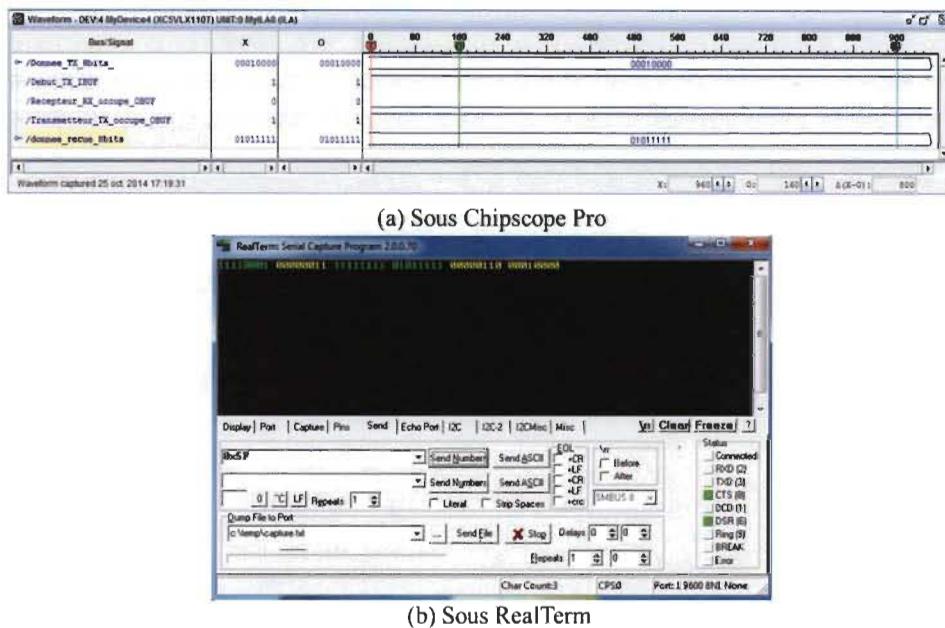

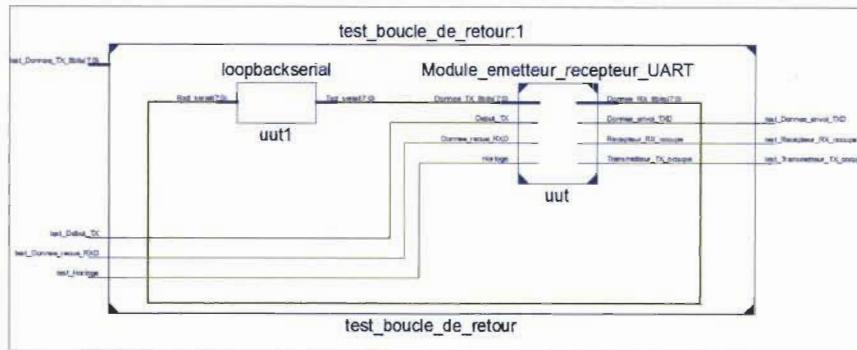

| Figure 4.19 : Résultats de test obtenus.....                                          | 74 |

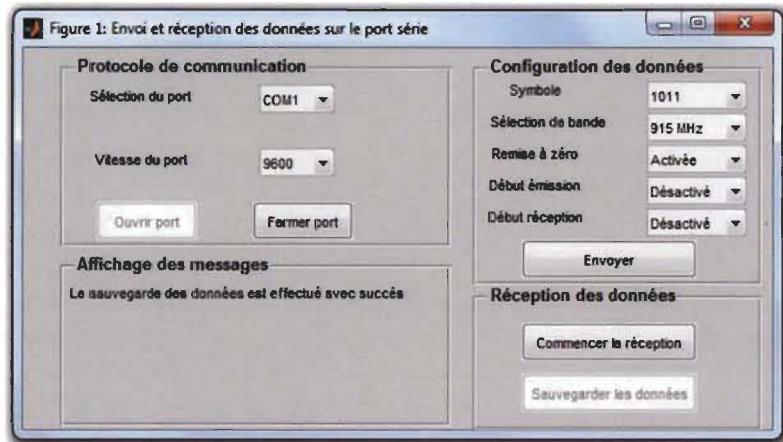

| Figure 4.20 : La sauvegarde des données émises et reçues.....                         | 75 |

| Figure 4.21 : Lors d'une remise à zéro .....                                          | 77 |

|                                                                     |    |

|---------------------------------------------------------------------|----|

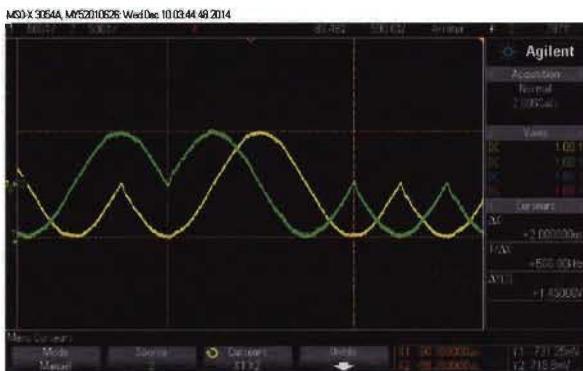

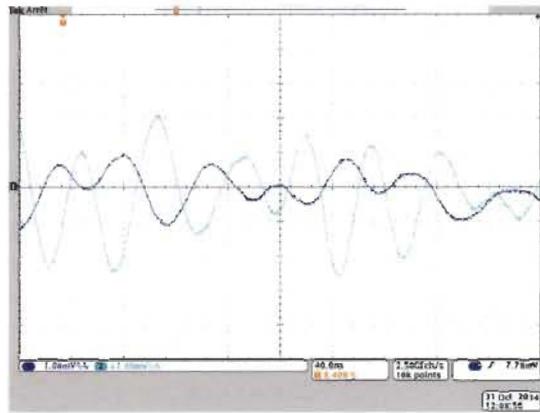

| Figure 4.22 : Résultats de visualisation sur l'oscilloscope .....   | 78 |

| Figure 4.23 : Lors de l'envoi d'un symbole.....                     | 79 |

| Figure 4.24 : Comparaison des résultats .....                       | 79 |

| Figure 4.25 : Résultats du test de la boucle de retour .....        | 81 |

| Figure 4.26 : Banc de test global.....                              | 82 |

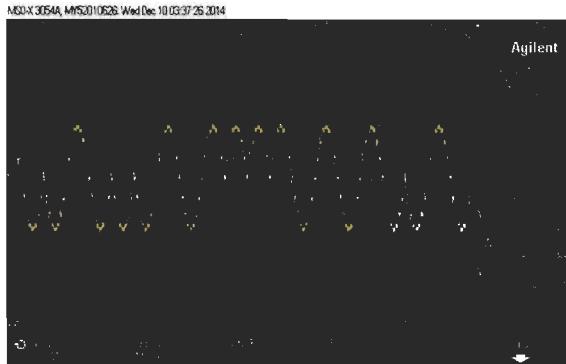

| Figure 4.27 : Les sorties du CNA avec une fréquence de 8 MHz.....   | 83 |

| Figure 4.28 : Les sorties du CNA avec une fréquence de 20 MHz.....  | 83 |

| Figure 4.29 : Les sorties du CNA avec une fréquence de 50 MHz.....  | 84 |

| Figure 4.30 : La visualisation des sorties sur l'oscilloscope ..... | 85 |

| Figure 4.31 : Résultats d'analyseur du spectre .....                | 86 |

| Figure 4.32 : Les données existantes dans la mémoire RAM .....      | 87 |

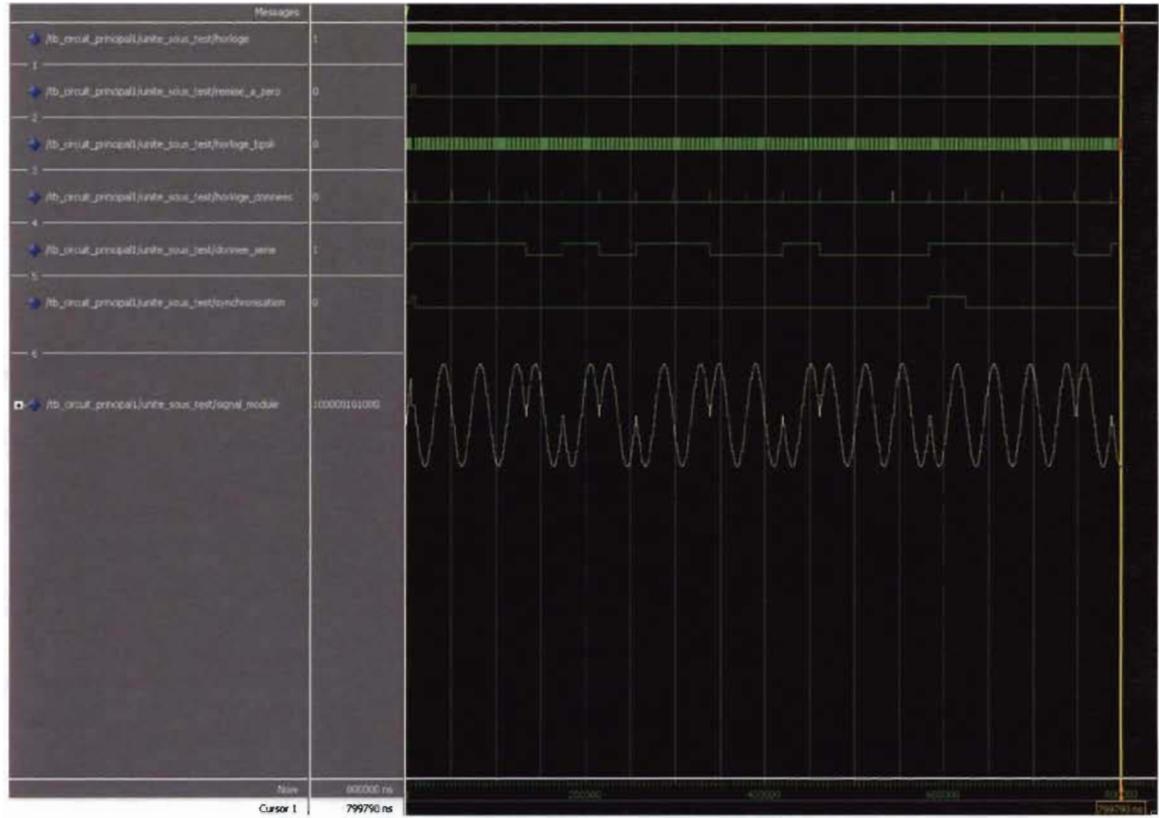

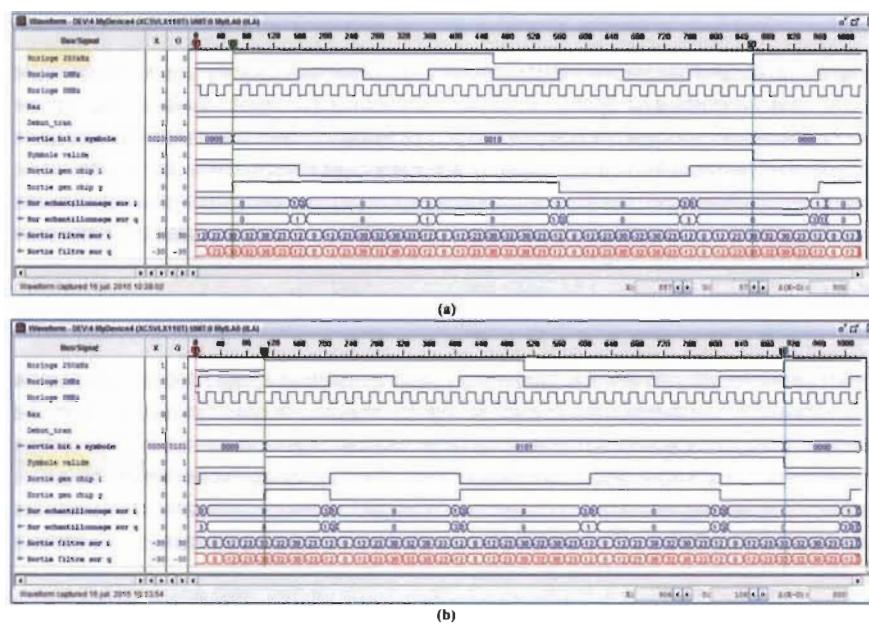

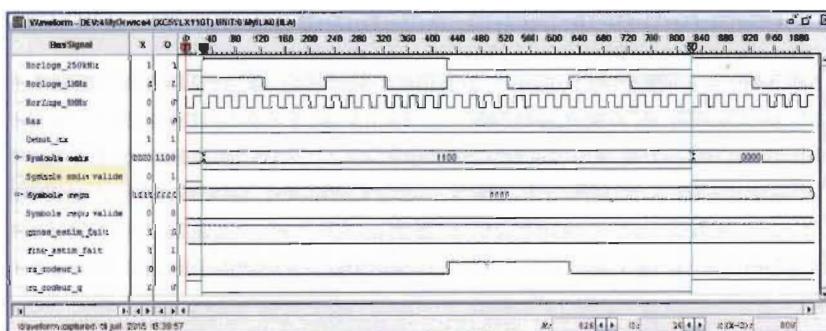

| Figure 4.33 : La simulation de la trame PPDU .....                  | 88 |

| Figure 4.34 : Une vue zoomée sur les données .....                  | 89 |

| Figure 4.35 : L'interface d'envoi d'une trame PPDU .....            | 90 |

| Figure 4.36 : Résultats de l'émetteur sur Chipscope Pro.....        | 91 |

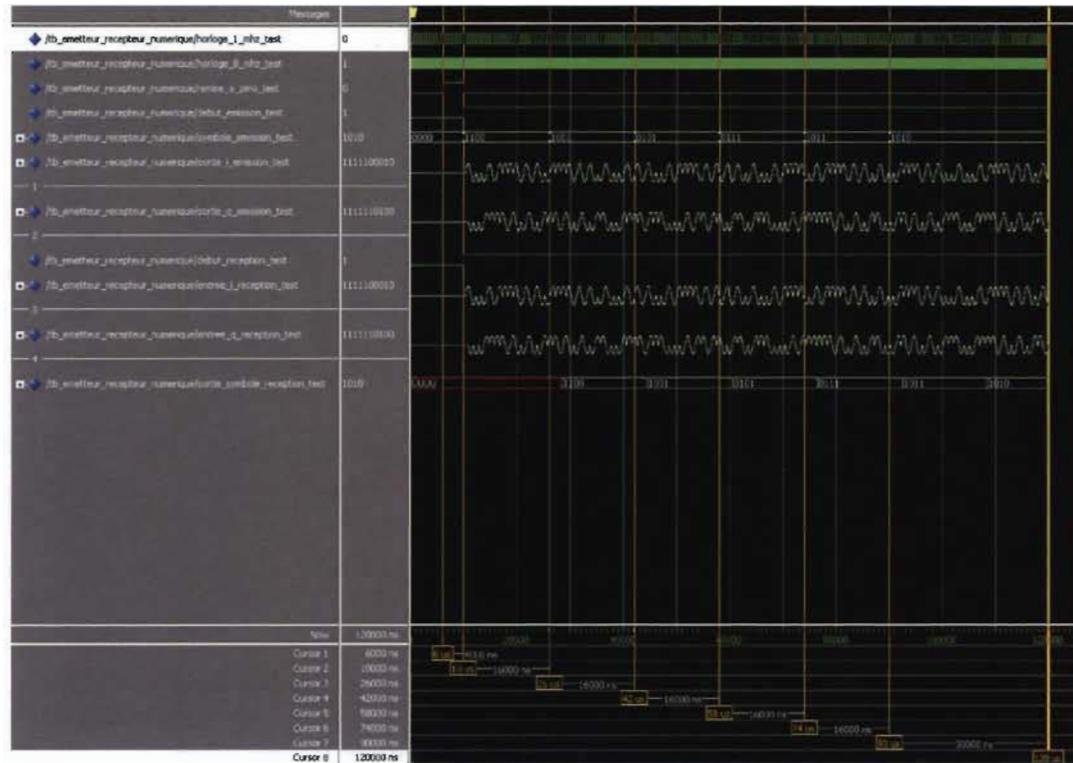

| Figure 4.37 : Simulation de l'E/R sous Modelsim .....               | 92 |

| Figure 4.38 : Test de l'E/R sur Chipscope Pro.....                  | 92 |

## Liste des symboles

ASIC: Application Specific Integrated Circuit

ASK: Amplitude Shift Keying

SFD: start frame delimiter

AWGN: Additive white Gaussian noise

SHR: Synchronization Header

BB: bande de base (Base Band)

RZ: retour zéro

NRZ: non-retour zéro

BF: Basse fréquence

TX: transmetteur

RX: récepteur

BPSK: Binary Phase Shift Keying

PHR: PHY Header

CAN: Convertisseur Analogique- Numérique (ADC : Analog to Digital Converter)

CNA: Convertisseur Numérique-Analogique (DAC: Digital to Analog Converter)

DC: Courant direct ou composante continue (Direct Current)

DDC: Convertisseur-abaisseur de fréquence (Digital Down Converter)

DDS: synthétiseur numérique directe (Direct Digital Synthesizer)

DI: Donnée d'entrée (Data Input)

DO: Donnée de sortie (Data Output)

DSSS: Spectre étalé à séquence directe (Direct Sequence Spread Spectrum)

DUC: Convertisseur-élévateur de fréquence (Digital Up Converter)

E/R: Emetteur / Récepteur

FDX: Full-Duplex

FFT: Transformée de Fourier rapide (Fast Fourier Transform)

FI: Fréquence intermédiaire (IF: Intermediate Frequency)

FIFO: First In First Out

FIR: Filtre à réponse impulsionnelle finie (Finite Impulse Response Filter)

FPGA: Field Programmable Gate Array

FSK: Frequency Shift Keying

FSM: Machine à état fini (Finite State Machine)

GPP: General Purpose Processor

HDX: Half-Duplex

IEEE: Institute of Electrical and Electronics Engineers

IFFT: Transformée de Fourier rapide inverse (Inverse Fast Fourier Transform)

IP: Propriété intellectuelle (Intellectual Property (Design), Internet Protocol (Network))

E/S: entrée / sortie (I/O: Input / Output)

FPB: Filtre passe bas (LPF: Low-Pass Filter)

I/Q: In phase and Quadrature phase

ISE: Integrated Software Environment

ISM: Industriel, Scientifique and Médical

ISO: International Organization for Standardization

JTAG: Joint Test Action Group

LPT: Line Print Terminal

NCO: Oscillateur contrôlé numériquement (numerical controlled oscillator)

NI: National Instruments

OLN: Oscillateur Local Numérique

OOK: On Off Keying

O-QPSK: Offset Quadrature Phase-shift keying

PC: Ordinateur (Personal Computer)

PLL: Boucle à verrouillage de phase (Phase Locked Loop)

PPDU: PHY protocol data units

PSK: Phase Shift Keying

QPSK: Quadrature Phase Shift Keying

QAM: Quadrature Amplitude Modulation

RAM: Mémoire à accès aléatoire (Random Access Memory)

RF: Radio Fréquence

RSB : Rapport signal sur bruit (SNR: Signal-to-Noise Ratio)

SHF: Supra-haute fréquence

UHF: Ultra Haute Fréquence

TSN: Traitement du signal numérique (DSP: Digital Signal Processing or DSP Processor)

USB: Universal Serial Bus

VCO: Oscillateur contrôlé par tension (Voltage Controlled Oscillator)

VHDL: Vhsic (very-high-speed integrated circuits) Hardware Description Language

WSN: Réseau de capteurs sans fil (Wireless Sensor Network)

# Chapitre 1 - Introduction

## 1.1 Les réseaux de capteurs sans fils

Dans un premier temps, nous allons parler sur la technologie des réseaux de capteurs, qui est par définition une collecte de petits dispositifs de détection à faible coût avec calcul, stockage et communication.

Ils possèdent une large gamme d'applications potentielles à l'industrie, la science, le transport, les infrastructures civiles, et de la sécurité. Nous pouvons citer à titre d'exemple : la surveillance médicale et le contrôle des patients, détection d'intrusions et contrôle d'accès, contrôle de la pollution et découverte des catastrophes naturelles et industrielles dans des milieux hostiles.

Suivant l'historique des capteurs, les premiers capteurs inventés sont connectés par fil à un emplacement central en 1970. En 1980, les réseaux de capteurs câblés distribués sont apparus et à partir de l'année 1993, les projets sur ce domaine ont commencés tel que le projet de LWIM à UCLA et aussi le projet DARPA SENSIT: UC Berkeley, USC, Cornell (1999-2003). En 2001, le laboratoire de recherche d'Intel à Berkeley était focalisé sur les réseaux des capteurs sans fil, ainsi que le centre NSF était spécialisé sur les réseaux de détection embarqués. Dans la même période, les réseaux de capteurs sont émergés par l'industrie et les entreprises y compris Sensoria, Arbalète, Ember Corp, SensiCast. Il y avait des prototypes fabriqués par : Intel, Bosch, Motorola, General Electric, Samsung. En 2003, le standard IEEE 802.15.4 [1] est apparu.

## 1.2 Le standard IEEE 802.15.4

La norme la plus utilisée dans la technologie de réseaux de capteurs est la norme IEEE 802.15.4 [1]. Il existe beaucoup de protocoles de communication sans fil reposants sur cette norme dans le but est d'optimiser la communication entre les objets. Nous citons par exemple : Wireless HART, ISA-SP100, IETF IPv6 – LoWPAN, DigiMesh (réseaux maillés) et le plus répandu : ZigBee.

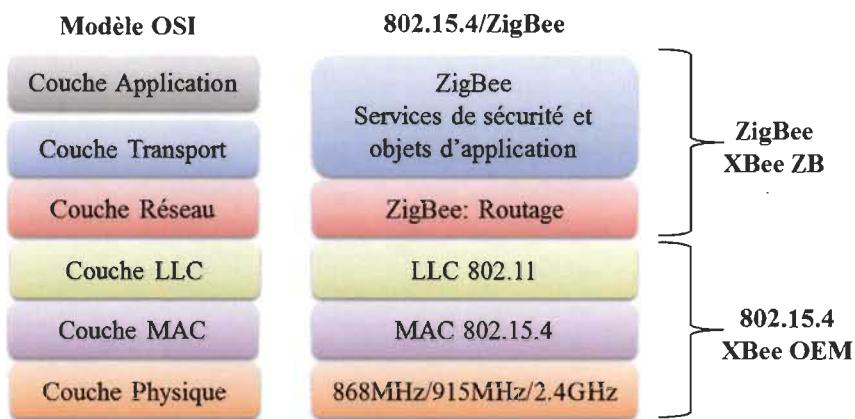

Figure 1.1 : Le modèle en couche (adaptée de [1])

Cette norme définit une couche de communication au niveau 2 (liaison des données) du modèle OSI [2]. Le but principal est de permettre la communication entre deux appareils. Elle a été créée par l'Institut d'ingénieurs en électrique et électronique (IEEE) [3]. Sa tâche essentielle est d'établir des normes de sorte que les progrès technologiques peuvent compter avec une plate-forme commune de règles à définir et compatible. Dans les dispositifs existants, ce protocole est défini à l'aide du module XBee 802.15.4 OEM [4].

Les unités d'information numériques (bits) sont gérées et organisées par la couche liaison de données pour devenir des impulsions électromagnétiques (ondes) au niveau inférieur (couche physique). Cette couche est similaire à celles d'autres connus comme la

norme 802.11 (la technologie Wifi) ou la norme 802.3 (Ethernet). Les fréquences définies dans la norme sont réparties entre 27 canaux différents divisés en trois groupes principaux:

- 868.0 - 868.6MHz → 1 canal (Europe)

- 902.0-928.0MHz → 10 canaux (États-Unis)

- 2.40-2.48GHz → 16 canaux (international)

### 1.3 Le protocole de communication ZigBee

Le protocole de communication ZigBee est le plus répandu pour les réseaux de capteurs. Il est basé sur le standard IEEE 802.15.4 [1].

Cette technologie définit une couche de communication au niveau 3 et dessous dans le modèle OSI. Son objectif principal est de créer une topologie de réseau (hiérarchie) afin de laisser un certain nombre de périphériques communiquer entre eux, et définit aussi les fonctions de communication supplémentaires telles que l'authentification, le cryptage et l'association. Elle a été créée par un ensemble de sociétés qui forment l'Alliance ZigBee [5]. Le module XBee ZB de Digi [6] s'inspire de ce protocole.

Trois émetteurs-récepteurs XBee différents sont utilisés pour fournir une communication dans les bandes de fréquence mentionnées précédemment:

- 868MHz → XBee 868MHz OEM [7]

- 900MHz → XBee 900MHz OEM [8]

- 2.40GHz → XBee 802.15.4 OEM [4] / XBee ZB [6]

La norme propose deux options de la couche physique basées sur la bande de fréquence. Toutes les deux reposent sur la séquence directe d'étalement du spectre (DSSS, Direct Sequence Spread Spectrum).

Tableau 1-1 : Bandes spécifiées par la norme IEEE 802.15.4 (adaptée de [1])

| Bande (MHz)              | Bande de fréquence (MHz) | Paramètres d'étalement |            | Paramètres de données |                              |                     |

|--------------------------|--------------------------|------------------------|------------|-----------------------|------------------------------|---------------------|

|                          |                          | Taux de Chip (kchip/s) | Modulation | Débit binaire (kb/s)  | Taux de symbole (ksymbole/s) | Symboles            |

| 868/915                  | 868-868.6                | 300                    | BPSK       | 20                    | 20                           | Binaire             |

|                          | 902-928                  | 600                    | BPSK       | 40                    | 40                           | Binaire             |

| 868/915<br>(optionnelle) | 868-868.6                | 400                    | ASK        | 250                   | 12.5                         | 20 bits PSSS        |

|                          | 902-928                  | 1600                   | ASK        | 250                   | 50                           | 5 bits PSSS         |

| 868/915<br>(optionnelle) | 868-868.6                | 400                    | O-QPSK     | 100                   | 25                           | 16-aire Orthogonaux |

|                          | 902-928                  | 1000                   | O-QPSK     | 250                   | 62.5                         | 16-aire Orthogonaux |

| 2450                     | 2400-2483.5              | 2000                   | O-QPSK     | 250                   | 62.5                         | 16-aire Orthogonaux |

Le tableau 1-1 dresse les paramètres de chaque bande définie par la norme IEEE 802.15.4. Le chip est un code symbole (PN, pseudo noise) : qui possède une fréquence beaucoup plus élevée que la fréquence des données d'entrée. Le débit de données est 250kbps à 2.45 GHz, 40kbps à 915MHz et 20kbps à 868MHz.

Le débit le plus élevé à 2.45 GHz est attribué à un schéma de modulation d'ordre supérieur. La basse fréquence fournit une portée accrue en raison de faibles pertes de propagation. Le faible taux peut être traduit en une meilleure sensibilité et une large zone de couverture. Le taux élevé signifie un débit plus élevé, une latence plus faible ou un faible rapport cyclique [1]. L'acheminement du flux de données (en émission et en réception) passé dans chaque bloc est mentionné sur la figure 1.2.

Figure 1.2 : L’acheminement du flux de données (adapté de [1])

#### 1.4 Problématique

Nous pouvons signaler que la chaîne de communication en bande de base existante pour le protocole ZigBee est implémentée sur des circuits figés. Lorsque nous avons besoin à chaque fois de travailler sur un taux de transmission (à titre d’exemple) bien déterminé, nous serons obligé de changer le circuit au complet.

Donc nous avons un grand défi sur le fait d’implémenter une chaîne numérique en bande de base reconfigurable, pour ce protocole, sur FPGA, cette chaîne sert à :

- Configurer des paramètres dans le circuit programmable à savoir : différents taux de transmission (1 MHz, 2 MHz par exemple) ; prendre en considération les trois bandes 868 MHz, 915 MHz, 2,45 GHz ; deux schémas de modulation (QPSK et O-QPSK) ; et différentes résolutions des convertisseurs numérique-analogique (nombre de bits).

- Implémenter la technique d’étalement du spectre DSSS pour avoir un spectre large bande (à la place d’un modulateur numérique basé sur DDS).

- Effectuer un filtrage numérique reconfigurable avec la fonction d'interpolation et décimation pour différente fréquence d'échantillonnage ;

- Elle est contrôlée par une interface graphique développée sur un ordinateur ;

- Faire un test réel sur un circuit programmable FPGA et la validation par le matériel ;

- Faire un contrôle général d'émetteur/récepteur basant sur une machine à état finie afin de gérer les modes de transmission : Arrêt, boucle, émission et réception.

- Etudier la trame binaire PPDU venant de la couche MAC

L'avantage est que l'architecture à implémenter est bien définie par le standard, ce qui nous facilite sa description en VHDL bloc par bloc. Les trois bandes qui nous intéressent sont celles de trois dernières lignes du tableau précédent (bande 868 MHz, bande 915 MHz et bande 2.45 GHz). Vu que les deux bandes (bande 868 MHz, bande 915 MHz) sont semblables au niveau de conception donc, nous étudierons seulement les deux bandes (bande 915 MHz et bande 2.45 GHz).

## 1.5 Objectifs spécifiques

Comme objectifs à court et long terme dans ce projet, nous pouvons les souligner de cette façon :

- Conception d'un émetteur en bande de base avec étalement du spectre (DSSS) ;

- Conception d'un émetteur récepteur en bande de base avec étalement du spectre (DSSS);

- Etude de la chaîne reconfigurable avec un étalement du spectre (DSSS) ;

- Développement d'une interface graphique en interrogeant avec la chaîne ;

- Test réel et validation sur le matériel ;

- Conception du contrôleur général des modes de transmission basant sur la machine à état finie.

## 1.6 Méthodologie

La première étape du travail est de faire l'état de l'art autour de notre sujet de recherche afin de clarifier les idées et d'identifier la problématique liée aux travaux antérieurs. Nous montrons les limites de la portée des travaux effectués par les prédecesseurs, ainsi, nous survolons les travaux connexes en faisant une analyse de fonctionnement; qui comprend les hypothèses projetées et aussi les démarches à suivre en terminant par une présentation sur les résultats obtenus.

L'étape suivante consiste à, détailler la partie essentielle décrite par la composition de la couche physique définie par le standard IEEE 802.15.4, ainsi que les différentes techniques utilisées. Nous parlons aussi sur les plateformes reconfigurables utilisant FPGA comme circuit pour le test et débogage.

La troisième étape s'agit de, présenter la composition de notre chaîne de communication proposée; en décrivant toute la chaîne en émission et en réception. Ainsi, elle permet d'expliquer la description et l'implémentation de la chaîne en VHDL et aussi le processus de développement qui décrit la méthodologie utilisée pour réaliser ce projet.

La dernière étape de notre projet comprend la conception des éléments de notre chaîne par programmation en VHDL, nous exposons les différents résultats des simulations obtenus et aussi les différents tests effectués avec la validation sur le matériel.

### **1.7 Organisation du mémoire**

La structure du mémoire est décrite comme suit : le deuxième chapitre donnera une idée globale sur la composition de la couche physique définie par le standard IEEE 802.15.4, ainsi que les différentes techniques utilisées.

La troisième partie présente la chaîne de communication proposée. Nous mettrons dans l'annexe B les blocs internes de toute la chaîne d'émission et réception, en plus, nous expliquerons la description de différents blocs à implémenter en VHDL. Nous parlerons aussi sur l'interface graphique à développer pour pouvoir communiquer avec la chaîne à partir d'un ordinateur, ainsi que les éléments requis pour la validation de ce projet.

Le quatrième chapitre va exposer les résultats des simulations obtenus ainsi que les tests réels effectués durant le projet. Sachant que l'annexe D comporte une panoplie de nos travaux supplémentaires réalisés.

Enfin, ce mémoire se terminera par une brève conclusion en survolant les parties essentielles du rapport et en mentionnant quelques perspectives.

# **Chapitre 2 - La couche physique de IEEE 802.15.4**

## **2.1 Introduction**

Il y a quelques années, un nouveau standard est apparu qui est dédié au domaine à faible taux de transfert de données sans fil personnel (LR-WPAN). Ces réseaux sont caractérisés par le faible coût et le faible rendement de traitement. Cette norme connue sous le nom IEEE 802.15.4 et le protocole ZigBee représente le résultat des efforts du groupe de cette norme avec Alliance ZigBee. Ce groupe est responsable de la couche physique (PHY) et de la couche d'accès au support (MAC), tandis que ZigBee Alliance a été concentrée dans les couches supérieures.

Nous allons nous concentrer dans ce chapitre sur la composition de la couche physique définie par le standard IEEE 802.15.4 [9] et les différentes techniques utilisées. Ainsi, une brève introduction sera réservée pour la configuration numérique d'un système radio fréquence par un circuit programmable FPGA.

## **2.2 La composition de la couche physique pour la norme IEEE 802.15.4**

Le standard définit 27 canaux répartis dans trois bandes de fréquences: 1 canal réservé dans la bande 868 MHz, 10 canaux dans la bande 915 MHz, et 16 canaux dans la bande 2.4 GHz.

Les fréquences des différents canaux sont données par l'équation suivante :

$$F(k) = \begin{cases} 868.3 \text{ MHz} & \text{si } k = 0; \\ 906 + 2(k - 1) \text{ MHz} & \text{si } k = 1.., 10; \\ 2405 + 5(k - 11) \text{ MHz} & \text{si } k = 11.., 26; \end{cases} \quad (2.1)$$

Où k est le numéro du canal.

### 2.2.1 La trame des données PPDU

Le tableau 2-1 montre les types de données de la trame PPDU dans la couche physique venant de la couche MAC.

Le champ entête de synchronisation ou SHR permet au récepteur de synchroniser et de verrouiller dans le flux binaire. L'entête couche physique ou PHR contient la longueur de la trame d'information. La charge utile de la couche physique (Payload en anglais) est fournie par les couches supérieures et elle comprend des données ou des commandes qui doivent être transmises à un autre dispositif.

La longueur du préambule de la modulation O-QPSK est de 4 octets (8 symboles): 868 MHz → 320 μs; 915 MHz → 128 μs; 2.45 GHz → 128 μs.

La longueur du champ début délimiteur de trame ou SFD pour la modulation O-QPSK est de 1 octet (2 symboles) pour 868 MHz; 915 MHz et 2.45 GHz.

Le temps maximal qu'un émetteur-récepteur en bande de base ait besoin pour passer de la transmission (TX) à la réception (RX) et vice-versa est de 12 périodes symbole ( $T_s$ ).

Le premier bit qui sera transmis est celui le moins significatif (LSB) du champ SHR, le plus significatif (MSB) du dernier octet de la charge utile de la couche physique est transmis en dernier.

Tableau 2-1 : La trame PPDU de la couche physique (adapté de [9])

| Type des données PPDU | Trame PPDU     |          |                              |                 |                                           |

|-----------------------|----------------|----------|------------------------------|-----------------|-------------------------------------------|

|                       | vers LSB ← ←   |          | Trame PPDU                   |                 | → → vers MSB                              |

|                       | SHR            |          | PHR                          |                 | PHY payload                               |

|                       | 4 octets       | 1 octet  | 1 octet                      |                 | Variable (de 0 octet jusqu'au 127 octets) |

| Réservé               | Préambule      | SFD      | Longueur de données (7 bits) | Réserve (1 bit) | PSDU ou MPDU                              |

|                       | 00000000 (x 4) | 11100101 | 0000000                      | 0               | Pas des données                           |

|                       | 00000000 (x 4) | 11100101 | 1000000                      | 0               | 1 octet des données                       |

|                       | 00000000 (x 4) | 11100101 | 0100000                      | 0               | 2 octets des données                      |

|                       | 00000000 (x 4) | 11100101 | 1100000                      | 0               | 3 octets des données                      |

| MPDU (acquittement)   | 00000000 (x 4) | 11100101 | 0010000                      | 0               | 4 octets des données                      |

|                       | 00000000 (x 4) | 11100101 | 1010000                      | 0               | 5 octets des données                      |

| Réservé               | 00000000 (x 4) | 11100101 | 0110000                      | 0               | 6 octets des données                      |

|                       | 00000000 (x 4) | 11100101 | 1110000                      | 0               | 7 octets des données                      |

|                       | 00000000 (x 4) | 11100101 | 0001000                      | 0               | 8 octets des données                      |

| MPDU (données utiles) | 00000000 (x 4) | 11100101 | 1001000                      | 0               | 9 octets des données                      |

|                       | :              | :        | :                            | :               | :                                         |

|                       | 00000000 (x 4) | 11100101 | 1111111                      | 0               | 127 octets des données                    |

### 2.2.2 Technique d'étalement du spectre par DSSS

La norme IEEE 802.15.4 utilise la méthode d'étalement du spectre en séquence directe (DSSS). En effet, les symboles sont élargis par des séquences pseudo-aléatoire PN de 32 bits (les chips) lorsque le nombre de « 0 » est égal au nombre des « 1 ». Chaque séquence PN est générée à partir du précédent par une rotation de quatre bits vers la droite dans les séquences des huit premiers symboles.

Tableau 2-2 : Pour la bande 2.45 GHz utilisant O-QPSK (adapté de [1] et [9])

| Symbol de données<br>(décimale) | Symbol de données (binaire)<br>( $b_0 b_1 b_2 b_3$ ) | Valeurs du Chip<br>( $c_0 c_1 \dots c_{30} c_{31}$ ) |

|---------------------------------|------------------------------------------------------|------------------------------------------------------|

| 0                               | 0000                                                 | 11011001110000110101001000101110                     |

| 1                               | 1000                                                 | 11101101100111000011010100100010                     |

| 2                               | 0100                                                 | 00101110110110011100001101010010                     |

| 3                               | 1100                                                 | 00100010111011011001110000110101                     |

| 4                               | 0010                                                 | 01010010001011101101100111000011                     |

| 5                               | 1010                                                 | 00110101001000101110110110011100                     |

| 6                               | 0110                                                 | 11000011010100100010111011011001                     |

| 7                               | 1110                                                 | 10011100001101010010001011101101                     |

| 8                               | 0001                                                 | 1000110010010110000001101111011                      |

| 9                               | 1001                                                 | 1011100011001001011000001110111                      |

| 10                              | 0101                                                 | 0111101110001100100101100000111                      |

| 11                              | 1101                                                 | 01110111101110001100100101100000                     |

| 12                              | 0011                                                 | 00000111011110111000110010010110                     |

| 13                              | 1011                                                 | 0110000011101111011100011001001001                   |

| 14                              | 0111                                                 | 1001011000000110111101110001100                      |

| 15                              | 1111                                                 | 1100100101100000111011110111000                      |

Les séquences des 8 derniers symboles sont générées en inversant les bits des 8 premières paires. Ainsi, à partir de la séquence correspondante au symbole zéro, nous pouvons générer tous les autres. Dans l'implémentation, les chips sont générés en basant sur le premier symbole en utilisant un tampon circulaire et chaque séquence du chip prend une certaine position du tampon. Le tableau 2-2 présente les 16 symboles définis par la norme avec sa séquence correspondante.

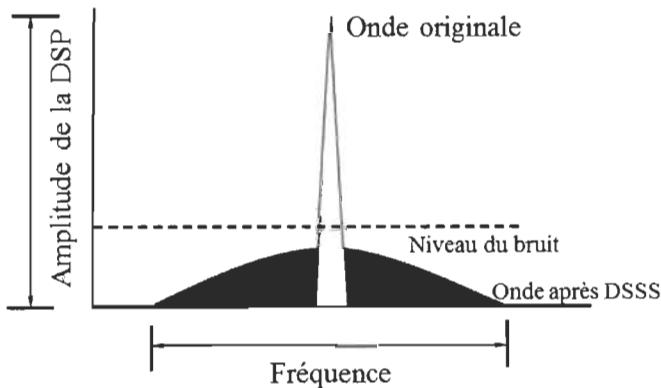

La séquence est convertie [une séquence chip de 2 Mcps (32 x 62.5 Kbps)] à travers un processus d'étalement de 32 fois (DSSS), c'est un type de séquence orthogonale qui est utilisée afin de fournir un taux d'erreur du paquet (PER) stable dans le système de Zigbee sans codage canal. La figure 2.1 représente l'effet d'étalement avec DSSS sur l'onde originale. Le DSSS est une technique de modulation pour la communication sans fil. Il étale les bits de données à une grande largeur de bande et occupe plus de bande passante que la bande passante d'origine du signal transmis. Toutefois, il occupe une très faible densité spectrale de puissance pour le signal. Ici, le facteur clé est la faible densité spectrale de puissance, ce qui entraîne moins d'interférences aux autres services partageant la même bande.

Figure 2.1 : Effet d'étalement avec DSSS (adaptée de [9])

Il y a une autre architecture pour la bande 868/915 MHz en utilisant PSSS comme technique d'étalement au lieu de DSSS avec la modulation BPSK et ASK (250 Kb/s) ou aussi une architecture qui utilise la technique DSSS avec le schéma de modulation O-QPSK (le débit binaire de 250 Kb/s), tel que nous utilisons un mappage d'un symbole à 16 séquences de 16 chips (au lieu de 32 chips pour la bande 2.45 GHz), comme le montre le tableau 2-3.

Tableau 2-3 : Pour les bandes 868/915 MHz avec O-QPSK (adaptée de [1] et [9])

| Symbol de données (décimale) | Symbol de données (binaire) $(b_0 \ b_1 \ b_2 \ b_3)$ | Valeurs du Chip $(c_0 \ c_1 \dots \ c_{15})$ |

|------------------------------|-------------------------------------------------------|----------------------------------------------|

| 1                            | 0000                                                  | 001111000100101                              |

| 2                            | 1000                                                  | 010011110001001                              |

| 3                            | 0100                                                  | 010100111100010                              |

| 4                            | 1100                                                  | 100101001111000                              |

| 5                            | 0010                                                  | 001001010011110                              |

| 6                            | 1010                                                  | 100010010100111                              |

| 7                            | 1110                                                  | 111100010010100                              |

| 8                            | 0001                                                  | 0110101101110000                             |

| 9                            | 1001                                                  | 0001101011011100                             |

| 10                           | 0101                                                  | 0000011010110111                             |

| 11                           | 1101                                                  | 1100000110101101                             |

| 12                           | 0011                                                  | 0111000001101011                             |

| 13                           | 1011                                                  | 1101110000011010                             |

| 14                           | 0111                                                  | 1011011100000110                             |

| 15                           | 1111                                                  | 1010110111000001                             |

Pour avoir besoin plus d'informations sur les architectures de la norme IEEE 802.15.4, veuillez consulter les références [10], [11], [1], [12], [9], et [13].

### 2.2.3 *La modulation QPSK versus O-QPSK*

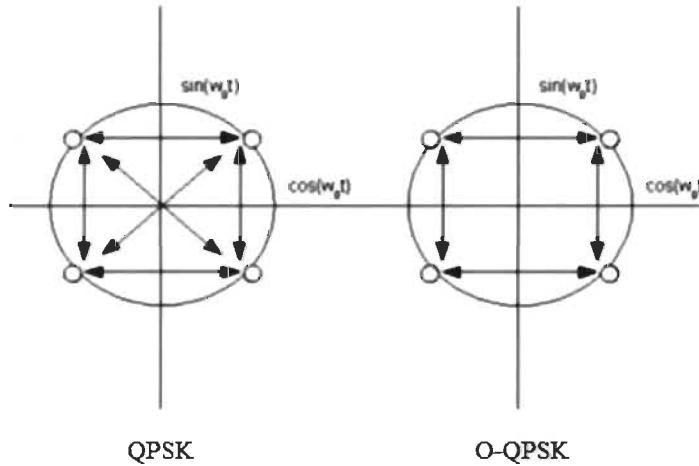

Le standard IEEE 802.15.4 utilise la modulation O-QPSK, elle présente plusieurs avantages par rapport QPSK: les variations de phase, sont réduites de  $180^\circ$  à  $90^\circ$ , peuvent utiliser, dans une transmission, un amplificateur non linéaire (Vous pouvez en savoir plus à ce sujet dans [15]).

La modulation QPSK, dans un flux des données  $d_k = d_0, d_1, d_2, \dots$ , est composée d'impulsions bipolaires de données +1 ou -1, elle est divisée en deux composantes: une composante de phase  $d_I(t) = d_0, d_2, d_4, \dots$  et une composante en quadrature,  $d_Q(t) = d_1, d_3, d_5, \dots$  dans laquelle la composante de phase est constituée par les bits pairs et la composante en quadrature par les bits impairs avec un débit binaire en moitié de  $d_k(t)$ .

Une onde modulée en QPSK est obtenue en utilisant les fonctions sinus et cosinus d'une onde porteuse, résultant en:

$$s(t) = \frac{1}{\sqrt{2}} d_I(t) \cos\left(2\pi f_{ot} t + \frac{\pi}{4}\right) + \frac{1}{\sqrt{2}} d_Q(t) \sin\left(2\pi f_{ot} t + \frac{\pi}{4}\right) \quad (2.2)$$

$$\text{Qui peut être écrite comme: } s(t) = \frac{1}{\sqrt{2}} d_I(t) \cos(w_{ot} t + \theta(t)) \quad (2.3)$$

Les signaux  $d_I$  et  $d_Q$  sont modulés en amplitude par la fonction cosinus avec une amplitude de +1 ou -1, qui équivaut à un décalage de phase de cosinus ou de sinus de 0 ou  $\pi$ , où les deux étant orthogonaux. La somme de ces deux signaux orthogonaux résulte une

onde modulée QPSK, où la valeur de  $\Theta(t)$  correspond à l'une des quatre combinaisons de  $d_I$  et  $d_Q$ :  $0^\circ, \pm 90^\circ, 180^\circ$ .

La technique de modulation O-QPSK peut être représentée de la même manière. La différence est dans un décalage temporel dans le signal  $d_Q$ . La durée de chaque impulsion d'origine  $d_k(t)$  est de  $T$  et les deux signaux sont distincts de  $2T$ . En QPSK, les impulsions paires et impaires sont transmises à un débit de  $1/2T$  bits/s, elles sont alignées de telle sorte que leurs transitions coïncident. Dans O-QPSK, le signal  $d_Q$  se décale d'une période de temps  $T$ .

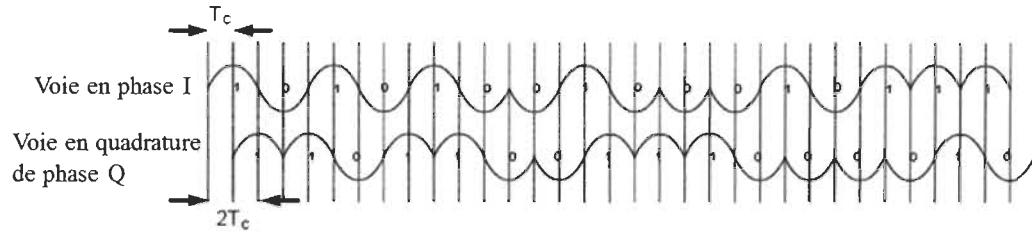

Figure 2.2 : Les changements de phase dans QPSK et O-QPSK (adaptée de [17])

En QPSK, dans chaque période de  $2T$ , la phase peut changer. Si les deux signaux changent en même temps, nous obtenons un décalage de phase de  $180^\circ$  mais si nous la changeons à  $90^\circ$  et si nous ne la changeons pas, la phase reste la même. Le problème réside dans les changements de phase  $180^\circ$ : quand un signal de ce type passe à travers un filtre passe-bas, ces changements de phase se produisent avec de très grands changements d'amplitude qui est indésirable dans un système de communication.

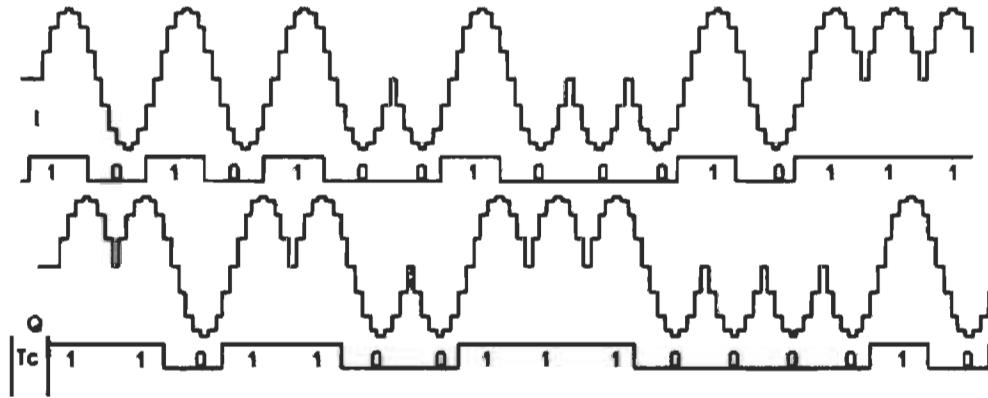

Figure 2.3 : Résultat de la modulation du symbole zéro (adaptée de [13])

En O-QPSK, il n'est pas possible que les deux signaux changent simultanément, vu que les changements de phase sont limités entre 0 et 90 ° (figure 2.2). Dans la figure 2.3, le symbole 0 du standard est modulé en O-QPSK. Vous pouvez trouver plus d'informations sur les avantages d'O-QPSK par rapport QPSK dans [16].

#### 2.2.4 *Estimation de la fréquence et correction de la phase dans le récepteur*

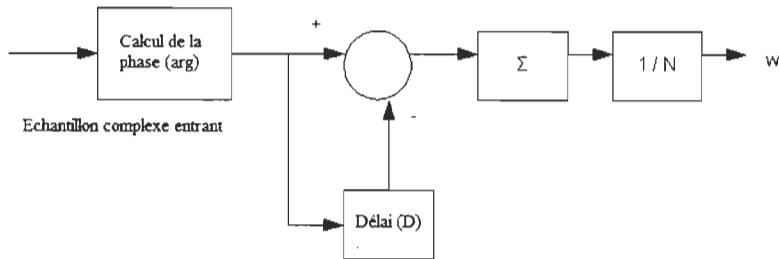

Dans un système de communication sans fil les imperfections des oscillateurs dans l'émetteur et le récepteur conduisent à un décalage dans le support qui est détecté dans le récepteur. Ce décalage provoque une rotation de la constellation du signal qui doit être corrigé pour obtenir les données originales dans le processus de la démodulation.

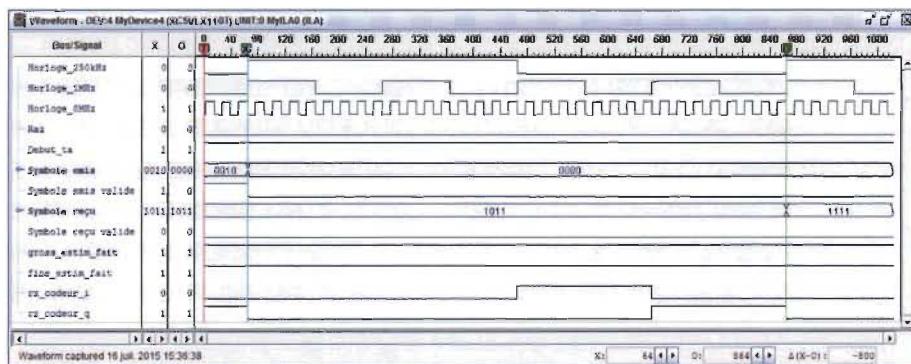

Le récepteur utilise l'action combinée de deux méthodes d'estimation de fréquence et de correction de phase. D'abord, nous utilisons l'estimateur de Kay pour faire une première estimation (grossière) et une fois que nous synchronisons avec les données reçues, nous faisons une deuxième estimation « fine » en sachant les données que nous devons obtenir.

Figure 2.4 : Esquisse d'estimation et de correction de phase

L'algorithme de Kay est un estimateur de fréquence pour les sinusoïdes complexes qui est basé sur la technique de la prédiction linéaire. Dans la partie de la démodulation du récepteur, les données reçues sont affectées par un bruit de nature gaussien qui se traduit par des décalages de phase. Ces données peuvent être interprétées comme des données erronées. L'algorithme de Kay nous permet de faire une correction «aveugle» des données entrantes, selon la valeur moyenne de la différence de phases entre les échantillons mesurés.

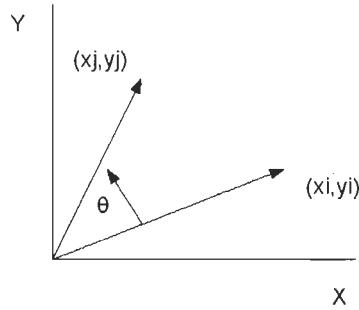

L'implémentation d'estimateur de Kay, utilise le module CORDIC (Coordinate Rotation Digital Computer) pour estimer les phases des échantillons entrants pendant la mesure et le mode rotationnel du CORDIC; une fois que la mesure est terminée et que la correction est exécutée.

Le CORDIC permet d'implémenter des fonctions élémentaires spécifiques (trigonométrique et hyperbolique) en utilisant une configuration matérielle minimale à l'aide des opérations de déplacements simples, comparaisons, additions et soustractions.

Le CORDIC fonctionne grâce à des rotations dans le domaine complexe selon des angles constantes, jusqu'à ce que l'angle soit réduit à zéro. Ces angles sont choisis de

manière que les rotations peuvent être implémentées par des déplacements, additions et soustractions.

L'article original qui décrit l'algorithme peut être trouvé dans [20] et une généralisation de celui-ci dans [21]. Les différentes façons d'implémentation dans le matériel peuvent être trouvées dans [22].

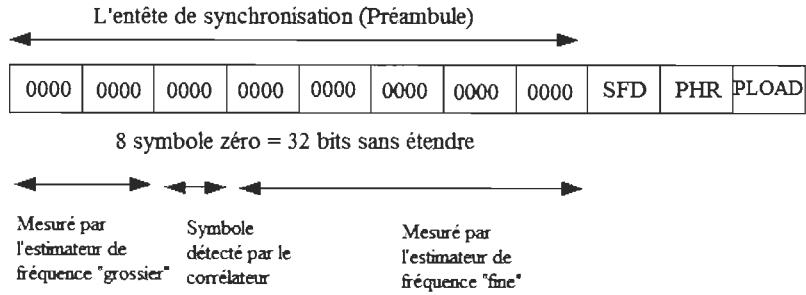

L'estimation « fine » utilise une implémentation du CORDIC pour mesurer et faire tourner les échantillons, en contraste les mesures avec une table des phases prévues (avec les données qui doivent être reçues). Vous pouvez voir un aperçu des différentes parties du préambule qui traite chaque estimateur dans la figure précédente.

La trame PDU de la norme contient un préambule de 8 symboles zéro qui servent à synchroniser avec les données reçues. Une fois que nous détectons l'un des symboles zéro, nous ne pouvons qu'espérer pour détecter le champ SFD pour être complètement sûr que nous sommes synchronisés avec l'émetteur.

Il existe de nombreuses façons de combiner les deux estimateurs, utilisant plus ou moins une partie du préambule pour une meilleure estimation et une synchronisation avec les données reçues.

Dans ce cas, nous supposons que le corrélateur est incapable de détecter le symbole zéro qui se trouve dans la troisième position du préambule. C'est le troisième symbole zéro de l'en-tête de synchronisation. Par conséquent, l'estimateur de fréquence « grossier » effectue l'estimation durant les deux premiers symboles zéro du préambule, qui sont étendus et ils ont traversés le sous-échantillonneur, 256 chips à mesurer. Puis, l'estimateur

pas à corriger les phases des échantillons entrants suivants, en espérant que le corrélateur soit capable de détecter après le symbole zéro suivant.

Une fois que le corrélateur détecte un symbole zéro, et il sait que les échantillons suivants font partie du préambule et les données connues (symboles zéro de la norme), l'estimateur de fréquence «fin» est activé, qui estime jusqu'à ce que le préambule se termine (la comparaison des phases avec les données prévues). Lorsque l'estimateur «fin» termine l'estimation, il commence à corriger les échantillons entrants. Enfin, une fois le corrélateur détecte le champ SFD, nous sommes pleinement confiants de la synchronisation avec l'émetteur.

Pour plus d'informations sur l'estimateur de Kay ainsi que le module CORDIC, veuillez consulter l'annexe A.

#### 2.2.5 *L'indicateur de puissance du signal reçu (RSSI)*

L'indicateur du système de niveau du signal ou RSSI (Received Signal Strength Indicator) peut être implémenté en utilisant le module CORDIC. Le CORDIC en mode vectoriel nous permet de convertir une valeur complexe de forme cartésienne en forme polaire (modulo, phase). Si vous vous souvenez, la formule de RSSI est donnée par :

$$RSSI = \frac{1}{N} \sum_{n=0}^{N-1} |m(n)|^2 = \frac{1}{N} \sum_{n=0}^{N-1} s_I^2(n) + s_Q^2(n) \quad (2.4)$$

Donc, nous accumulons juste le module des échantillons entrants (calculé avec le CORDIC rotationnel) pour N échantillons et à la fin, nous divisons par N échantillons. Cette division peut être implémentée par un décalage vers la droite si le nombre d'échantillons N est une puissance de 2.

### 2.3 Les architectures spécifiées par la norme

Dans ce qui suit, nous focalisons sur les différentes architectures définies par la norme IEEE 802.15.4 et plus particulièrement pour la bande 915 MHz et la bande 2.45 GHz.

#### 2.3.1 L'architecture de la chaîne en bande de base pour la bande 2.45 GHz

Premièrement, nous allons parler sur la chaîne de transmission en bande de base spécifiée par la norme comme la montre la figure 2.5, elle est définie pour la bande 2.45 GHz. Pour plus des détails, veuillez consulter les références [10], [11], [1], [12], [9], et [13].

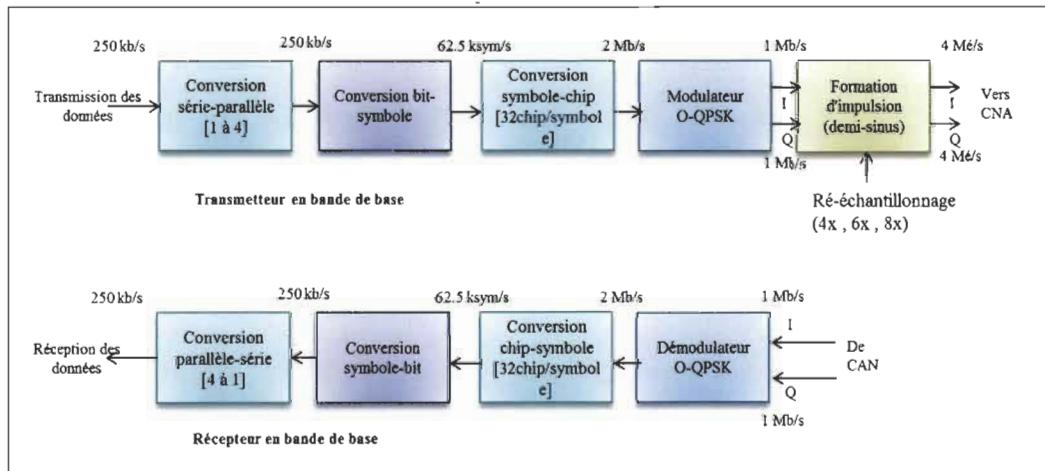

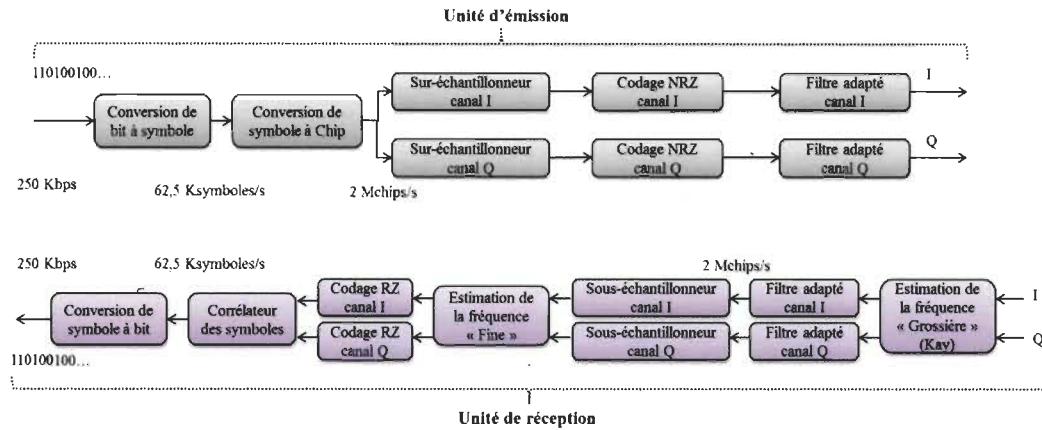

Figure 2.5 : L'architecture pour la bande 2.45 GHz (adaptée de [12])

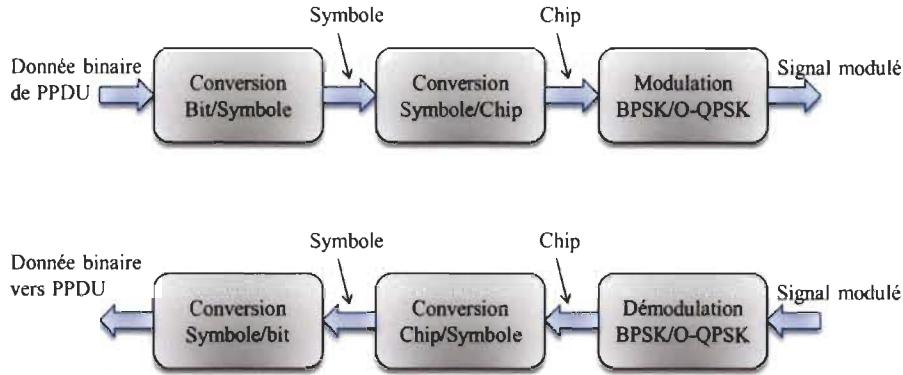

Nous voyons bien dans la figure 2.5 que l'acheminement des données se fait sur la voie en phase I et la voie en quadrature de phase Q, que ce soit pour la chaîne d'émission ou la chaîne de réception. Dans la chaîne d'émission, après la réception du paquet (les données d'entrée viennent sous forme des paquets PPDU de la couche MAC dans la pile protocolaire de l'IEEE 802.15.4), nous le passons dans un bloc qui n'est pas mentionné dans la figure. En effet, un bloc qui sert à convertir le mode de transmission du flux binaire

série au mode parallèle (1 à 4) avec un débit binaire de 250 kbps, il s'agit d'une conversion d'un flux binaire à une représentation en symbole pour avoir à la sortie un taux de 62.5 ksymbole/s. Comme le montre la figure, la chaîne d'émission commence par un bloc dédié pour la conversion (32 chip/s) ou le mappage du symbole (avec un taux de 62.5 ksymbole/s) vers une représentation en chip (le taux est de 2 Mchip/s, avec 1 Mchip/s par canal), nous suivons la chaîne par un sur-échantillonneur avec un facteur égal à 8, pour avoir en sortie un taux de 8 Mé/s sur chaque canal (I et Q). La chaîne se termine par un bloc de filtrage de mise en forme de l'impulsion que nous pouvons l'injecter dans le convertisseur numérique-analogique pour un post-traitement analogique (module RF). Pareillement pour la chaîne de réception, nous avons juste les blocs inverses. Pour plus de détails, consultez les références [7] et [8].

L'architecture est composée de :

- Convertisseur série-parallèle qui convertie les données en série vers des données en parallèle.

- Convertisseur bit-symbole qui convertie les données en parallèle (4 bits de 250 Kbps) vers un symbole (de 62.5 Ksps).

- Convertisseur symbole-chip (également par DSSS) qui mappe le symbole vers 16 séquences de 32 chip (Tableau 2-2). Dans l'implémentation du système de modulation O-QPSK, l'émetteur fait le mappage de bits 1 et 0 pour 0 à 15 symboles, et les symboles (de 0 à 15) sont mappés à 16 séquences chips de 32 bits (bruit pseudo-aléatoire).

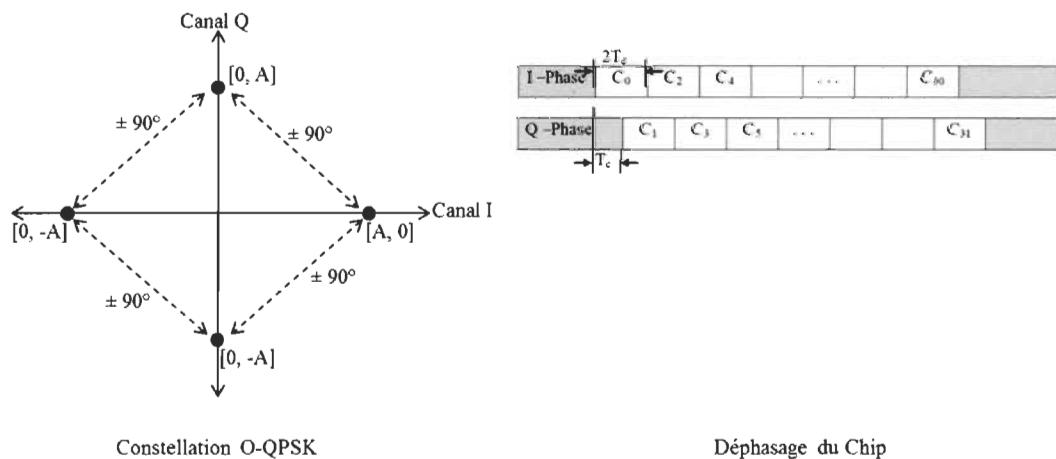

- Modulateur O-QPSK : transmet une séquence chip de 1 Mcps par les canaux I et Q à travers ce processus de modulation (une séquence de 16 chips sur chaque canal)

→ Ce schéma de modulation possède un maximum de déphasage de  $\pm 90^\circ$ . La figure 2.6 nous montre la constellation et le décalage de phase du Chip pour la modulation O-QPSK. Chaque chip pair de la séquence PN est modulé sur la porteuse en phase (I); tandis que chaque chip impair de la séquence PN est modulé sur la porteuse en quadrature de phase (Q). Surtout, les chips sur la voie Q sont décalés de  $T_c$  (l'inverse du taux de chip) par rapport aux chips sur la voie I en créant un décalage de phase et la modulation est dite O-QPSK.

Figure 2.6 : La modulation O-QPSK (adaptée de [9] et [12])

- La formation d'impulsion de demi-sinus qui représente un filtre de mise en forme. La figure 2.7 illustre les échantillons des séquences chip en bande de base avec le filtrage de formation d'impulsion.

Figure 2.7 : Le filtrage de formation d'impulsion (adaptée de [9])

Le filtre de formation d'impulsion de demi-sinus change le diagramme de transition d'O-QPSK d'un carré à un cercle. Il supprime les variations d'amplitude et tourne donc O-QPSK en modulation à enveloppe constante. L'équation est utilisée pour chaque chip de bande de base par ce filtre est montrée ci-dessous, elle est décrite en détails dans [9].

$$P(t) = \begin{cases} \sin\left(\pi \frac{t}{2T_c}\right), & 0 \leq t \leq 2T_c \\ 0, & \text{autrement} \end{cases} \quad (2.5)$$

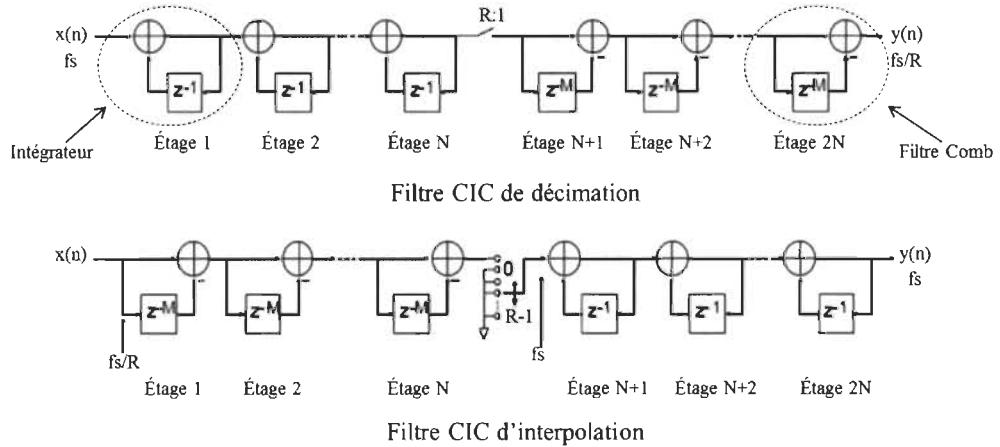

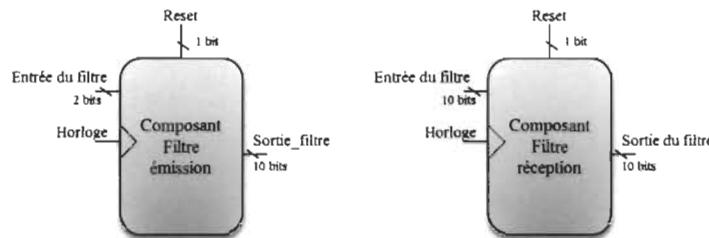

La figure 2.8 schématise les deux filtres numériques en bande de base que ce soit en émission (interpolation) ou en réception (décimation).

Figure 2.8 : Le filtrage numérique (adaptée de [14])

L'implémentation du filtre FIR est en forme directe. Pour obtenir la sortie, le filtre est basé seulement sur les données de l'entrée actuelle et les antérieures. La sortie du filtre peut être exprimée simplement comme la convolution du signal d'entrée avec la réponse impulsionnelle du filtre:

$$y(n) = \sum_{k=0}^{M-1} h(k)x(n-k) \quad (2.6)$$

Où  $M$  est l'ordre du filtre,  $h(k)$  sont les coefficients,  $x$  est l'entrée et  $y$  la sortie du filtre. Pour chacun des canaux I et Q, il existe un filtre séparé.

Les opérations du filtre sont limitées à l'addition, la soustraction et le déplacement étant donné que les données entrantes sont 1, -1 ou 0, oubliant la multiplication par les coefficients. L'implémentation du filtre est basée sur la référence [14].

Le filtre de réception est identique à l'émission, permettant une bonne valeur du SNR pour que le codeur RZ puisse faire la distinction entre 1 ou 0 avec plus de probabilité de succès.

- Démodulateur O-QPSK : il effectue un processus de synchronisation afin de connaître le début de la séquence chip reçue (démodulation non cohérente).

- ➔ Les données démodulées sont traitées par l'inverse du processus de transmission (conversion chip-symbole, conversion symbole-bit, et conversion parallèle-série).

- ➔ Le taux de transmission supporté : 1 Mbps / 2 Mbps ➔ la méthode de diminution du taux d'étalement à travers la modification du convertisseur série-parallèle, convertisseur bit-symbole, et convertisseur symbole-chip.

Par exemple : pour le taux 1 Mbps  $\rightarrow$  nous avons une conversion vers 16 séquences de 8 chips, tel que la longueur de la séquence chip transmise sur les canaux I et Q, est égale à 4 (16 séquences de 4 chips sur I et 16 séquences de 4 chips sur Q).

→ Le système peut augmenter le taux de transmission sur la même largeur de bande utilisant 8-PSK, QAM, ou un système multicode, mais, il est très complexe parce qu'il n'y a plus de séparation du pilot canal (l'erreur de la haute fréquence).

La référence [9] incite sur la conception et l'implémentation de l'émetteur / récepteur pour la norme IEEE 802.15.4 en utilisant MATLAB. Il a implémenté la séquence directe d'étalement du spectre (DSSS) utilisant la modulation (O-QPSK) avec la mise en forme de demi-impulsion sinusoïdale. La référence [11] incite sur la mise en œuvre de l'émetteur / récepteur du protocole ZigBee avec ses spécifications. Il a utilisé Matlab / Simulink pour la modélisation, sans recourir aux blocs mathématiques complexes.

Concernant la partie frontale analogique, la chaîne pour le sens montant peut contenir des filtres passe-bas intermédiaires, un étage d'amplification de puissance du signal, voire même un mélangeur des signaux, en se référant à un oscillateur local qui nous fixe la bande de fréquence (micro-onde dans notre cas). Le modulateur nous permet de transposer la fréquence en bande de base (après conversion en signal analogique) vers une autre plus haute, qui peut être du type QPSK ou O-QPSK. Cette dernière doit être autour de la fréquence de l'oscillateur local.

### 2.3.2 L'architecture de la chaîne en bande de base pour la bande 915 MHz

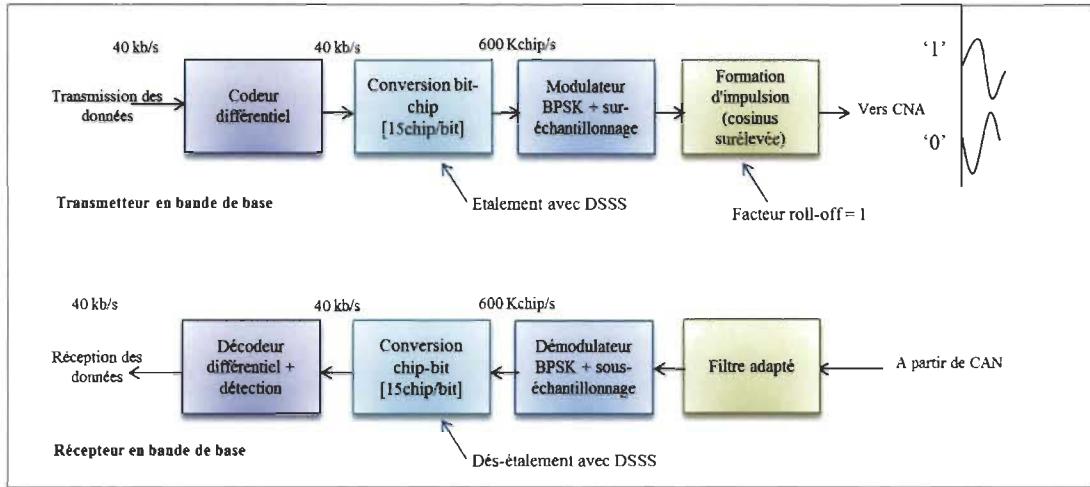

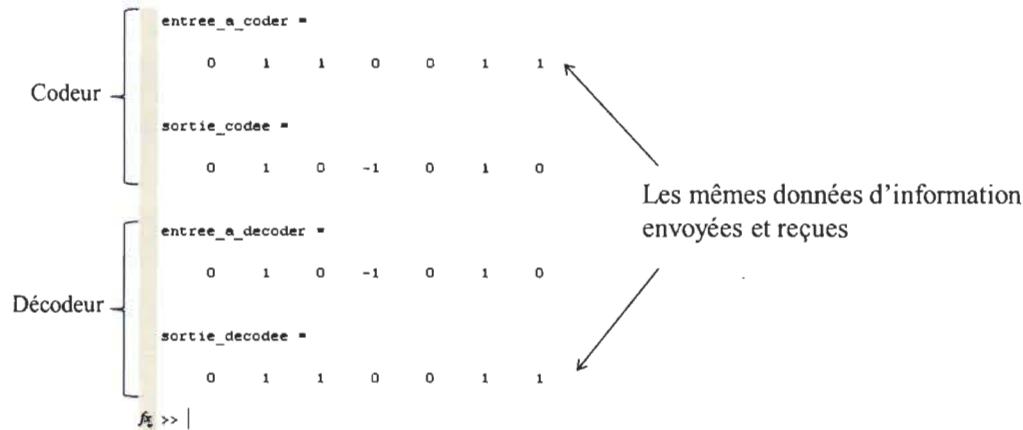

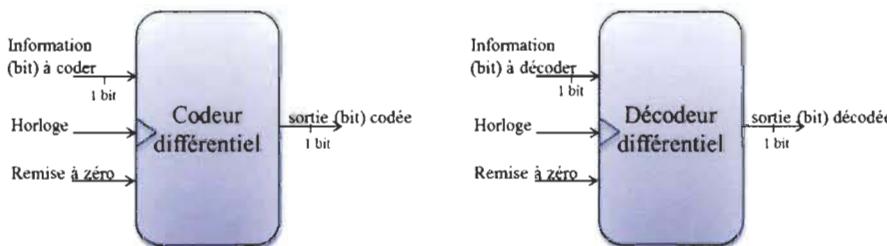

La figure 2.9 illustre l'architecture de la chaîne d'émission et réception en bande de base pour la bande 915 MHz, elle utilise la modulation BPSK et un codage différentiel.

Figure 2.9 : L'architecture pour la bande 915 MHz (adaptée de [10])

Le but du codage différentiel est de résoudre le problème d'ambiguïté sur la phase au niveau du récepteur. En effet, en codage :  $E_n = R_n \text{ xor } E_{n-1}$  tel que :  $R_1$  est le premier bit de données à coder et  $E_0 = 0$ , avec :

$R_n$  : premier bit des données étant codé;

$E_n$  : bit correspondant codé différentiellement;

$E_{n-1}$  : bit précédent codé différentiellement.

Pour le décodage :  $R_n = E_n \text{ xor } E_{n-1}$  tel que :  $E_1$  est le premier à décoder et  $E_0 = 0$ .

Le tableau 2-4 explique le mappage du bit vers 2 séquences de 15 chips utilisant un étalement par DSSS.

$T_c = T_b / N$  ; avec  $T_c$  : durée du chip,  $T_b$  : période du bit,  $N$  : longueur du code.

Tableau 2-4 : Pour les bandes 868/915 MHz avec BPSK (adaptée de [1] et [9])

| Les bits en entrée | Valeurs du Chip ( $c_0 c_1 \dots c_{14}$ ) |

|--------------------|--------------------------------------------|

| 0                  | 111101011001000                            |

| 1                  | 000010100110111                            |

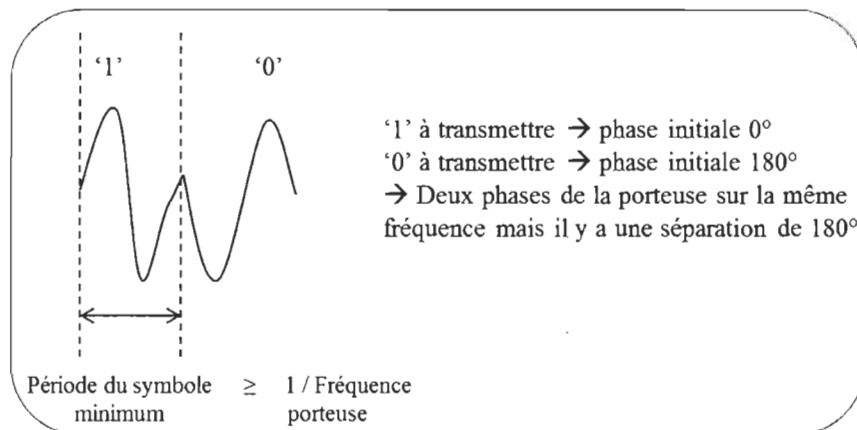

Concernant la modulation BPSK (expliquée sur la figure 2.10), elle consiste à avoir une fréquence d'échantillonnage  $\geq 10 \times$  Fréquence porteuse; à la réception : le décodeur symbole extrait le temps symbole et les valeurs du symbole du signal BPSK reçu (période symbole et seuil). La période symbole est le nombre entier de cycles d'horloges pour une fréquence d'échantillonnage choisie. Le seuil est l'amplitude relative, qui détermine la présence du symbole (0 ou 1) dans le décodeur (si le seuil diminue  $\rightarrow$  la sensibilité du décodeur augmente et si le seuil augmente  $\rightarrow$  la sensibilité du décodeur diminue).

Figure 2.10 : La modulation BPSK

Le filtre de formation d'impulsion en cosinus surélevée (en supposant que le coefficient de retombée = 1) a la particularité de ne pas produire d'interférence entre symboles et d'être à support spectral borné; il est exprimé par l'équation suivante :

$$p(t) = \begin{cases} \frac{\sin \frac{\pi t}{T_c}}{\frac{\pi t}{T_c}} \times \frac{\cos \frac{\pi t}{T_c}}{1 - \frac{4t^2}{T_c^2}}, & t \neq 0 \\ 1, & t = 0 \end{cases} \quad (2.7)$$

## 2.4 La reconfiguration par le circuit programmable FPGA

Nous savons bien, que tous les éléments logiques dans les FPGA peuvent s'exécuter en parallèle. Cela inclut les multiplicateurs matériels et nous pouvons maintenant obtenir plus de 1000 d'entre eux sur un seul FPGA. Ceci est en contraste avec les processeurs TSN programmables, qui ont généralement quelques multiplicateurs et ils doivent être exploités de manière séquentielle.

Les FPGA ont désormais des interfaces série et parallèle spécialisées, pour répondre aux exigences des périphériques à haute vitesse et des bus.

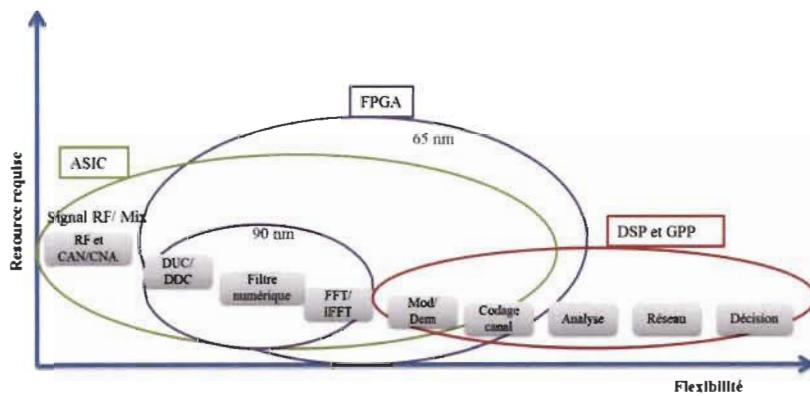

Figure 2.11 : Les tâches des applications en communication (adaptée de [9], [10] et [11])

Ce que nous entendons par intensité du processus (figure 2.11) est le degré d'opérations fortement répétitives et assez primitives. En haut à gauche, ce sont les fonctions dédiées comme des convertisseurs CAN et CNA, et aussi les DDC (les convertisseurs-abaisseurs de

fréquence numérique ou Digital Down Converter en anglais) et DUC (les convertisseurs-élévateurs de fréquence numérique ou Digital Up Converter en anglais), ces derniers nécessitent des structures matérielles spécialisées pour exécuter les opérations en temps réel.

La flexibilité concerne l'unicité ou la variabilité du traitement, et de la façon dont la fonction peut être modifiée ou adaptée pour toute application spécifique. En bas à droite ce sont des tâches telles que l'analyse et la prise de décision; qui sont très variables et souvent subjectives.

Les processeurs programmables à usage général (GPP) ou les DSP, sont généralement choisis pour ces tâches, puisque ces tâches peuvent être facilement modifiées par logiciel.

En conséquence, les FPGAs ont considérablement envahi l'espace des tâches d'application, comme indiqué par la bulle centrale dans le diagramme des tâches ci-dessus. Ils offrent des avantages du parallélisme matériel, pour traiter certaines fonctions à processus de haute intensité comme le DDC; et le bénéfice de programmation pour accueillir une partie du décodage et d'analyse des processeurs de TNS (DSP).

Ces avantages peuvent se faire au détriment de la dissipation de puissance accrue et les coûts de production plus élevés. Toutefois, ces considérations sont souvent secondaires à la performance et aux capacités de ces dispositifs remarquables.

Il y a certains paramètres à identifier qui servent à la configuration d'un système de communication, nous citons les paramètres clés (à titre d'exemple) comme suit :

- La méthode d'échantillonnage : elle décrit si le système permet un échantillonnage d'un signal complexe en I et Q (échantillonnage en quadrature),

ou tout simplement d'un signal réel. Dans le premier cas, ça nécessite deux convertisseurs CAN/CNA (ou un CAN/CNA multi canaux), et dans le second seulement un CAN/CNA est requis.

- Le dispositif d'échantillonnage : ce paramètre décrit le type de périphérique d'échantillonnage qui est utilisé dans le système. Ça peut être une carte son d'ordinateur, un CAN/CNA audio dédié, une carte d'acquisition dédiée, un CAN/CNA RF dédié, ou un ASIC dédié spécialisé au traitement frontal analogique à fréquence intermédiaire.

- Le mélangeur analogique : Certains systèmes ne sont pas entièrement numériques, car un convertisseur-abaisseur analogique de fréquence ou un convertisseur-élévateur analogique de fréquence est fait avant que l'échantillonnage s'effectue. S'il existe, ce mélange analogique peut être programmable à partir de l'ordinateur, ou parfois il n'est pas programmable (fixe). Nous pouvons rencontrer les scénarios suivants :

- La fréquence peut être fixée par un oscillateur local OL (il n'est pas programmable par logiciel ou programmable manuellement) ;

- Ou l'OL est programmable, et réalisé par une puce VCO et PLL (par exemple LMX2486, LMX1501A, MC145170) ;

- Ou l'OL est programmable, et réalisé par un DDS sur un ASIC (par exemple: AD9958/59, AD9951, AD9854, AD9851) ;

- Ou même l'OL est programmable, et réalisé par un DDS sur un FPGA (puce programmable).

- La sélection de la chaîne numérique : l'échantillonnage est accompli avec un taux élevé afin de numériser une dimension du spectre beaucoup plus large que la bande occupée par un seul canal interne. La sélection du canal est alors effectuée numériquement par le convertisseur-abaisseur numérique de fréquence qui représente une combinaison de mélange numérique, de filtrage et de décimation (ou interpolation). Ce paramètre décrit comment la sélection de la chaîne numérique est atteinte. Nous trouvons le choix de:

- La sélection du canal numérique se fait avec un FPGA ;

- La sélection du canal numérique se fait avec un ASIC (puce spécifique. Par exemple AD6620, AD6636, HSP50214, HSP50016) ;

- La sélection du canal numérique se fait par un ASIC spécialisé dédié pour le front end à FI avec les deux fonctions CAN et DDC (par exemple AFEDRI8201) ;

- La sélection du canal numérique se fait via le logiciel dans un PC ;

- La sélection du canal numérique se fait par une puce DSP Array ;

- Ou la sélection n'est pas possible, par exemple, lorsque la sélection du canal est faite dans le côté analogique et le côté à fréquence intermédiaire numérique de la largeur du canal souhaitée.

- Le transfert d'échantillons numériques vers l'ordinateur : il décrit la façon dont les échantillons numériques sont transférés vers l'ordinateur. Ça peut être par soit:

- Les échantillons numériques sont transférés vers le PC via l'interface USB ;

- Les échantillons numériques sont transférés vers le PC via l'interface Ethernet ;

- Les échantillons numériques sont transférés vers le PC à travers l'interface série RS232 par exemple ;

- Ou même les échantillons numériques ne sont pas transférés à un PC mais ils sont traités localement.

- Le contrôle du système : il décrit la façon dont le système est contrôlé à distance. Ce contrôle est par exemple nécessaire pour programmer l'oscillateur local (OL), le convertisseur abaisseur numérique de fréquence (DDC), ou le convertisseur élévateur numérique de fréquence (DUC). Ça peut être par un ordinateur via l'interface série, parallèle, USB, ou Ethernet. Nous pouvons aussi le contrôler localement à travers un processeur intégré (par exemple dans un FPGA).

## 2.5 Conclusion

Nous avons étudié dans cette partie du rapport la composition de la couche physique définie par le standard IEEE 802.15.4, à savoir la modulation O-QPSK, la technique d'étalement du spectre DSSS, et les architectures internes pour chaque bande de fréquence. Ainsi, nous avons décrit la configuration numérique d'un système de communication par un circuit programmable FPGA.

Le chapitre suivant mettra la lumière sur notre chaîne de communication proposée; dans ce dernier, nous présenterons les éléments essentiels de cette chaîne, ainsi que la méthodologie de conception et l'explication de la description en VHDL.

# Chapitre 3 - Chaîne de communication proposée

## 3.1 Introduction

Nous présentons dans ce chapitre la composition de notre chaîne de communication proposée. Nous présenterons les éléments essentiels de cette chaîne, ainsi que la méthodologie de conception et l'explication de la description en VHDL. L'annexe B contient une explication plus détaillée afin de comprendre l'architecture interne.

## 3.2 La composition de la chaîne proposée

Le but de notre travail est d'implémenter une chaîne d'émission / réception en bande de base (la couche physique du protocole de communication ZigBee). Nous jouons sur quelques paramètres de cette chaîne (comme le taux d'échantillonnage, le taux de transmission, la résolution du convertisseur) afin de la rendre flexible. Une version de nos travaux sera sur l'implémentation du contrôleur de notre chaîne basé sur la machine à état fini et l'étude de la trame binaire PDU venant de la couche MAC.

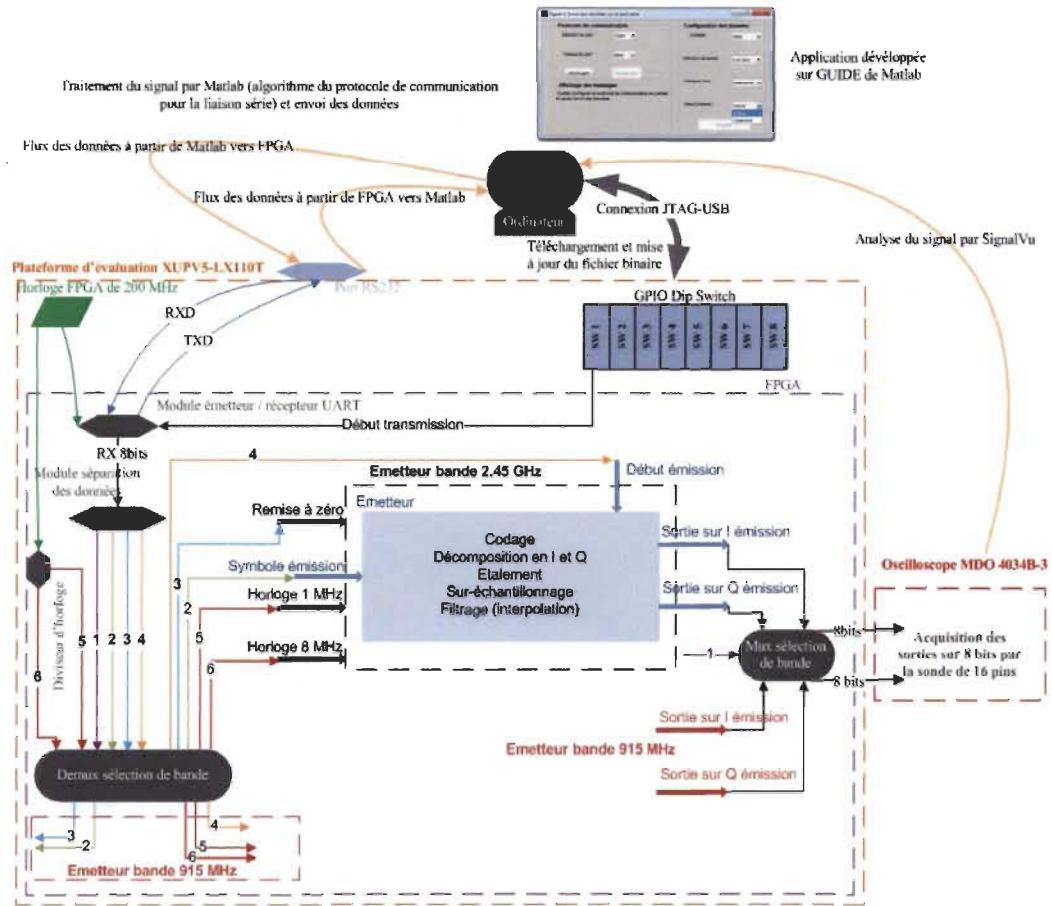

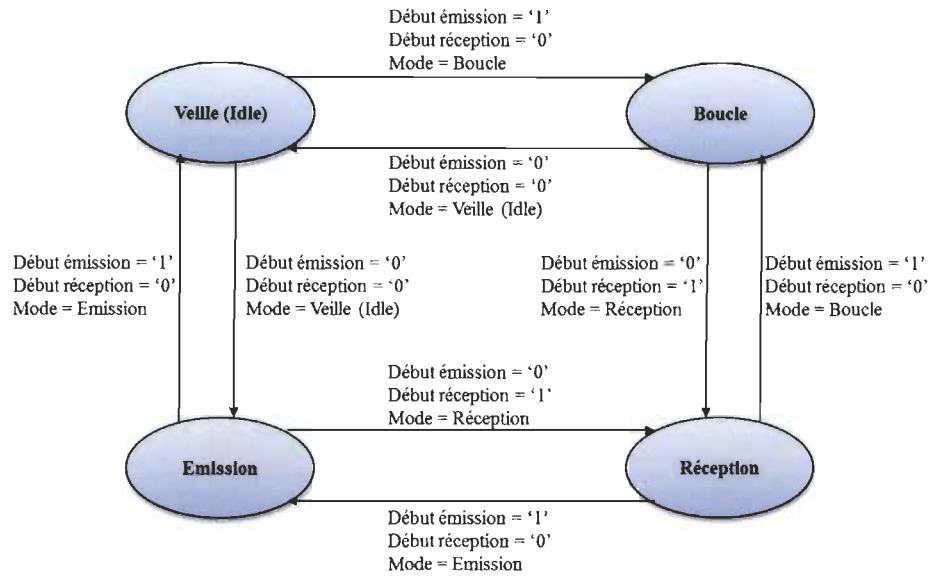

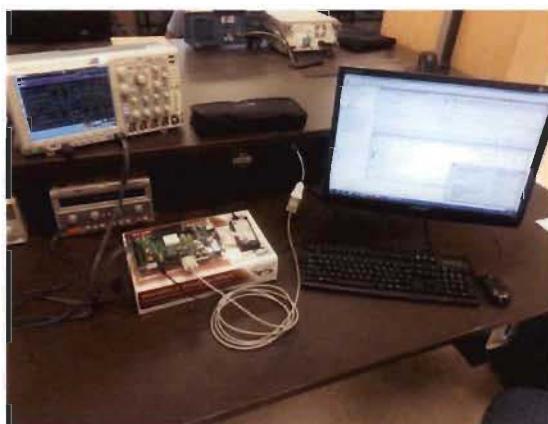

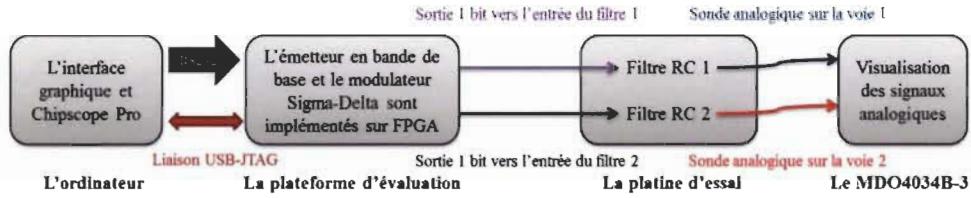

Tout d'abord, la chaîne est constituée de trois éléments essentiels : la partie analogique (étudiée pour le test au niveau de l'oscilloscope et l'analyseur du spectre pour la chaîne d'émission) qui se traduit par la chaîne de transmission RF (émetteur) et le convertisseur numérique/analogique, la partie numérique pour le traitement des signaux utilisant un FPGA, et le dernier élément comporte l'interfaçage avec l'ordinateur. L'ordinateur sert à contrôler et configurer la chaîne de communication et ainsi d'envoyer et de recevoir des

échantillons (dans notre cas, des symboles voire même une trame binaire), moyennant une communication serielle ou même à travers une liaison par câble USB.

Notre contribution dans ce projet est de faire la description en langage VHDL d'un émetteur/récepteur en bande de base (la couche physique) reconfigurable pour la bande 915 MHz et la bande 2.45 GHz, basant sur les architectures spécifiées par le protocole Zigbee. Les deux bandes utilisent le schéma de modulation O-QPSK (voire même QPSK sans conserver le décalage entre la composante en phase et la composante en quadrature de phase que ce soit en émission et en réception), elles seront implémentées avec la technique d'étalement du spectre DSSS (consultez le tableau 2-2 du deuxième chapitre). Nous nous intéressons aussi au développement de l'interface graphique pour communiquer avec la chaîne en bande de base; ainsi que, la mise en place d'un banc de test réel. Concernant la partie frontale analogique (étude du transmetteur seulement pour la bande 2.45 GHz), nous testons la partie numérique après la conversion des signaux numériques en signaux analogiques et aussi l'analyse spectrale après la modulation des signaux en bande de base. La troisième contribution consiste à, décrire en VHDL le contrôleur du mode de transmission basé sur une machine à état fini et ainsi d'étudier la trame PDU venant de la couche MAC.

### *3.2.1 Le premier travail à faire*

Nous implémentons la chaîne d'émission et de réception décrite dans la norme IEEE 802.15.4 [9].

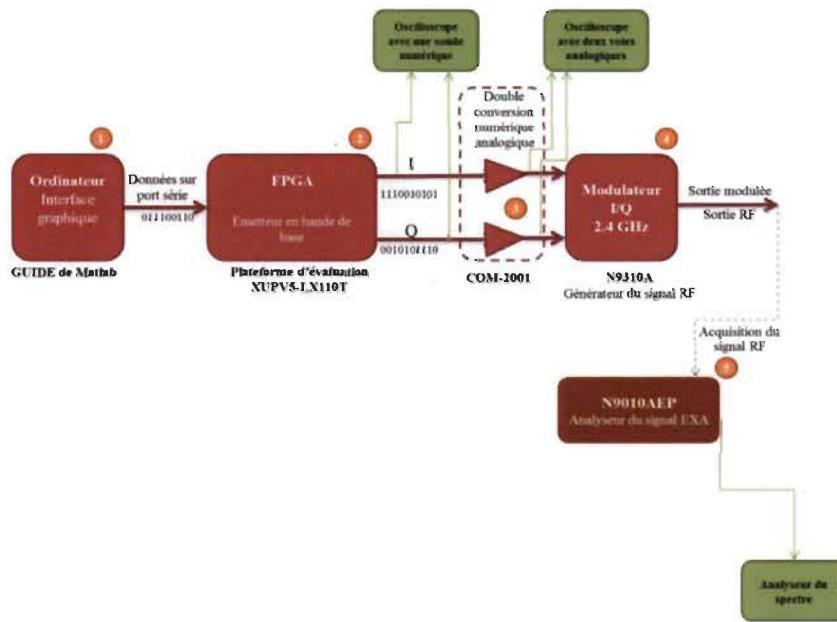

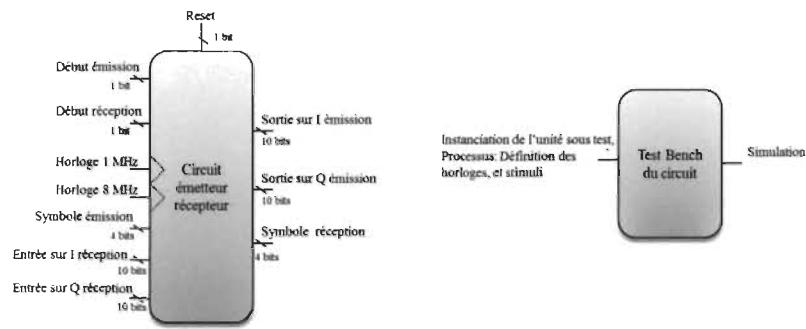

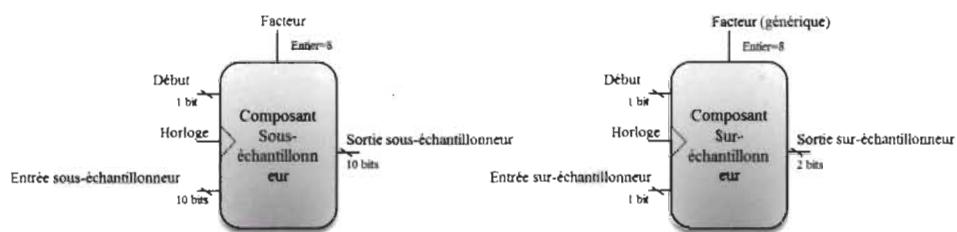

Figure 3.1 : L'architecture complète à implémenter (adaptée de [8] et [9])

La figure 3.1 représente l'architecture complète que nous allons l'implémenter au long de nos travaux, et comporte l'unité d'émission et de réception. Nous allons parler en détails sur cette architecture dans la section liée au troisième travail à faire.

Mais, dans un premier temps, (le premier travail) nous nous concentrerons sur l'architecture qui envoie un seul symbole sur la chaîne d'émission et qui reçoit un seul symbole après le passage par les blocs qui forment la chaîne de réception. Donc, dans cette sous-section, nous ne traitons pas les blocs liés à la conversion de bit à symbole et à la conversion du symbole à bit.

La partie frontale analogique (en anglais, Analog Front-end) n'est pas vraiment à concevoir, nous l'étudions juste pour le test réel sur un oscilloscope multi-domaine avec le post-traitement des signaux après la chaîne numérique ainsi que l'analyseur du spectre.

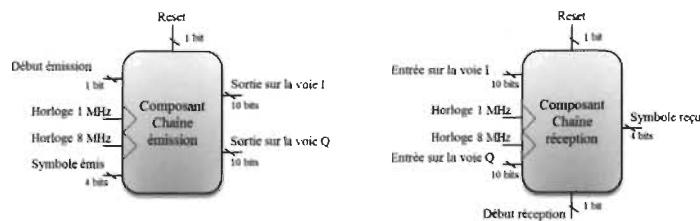

La partie sur FPGA est composée de deux chaînes en émission en bande de base qui sont implémentées : la première fonctionne sur la bande 915 MHz et la deuxième fonctionne sur 2.45 GHz.

La différence de deux bandes au niveau de la conception réside dans la conversion du symbole vers chip et la conversion du chip vers symbole ; consultez le deuxième chapitre pour plus des détails.

Figure 3.2 Schéma globale en émission

Donc nous faisons :

- L'acquisition des données numériques de deux sorties par l'oscilloscope MDO4034B-3 (existant à l'université) via une communication par la sonde de 16 bits;

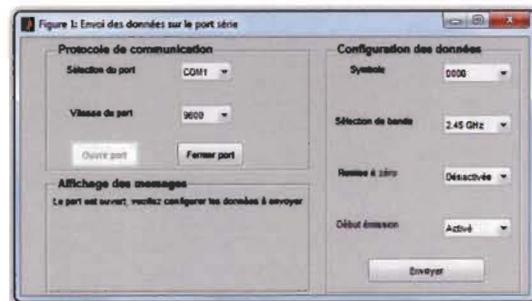

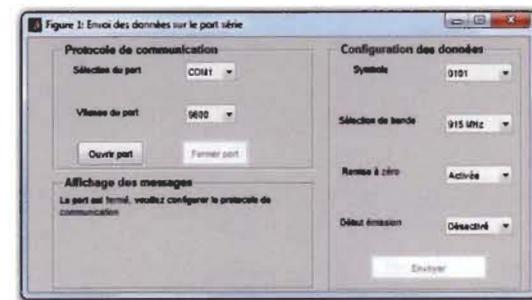

- La communication entre l'ordinateur et la plateforme d'évaluation, en envoyant une donnée à partir d'une interface graphique sous Matlab vers un FPGA (dans notre

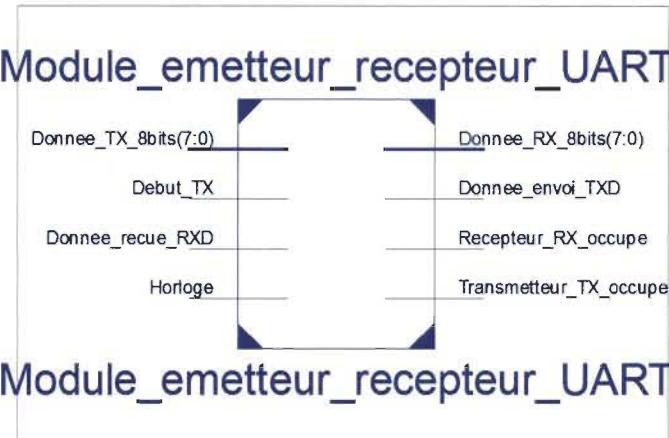

cas la configuration des entrées) et de recevoir une donnée (elle est testée seulement pour la boucle de retour), utilisant la liaison série via l'interface de communication UART (le développement de l'interface graphique est sur GUIDE de Matlab, il comprend l'algorithme du protocole de communication);

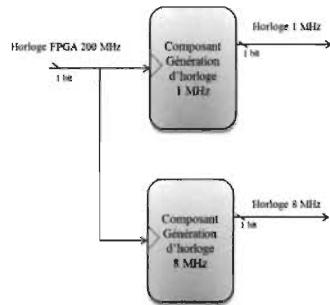

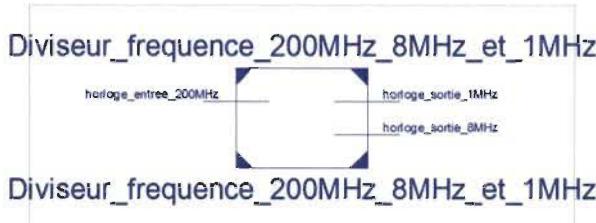

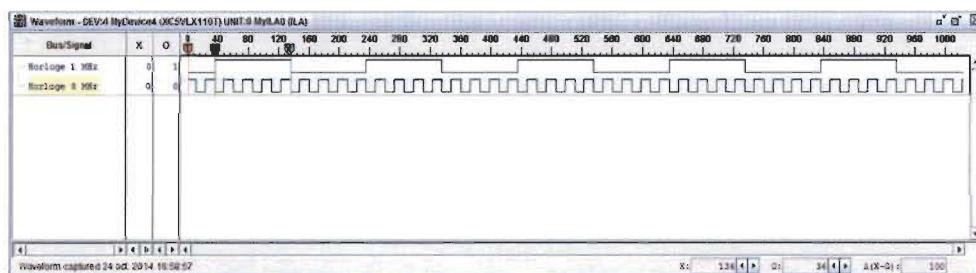

- La division d'horloge (description en VHDL) à partir de l'horloge FPGA 200 MHz vers les deux entrées d'horloge (8 MHz et 1 MHz);

- L'interfaçage du port série RS232 avec le FPGA via le module émetteur/récepteur UART (description en VHDL) ;

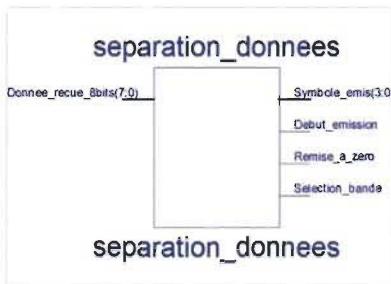

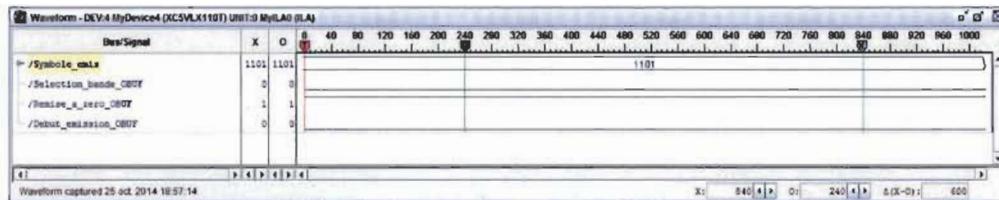

- La séparation des données venant du module UART vers les entrées à configurer (description en VHDL).

- L'adaptation des données de 4 bits à 8 bits juste pour le test de la boucle de retour (description en VHDL);

Donc tous ces modules numériques (à implémenter sur FPGA) sont décrits en VHDL.

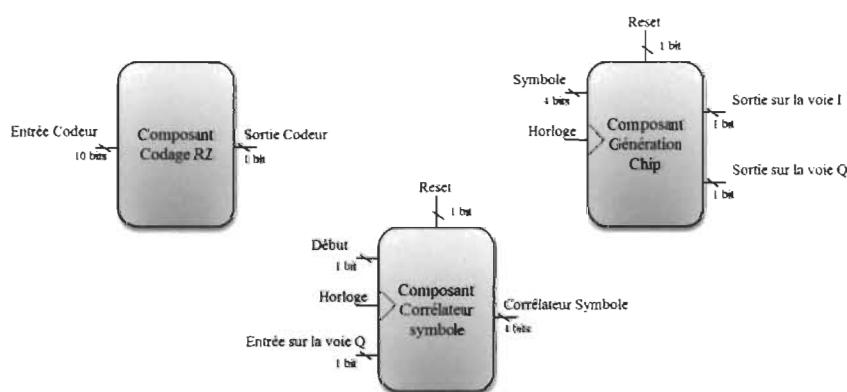

Pour plus des détails, nous avons mis dans l'annexe B une description détaillée de chaque bloc à concevoir.

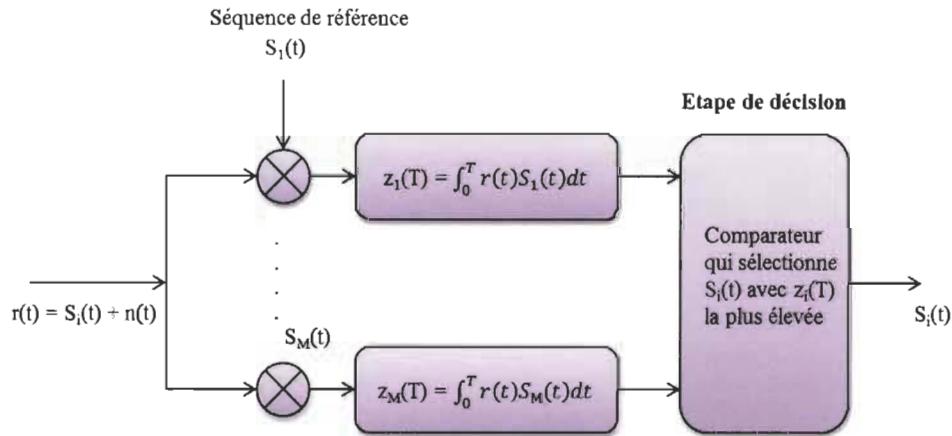

Le corrélateur de réception détecte les symboles de 4 bits du standard 802.15.4 à partir de l'entrée du codeur RZ. Il existe de nombreuses alternatives pour faire la détection des symboles. Dans notre cas, seules les données appartenant au canal Q sont utilisées, puisque nous utilisons seulement les données du canal I. Nous ne pourrions pas distinguer entre la première moitié des 16 symboles et la seconde (les séquences PN du canal I pour les huit premiers symboles sont identiques à celles des huit derniers).

Le corrélateur de réception est implémenté basant sur l'article [16] (figure 3.3). Le corrélateur comporte un registre qui stocke la séquence PN du symbole 0 pour le canal Q. Il peut générer chacune des séquences correspondantes aux 15 autres symboles (en une base similaire au générateur de chips de l'unité de l'émission).

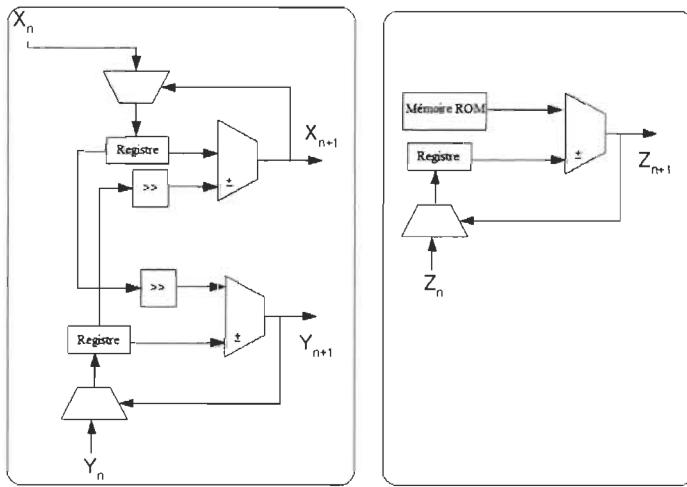

Figure 3.3 : Le corrélateur de réception (adaptée de [16])

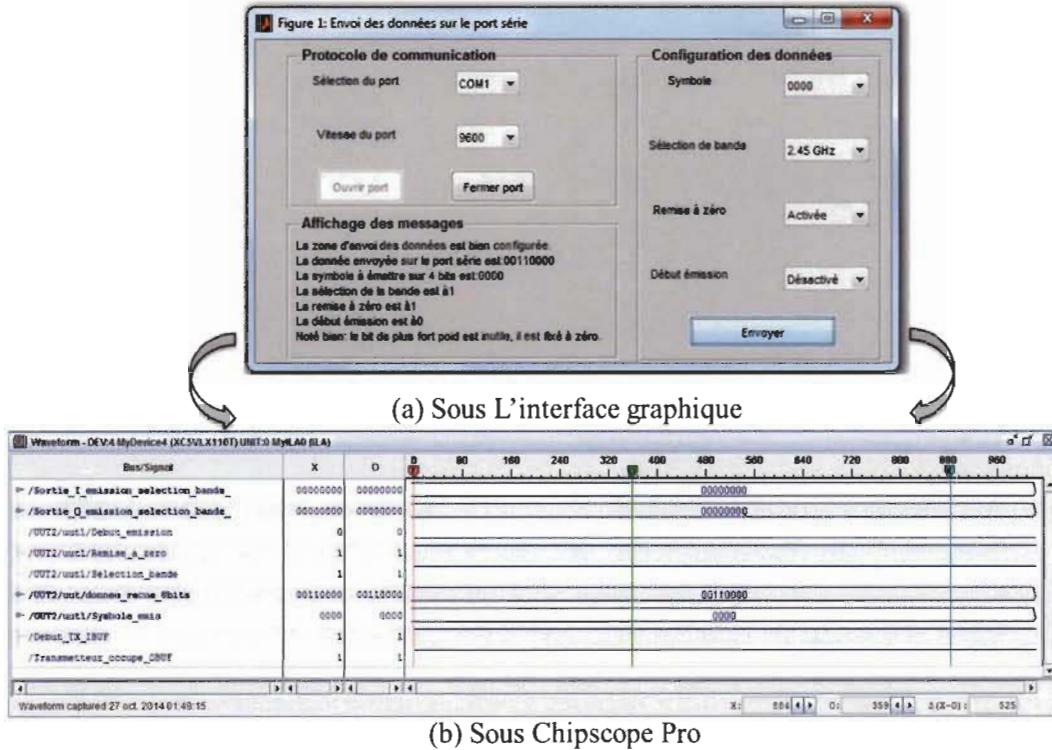

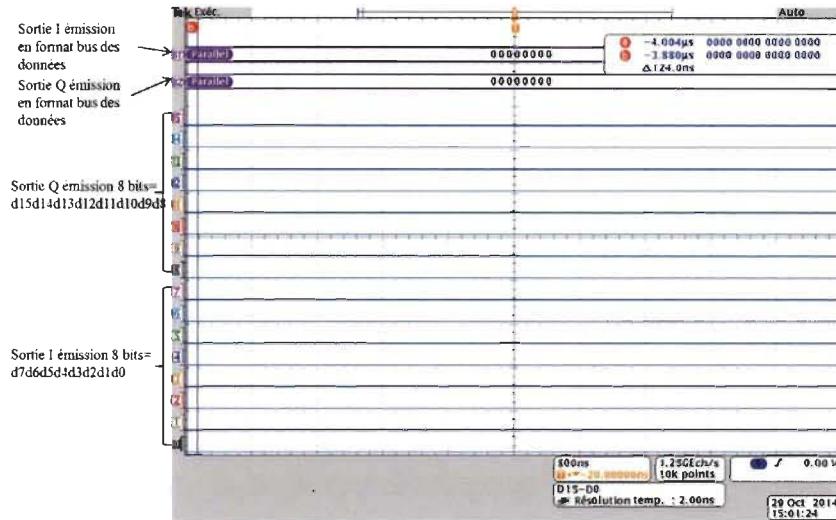

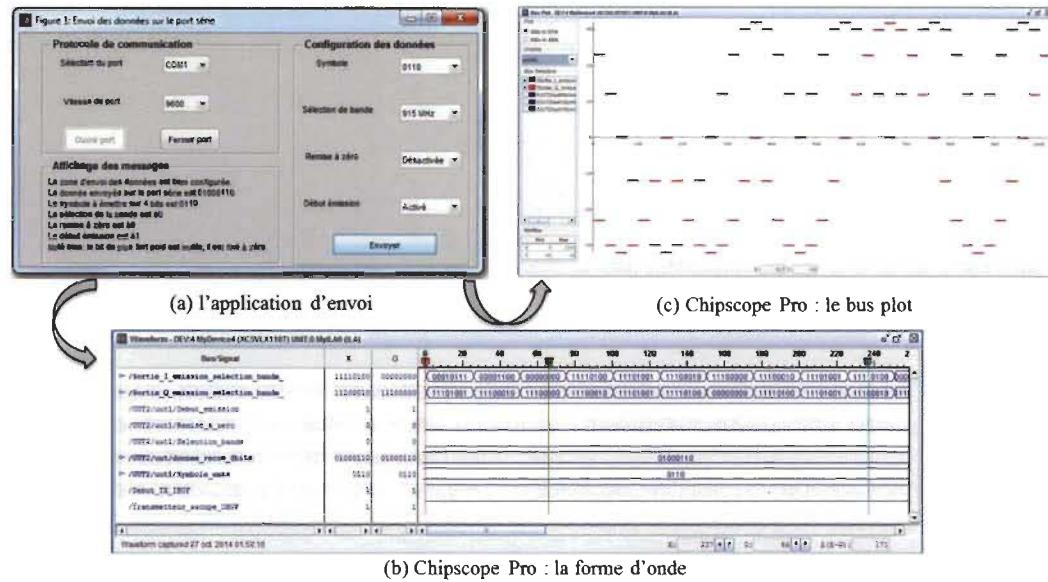

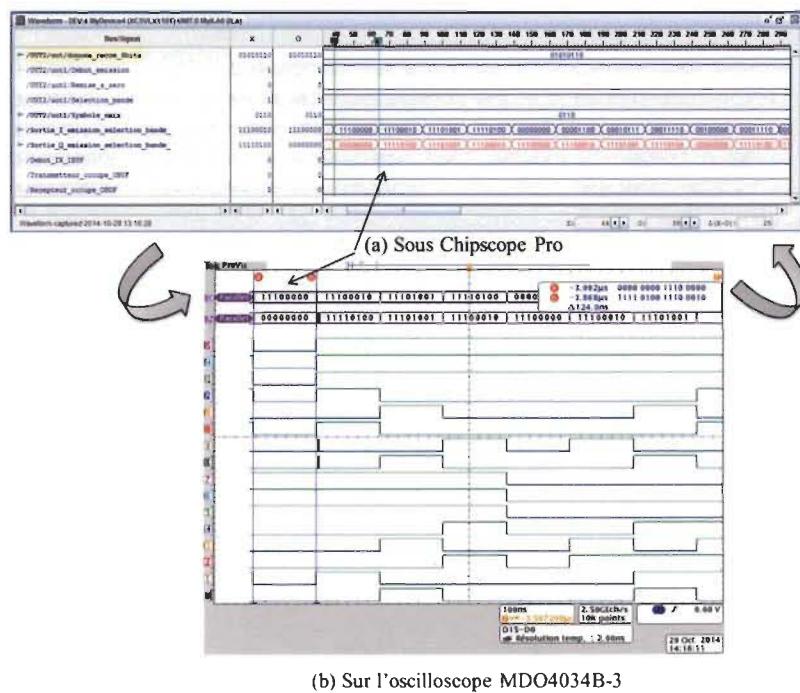

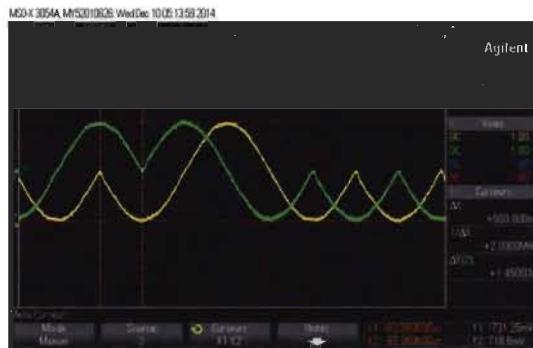

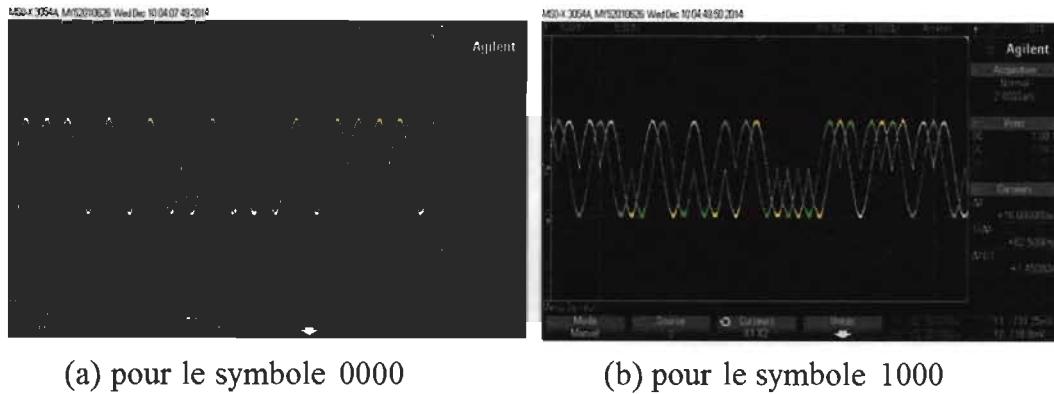

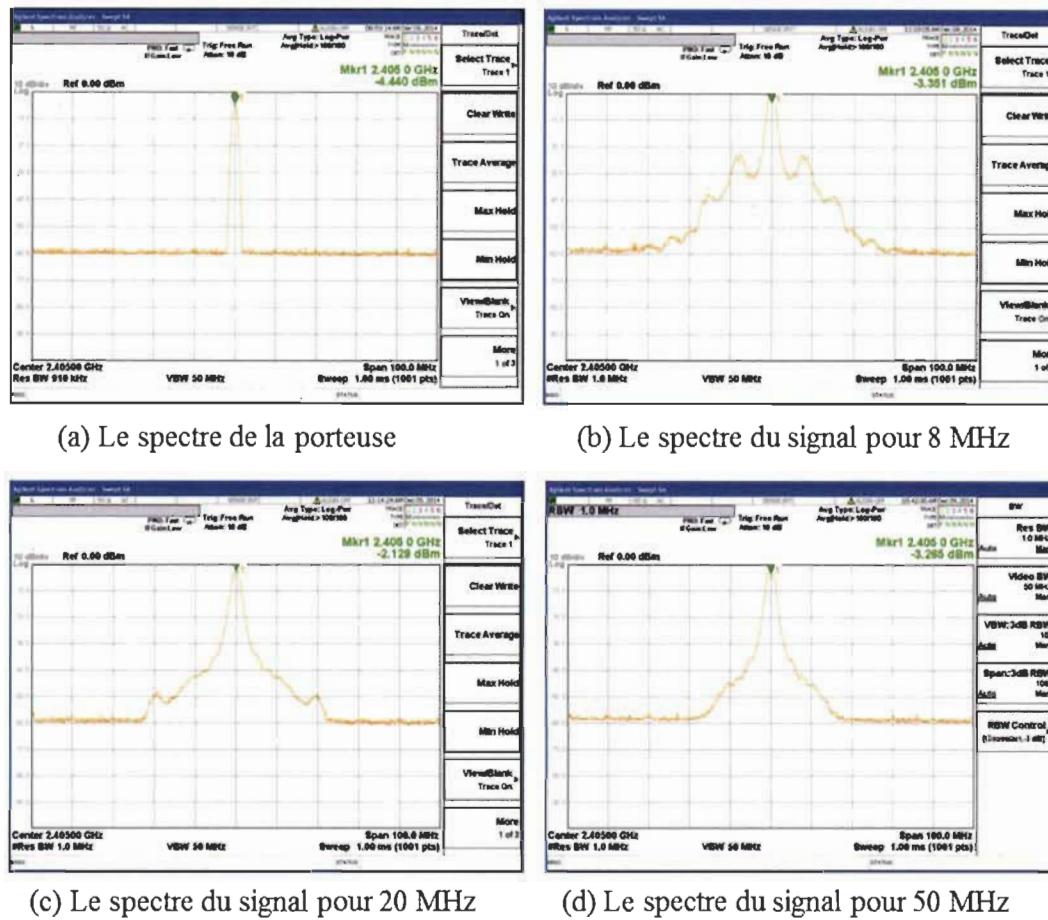

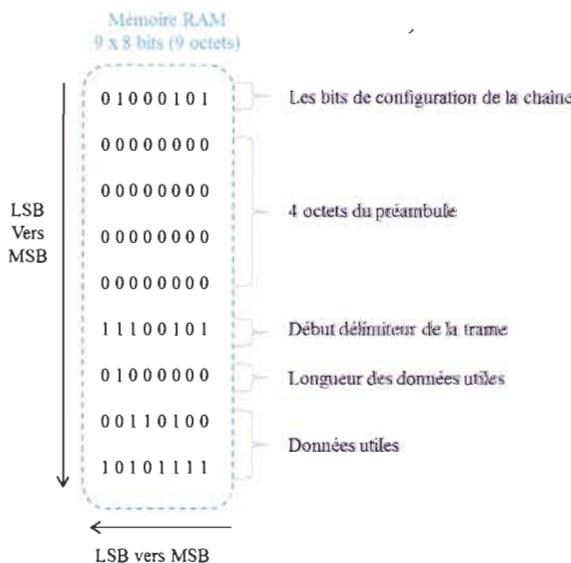

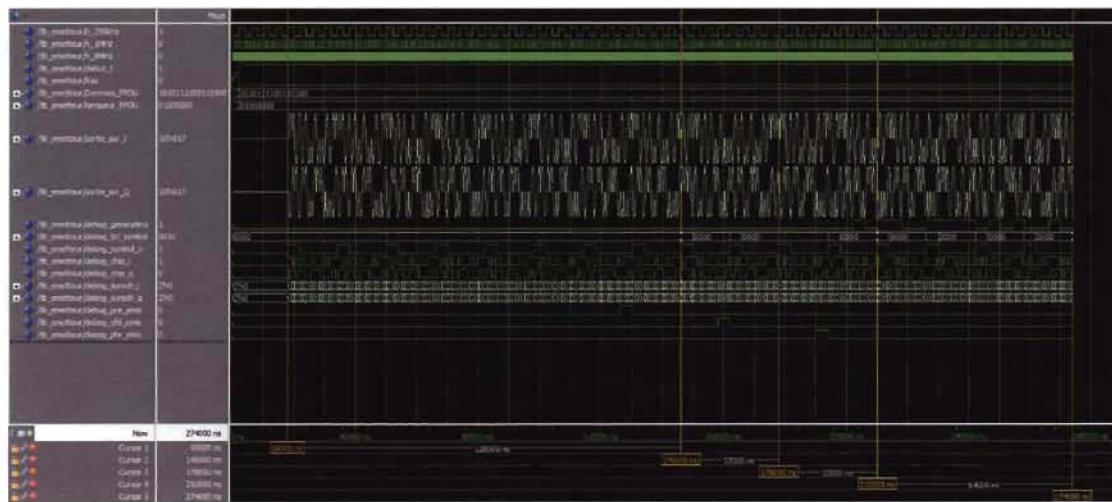

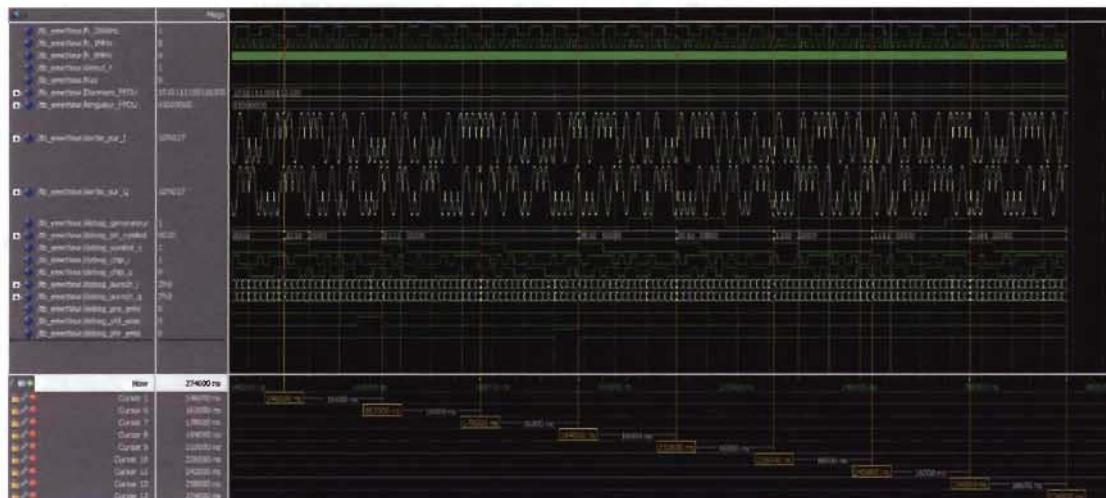

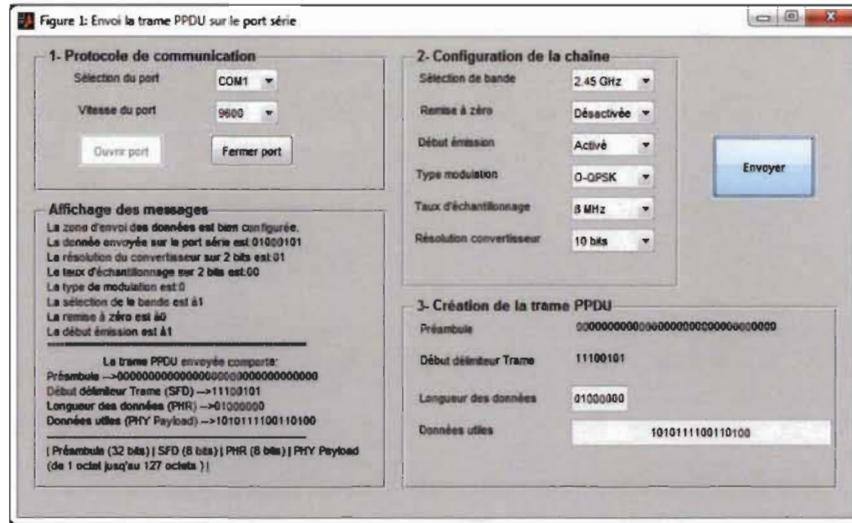

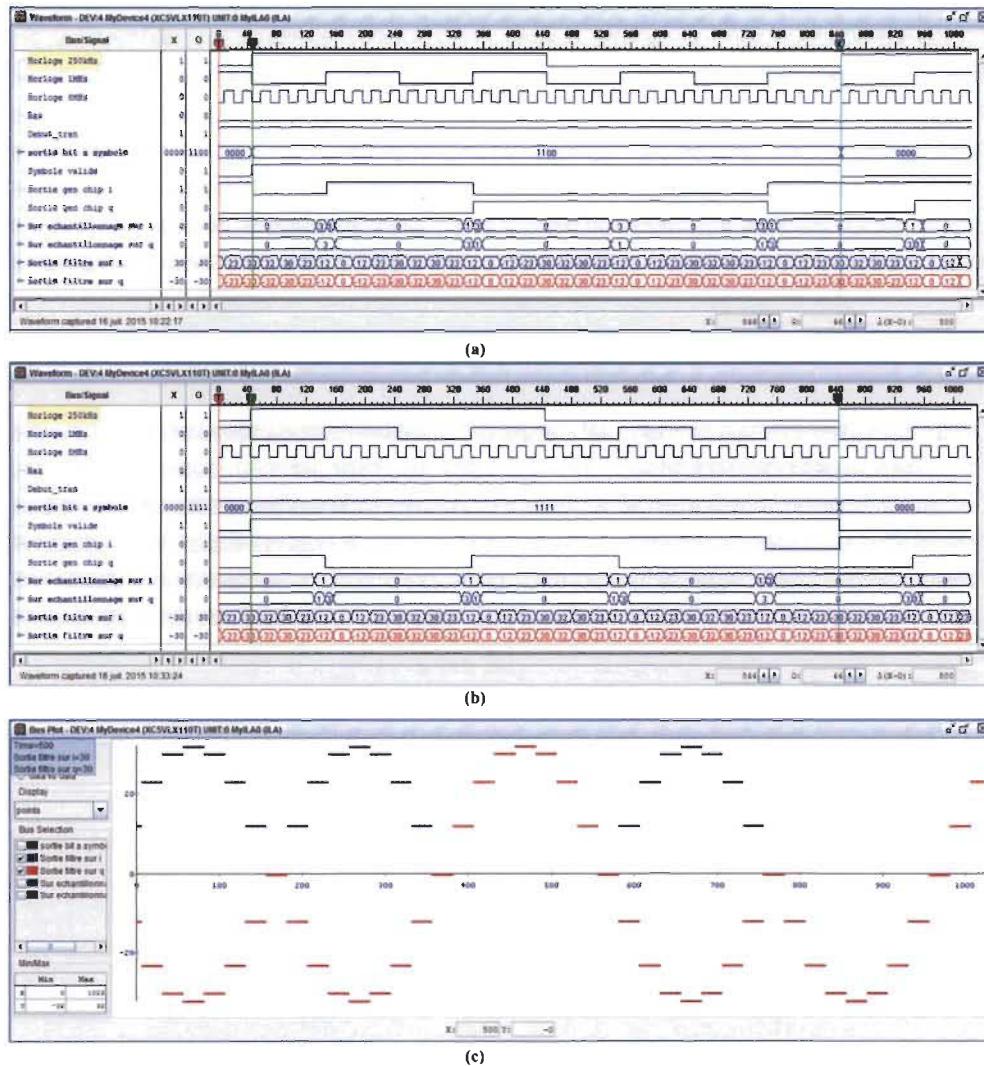

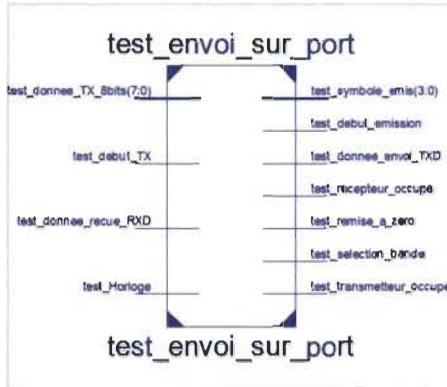

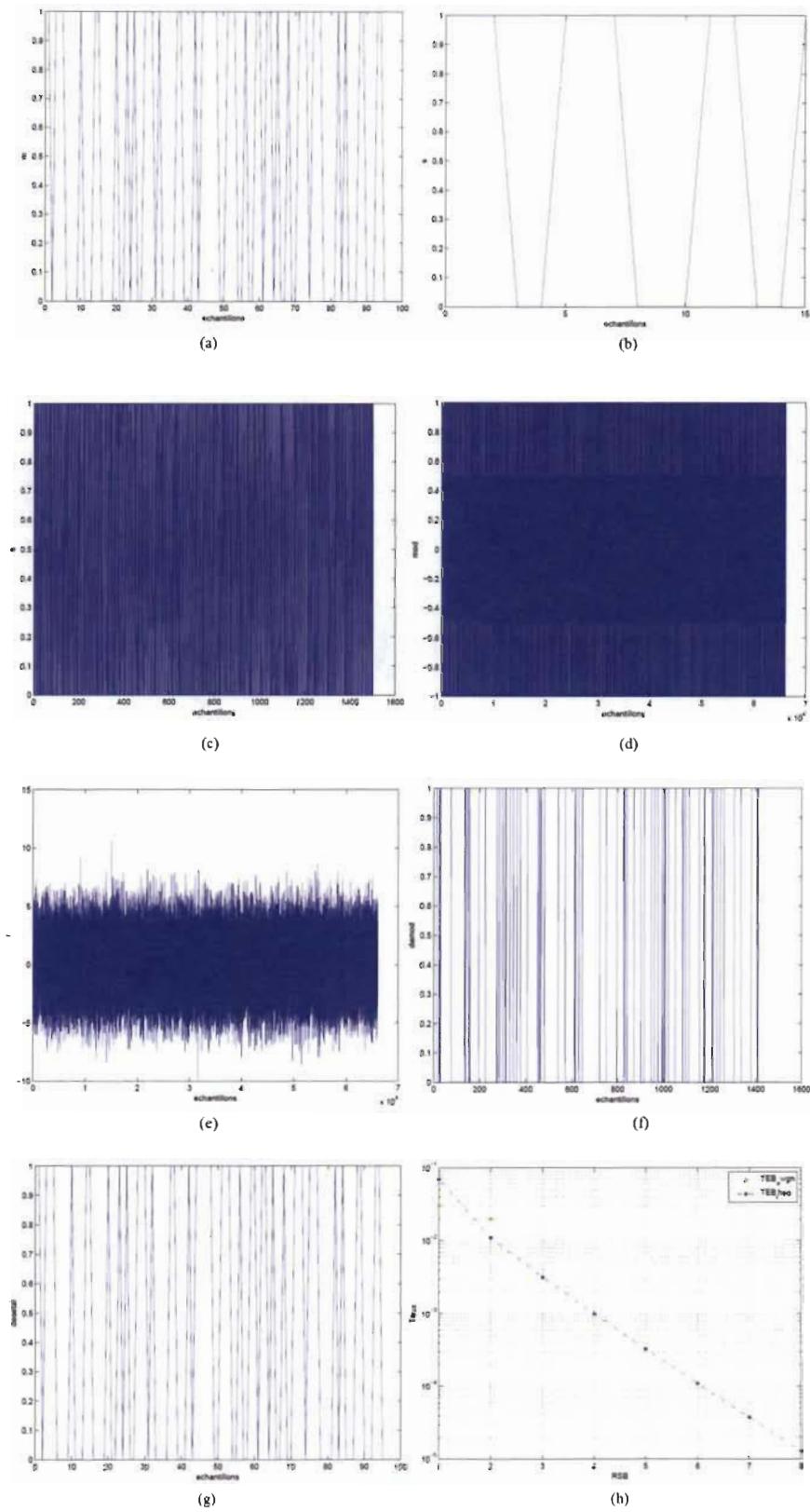

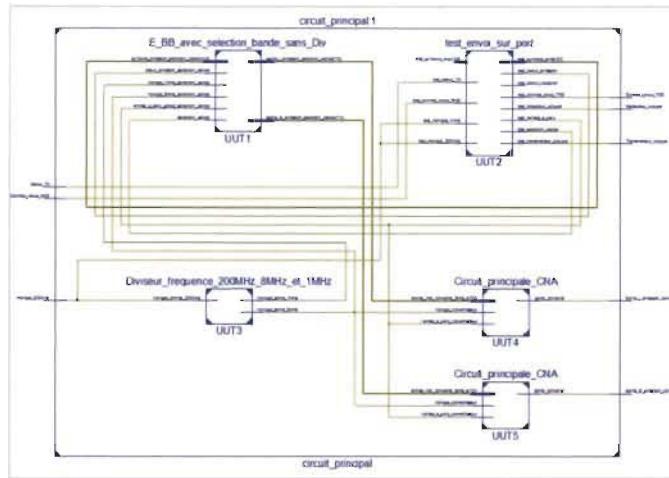

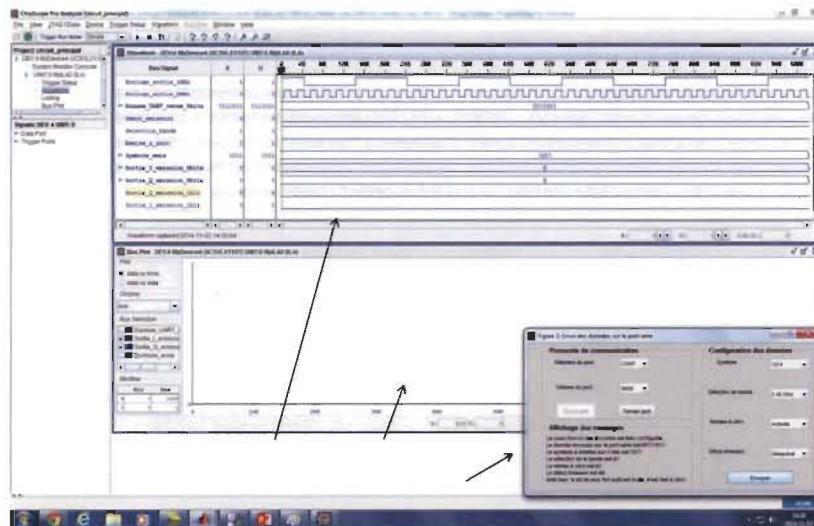

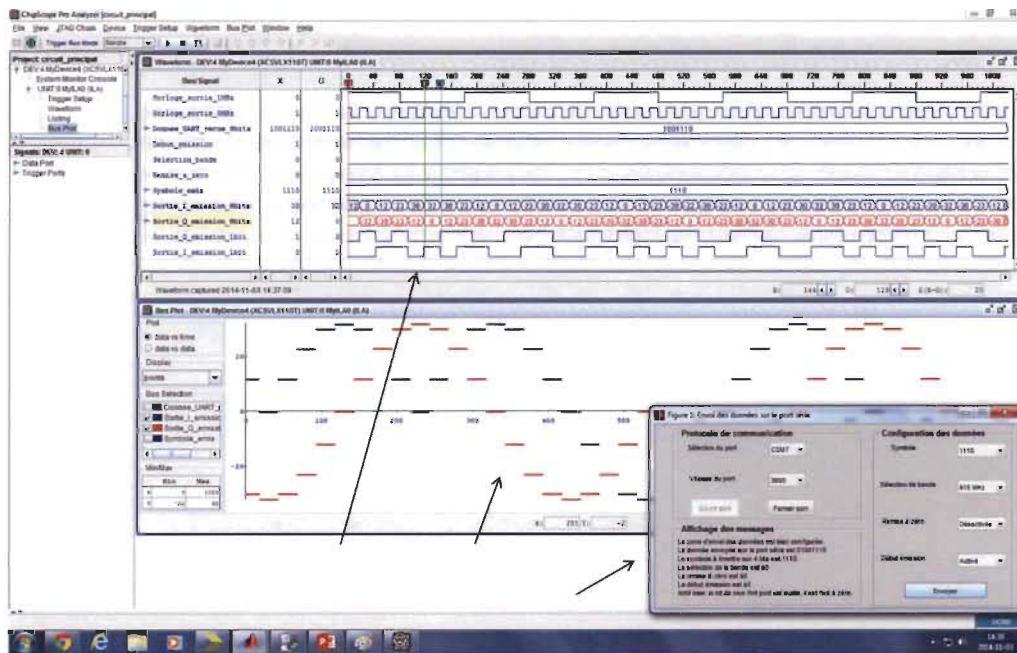

Une fois que le corrélateur détecte l'entrée de données, chacune des séquences de référence (qui sont générées par le corrélateur) est multipliée par l'entrée (soit des données binaires. Cette opération peut être réalisée par l'opération AND. Le résultat est accumulé dans 16 registres. Lorsque les 16 bits sont analysés, le registre avec une valeur maximale 8 correspond au symbole à détecter. La valeur de détection est 8, étant donné que chacune des séquences contient le même nombre de « 1 » et de « 0 » et analyse les séquences de 16 bits.