UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

MÉMOIRE PRÉSENTÉ À

L'UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

COMME EXIGENCE PARTIELLE

DE LA MAÎTRISE EN GÉNIE ÉLECTRIQUE

PAR

THIERRY DUFOUR

ÉGALISEURS ADAPTATIFS PIPELINÉS PAR LA TECHNIQUE DE

L'ANTICIPATION RELAXÉE

JANVIER 2002

Université du Québec à Trois-Rivières

Service de la bibliothèque

Avertissement

L'auteur de ce mémoire ou de cette thèse a autorisé l'Université du Québec à Trois-Rivières à diffuser, à des fins non lucratives, une copie de son mémoire ou de sa thèse.

Cette diffusion n'entraîne pas une renonciation de la part de l'auteur à ses droits de propriété intellectuelle, incluant le droit d'auteur, sur ce mémoire ou cette thèse. Notamment, la reproduction ou la publication de la totalité ou d'une partie importante de ce mémoire ou de cette thèse requiert son autorisation.

# Résumé

Ce mémoire propose une méthode de transformation d'algorithme et une intégration à très grande échelle (*ITGE – VLSI*) d'un égaliseur à base de réseaux de neurones afin d'améliorer la qualité des systèmes de communications numériques. Lors d'une transmission numérique sur un canal, le signal porteur d'information subit des dégradations importantes comme l'interférence inter-symbole, les non linéarités et le bruit. Ces dégradations dépendent du canal de communication utilisé (liaison hertzienne, paire de fil torsadé, guide d'onde, etc.) et le message reçu est souvent porteur d'erreurs. Pour corriger les effets du canal de communication, nous avons recours à la technique d'égalisation des canaux qui permet d'éliminer les erreurs sur le signal reçu et retrouver la séquence de données originales. La technique d'égalisation des canaux consiste à utiliser la sortie du canal et les informations du canal pour estimer le message original.

Puisque les paramètres du canal de communication sont souvent inconnus, on doit faire appel à des algorithmes adaptatifs pour permettre la reconstitution du signal transmis. Dans ce travail, l'adaptation de l'algorithme se fait à partir d'une séquence de données connues *a priori* du récepteur (type supervisé). De plus, la prise en compte des non linéarités du canal rend inefficace les méthodes adaptatives classiques tels les filtres transverses linéaires adaptés par l'algorithme *LMS* ou *RLS*. Nous avons donc recours à un

égaliseur à base de réseau de neurones artificiels (*RNA*) qui permet de traiter des canaux non linéaires.

Les algorithmes d'adaptation du *RNA* sont très souvent de nature récursive et leur application à de hauts débits de calculs est presque impossible. Nous proposons donc une technique de transformation d'algorithme permettant de modifier un algorithme d'adaptation du *RNA*. Cette transformation permet alors de pipeliner l'algorithme d'adaptation et ainsi opérer à de forts débits de calculs.

Des simulations à l'aide de données synthétiques ont été réalisées dans *Matlab*<sup>TM</sup>. Ces simulations ont permis de démontrer les effets de la transformation de l'algorithme et nous ont permis de comparer la solution proposée à d'autres méthodes classiques. L'application à des canaux non linéaires est aussi réalisée. L'architecture de calcul proposée est hautement parallèle et la profondeur de pipeline est simple. Des simulations sur l'architecture ont été réalisées à l'aide de l'outil *Mentor Graphics*<sup>TM</sup> et les résultats sont comparés à ceux obtenus par *Matlab*<sup>TM</sup> afin de valider le fonctionnement. Une intégration de l'architecture en technologie CMOS 0.18µm dans *Synopsys*<sup>TM</sup> a permis d'évaluer les performances de l'architecture pipelinée.

Enfin, ce projet permet d'utiliser des algorithmes complexes fonctionnant à hauts débits dans la problématique d'égalisation des canaux. La réalisation de l'algorithme dans le domaine numérique rend son application fiable et peu coûteuse. De plus, la technique de transformation d'algorithme utilisée permet de modifier les caractéristiques de l'algorithme afin de traiter des cas spécifiques.

## ***Remerciements***

Je tiens à remercier en premier lieu mon directeur de recherche le professeur Daniel Massicotte. Son support et son expérience m'ont permis d'acquérir des connaissances inestimables en recherche. Sa grande compréhension et son côté humain m'ont par ailleurs permis de me réaliser pleinement sur tous les plans de ma vie tout au long de ce travail.

J'aimerais aussi remercier mes parents qui m'ont toujours encouragé et qui m'ont offert la possibilité de poursuivre mes études. Leur support moral a toujours été très apprécié et a grandement contribué à la réalisation de ce travail.

Enfin, je remercie mes collègues du Laboratoire des Signaux et Systèmes Intégrés (LSSI) pour l'aide qu'ils m'ont accordée. Les bons moments de discussion et de détente m'ont permis d'effectuer ce travail dans une ambiance motivante.

# Table des matières

|                                                                            |            |

|----------------------------------------------------------------------------|------------|

| <i>Résumé</i>                                                              | <i>i</i>   |

| <i>Remerciements</i>                                                       | <i>iii</i> |

| <i>Liste des figures</i>                                                   | <i>vii</i> |

| <i>Liste des tableaux</i>                                                  | <i>x</i>   |

| <i>Liste des symboles et abréviations</i>                                  | <i>xi</i>  |

| <i>Chapitre 1</i>                                                          | <i>1</i>   |

| <i>Introduction</i>                                                        | <i>1</i>   |

| 1.1 Problématique                                                          | <i>2</i>   |

| 1.2 Objectifs                                                              | <i>4</i>   |

| 1.3 Méthodologie                                                           | <i>5</i>   |

| 1.4 Organisation de ce rapport                                             | <i>6</i>   |

| <i>Chapitre 2</i>                                                          | <i>8</i>   |

| <i>    Égalisations adaptatives de canaux en communications numériques</i> | <i>8</i>   |

| 2.1 La communication numérique                                             | <i>9</i>   |

| 2.1.1 Principes de modulation et de démodulation                           | <i>12</i>  |

| 2.1.2 Modèles de canaux de transmission                                    | <i>19</i>  |

| 2.2 Égaliseurs adaptatifs des canaux                                       | <i>22</i>  |

| 2.2.1 Principe de l'égalisation                                            | <i>22</i>  |

| 2.2.2 Les techniques de l'égalisation                                      | <i>24</i>  |

| 2.2.3 Les techniques d'adaptation des égaliseurs                           | <i>28</i>  |

|                                                              |    |

|--------------------------------------------------------------|----|

| <i>Chapitre 3</i>                                            | 31 |

| <i>Techniques du pipeline</i>                                | 31 |

| 3.1 Méthode de resynchronisation                             | 32 |

| 3.2 Pipeline classique                                       | 35 |

| 3.3 Technique de l'anticipation                              | 38 |

| 3.3.1 Principe                                               | 38 |

| 3.3.2 Anticipation dispersée et regroupée                    | 40 |

| 3.4 Transformation de la technique de l'anticipation         | 41 |

| 3.4.1 Justification de la transformation                     | 41 |

| 3.4.2 Anticipation relaxée                                   | 42 |

| 3.4.3 Autres méthodes                                        | 44 |

| 3.5 Application à l'égalisation adaptative des canaux        | 45 |

| 3.6 Conclusion                                               | 50 |

| <i>Chapitre 4</i>                                            | 52 |

| <i>Pipeline d'égaliseurs à base de réseaux de neurones</i>   | 52 |

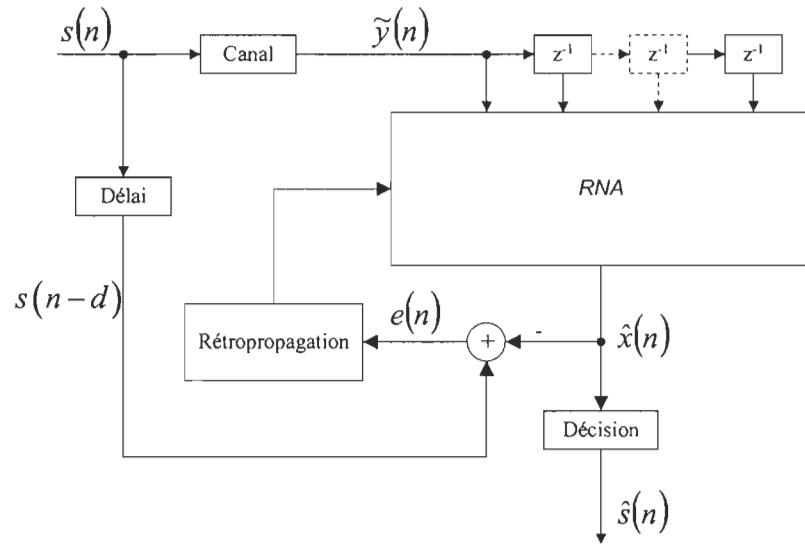

| 4.1 Réseaux de neurones pour l'égalisation des canaux        | 52 |

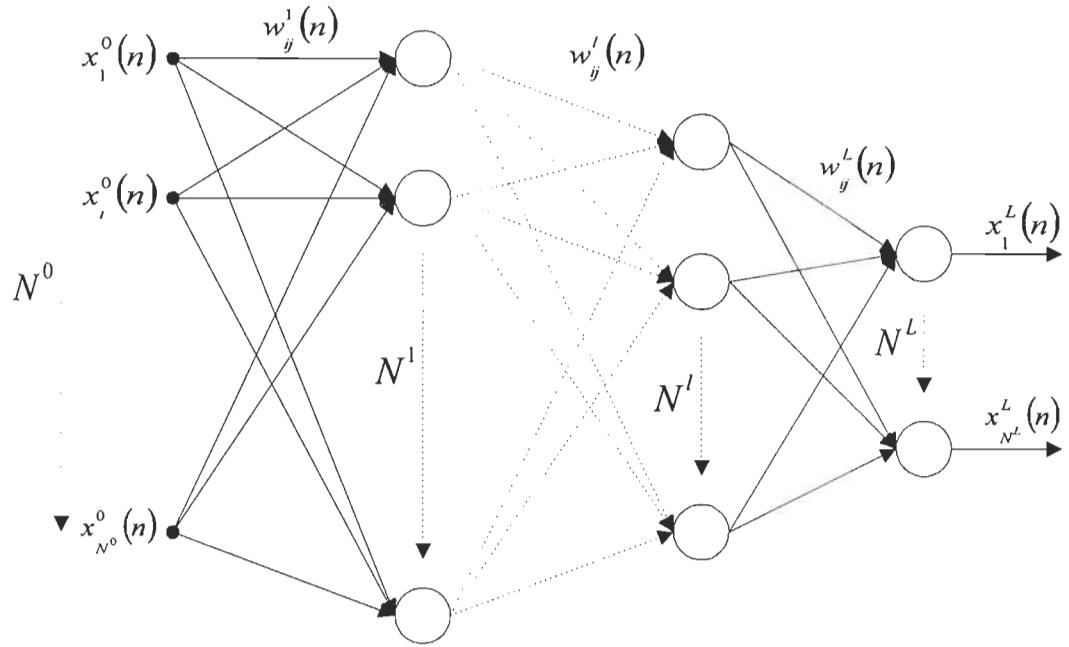

| 4.2 Les réseaux de neurones perceptron multicouches          | 54 |

| 4.3 Anticipation relaxée sur la rétropropagation du gradient | 56 |

| 4.4 Résultats de simulations                                 | 60 |

| 4.4.1 Canal C1 linéaire                                      | 60 |

| 4.4.2 Canal C1 non linéaire                                  | 66 |

| 4.5 Conclusion                                               | 70 |

|                                                                   |            |

|-------------------------------------------------------------------|------------|

| <i>Chapitre 5</i>                                                 | <b>71</b>  |

| <i>Intégration sur silicium de l'égaliseur adaptatif pipeliné</i> | <b>71</b>  |

| <b>5.1 Architectures de calcul</b>                                | <b>71</b>  |

| <b>5.2 Éléments de calculs</b>                                    | <b>81</b>  |

| 5.2.1 Addition et soustraction                                    | 81         |

| 5.2.2 Multiplication                                              | 81         |

| 5.2.3 Fonction d'activation ( $f_{PL}(x)$ )                       | 83         |

| 5.2.4 Dérivée de la fonction d'activation ( $f_{PL}'(x)$ )        | 95         |

| <b>5.3 Résultats de simulations</b>                               | <b>97</b>  |

| 5.3.1 Propriétés de convergence                                   | 98         |

| 5.3.2 Performances en égalisation                                 | 101        |

| 5.3.3 Résultats de synthèse                                       | 102        |

| <b>5.4 Conclusion</b>                                             | <b>103</b> |

| <i>Conclusion</i>                                                 | <b>105</b> |

| <i>Bibliographie</i>                                              | <b>109</b> |

# Liste des figures

|                                                                       |    |

|-----------------------------------------------------------------------|----|

| <i>Figure 2.1: Système de communication général</i>                   | 9  |

| <i>Figure 2.2: Système de communication numérique</i>                 | 10 |

| <i>Figure 2.3: Information binaire classique</i>                      | 14 |

| <i>Figure 2.4: Format de données NRZ</i>                              | 14 |

| <i>Figure 2.5: Signal ASK</i>                                         | 15 |

| <i>Figure 2.6: Constellation 32-QAM</i>                               | 16 |

| <i>Figure 2.7: Constellation 8-PSK</i>                                | 17 |

| <i>Figure 2.8: Modulateur QAM</i>                                     | 17 |

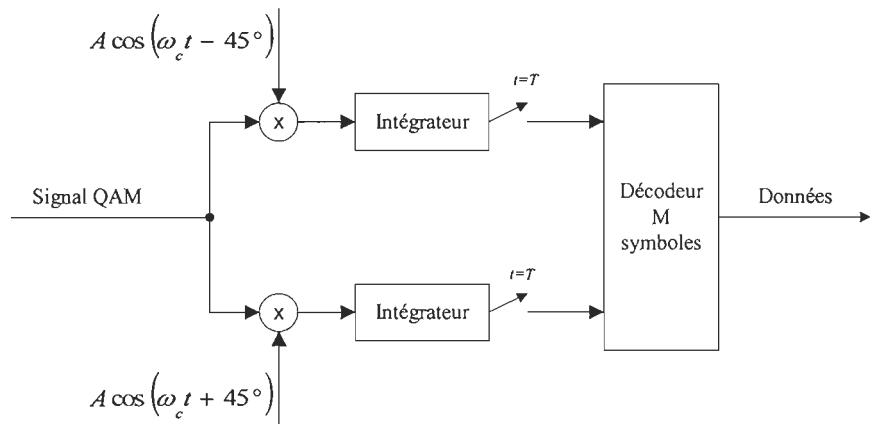

| <i>Figure 2.9: Démodulateur QAM</i>                                   | 18 |

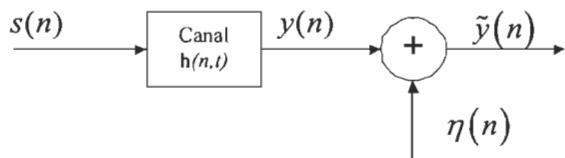

| <i>Figure 2.10: Schéma du canal linéaire et variant dans le temps</i> | 20 |

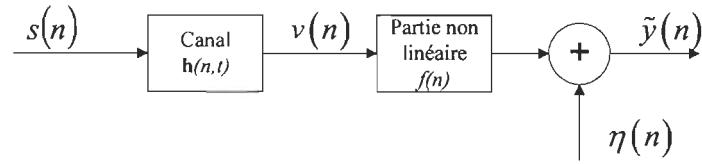

| <i>Figure 2.11: Modèle de canal non linéaire</i>                      | 21 |

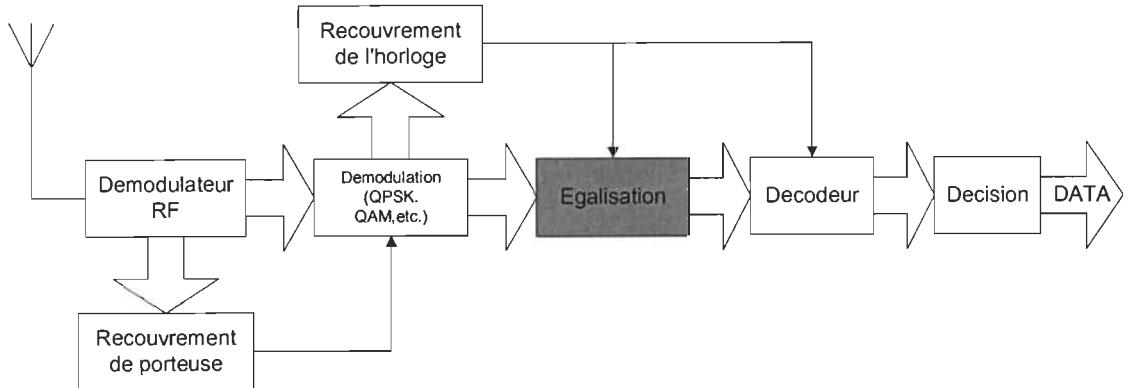

| <i>Figure 2.12: Récepteur en communications numériques sans fil</i>   | 23 |

| <i>Figure 2.13: Schéma du récepteur optimum</i>                       | 23 |

| <i>Figure 2.14: Schéma du récepteur sous optimum</i>                  | 24 |

| <i>Figure 2.15: Égaliseur transverse linéaire</i>                     | 25 |

| <i>Figure 2.16: Égaliseur à retour de décision</i>                    | 26 |

| <i>Figure 2.17: Égaliseur MLSE</i>                                    | 28 |

| <i>Figure 3.1: FIR avant resynchronisation</i>                        | 33 |

| <i>Figure 3.2: Resynchronisation du FIR étape 1</i>                   | 34 |

| <i>Figure 3.3: FIR après resynchronisation complète</i>               | 34 |

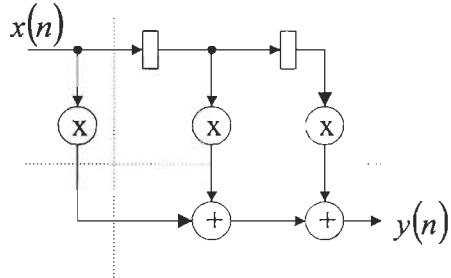

| <i>Figure 3.4: Structure FIR avant pipeline</i>                       | 36 |

| <i>Figure 3.5: Structure FIR pipelinée #1</i>                         | 36 |

| <i>Figure 3.6: Structure FIR pipelinée #2</i>                         | 37 |

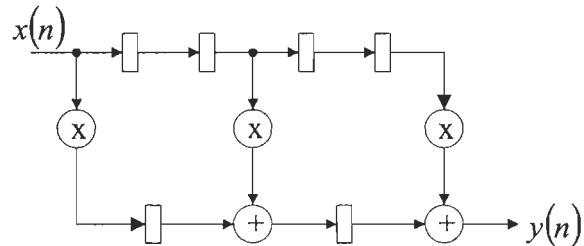

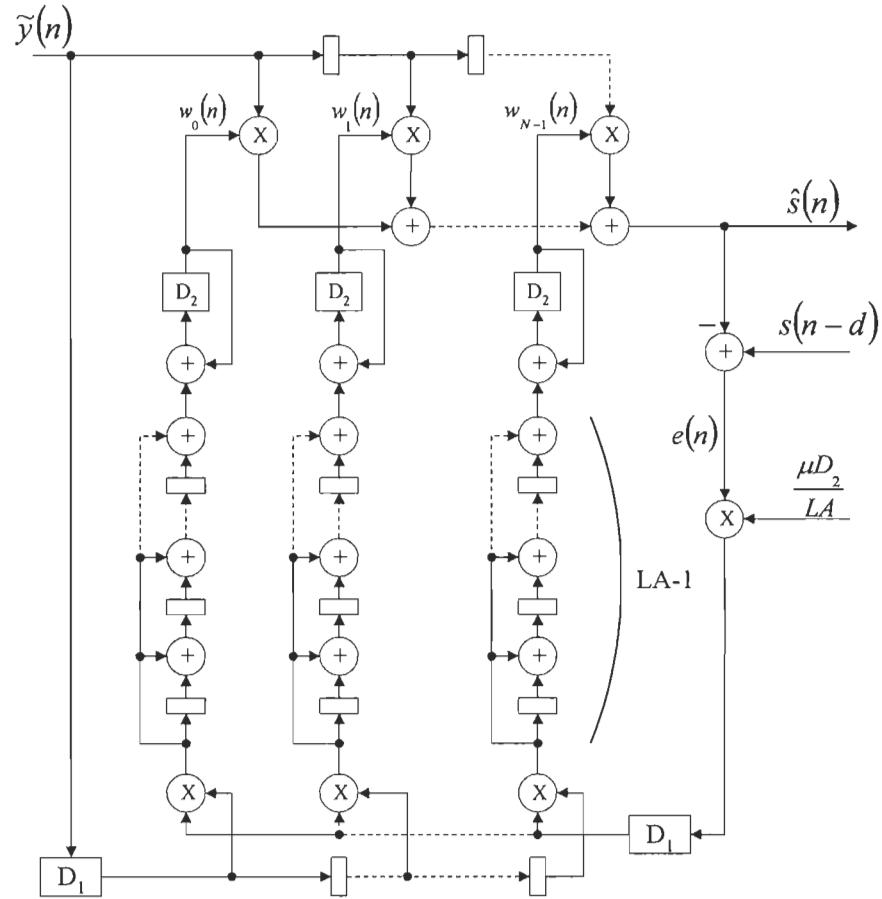

| <i>Figure 3.7 Architecture serielle du filtre transverse</i>          | 47 |

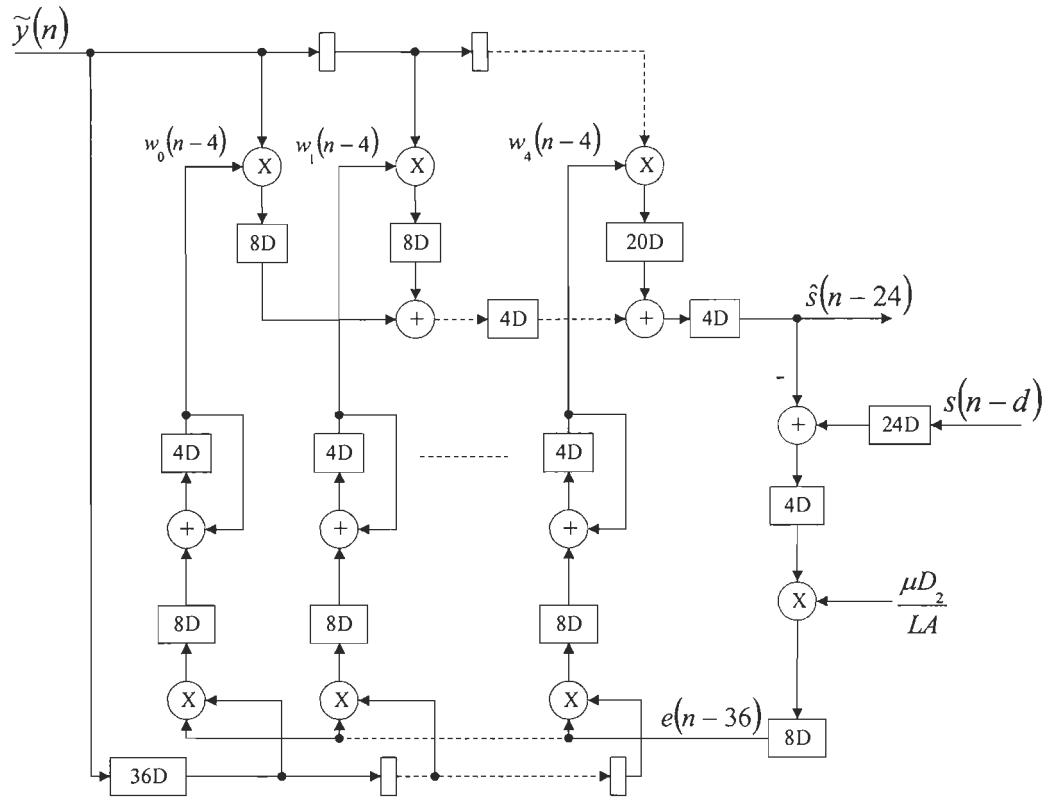

| <i>Figure 3.8: Architecture pipelinée du filtre transverse</i>        | 49 |

|                                                                                                                                     |    |

|-------------------------------------------------------------------------------------------------------------------------------------|----|

| <i>Figure 3.9: Filtre transverse pipeliné avec gain en vitesse de 48</i>                                                            | 50 |

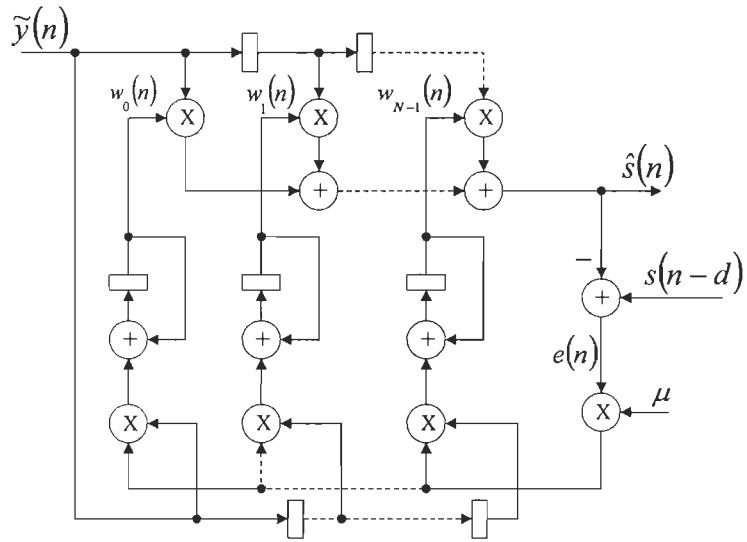

| <i>Figure 4.1: RNA pour l'égalisation des canaux</i>                                                                                | 54 |

| <i>Figure 4.2: Réseau de neurones multicouches</i>                                                                                  | 55 |

| <i>Figure 4.3: Détail d'un neurone</i>                                                                                              | 55 |

| <i>Figure 4.4: Réseau de <math>M</math> neurones à 2 couches, <math>N</math> entrées et une sortie</i>                              | 60 |

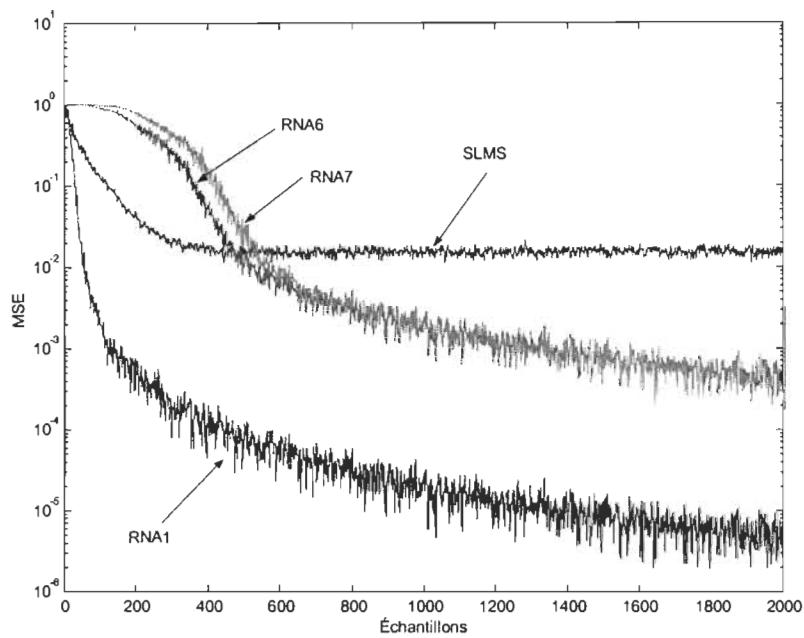

| <i>Figure 4.5: Convergence pour <math>RNA_1</math>, <math>RNA_2</math>, <math>RNA_3</math> et SLMS (C1 lin)</i>                     | 64 |

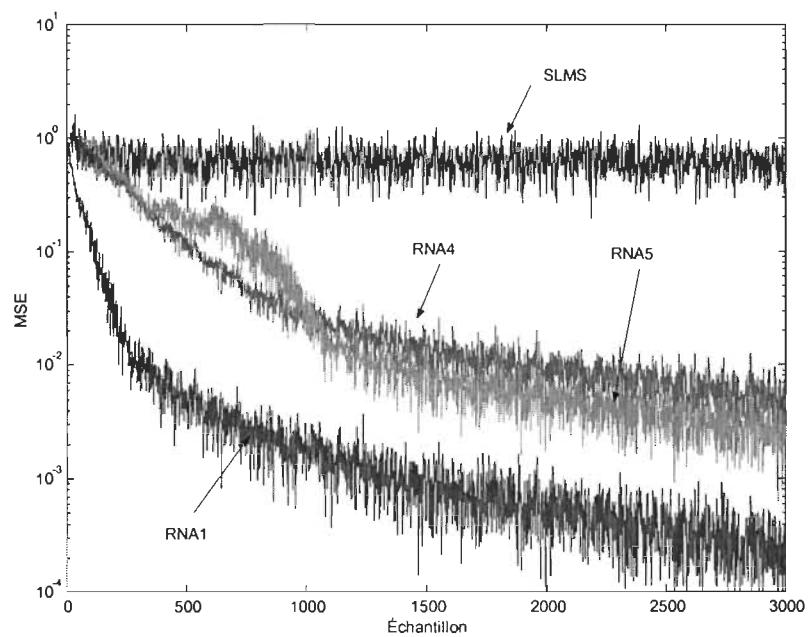

| <i>Figure 4.6: Convergence pour <math>RNA_1</math>, <math>RNA_4</math>, <math>RNA_5</math> et SLMS (C1 lin)</i>                     | 64 |

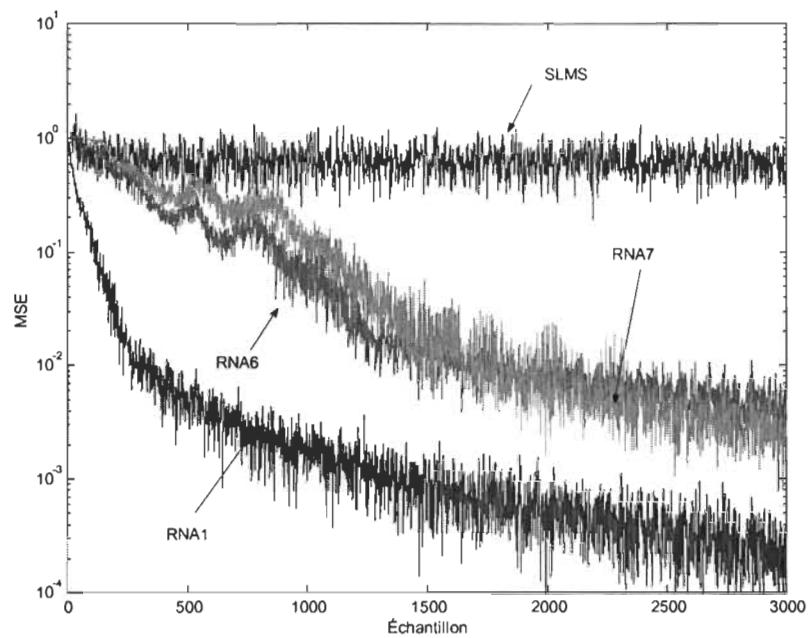

| <i>Figure 4.7: Convergence pour <math>RNA_1</math>, <math>RNA_6</math>, <math>RNA_7</math> et SLMS (C1 lin)</i>                     | 65 |

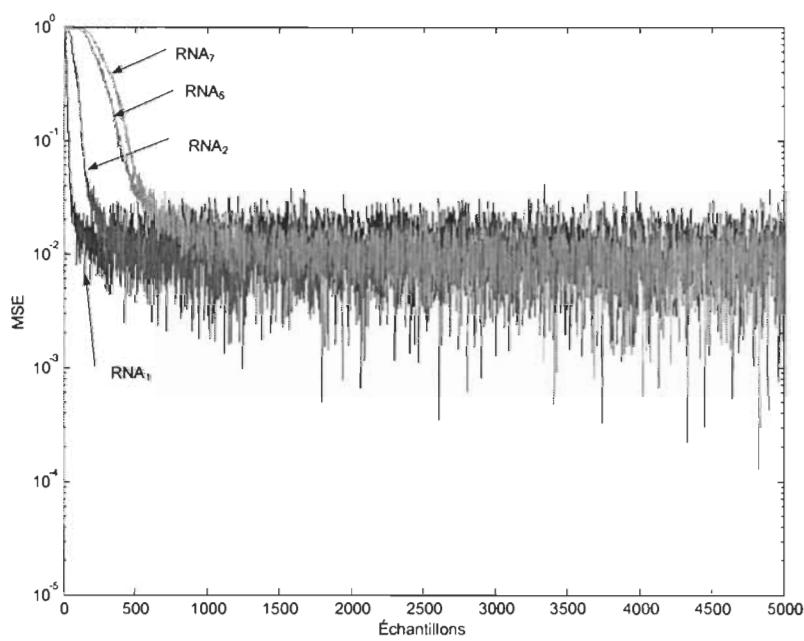

| <i>Figure 4.8: Convergence de <math>RNA_1</math>, <math>RNA_2</math>, <math>RNA_5</math> et <math>RNA_7</math> pour SNR de 17dB</i> | 65 |

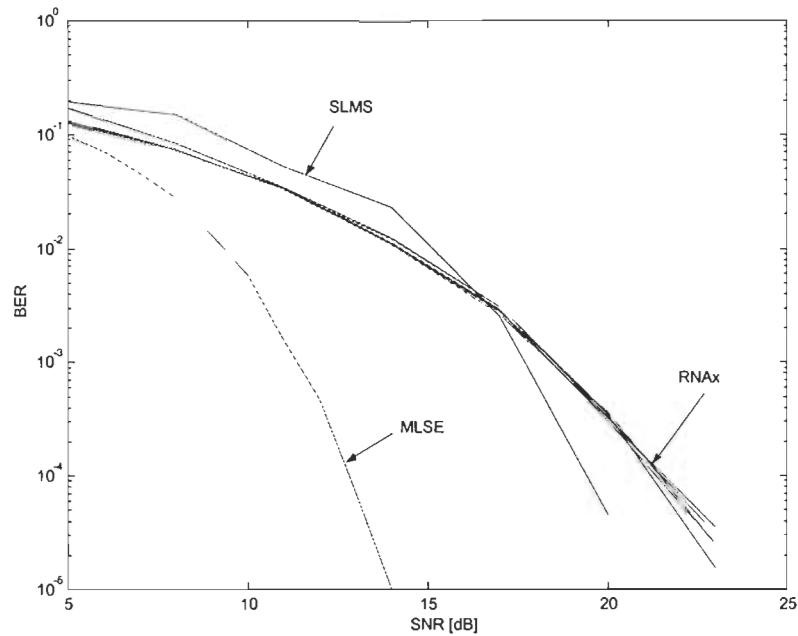

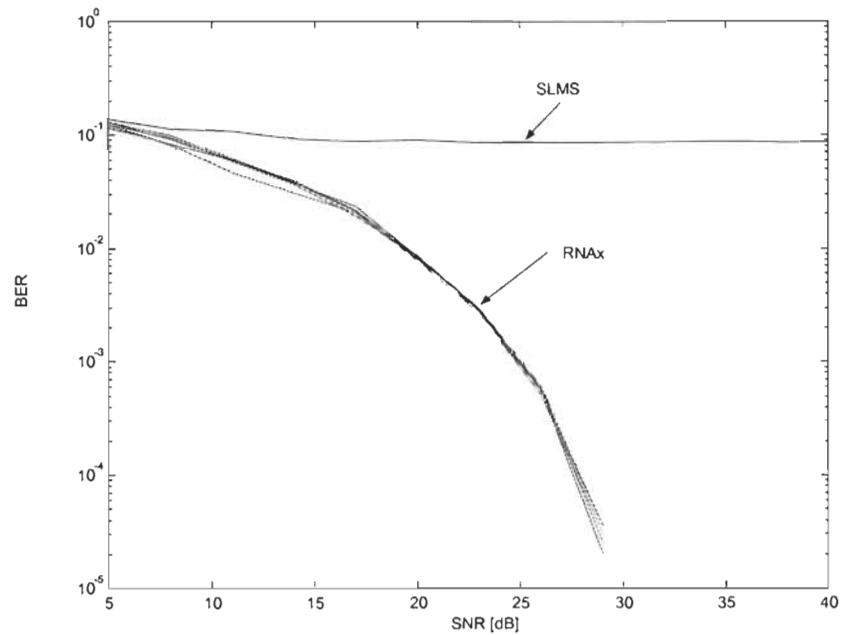

| <i>Figure 4.9: Performance en égalisation pour C1 linéaire</i>                                                                      | 66 |

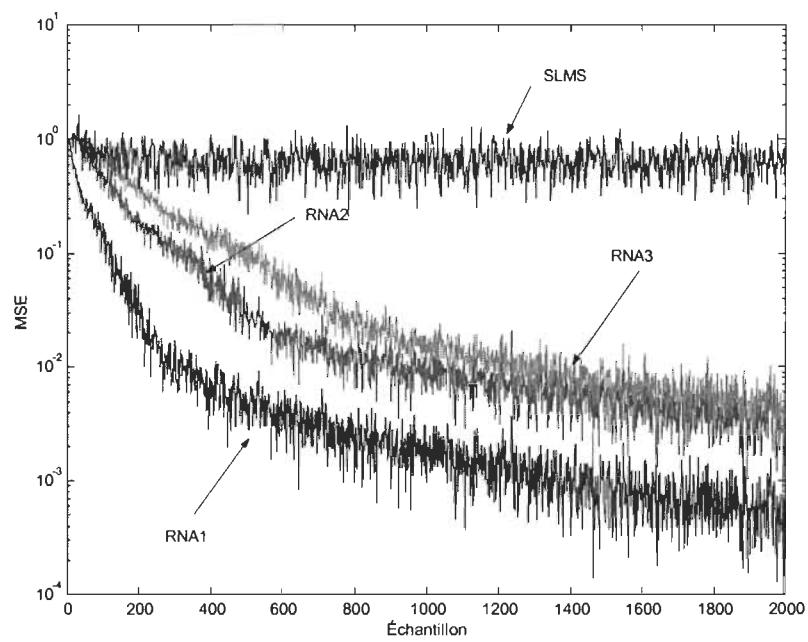

| <i>Figure 4.10: Convergence pour <math>RNA_1</math>, <math>RNA_2</math>, <math>RNA_3</math> et SLMS (C1 nlin)</i>                   | 68 |

| <i>Figure 4.11: Convergence pour <math>RNA_1</math>, <math>RNA_4</math>, <math>RNA_5</math> et SLMS (C1 nlin)</i>                   | 68 |

| <i>Figure 4.12: Convergence pour <math>RNA_1</math>, <math>RNA_6</math>, <math>RNA_7</math> et SLMS (C1 nlin)</i>                   | 69 |

| <i>Figure 4.13: BER vs SNR pour C1 non linéaire</i>                                                                                 | 69 |

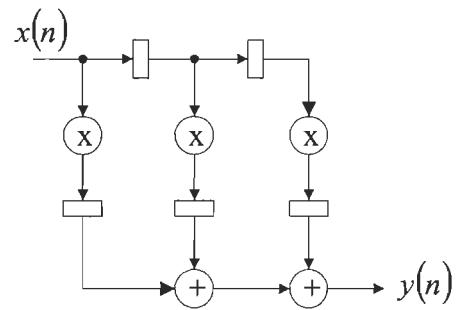

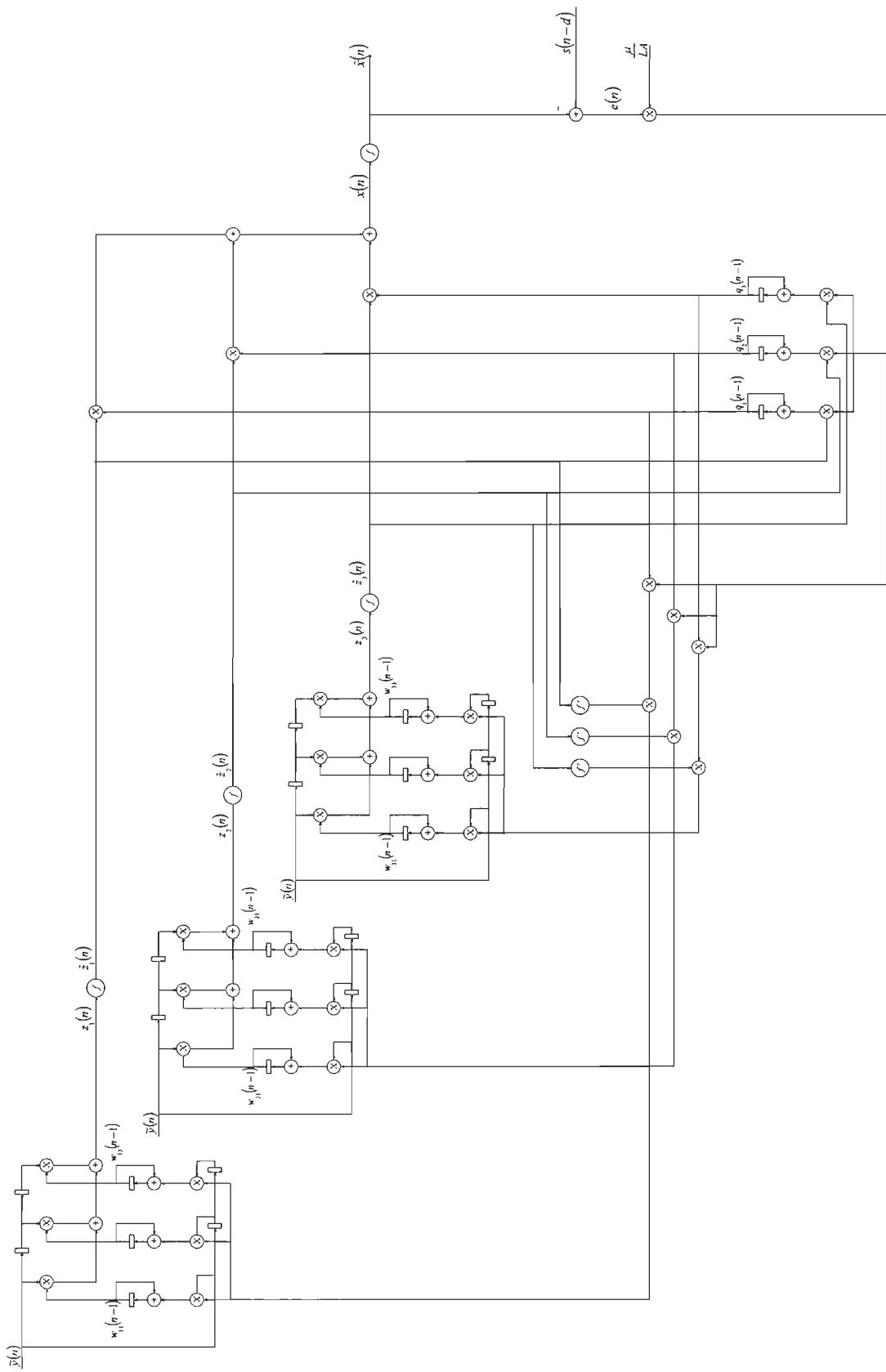

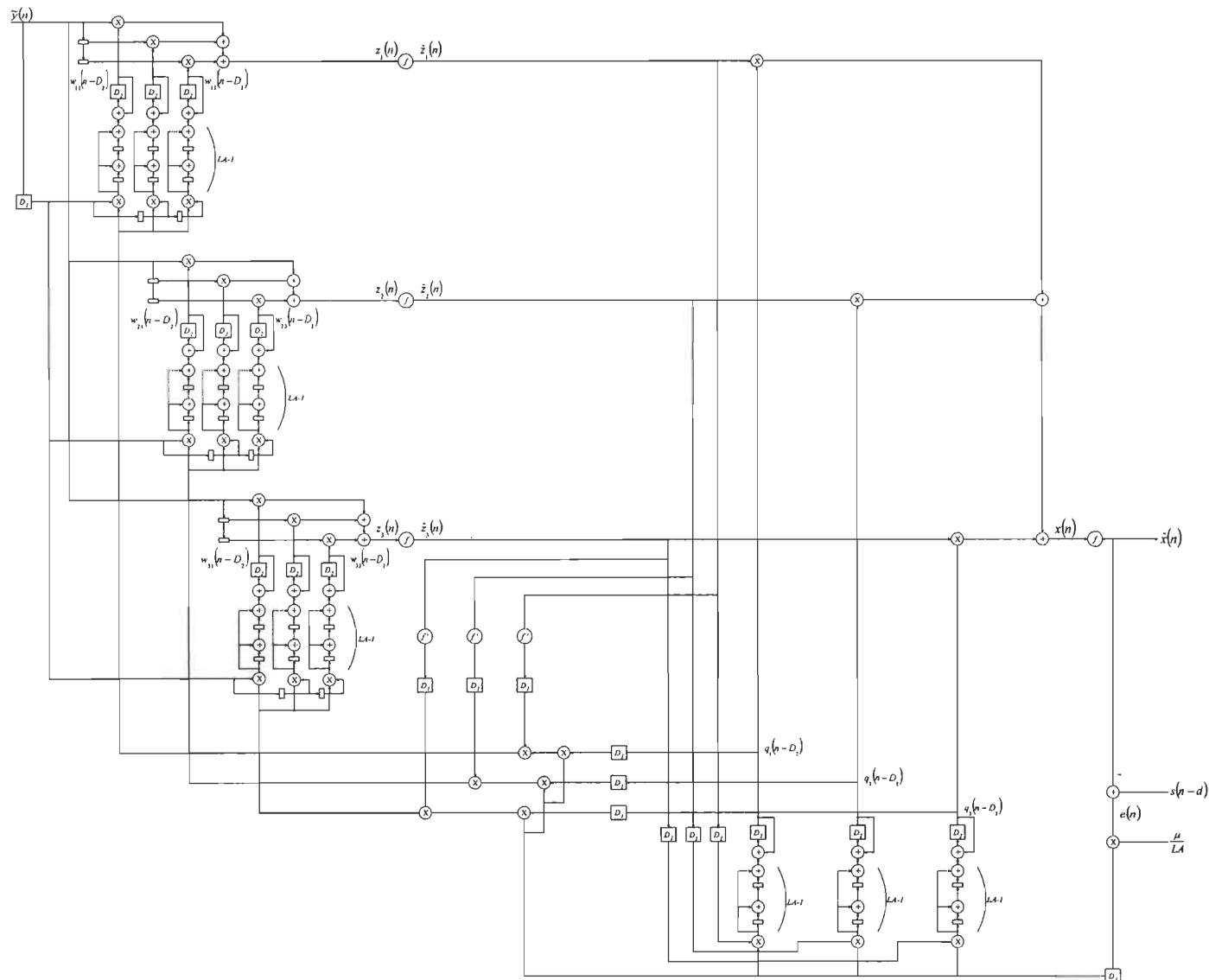

| <i>Figure 5.1: Architecture serielle (SRNA)</i>                                                                                     | 76 |

| <i>Figure 5.2: Architecture pipelinée avant resynchronisation (PIPRNA)</i>                                                          | 77 |

| <i>Figure 5.3: Architecture pipelinée après resynchronisation (PIPRNA1)</i>                                                         | 78 |

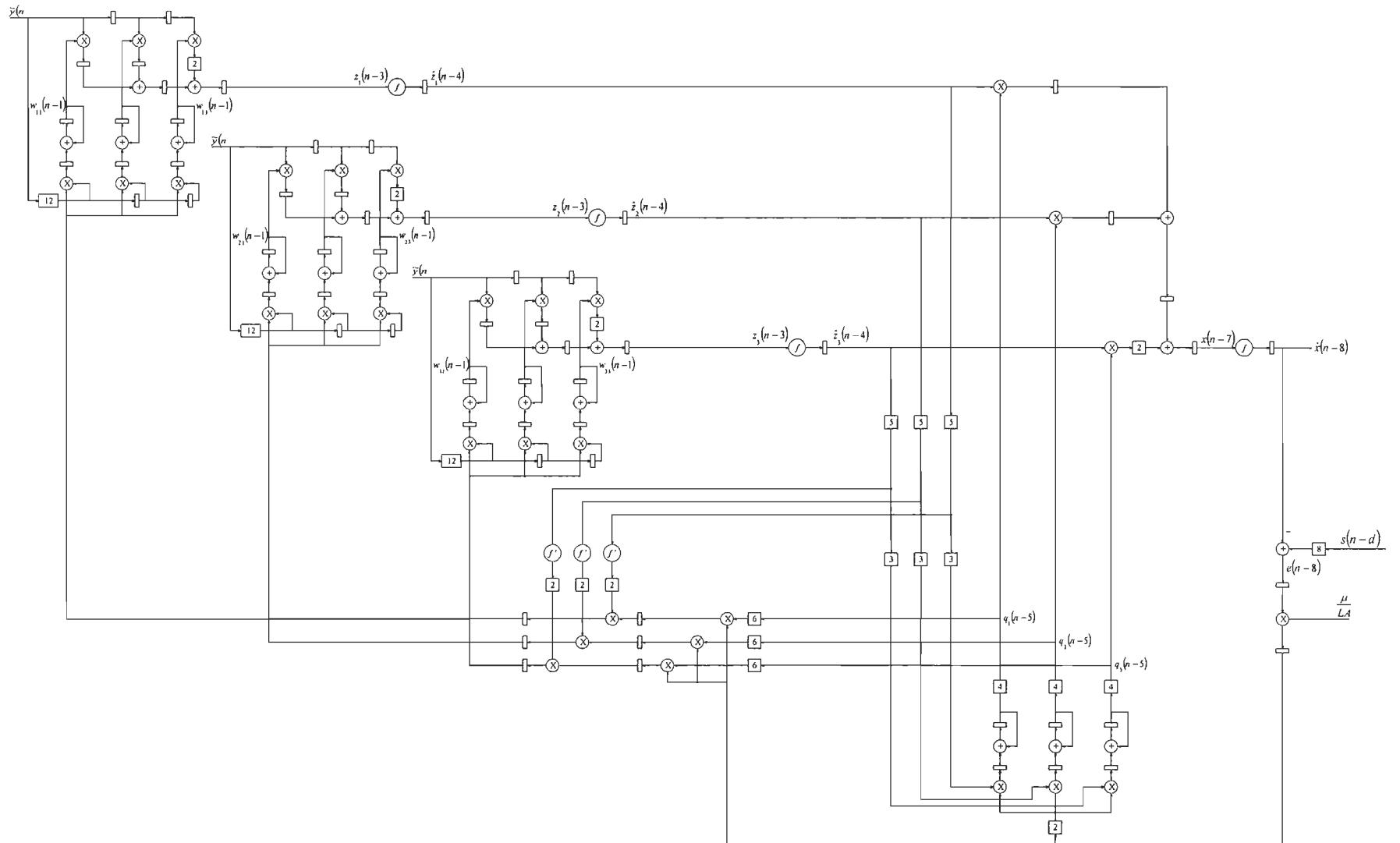

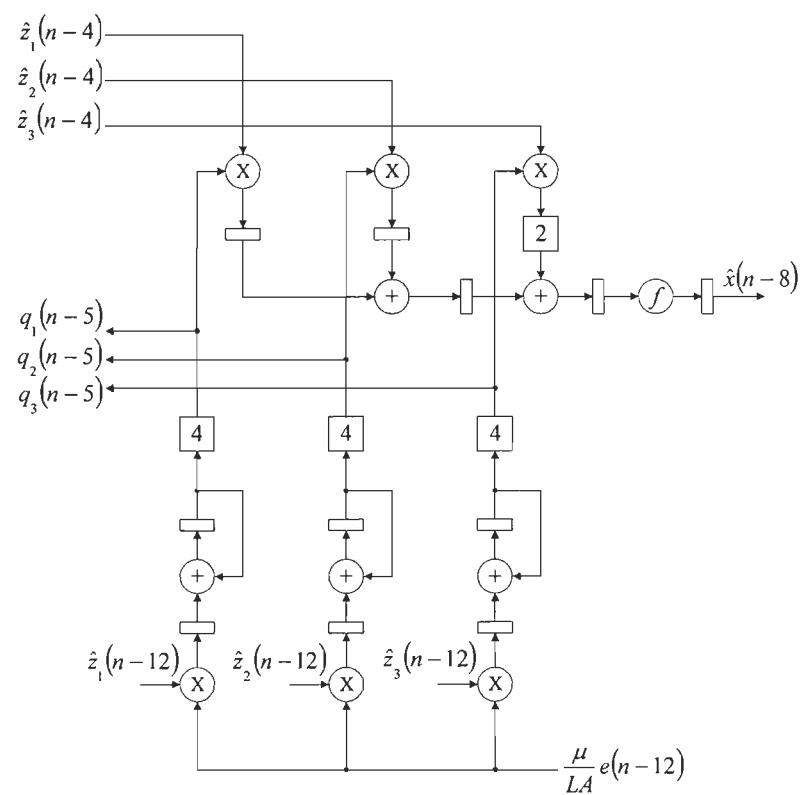

| <i>Figure 5.4: Architecture pipelinée réalisée en VHDL (PIPRNA2)</i>                                                                | 79 |

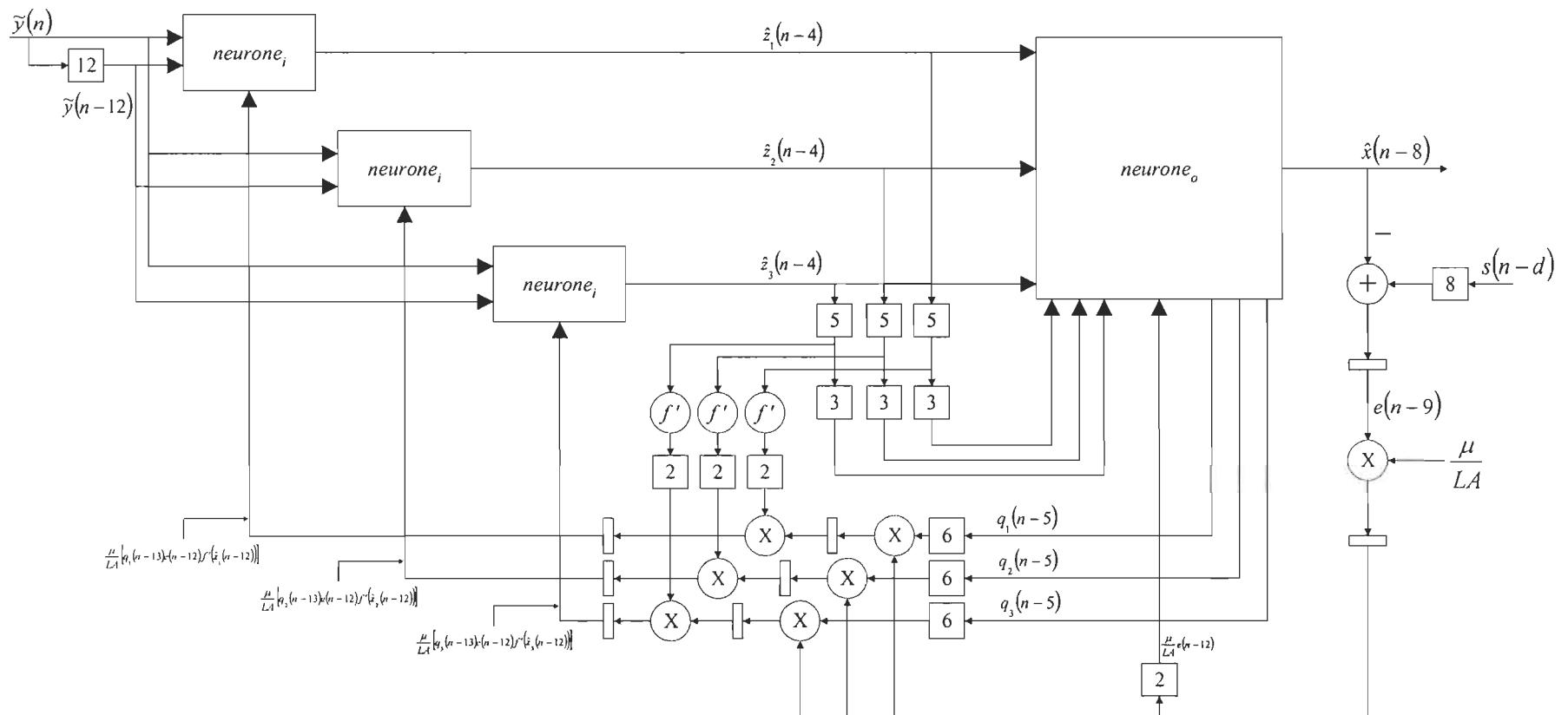

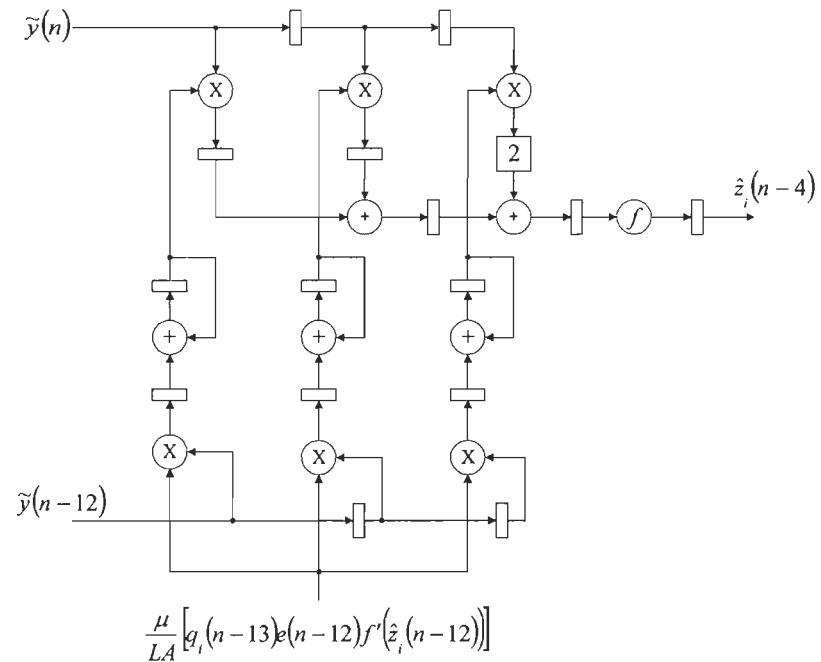

| <i>Figure 5.5: Schéma de neurone<sub>i</sub></i>                                                                                    | 80 |

| <i>Figure 5.6: Schéma de neurone<sub>o</sub></i>                                                                                    | 80 |

| <i>Figure 5.7: Exemple de multiplications a) 1 par 2 b) 1 par -1</i>                                                                | 82 |

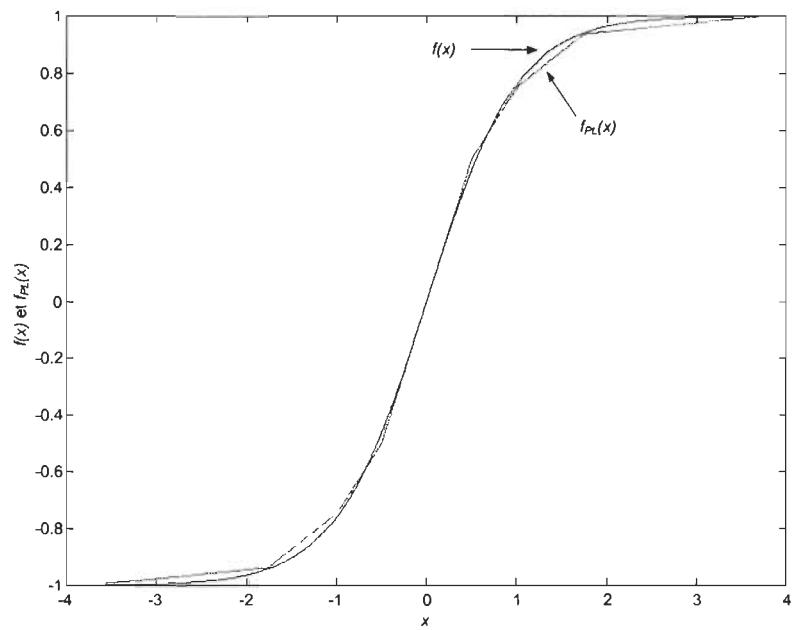

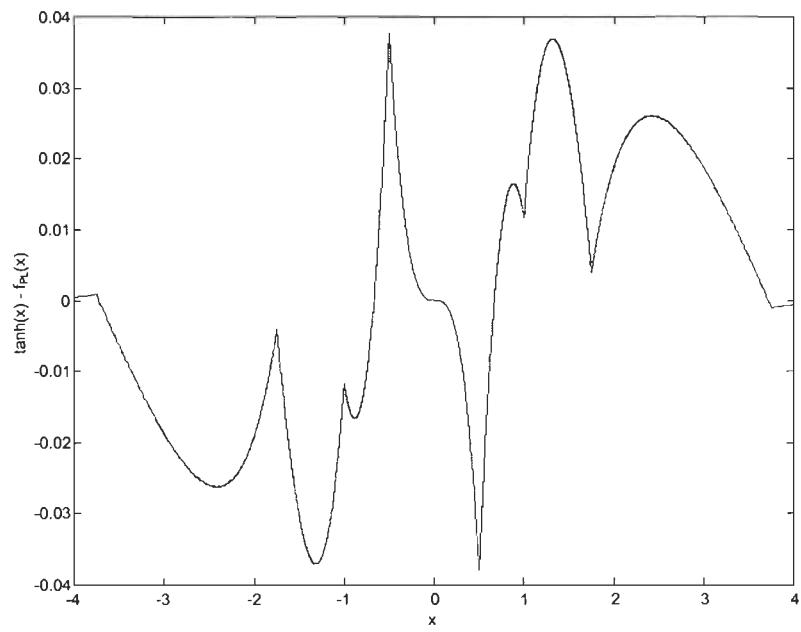

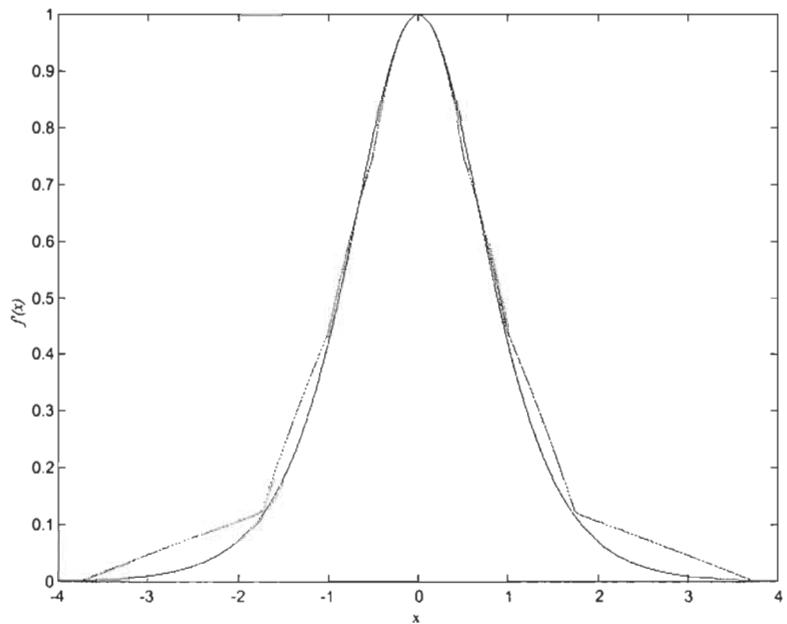

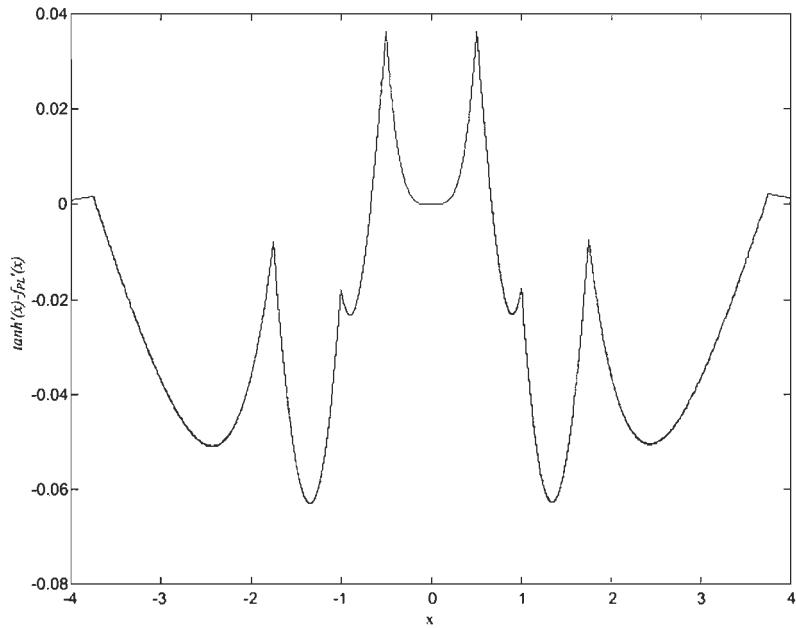

| <i>Figure 5.8: Fonction d'activation a) Approximation b) Erreur d'approximation</i>                                                 | 85 |

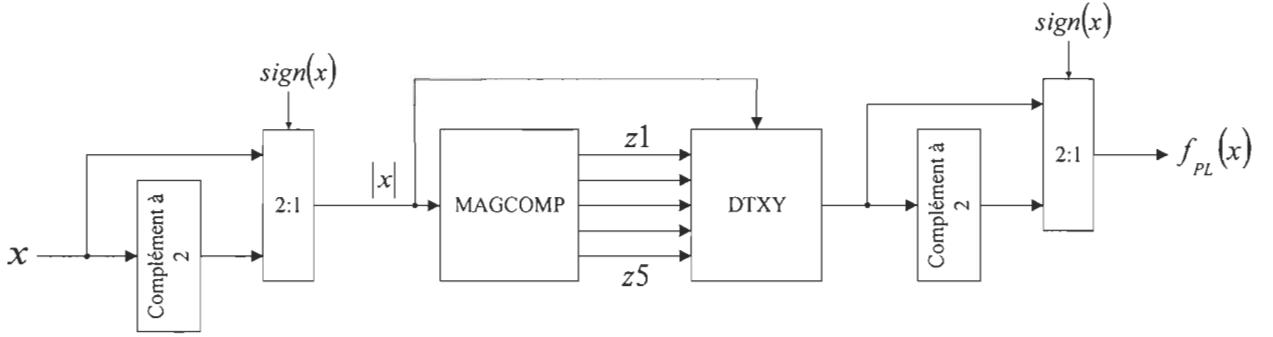

| <i>Figure 5.9: Réalisation de la fonction <math>f_{PL}(x)</math></i>                                                                | 86 |

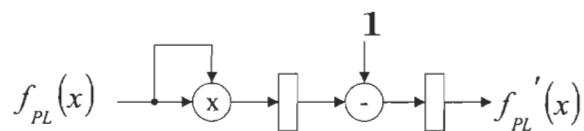

| <i>Figure 5.10: Réalisation de la dérivée de <math>f_{PL}(x)</math></i>                                                             | 95 |

| <i>Figure 5.11: Dérivée de <math>\tanh(x)</math> et <math>f_{PL}'(x)</math></i>                                                     | 96 |

| <i>Figure 5.12: Erreur d'approximation de <math>f_{PL}'(x)</math></i>                                                               | 97 |

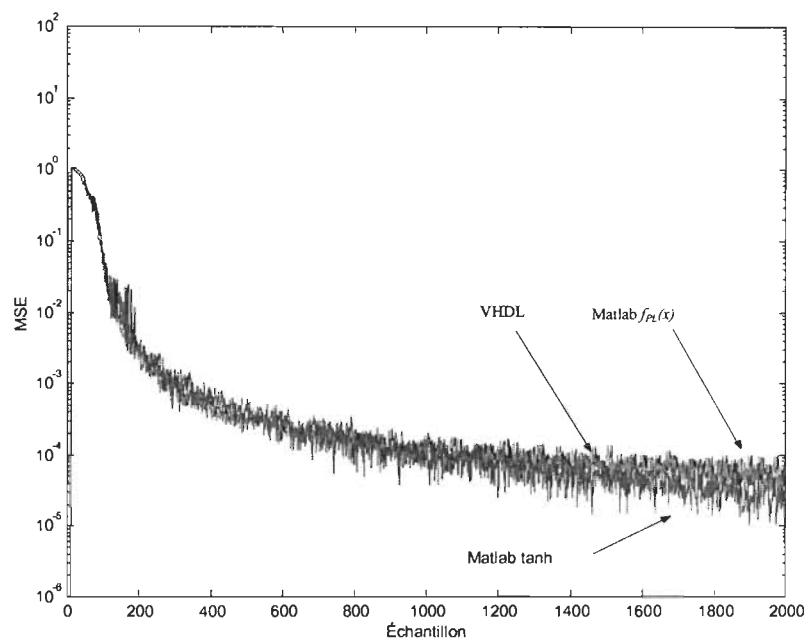

| <i>Figure 5.13: Caractéristiques de convergence du réseau VHDL pour C1 linéaire</i>                                                 | 99 |

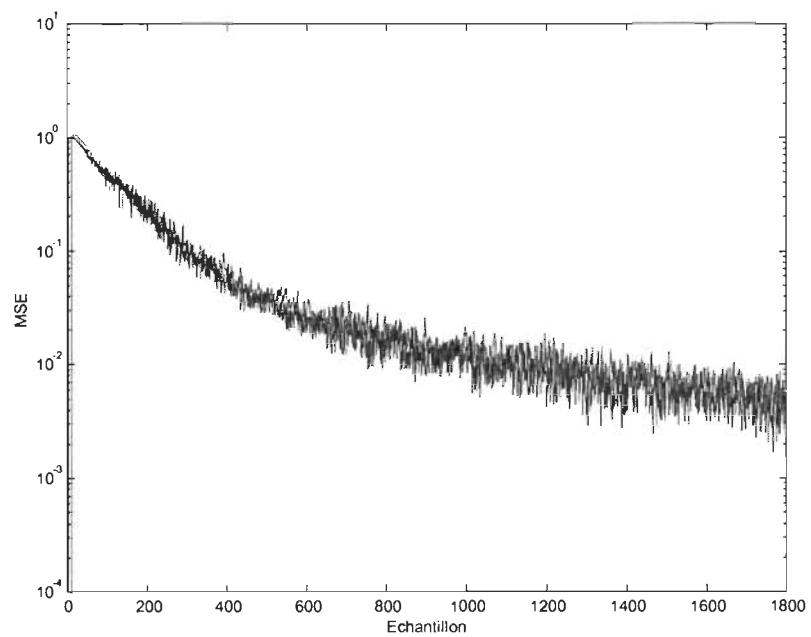

*Figure 5.14: Caractéristiques de convergence du réseau VHDL pour C1 non linéaire* \_\_\_\_\_ 99

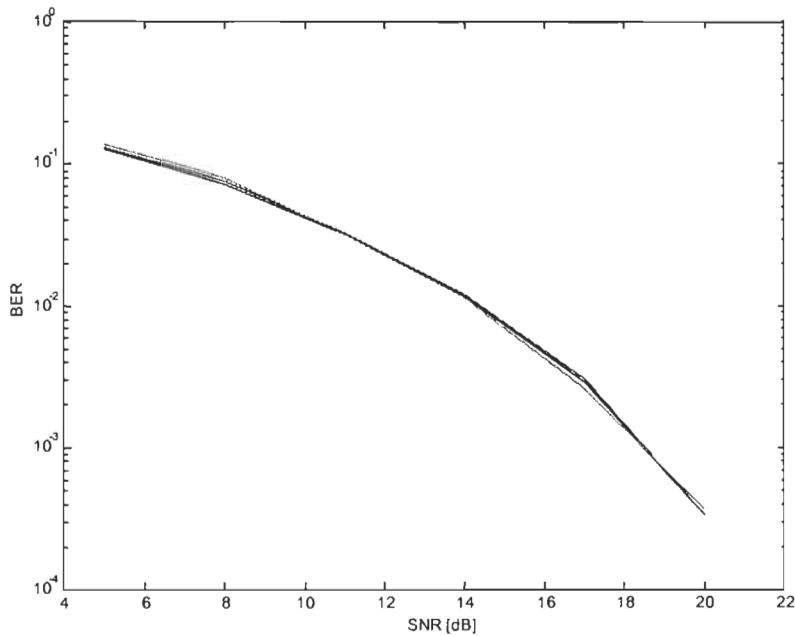

*Figure 5.15: Performances en égalisation du réseau VHDL pour C1 linéaire* \_\_\_\_\_ 100

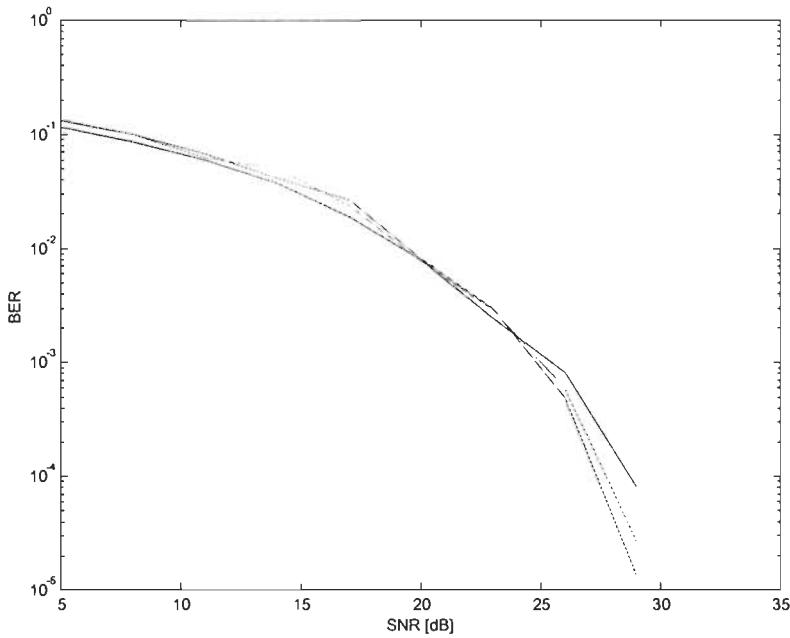

*Figure 5.16: Performances en égalisation du réseau VHDL pour C1 non linéaire* \_\_\_\_\_ 101

# Liste des tableaux

|                                                                                                           |     |

|-----------------------------------------------------------------------------------------------------------|-----|

| <i>Tableau 2.1 : Sommaire des méthodes classiques [HAY95]</i>                                             | 30  |

| <i>Tableau 4.1: Paramètres de simulation pour C1 linéaire</i>                                             | 62  |

| <i>Tableau 4.2: Paramètres du réseau pour C1 non linéaire</i>                                             | 67  |

| <i>Tableau 5.1: Éléments des architectures de calcul</i>                                                  | 73  |

| <i>Tableau 5.2: Équations de la fonction d'activation <math>f_{PL}(x)</math></i>                          | 84  |

| <i>Tableau 5.3: Table de correspondance du comparateur de magnitude</i>                                   | 87  |

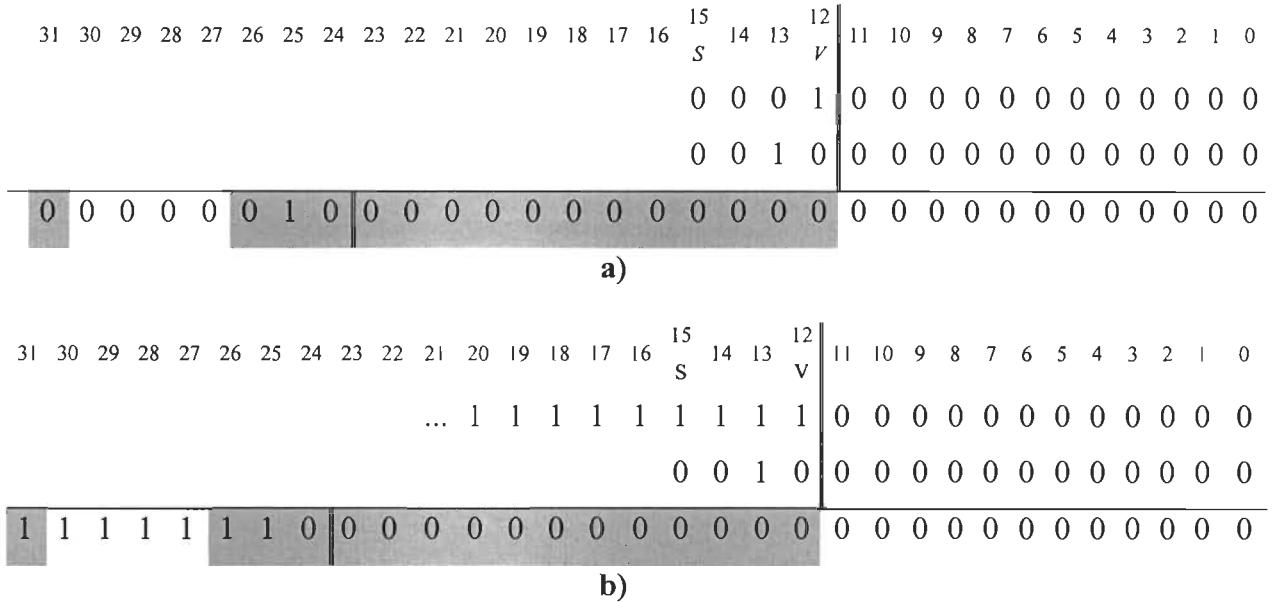

| <i>Tableau 5.4: Exemple d'orientation des bits a) <math>b = 0.5</math> b) <math>b = 0.125</math></i>      | 89  |

| <i>Tableau 5.5: Table de vérité pour l'exemple d'orientation des bits</i>                                 | 90  |

| <i>Tableau 5.6: DTXY pour <math>z1 = 1</math></i>                                                         | 91  |

| <i>Tableau 5.7: DTXY pour <math>z2 = 1</math></i>                                                         | 92  |

| <i>Tableau 5.8: DTXY pour <math>z3 = 1</math></i>                                                         | 92  |

| <i>Tableau 5.9: DTXY pour <math>z4 = 1</math></i>                                                         | 93  |

| <i>Tableau 5.10: Table de vérité pour <math>H', I', J'</math> et <math>K'</math> en <math>z4=1</math></i> | 93  |

| <i>Tableau 5.11: Résultats de la synthèse du réseau complet</i>                                           | 102 |

# *Liste des symboles et abréviations*

## *Symboles*

|                   |                                               |

|-------------------|-----------------------------------------------|

| $e$               | Erreurs de correction                         |

| $q$               | Vecteur des poids du neurone de sortie        |

| $s$               | Symbol transmis                               |

| $W$               | Matrice des poids de la couche cachée         |

| $x$               | Signal analogique de la sortie du réseau      |

| $y$               | Signal à la sortie du canal                   |

| $\mu$             | Pas d'apprentissage                           |

| $\eta$            | Bruit additif du canal                        |

| $D_1$             | Relaxation du délai                           |

| $D_2$             | Profondeur de pipeline de la boucle récursive |

| $LA$              | Relaxation de somme                           |

| $\tilde{\bullet}$ | Signal bruité                                 |

| $\hat{\bullet}$   | Estimé de                                     |

## *Abréviations*

|            |                                                                         |

|------------|-------------------------------------------------------------------------|

| BER        | Bit Error Rate                                                          |

| DFE        | Decision Feedback Equalizer                                             |

| ITGE -VLSI | Intégration à Très Grande Échelle – <i>Very Large Scale Integration</i> |

| LMS        | Least Mean Squares                                                      |

|      |                                                         |

|------|---------------------------------------------------------|

| MSE  | <i>Mean Square Error</i> – Erreur quadratique moyenne   |

| PAM  | Pulse Amplitude Modulation                              |

| QAM  | Quadrature Amplitude Modulation                         |

| QPSK | Quadrature Phased Shift Keying                          |

| RLS  | Recursive Mean Squares                                  |

| SNR  | <i>Signal to Noise Ratio</i> – Rapport signal sur bruit |

| RNA  | Réseau de neurones artificiels                          |

# *Chapitre 1*

## *Introduction*

De nos jours, la communication de l'information prend de plus en plus de place et d'importance dans notre quotidien. Que ce soit la téléphonie, la télévision ou l'Internet, il est évident que nous sommes constamment entourés par des systèmes de communications. Cette popularité des communications nous pousse d'ailleurs à continuellement augmenter les capacités des systèmes de transmissions d'information et c'est cette quête d'augmenter le débit de données qui est la motivation principale des recherches effectuées en communications.

Dans les systèmes modernes, on utilise de plus en plus les circuits numériques pour la réalisation pratique. Cette approche nous permet d'atteindre de meilleures performances au niveau de la fiabilité, de la flexibilité, de la simplicité et de la qualité de transmission.

Dans les systèmes de communications, on retrouve le maillon le plus faible au niveau du canal de transmission. Ce canal peut entre autre être une paire de fil torsadé, une

fibre optique, une liaison hertzienne, etc. Puisque nous ne pouvons pas interagir sur les paramètres de ce bloc, le développement de plusieurs techniques de traitement des signaux ont été adoptées pour minimiser son effet. Une méthode bien connue de nos jours est appelée l'égalisation des canaux de transmission [HAY96]. Cette égalisation devient absolument nécessaire lorsque nous désirons transmettre des données à fort débit dans un environnement très hostile (bruit, distorsion de phase et d'amplitude, etc.).

L'égaliseur nous permet alors de corriger les effets du canal de transmission et de retrouver le signal original. De plus, l'algorithme de l'égaliseur doit être de nature adaptative dans le sens où les paramètres de calcul doivent pouvoir être modifiés dans le temps. Cette particularité permet de pallier les variations des paramètres du canal à travers le temps. De plus, cette adaptation de paramètres permet de régler le filtre avec une connaissance minimale du canal de transmission.

## 1.1 Problématique

Pour transmettre des données de nature numérique, on a souvent recours à des techniques de modulation numérique. Ces techniques permettent d'exploiter la bande passante utile du canal de transmission avec une meilleure efficacité. Par contre, le passage des données dans le canal de transmission provoque de l'interférence entre les symboles (*ISI*: Interférence Inter-Symboles) d'une même séquence de données. Alors, pour pouvoir récupérer la séquence de données originales, il faut absolument avoir recours à un égaliseur qui corrigera l'effet de l'*ISI*.

On peut résumer le problème de l'égalisation des canaux lorsqu'on désire transmettre une séquence de données  $s(n)$  sur un canal quelconque de transmission. La sortie du canal nous donne le signal bruité  $\tilde{y}(n)$  qui est lié au signal  $s(n)$  original. Le signal  $\tilde{y}(n)$  sera alors utilisé pour reconstituer la séquence originale. Cette opération de reconstitution consiste à générer un signal  $\hat{s}(n)$  qui correspond à la séquence estimée de la séquence originale  $s(n)$ .

Plusieurs méthodes linéaires ont été proposées comme fonctions d'estimation [HAY96]. On retrouve par exemple les méthodes du gradient stochastique (*LMS*: Least Mean Square) et des moindres carrées (*RLS*: Recursive Least Square). Ces méthodes s'avèrent efficaces seulement si le système est linéaire. Dans certains systèmes, on retrouve la présence de non linéarité ce qui exige que l'égaliseur soit apte à éliminer cette non linéarité. Des propositions d'égaliseurs non linéaires ont d'ailleurs été présentées dans [VID99].

En plus de rencontrer les critères de performance selon un canal donné, les systèmes modernes doivent aussi rencontrer des critères d'implantation matérielle. Ces critères sont: la consommation en puissance, la vitesse maximale de calcul et d'exécution et le niveau de difficulté de l'implantation de l'algorithme (surface d'utilisation et/ou ressources matérielles). Pour rencontrer les critères de performances de l'application (taux d'erreurs binaires, temps d'adaptation, etc.), nous avons recours à des algorithmes adaptatifs qui permettent d'ajuster l'égaliseur. Afin d'atteindre de forts débits, on doit appliquer la

technique du pipeline sur l'architecture. Or, la plupart des algorithmes adaptatifs sont de nature récursive ce qui limite la profondeur de pipeline car l'algorithme a besoin de l'erreur à l'instant présent pour le calcul. Alors, pour pouvoir pipeliner les architectures récursives, nous avons recours à des techniques de transformation d'algorithmes qui introduisent des délais dans la boucle du calcul de l'erreur. Ces techniques nous permettent alors d'optimiser un ou plusieurs critères afin d'atteindre l'objectif visé par une application donnée.

L'application des techniques de pipeline classiques comme l'ajout de retard direct et la resynchronisation sont bien connues pour les algorithmes non récursifs [SHA98]. Dans le cas des algorithmes récursifs, diverses techniques de transformation d'algorithmes peuvent être employées mais leur application implique plusieurs compromis. Le projet de recherche proposé ici s'inscrit donc dans cette lignée et les principaux objectifs sont présentés à la section suivante.

## 1.2 Objectifs

Le but du présent projet consiste à appliquer les techniques de transformations sur les algorithmes récursifs actuellement rencontrés dans l'application à l'égalisation des canaux. La transformation de l'algorithme permettra d'augmenter le débit de l'égaliseur choisi. Le choix retenu doit tenir compte de l'intégration sur silicium de l'architecture résultante pour une éventuelle application réelle de l'égaliseur. De plus, la consommation en puissance sera aussi prise en considération dans le cas des applications portables. On peut résumer les objectifs de la recherche par les points suivants:

1. Études des algorithmes récursifs appliqués à l'égalisation des canaux selon les techniques de traitement numériques des signaux : algorithme *LMS*, algorithme *RLS*, filtre de Kalman, réseau de neurones.

2. Études des techniques de transformation d'algorithmes dans le but d'augmenter le débit des architectures. Attention particulière sur l'anticipation relaxée.

3. Proposition d'une méthode d'égalisation des canaux transformée par l'anticipation relaxée.

4. Évaluation des performances de la méthode retenue.

### 1.3 Méthodologie

Afin de bien cerner la problématique de transformation d'algorithme appliquée à l'égalisation des canaux en communication, on doit d'abord bien définir les différentes spécifications que l'égaliseur doit satisfaire. Pour ce faire, une analyse des différents canaux de transmission sera menée. Par la suite, nous verrons les principes et les différentes classes d'égaliseurs rencontrés dans les systèmes actuels sous la forme d'une synthèse [MAC98].

On abordera ensuite l'étude des différentes méthodes de transformation d'algorithmes en s'inspirant grandement de [SHA98]. Suite à l'étude des transformations, quelques méthodes comme l'anticipation, l'anticipation relaxée et la resynchronisation seront appliquées à des algorithmes simples comme le *LMS* pour en évaluer leur efficacité. L'étude des différents paramètres de la transformation permettra d'imposer les bornes

d'application et les grandes lignes d'influence des différentes techniques. On parlera alors de région de stabilité, de vitesse de convergence et d'erreur d'ajustement.

Des simulations à l'aide de l'outil *Matlab*<sup>TM</sup> seront menées et les résultats sous forme de graphiques et de tableaux seront présentés. Dans la mesure du possible, les résultats seront comparés aux valeurs théoriques pour vérifier les approximations et les hypothèses en cause.

#### **1.4 Organisation de ce rapport**

Nous verrons au Chapitre 2 les différents principes de l'égalisation adaptative des canaux en communications numériques. La section 2.1 traitera principalement de la communication numérique en général alors que la section 2.2 présentera les concepts des égaliseurs adaptatifs des canaux. Le chapitre 2 terminera sur les différentes contraintes quant à l'intégration des égaliseurs sur silicium.

Nous verrons au chapitre 3 les différentes techniques du pipeline. Les cas classiques seront présentés en 3.1 et 3.2 et nous verrons les différentes méthodes pour les algorithmes récursifs en 3.3 et 3.4. Par la suite, à la section 3.5, il sera question de l'application des techniques appliquées à l'égalisation des canaux avec un exemple d'application sur un filtre transverse linéaire adapté par la méthode *LMS*.

Le Chapitre 4 traitera du pipeline d'un égaliseur basé sur les réseaux de neurones. L'application des réseaux de neurones pour l'égalisation des canaux sera présenté en 4.1. Un rappel sur les réseaux de neurones en général sera ensuite présenté en 4.2 et nous verrons en 4.3 l'application de l'anticipation relaxée sur l'algorithme de rétropropagation du gradient. Les résultats de simulations seront enfin présentés en 4.4.

Le Chapitre 5 sera consacré à l'intégration de l'algorithme pipeliné de l'égaliseur à base de réseau de neurones. En 5.1, nous verrons l'architecture pipelinée du réseau de neurone. Nous présenterons en 5.2 les différents éléments de calculs dont l'architecture est composée. Enfin, en 5.3, nous présenterons les résultats de l'intégration dans *Synopsys*<sup>TM</sup> ainsi que des résultats de simulations qui démontrent le bon fonctionnement du réseau.

## *Chapitre 2*

### *Égalisations adaptatives de canaux en communications numériques*

L'élaboration d'un système de communication comporte une multitude de volets.

Pour mieux cerner le problème de l'égalisation des canaux, il est important de bien connaître les différents paramètres entourant les systèmes de communication. Nous verrons donc en premier lieu les systèmes de communications d'une façon générale en présentant les différents blocs du système. Par la suite, nous aborderons les principes de bases en communication numérique avec les techniques de modulation et de démodulation. Les différents modèles de canaux de communication seront aussi présentés. Les égaliseurs adaptatifs seront abordés en présentant leur principe et les différentes techniques utilisées. Nous verrons aussi les différentes techniques d'adaptation de ces égaliseurs.

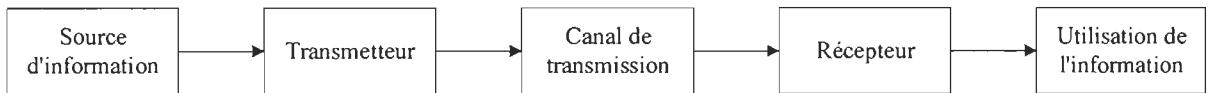

On peut représenter un système de communication par le schéma général de la Figure 2.1.

**Figure 2.1: Système de communication général**

Dans ce schéma général, on retrouve une source d'information qui peut être de la voix, des données, des mesures, etc. Cette information est ensuite acheminée vers un transmetteur qui transforme le signal de la source en une information qui peut être transmise sur le canal de transmission. Une fois que le signal est passé à travers le canal de transmission, il faut retrouver le message original. Pour ce faire, le bloc récepteur crée l'inverse du transmetteur et l'utilisateur ou le système peut ensuite récupérer l'information pour l'utiliser.

## 2.1 La communication numérique

Les avantages d'un système numérique par rapport aux systèmes analogiques ne sont plus à démontrer. Avec les systèmes numériques, il est possible d'améliorer grandement la flexibilité des communications. Nous sommes aussi en mesure d'atteindre de meilleures performances au niveau de la fiabilité, de la simplicité et de la qualité de transmission. Avec les systèmes numériques, nous avons beaucoup plus de latitude sur le contrôle de la qualité du signal. Par exemple, dans les transmissions sur longue distance, il est possible de régénérer le signal transmis par des répéitrices ce qui élimine l'effet du canal et du bruit sur le signal original. De cette façon, le signal reçu correspond exactement à ce qui a été transmis. En communication analogique, une telle régénération améliore certes la qualité du

signal reçu mais le signal régénéré est toujours de moindre qualité que le signal transmis [PRO95].

Un autre avantage se situe au niveau de la redondance dans l'information. Dans les systèmes numériques, il est possible d'éliminer cette redondance avant la modulation permettant de conserver la bande passante utile du canal de transmission au maximum. Enfin, le coût des systèmes de communications est souvent moindre que celui des systèmes de communications analogiques offrant les mêmes performances.

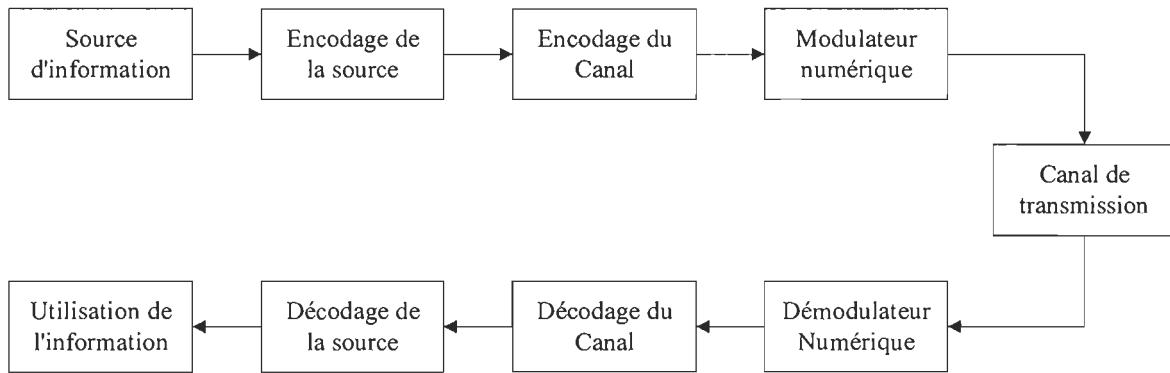

Le schéma général d'un système de communication numérique est présenté à la Figure 2.2 :

**Figure 2.2: Système de communication numérique**

Dans ce schéma, la source d'information peut être un signal de nature numérique ou analogique. Dans le cas d'un signal analogique, il faut le convertir en un signal numérique de dimension finie. Dans la plupart des cas, les signaux numériques sont en fait une séquence de nombres binaires. De façon idéale, il faut coder l'information sur le moins de bits possibles pour garder le débit d'information le plus bas possible. Cette fonction de

quantification est assurée par le bloc *Encodage de la source*. On peut aussi retrouver des techniques de compression des données dans ce même bloc.

Par la suite, le signal est introduit dans le bloc *Encodage du Canal* dont la fonction principale est de contrôler la redondance rencontrée dans la séquence binaire. Cette opération permet de minimiser l'effet du bruit introduit par le canal sur le signal et ainsi améliorer la qualité à la réception.

Ensuite, nous avons le modulateur numérique qui permet d'interfacer la séquence binaire au canal de transmission. Pour ce faire, le modulateur transforme la séquence en un signal électrique donné. Il est possible de transmettre les bits  $b$  un à la fois ou en les regroupant pour transmettre un groupe de bits en même temps. Cette dernière méthode est connue sous le nom de modulation *M-aire* où  $M$  représente le nombre de groupe possible ( $M=2^b$ ). Nous verrons plus de détails sur ces techniques au cours du rapport.

Le signal est ensuite introduit dans le canal de transmission. Ce canal sera expliqué en détails plus loin et on peut résumer son effet en disant qu'il introduit une distorsion (phase, amplitude et bruit) sur le signal transmis.

À la réception, on retrouve le démodulateur numérique qui est idéalement le traitement inverse du modulateur. Cette section peut devenir très élaborée car le signal reçu est très différent de ce qui a été transmis. C'est d'ailleurs au niveau de ce bloc que la majorité des recherches s'effectuent de nos jours. Avant de prendre une décision sur le signal reçu, il

faut éliminer l'effet du canal. Cette opération est souvent effectuée par l'égaliseur. Nous verrons plus loin les différents types d'égaliseurs que nous retrouvons aujourd'hui.

### 2.1.1 *Principes de modulation et de démodulation*

Toujours dans le but de minimiser le taux de données transmises, les techniques de modulations numériques permettent de regrouper l'information dans le but de la condenser sur les différents paramètres de la porteuse. Le but ici est de maximiser l'utilisation de la bande passante disponible sur le canal de transmission. Voyons le principe de la modulation numérique dans le cas d'une liaison hertzienne.

Dans les applications de communication sans fil, il est absolument nécessaire d'utiliser une onde porteuse à haute fréquence. En effet, la longueur des antennes de transmission et de réception doit être d'environ  $\lambda/4$  où  $\lambda$  représente la longueur d'onde de la porteuse. Cette longueur d'onde est donnée par (2.1).

$$\lambda = \frac{c}{\sqrt{\epsilon_r} f} \quad (2.1)$$

où  $c$  représente la vitesse de la lumière,  $\epsilon_r$  représente la permittivité relative du milieu et  $f$  est la fréquence de la porteuse.

Dans l'air, la permittivité relative est d'environ 1 et la vitesse de la lumière est fixe à  $3 \times 10^8$  m/s. Dans le cas où la porteuse serait de 1kHz, la longueur d'onde nous donnerait  $\lambda=300$ km. Il est évident qu'une antenne de 75km ( $\lambda/4$ ) est physiquement très difficile à réaliser et très peu pratique. Donc, pour faciliter la réalisation pratique, des fréquences de

l'ordre des Mégahertz (MHz) sont utilisées pour transmettre l'information. Par exemple, certains téléphones sans fils utilisent une porteuse de 1.2GHz ce qui donne  $\lambda=25\text{cm}$  d'où la longueur de l'antenne est de 6.25cm. Cette longueur est donc facilement réalisable pour les applications portables.

Puisque nous utilisons des fréquences pures comme porteuse, nous pouvons écrire l'équation générale d'une onde sinusoïdale par:

$$p(t) = A \cos(\omega t + \theta) \quad (2.2)$$

Dans cette équation, nous retrouvons l'amplitude de l'onde  $A$ , la fréquence angulaire  $\omega$  et la phase  $\theta$ . Pour moduler l'information sur la porteuse, il s'agit de faire varier un des trois paramètres ( $A$ ,  $\theta$ ,  $\omega$ ) par le signal porteur d'information (signal modulant). On peut donc réécrire (2.2) sous la forme:

$$p_M(t) = A(t) \cos(\omega(t)t + \phi + \theta(t)) \quad (2.3)$$

Où  $A(t)$ ,  $\omega(t)$  et  $\theta(t)$  sont les paramètres qui sont régis par le signal modulant.

Dans les communications analogiques, on retrouve trois types de modulation: la modulation d'amplitude (AM) qui utilise la fonction  $A(t)$ , la modulation de fréquence (FM) qui utilise la fonction  $\omega(t)$  et la modulation de phase (PM) qui utilise la fonction  $\theta(t)$ .

Dans les communications numériques, les fonctions  $A(t)$ ,  $\omega(t)$  et  $\theta(t)$  sont contrôlées par l'information binaire à transmettre. L'information binaire peut être représentée par

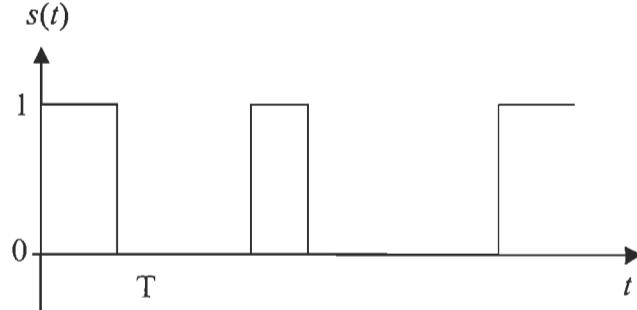

différentes formes d'ondes. Sa forme la plus simple est certes l'onde tout ou rien tel que montré à la Figure 2.3.

**Figure 2.3: Information binaire classique**

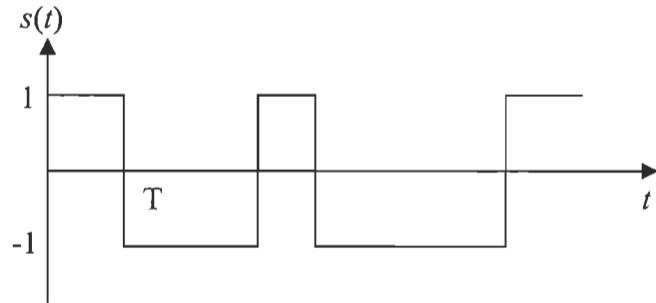

Une autre représentation des données peut se faire avec une moyenne nulle que l'on nomme non retour à zéro (NRZ). La Figure 2.4 montre bien la représentation de ce type de données.

**Figure 2.4: Format de données NRZ**

Pour transmettre les données sur le canal, l'information binaire contrôle la valeur de l'amplitude, de la phase ou de la fréquence de l'onde porteuse. Une combinaison des paramètres est aussi possible. La modulation numérique la plus simple est la modulation d'amplitude tout ou rien (ASK: *Amplitude Shift Keying* ou OOK: *On Off Keying*). Le principe de cette modulation est de transmettre la porteuse seulement lorsque la valeur du bit au temps  $t$  est d'amplitude  $A$ . Si la vitesse de la porteuse est beaucoup plus grande que la

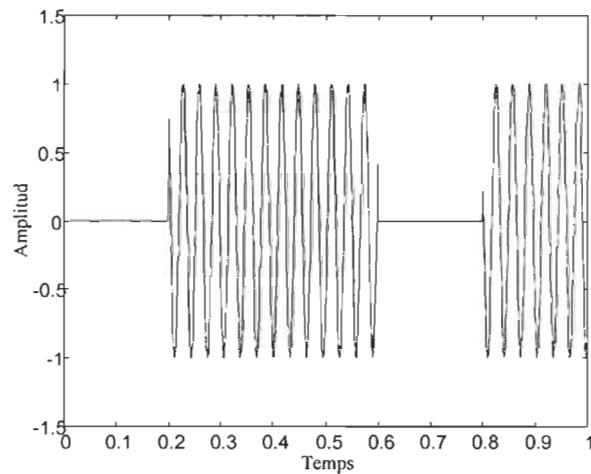

vitesse de l'information, on peut obtenir le signal modulé tel que montré à la Figure 2.5 (à titre d'exemple).

On voit dans cet exemple que la séquence transmise est 01101 (largeur des bits de 0.2 seconde) ce qui correspond aux endroits où la porteuse est présente ou non. Ce genre de modulation est utilisé dans le cas des communications à faibles débits sans contrainte dans l'utilisation spectrale du canal. Si on désire améliorer le taux d'utilisation de la bande passante, il est nécessaire de varier simultanément plusieurs paramètres de l'onde porteuse.

**Figure 2.5: Signal ASK**

Ce type de modulation n'utilise non pas un seul bit à la fois mais elle regroupe les bits en  $M$  symboles selon une règle définie. La valeur de  $M$  est définie par le nombre de bits  $b$  encodés à la fois soit  $M = 2^b$ . On appelle ce type de regroupement *M-aire*.

La façon de transmettre les symboles donne lieu au type de modulation en cause. On retrouve plusieurs méthodes de modulation des symboles et les principales sont la

modulation de phase (*PSK*: *Phase Shift Keying*) et la modulation de quadrature (*QAM*: *Quadrature Amplitude Modulation*). Selon le nombre de bits codés dans un même symbole, on nomme les modulations en fonction de  $M$  soit  $M$ -*PSK* ou  $M$ -*QAM*. Voyons maintenant les grandes lignes de la modulation  $M$ -*QAM*.

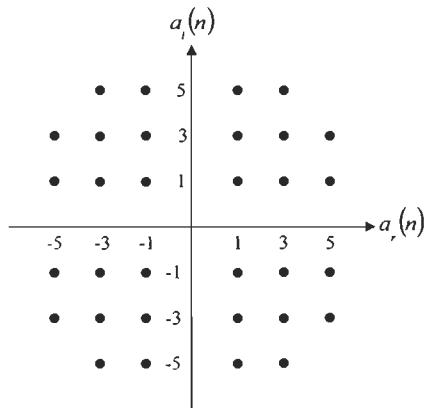

Le principe de la modulation *QAM* est de varier la phase et l'amplitude de la porteuse pour transmettre les symboles. Nous avons alors recours à une représentation dans le plan complexe de la résultante du codage des symboles. La Figure 2.6 nous montre le plan complexe pour une modulation 32-*QAM*.

**Figure 2.6: Constellation 32-*QAM***

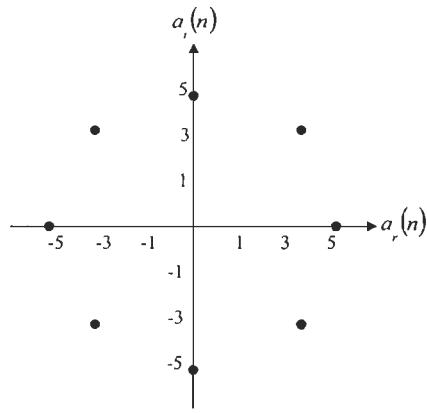

Nous avons alors deux variables soient  $a_r(n)$  et  $a_i(n)$  qui représentent respectivement la valeur de la composante réelle et complexe du symbole à transmettre. Les points représentent ici la valeur de l'amplitude et de la phase de la porteuse à transmettre. Dans le cas du  $M$ -*PSK*, la valeur de l'amplitude est fixe et ce n'est que la phase qui change. La Figure 2.7 nous montre le cas du 8-*PSK* afin de voir la différence avec la modulation *QAM*.

Figure 2.7: Constellation 8-PSK

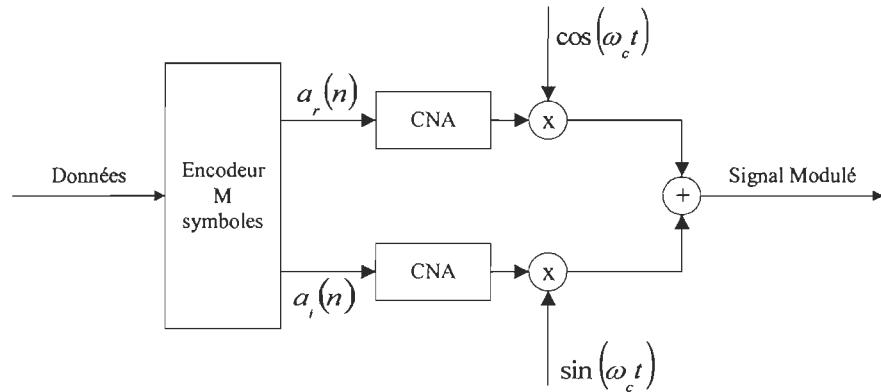

Voyons maintenant le schéma général du modulateur *QAM* que nous présentons à la Figure 2.8.

Figure 2.8: Modulateur *QAM*

On retrouve en premier lieu un encodeur qui associe les valeurs à  $a_r(n)$  et  $a_i(n)$ . Par la suite, ces valeurs réelles et complexes sont converties en échantillons analogiques (*CNA*: *Convertisseur Numérique à Analogique*) et sont multipliées par les deux ondes porteuses en quadrature. La sommation des deux ondes donne alors le signal contenant l'information

complexe du symbole original. Ce signal résultant peut être modulé à son tour dans le but de le déplacer en fréquence et ainsi être transmis sur le canal de transmission.

Ce genre de modulation est aujourd'hui très populaire. On retrouve d'ailleurs, à titre d'exemple, les modems de communication sur la ligne téléphonique. Pour augmenter le débit de transmission et aussi améliorer le taux d'utilisation du canal, nous n'avons qu'à augmenter le nombre de symboles. Par contre, l'augmentation du nombre de symboles demeure un risque car le bruit du canal rend la détection difficilement réalisable de façon simple. En effet, puisque le canal de transmission et la variation de l'amplitude des symboles sont limités, la distance entre 2 symboles de la constellation devient très petite lorsque  $M$  augmente. Or, en présence d'interférence inter-symbole et de bruit, le récepteur ne pourra récupérer sans erreur les symboles transmis. Il est alors nécessaire de minimiser l'effet du canal sur le signal porteur d'information et c'est dans cette optique que la notion d'égaliseur entre en jeu.

Figure 2.9: Démodulateur *QAM*

Dans le cas des récepteurs optimums, on utilise des filtres adaptés pour la démodulation et la décision des signaux reçus. On peut représenter le démodulateur *QAM* optimum par le schéma de la Figure 2.9 [STR90]. Ce genre de démodulateur est appelé détecteur de corrélation. Si le canal est plus hostile, il devient nécessaire d'utiliser un égaliseur. Avant d'aborder ce sujet, voyons les différents types de canaux de transmissions.

### *2.1.2 Modèles de canaux de transmission*

Tel que nous l'avons mentionné précédemment, le canal de transmission constitue en grande partie la problématique d'un système de communication. Peu importe sa nature, il demeure un paramètre que nous ne pouvons pas changer. Au mieux, nous pouvons en élaborer un modèle très précis mais dans plusieurs cas, un modèle unique ne peut être clairement établi. Une analyse statistique est alors nécessaire afin d'obtenir un modèle de canal représentatif de la réalité.

Les canaux de communications sont souvent modélisés sous forme mathématique pour permettre de mesurer les performances du système dans un environnement donné. Cette modélisation est basée surtout sur des observations et représente une approximation acceptable de la réalité. Le modèle du canal est divisé en deux sections. Nous avons premièrement sa réponse impulsionnelle et ensuite le type de bruit ajouté (additif, multiplicatif, blanc Gaussien, etc.).

En pratique, on retrouve principalement 4 types de canaux de transmission que nous présentons ici :

- Canal linéaire et invariant dans le temps (*LTI*)

- Canal linéaire et variant dans le temps (*LTV*)

- Canal non linéaire et invariant dans le temps (*NLTI*)

- Canal non linéaire et variant dans le temps (*NLTV*)

Les systèmes opérant avec des canaux linéaires sont évidemment plus simples à réaliser. Le schéma de la figure suivante représente le modèle du canal linéaire et variant dans le temps.

**Figure 2.10: Schéma du canal linéaire et variant dans le temps**

Dans le schéma de la Figure 2.10,  $s(n)$  représente les données numériques originales.  $h(n,t)$  représente la réponse impulsionnelle du canal en cause. Le coefficient  $\eta(n)$  représente un bruit blanc Gaussien de moyenne nulle. Enfin,  $\tilde{y}(n)$  représente le signal à l'entrée du récepteur.

On peut montrer que le canal linéaire se comporte souvent comme un filtre passe-bas à réponse impulsionnelle finie (*FIR*) causale, dont l'équation est une simple convolution [PRO95]. Pour un canal linéaire et invariant dans le temps, l'équation du canal est :

$$\tilde{y}(n) = \left\{ \sum_{p=0}^{P-1} h(p)s(n-p) \right\} + \eta(n) \quad (2.4)$$

Dans cet exemple,  $\tilde{y}(n)$  est le signal à l'entrée du récepteur,  $h(p)$  représente les coefficients de la réponse impulsionnelle du canal (de longueur  $P$ ),  $s(n)$  représente la séquence de données transmises et  $\eta(n)$  représente le bruit à l'instant  $n$ .

Un modèle de canal non linéaire est souvent représenté par une partie linéaire, une partie non linéaire et un bruit additif. Le schéma de la Figure 2.11 nous montre un tel type de canal.

**Figure 2.11: Modèle de canal non linéaire**

L'équation régissant un tel type de canal peut être donnée, à titre d'exemple, par l'équation (2.5).

$$\begin{aligned} \tilde{y}(n) &= 0.5v(n) + v^3(n) + \eta(n) \\ v(n) &= 0.25s(n-2) + s(n-1) + 0.25s(n) \end{aligned} \quad (2.5)$$

On remarque dans cet exemple que la non linéarité du canal est de forme polynomiale ce qui est souvent le cas en pratique. Il est possible de créer un égaliseur non linéaire permettant de minimiser son effet. De plus, il est possible que les coefficients du canal

varient en fonction du temps (canal  $NLTV$ ) ce qui implique une adaptation des paramètres de l'égaliseur dans le temps.

## 2.2 Égaliseurs adaptatifs des canaux

Puisque nous ne pouvons pas interagir sur les paramètres du canal de transmission, plusieurs techniques de traitement des signaux ont été développées pour minimiser son effet. On appelle cette méthode l'égalisation des canaux de transmission.

### 2.2.1 *Principe de l'égalisation*

Le premier rôle de l'égaliseur dans les systèmes de communication est d'annuler l'effet du canal sur le signal porteur d'information. Plusieurs méthodes peuvent être employées selon le type de canal que nous avons. Le schéma de la Figure 2.12 illustre bien la position de l'égaliseur dans un système de réception en communication numérique sans fil.

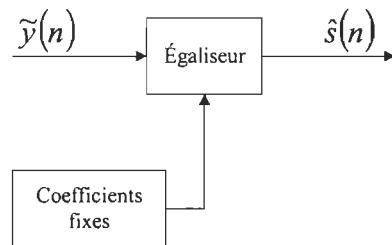

En pratique, on retrouve principalement 2 types de récepteurs. Le premier type est appelé récepteur optimal. Ce genre de récepteur est caractérisé par un égaliseur dont les paramètres de correction sont fixes dans le temps. C'est-à-dire que nous connaissons a priori les caractéristiques (réponse impulsionnelle ou réponse fréquentielle) du canal utilisé. Avec ces paramètres, la conception de l'égaliseur revient à créer l'inverse du canal de transmission.

**Figure 2.12: Récepteur en communications numériques sans fil**

Dans certains cas, l'utilisation de ce type de récepteur permet d'obtenir des performances satisfaisantes et l'avantage important réside dans la rapidité d'exécution de ce genre d'égaliseur. Le schéma de la Figure 2.13 nous montre un tel type d'égaliseur.

**Figure 2.13: Schéma du récepteur optimum**

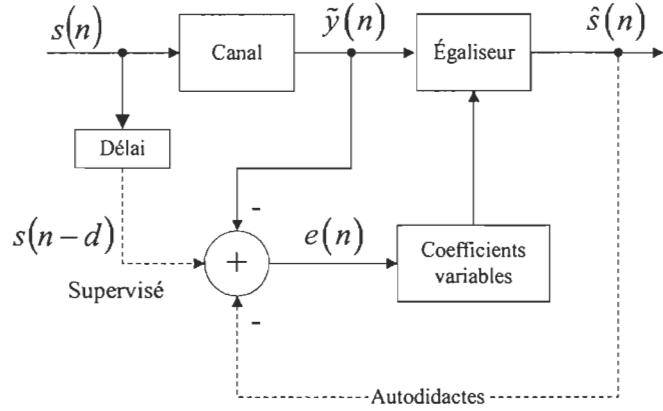

Le deuxième type de récepteur est nommé sous optimum car la fonction de transfert de l'égaliseur est créée à partir d'une estimation des paramètres du canal. Dans ce cas, il est possible d'avoir des paramètres d'égalisation variables dans le temps. Le récepteur est donc doté d'un algorithme qui adapte les coefficients de l'égaliseur. Ces paramètres peuvent être calculés à partir d'une séquence de données connues du transmetteur et du récepteur (mode supervisé) ou de façon autodidacte par un retour statistique sur la sortie de l'égaliseur. La

Figure 2.14 montre un tel type de récepteur (à noter que les types autodidactes et supervisés sont tous deux montrés) :

**Figure 2.14: Schéma du récepteur sous optimum**

### 2.2.2 Les techniques de l'égalisation

Les égaliseurs peuvent être divisés en trois familles principales :

- Égaliseurs transverses linéaires

- Égaliseur par retour de décision (*Decision Feedback Equalizer « DFE »*)

- Égaliseur par maximum de vraisemblance (*Maximum Likelihood Sequence Estimator « MLSE »*)

L'architecture des égaliseurs transverses linéaires est donnée par la Figure 2.15.

Dans ce schéma, on suppose une égalisation de type supervisée. Pour ce type d'égaliseur, l'algorithme d'adaptation utilise l'erreur entre la sortie de l'égaliseur et la donnée originale.

On qualifie cette différence d'erreur de reconstitution. Dans la famille des égaliseurs

transverses linéaires, on retrouve principalement les algorithmes d'adaptation suivants: *Least Mean Square (LMS)*, *Recursive Least Square (RLS)* et les filtres de Kalman [MAC98]. Nous verrons plus loin un résumé de ces techniques.

Figure 2.15: Égaliseur transverse linéaire

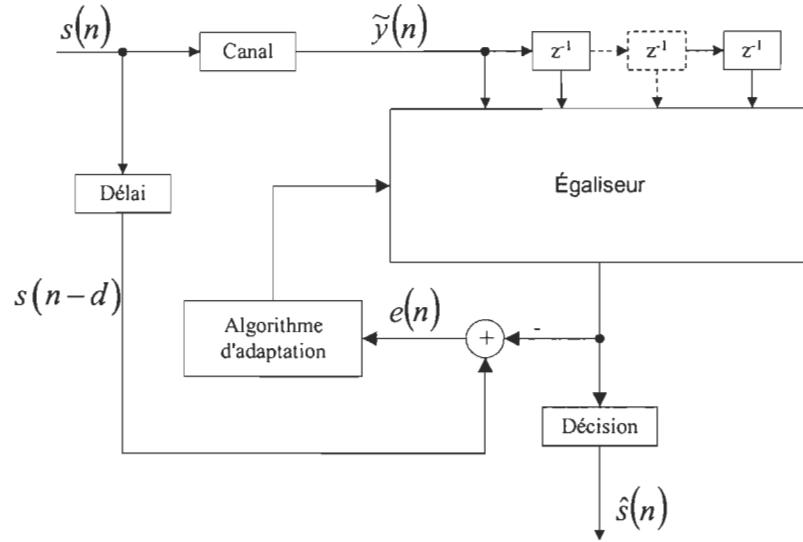

La Figure 2.16 nous montre le schéma de l'égaliseur *DFE*. Ce type d'égaliseur possède une nature non linéaire. Ce type d'égaliseur est caractérisé par l'ajout d'un deuxième filtre transverse dans la rétroaction. Ce filtre permet, pour l'estimation présente, d'éliminer l'interférence inter symbole causée par la détection des symboles précédents [HAY95]. L'adaptation des coefficients des filtres se fait de façon linéaire par un algorithme *LMS* ou *RLS*.

**Figure 2.16: Égaliseur à retour de décision**

Une autre remarque intéressante concerne le mode d'apprentissage. Selon la Figure 2.16, l'erreur  $e(n)$  peut être calculée à partir de la décision ou de la séquence originale. Prenons le cas où l'on utilise la décision pour le calcul de  $e(n)$ . Si le canal en cause n'est pas connu et que les poids des filtres sont initialisés à 0, l'égaliseur peut mettre un temps très long avant de converger vers un minimum. Cet effet s'explique par le fait que la décision  $\hat{s}(n)$  n'est pas valide pour les premiers échantillons. Il faut alors incorporer une phase d'apprentissage qui utilise la séquence originale  $s(n)$  pour adapter les poids des filtres. Une fois la convergence obtenue, on peut utiliser la décision pour le calcul de l'erreur ce qui élimine la nécessité de connaître les données originales. Il est bon de souligner que les variations dans les paramètres du canal ne doivent pas être trop rapides pour conserver les performances de l'égaliseur. Enfin, si les paramètres du canal sont

connus, les poids peuvent être initialisés à des valeurs prédefinies ce qui élimine la phase d'apprentissage.

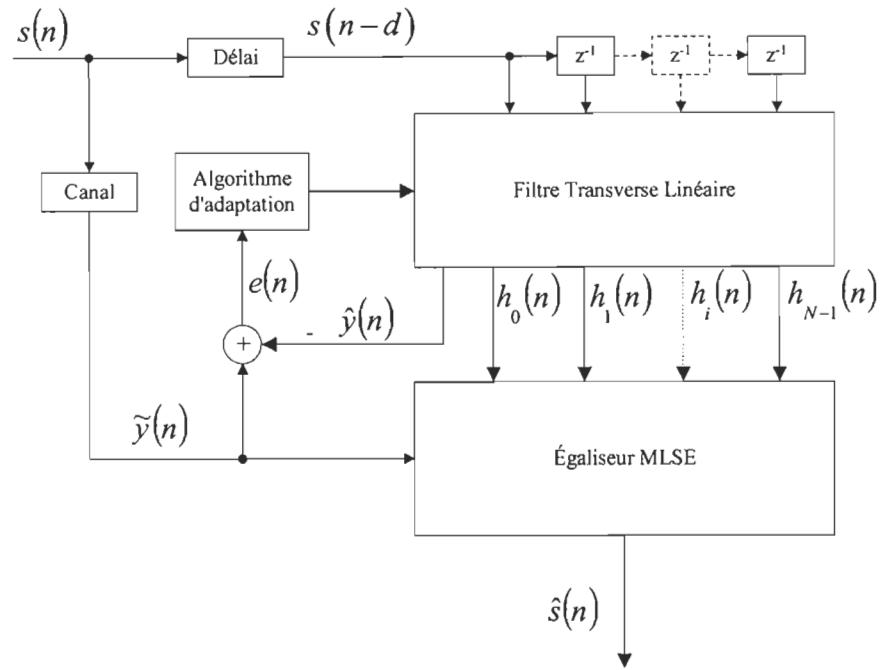

Le troisième type d'égaliseur est appelé égaliseur du maximum de vraisemblance (*MLSE*). L'approche consiste en l'estimation de la séquence transmise la plus vraisemblable. En effet, puisque les canaux créent une corrélation entre les échantillons (convolution), il est possible de retirer cette corrélation des données en connaissant ses paramètres. Ce genre d'égaliseur nécessite donc la connaissance des paramètres du canal en cause. Si le canal en cause est variant dans le temps, il est nécessaire d'intégrer un estimateur de canal adaptatif. Ce dernier peut être basé sur le filtre de Kalman ou un filtre transverse linéaire avec adaptation par *LMS* ou *RLS*.

L'algorithme de Viterbi est le plus répandu dans la détection des codes convolutifs. Son principal désavantage réside dans sa complexité de calcul et c'est pour cette raison qu'on le retrouve très rarement en pratique. La Figure 2.17 nous montre l'application de ce genre d'égaliseur. Nous pouvons mentionner que ce type d'égaliseur est très performant. Il sert souvent de référence afin de comparer les performances des différents types d'égaliseurs [HAY96].

Figure 2.17: Égaliseur MLSE

### 2.2.3 Les techniques d'adaptation des égaliseurs

L'adaptation des coefficients des égaliseurs se fait majoritairement par des algorithmes linéaires. Ces algorithmes sont basés sur les propriétés statistiques des signaux en cause. Les algorithmes les plus souvent rencontrés sont le *LMS*, le *RLS* et tous leurs dérivés. L'avantage du *LMS* réside dans sa simplicité de calcul. En effet, lors d'une *ITGE*, cette caractéristique devient primordiale. Par contre, le choix du paramètre d'adaptation est très délicat ce qui limite la plage d'application. Un mauvais choix peut résulter en une divergence de l'algorithme ou en une convergence terriblement lente.

L'algorithme *RLS* est pour sa part assez performant au niveau de la vitesse de convergence et de la stabilité. Cependant, son application aux *ITGE* est limitée car la méthode demande une complexité de calcul assez grande. De plus, la nécessité d'effectuer une division limite beaucoup sa rapidité.

La particularité des deux algorithmes est leur nature récursive. En d'autres termes, la sortie d'un système quelconque que nous définissons  $r(n)$  dépend des résultats précédents  $r(n-M)$  où  $M$  est un entier positif correspondant à la profondeur de pipeline. Pour des applications à très hauts débits, un problème se pose car la vitesse de calcul est limitée par la longueur de la boucle récursive (valeur de  $M$ ). Même s'il est possible de rendre parallèle le filtre transverse, il est souvent nécessaire de recourir aux techniques de pipeline à l'intérieur même de l'algorithme pour atteindre de forts débits de calculs. Plus la valeur de  $M$  est élevée, plus on pourra raffiner le pipeline de l'architecture ce qui justifie l'utilisation de techniques de transformations d'algorithmes. Ces techniques permettent d'ajuster la valeur de  $M$  et ainsi, de varier la profondeur de pipeline. On retrouve dans la littérature des techniques de transformation comme le traitement parallèle, la resynchronisation, le pliage, le déploiement ou l'anticipation (*look-ahead*) [SHA98]. Les détails de ces techniques de pipeline sont présentés au chapitre suivant.

Le Tableau 2.1 donne une synthèse des calculs de chaque méthode *RLS* et *LMS* [VID99]. Dans ces équations,  $\tilde{\mathbf{y}}$  et  $\mathbf{w}$  représentent respectivement  $[\tilde{y}(n) \ \tilde{y}(n-1) \ \tilde{y}(n-2)..\tilde{y}(n-N+1)]^T$  et  $[w_1(n) \ w_2(n) \ w_3(n)..\mathbf{w}_N(n)]^T$

Tableau 2.1 : Sommaire des méthodes classiques [HAY95]

|                                                                                                                                              |        |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------|

| <b>LMS</b>                                                                                                                                   |        |

| $\hat{x}(n) = \mathbf{w}^T (n-1) \tilde{\mathbf{y}}(n)$                                                                                      | (2.6)  |

| $e(n) = s(n-d) - \hat{x}(n)$                                                                                                                 | (2.7)  |

| $\mathbf{w}(n) = \mathbf{w}(n-1) + \mu \tilde{\mathbf{y}}(n) e(n)$                                                                           | (2.8)  |

| <b>RLS</b>                                                                                                                                   |        |

| $\hat{x}(n) = \mathbf{w}^T (n-1) \tilde{\mathbf{y}}(n)$                                                                                      | (2.9)  |

| $P(n) = \frac{1}{\lambda} P(n-1) - \frac{1}{\lambda} K(n) \tilde{\mathbf{y}}^T(n) P(n-1)$                                                    | (2.10) |

| $K(n) = \frac{1}{\lambda} * \frac{P(n-1) \tilde{\mathbf{y}}(n)}{1 + \frac{1}{\lambda} \tilde{\mathbf{y}}^T(n) P(n-1) \tilde{\mathbf{y}}(n)}$ | (2.11) |

| $\mathbf{w}(n) = \mathbf{w}(n-1) + K(n) e(n)$                                                                                                | (2.12) |

| $e(n) = s(n-d) - \hat{x}(n)$                                                                                                                 | (2.13) |

# *Chapitre 3*

## *Techniques du pipeline*

Dans le traitement numérique des signaux, il existe plusieurs méthodes de calculs. Puisque les signaux sont de nature discrète (quantifiée), nous définissons une base de temps discrète. Nous parlerons alors d'échantillons au temps  $n$  où l'instant  $n$  représente le temps actuel dans le domaine discret. Un échantillon appartenant au passé est nécessairement un échantillon du temps  $(n-M)$  et un échantillon futur est du temps  $(n+M)$  où  $M$  est un nombre entier positif.

Les différents algorithmes utilisent alors un ou plusieurs échantillons du domaine  $n$  pour calculer la réponse désirée. La séquence d'échantillons utilisés détermine le type d'algorithme en cause. Il existe plusieurs types d'algorithmes selon la séquence de données utilisées. Les algorithmes non récursifs ne sont fonction que des échantillons entrant dans l'architecture de calcul. Par contre, un algorithme est dit récursif si le calcul de la sortie nécessite les résultats antérieurs de la même opération. En d'autres termes, une sortie que nous définissons  $r(n)$  est fonction des résultats précédents  $r(n-M)$ . Dans [SHA98], il est

montré que de nos jours, les différents types d'algorithmes (récursifs ou non) doivent être utilisés dans des applications où le débit de l'information est très rapide. Pour ce faire, on doit avoir recours aux techniques de pipeline.

Le principe du pipeline est simple. Il consiste à ajouter des registres entre les étapes de calculs qui permettront soit d'augmenter la rapidité d'exécution ou de diminuer la consommation de puissance (en diminuant la fréquence d'horloge). La profondeur de pipeline (ou le raffinage) est caractérisée par le nombre de registres présents entre les différents étages de calculs. Dans le cas des algorithmes récursifs, cette profondeur est limitée par la valeur de  $M$ . Dans le cas où  $M$  est faible ou unitaire, il est nécessaire de transformer l'algorithme pour atteindre une profondeur de pipeline satisfaisante.

### 3.1 Méthode de resynchronisation

La méthode de resynchronisation ("retiming") n'est pas qualifiée de technique de pipeline proprement dite. Cette technique est appliquée pour redistribuer les registres inhérents de l'architecture ou les registres que le pipeline a introduit à travers l'architecture. Le principe est de transférer les registres d'un arc à l'autre sans altérer la séquence de sortie. Il est bon de noter que cette technique s'applique à toutes les architectures [SHA98].

Voyons un exemple d'application de la technique avec le filtre à réponse impulsionnelle finie (*FIR: Finite Impulse Response*) de la Figure 3.1 (les coefficients de multiplication sont inclus dans les multiplicateurs):

Figure 3.1: FIR avant resynchronisation

|     |                                                            |

|-----|------------------------------------------------------------|

| ◻   | Registre - délai de 1 cycle d'horloge ( $z^{-1}$ )         |

| xD  | $x$ Registres - délai de $x$ cycles d'horloge ( $z^{-x}$ ) |

| (x) | Multiplieur                                                |

| (+) | Additionneur                                               |

La vitesse maximale que ce filtre peut atteindre est délimitée par le chemin critique de calcul. Dans ce cas, le chemin critique avant que la sortie  $y(n)$  soit stable est donné par:

$$\tau_{crit} = \tau_{mult} + 3\tau_{add}$$

où

$$\tau_{mult} = \text{Temps d'un multiplieur} \quad (3.1)$$

$$\tau_{add} = \text{Temps d'un additionneur}$$

Pour diminuer le chemin critique, on applique la resynchronisation sur les 3 registres ( $3D$ ) présents à la sortie de l'architecture. Le principe est de redistribuer les registres de la branche sortante d'une opération (addition, multiplication, etc.) vers les branches entrantes. Effectuons la première passe qui consiste à redistribuer deux registres vers l'entrée du dernier additionneur. Un registre est gardé à sa sortie pour la synchronisation du système. La Figure 3.2 montre le résultat.

Figure 3.2: Resynchronisation du FIR étape 1

On voit qu'après la première étape, le chemin critique de la dernière branche est maintenant:

$$\tau_{crit} = \max\{\tau_{mult}, \tau_{add}\} \quad (3.2)$$

Par contre, le délai de l'architecture complète demeure grand et correspond maintenant à:

$$\tau_{crit} = \tau_{mult} + 2\tau_{add} \quad (3.3)$$

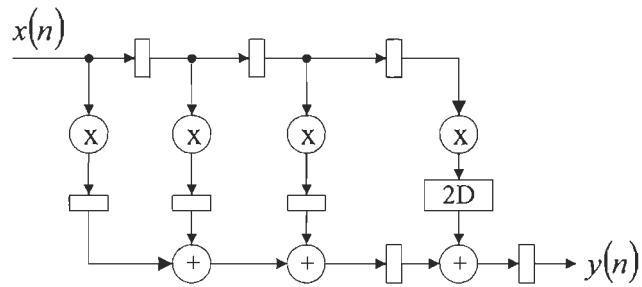

Pour diminuer ce délai, on applique une deuxième et une troisième passe de resynchronisation pour enfin arriver à l'architecture de la Figure 3.3.

Figure 3.3: FIR après resynchronisation complète

Le chemin critique du filtre complet est alors donné par l'éq (3.4):

$$\tau_{crit} = \max\{\tau_{mult}, 2\tau_{add}\} \quad (3.4)$$

Dans le cas où le délai de deux additionneurs est plus faible que la somme du délai d'un additionneur et d'un multiplicateur, il y a un gain au niveau de la vitesse maximale de calcul. De plus, on remarque que l'application de la resynchronisation n'altère pas la latence du filtre qui est de 3 cycles d'horloge dans ce cas.

### 3.2 Pipeline classique

Dans l'exemple précédent, la présence des 3 registres à la sortie du filtre nous permet d'appliquer la resynchronisation pour améliorer le chemin critique de l'architecture. Souvent, ces registres sont inexistant et pour pallier cet inconvénient, on applique la technique de pipeline classique [SHA98]. Notons que le pipeline classique s'applique dans le cas des algorithmes non récursifs. Il est donc possible d'ajouter des registres dans l'architecture qui pourront être redistribués par la resynchronisation. Les principes du pipeline reposent sur deux définitions que l'on retrouve dans [SHA98].

1. Une coupe dans une architecture correspond en une série de raccords qui, une fois séparées, donnent deux structures distinctes.

2. Une coupe unidirectionnelle est caractérisée par des entrées appartenant à une même coupe et des sorties appartenant à une coupe distincte.

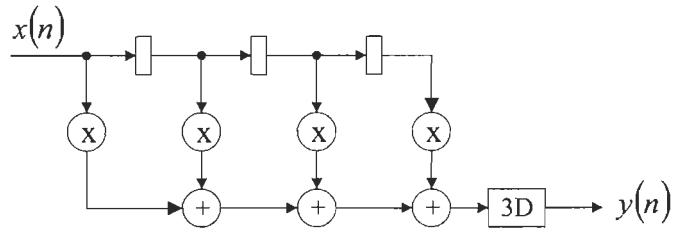

La technique consiste à introduire  $M$  registres dans chaque élément entrant d'une même coupe. Nous verrons ici un exemple de pipeline pour mieux comprendre la méthode. Pour la démonstration, on suppose un temps d'addition  $\tau_{add}$  de 10 et un temps de multiplication  $\tau_{mult}$  de 20. Considérons l'architecture *FIR* de la Figure 3.4.

**Figure 3.4: Structure FIR avant pipeline**

Dans cette figure, les traits pointillés dénotent les coupes que l'on peut effectuer sur l'architecture selon les 2 définitions précédentes. Si l'on introduit un registre dans chaque coupe verticale, on obtient l'architecture de la Figure 3.5.

**Figure 3.5: Structure FIR pipelinée #1**

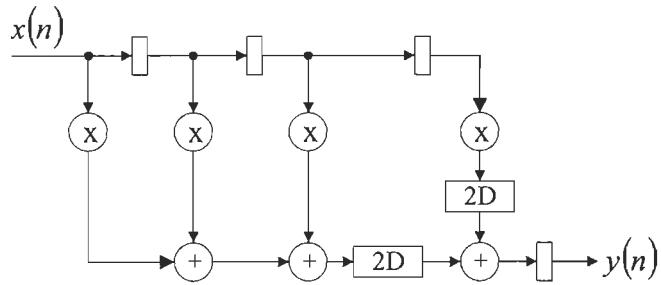

Dans cette architecture, on remarque que le temps critique est de 30 comparativement à 40 pour l'architecture originale. Il y a donc un gain en vitesse intéressant. Si on applique le pipeline sur la coupe horizontale, on obtient l'architecture de la Figure 3.6.

**Figure 3.6: Structure FIR pipelinée #2**

Dans ce cas, le chemin critique est de 20 ce qui représente la moitié du chemin critique original. On voit alors que l'application du pipeline s'avère très efficace. Par contre, l'ajout des registres implique une augmentation de la surface utilisée. Cette contrainte peut devenir importante lorsque l'ordre du filtre est très élevé.

L'ajout des registres ne se limite pas à un seul par branche. En effet, on peut ajouter  $M$  registres qui pourront être redistribués par la resynchronisation sans aucun problème. Les désavantages se situent au niveau de la surface utilisée et de la latence qui sera augmentée en fonction de  $M$ . Cette latence est souvent bien acceptée étant donné l'apport du pipeline sur la vitesse de l'architecture.

Dans le cas où l'algorithme est du type récursif, la technique classique de pipeline ne s'applique plus car la définition 2 n'est plus respectée. Si on désire pipeliner un algorithme récursif, il faut avoir recours à une technique différente que nous présentons à la section 3.3.

### 3.3 Technique de l'anticipation

La boucle de retour dans l'algorithme récursif limite souvent la profondeur de pipeline que l'on peut y appliquer. Par exemple, si la sortie  $r(n)$  nécessite la sortie précédente  $r(n-1)$ , il sera impossible de pipeliner l'architecture. Pour pipeliner, on doit développer la série des équations de l'algorithme sur une longueur  $M$ .

#### 3.3.1 Principe

La technique de l'anticipation permet d'utiliser la sortie  $r(n-M)$  au lieu de la sortie  $r(n-1)$  (où  $M$  est entier positif) pour le calcul de  $r(n)$  ce qui permet de pipeliner l'architecture à une profondeur  $M$ . Le choix de  $M$  dépend de la profondeur de pipeline désirée. Il est important de tenir compte de l'implantation matérielle car un  $M$  trop grand peut résulter en une surface d'utilisation très grande.

Voyons maintenant les détails de la méthode. Soit l'éq. (3.5) qui représente une équation récursive de premier ordre.

$$x(n) = ax(n-1) + u(n) \quad (3.5)$$

Dans l'éq. (3.5),  $x(n)$  représente la sortie du système et  $u(n)$  représente l'entrée du système. On remarque la nature récursive car la valeur actuelle de  $x(n)$  nécessite la valeur précédente  $x(n-1)$  que l'on multiplie par un coefficient  $a$ . La borne inférieure du chemin critique est donnée par le délai d'une addition et d'une multiplication. Si on utilise les

valeurs de l'exemple précédent, le chemin critique serait de 30. Pour franchir cette limite inférieure, on doit appliquer le pipeline sur l'éq (3.5).

Pour pipeliner l'algorithme, il est nécessaire de développer les calculs de l'équation soit:

$$\begin{aligned}

x(n) &= ax(n-1) + u(n) \\

x(n-1) &= ax(n-2) + u(n-1) \\

x(n) &= a[x(n-2) + u(n-1)] + u(n) \\

x(n) &= a^2 x(n-2) + au(n-1) + u(n)

\end{aligned} \tag{3.6}$$

Si on développe l'éq. (3.6) sur une longueur  $M$ , on obtient le résultat de l'éq. (3.7).

$$x(n) = a^M x(n-M) + \sum_{i=0}^{M-1} a^i u(n-i) \tag{3.7}$$

L'éq. (3.7) est très importante car elle représente la technique de base pour la majorité des transformations d'algorithmes récursifs. On remarque que la technique introduit  $M$  registres dans la boucle de récursivité ce qui permet de pipeliner l'opération de multiplication et d'addition au niveau désiré. La borne inférieure du chemin critique est alors franchie. Si la redistribution des registres est appliquée de façon uniforme sur l'addition et la multiplication, on obtient un gain en vitesse de  $M$  fois la vitesse originale [SHA98].

On remarque aussi que l'algorithme préserve la structure des données d'entrée et de sortie. C'est à dire que les performances de l'algorithme au niveau de l'erreur de reconstitution ne seront pas modifiées. Par contre, cette conservation de la performance se fait au détriment de la surface d'intégration. En effet, le calcul de l'anticipation (sommation

dans l'éq. (3.7)) est fonction de  $M*N$  ( $N$  représente l'ordre du filtre) ce qui ajoute beaucoup d'éléments lorsque  $M$  et  $N$  sont élevés. Une autre observation importante concerne la nature non récursive de la boucle d'anticipation. Cette propriété permet d'appliquer la technique de pipeline classique afin d'augmenter son débit. On retrouve l'application de la technique de l'anticipation dans [HAT92] où un filtre à réponse impulsionnelle infinie (*IIR - Infinite Impulse Response*) fonctionnant à 85 MHz a été réalisé en technologie *VLSI*.

### 3.3.2 Anticipation dispersée et regroupée

Dans le cas où la récursivité de l'algorithme est d'ordre supérieur à 1, on a recours à deux types de transformation: l'anticipation dispersée (*Scattered*), ou l'anticipation regroupée (*Clustered*). On retrouve ce genre d'algorithmes dans les filtres numériques *IIR*. Le calcul sériel de ce genre de filtre est donné par l'éq. (3.8).

$$x(n) = f_{\text{serial}}(x(n-1), x(n-2), \dots, x(n-N), u(n), u(n-1), \dots, u(n-P)) \quad (3.8)$$

Dans cette équation,  $x(n)$  représente la sortie du filtre,  $u(n)$  représente l'entrée du filtre,  $N$  représente l'ordre du filtre et  $f_{\text{serial}}(\bullet)$  représente une fonction linéaire. L'état présent d'un tel filtre est donc fonction des états passés et des valeurs présentes et passées de l'entrée. L'application de l'anticipation regroupée sur ce type d'équation pour obtenir un pipeline d'ordre  $M$  est donnée par (3.9).

$$x(n) = f_{c, \text{pipe}} \left( \begin{matrix} x(n-M), x(n-M-1), \dots, x(n-M-N+1), \\ u(n), u(n-1), \dots, u(n-M+1) \end{matrix} \right) \quad (3.9)$$

Le calcul de  $x(n)$  se fait en fonction d'un groupe de  $N$  états qui sont  $M$  échantillons dans le passé. Les détails de la fonction  $f_{c,pipe}(\bullet)$  sont donnés dans [PAR89]. L'ajout matériel d'un tel type de transformation est proportionnel à  $M$ . L'anticipation dispersée est pour sa part définie par (3.10).

$$x(n) = f_{s,pipe}(x(n-M), x(n-2M), \dots, x(n-MN), u(n), u(n-1), \dots, u(n-NM-2)) \quad (3.10)$$

Les détails de la fonction linéaire  $f_{s,pipe}(\bullet)$  sont donnés dans [PAR89]. L'ajout matériel de (3.10) est fonction de  $NM$  et peut être réduit à  $N \log_2(M)$  par décomposition [PAR89]. L'anticipation dispersée donne une architecture plus gourmande en surface que l'architecture obtenue par l'anticipation regroupée. Par contre, l'anticipation dispersée possède l'avantage de préserver la stabilité ce que l'anticipation regroupée ne peut garantir [PAR89].

### 3.4 Transformation de la technique de l'anticipation

#### 3.4.1 Justification de la transformation

Comme nous venons de le voir, les différentes techniques d'anticipation permettent d'atteindre de forts débits de calcul mais il en résulte des architectures qui utilisent beaucoup de surface lorsque le niveau de pipeline  $M$  et l'ordre  $N$  du filtre sont élevés. Il est donc intéressant de développer des techniques qui minimisent cet ajout de matériel. Le principe est de transformer la technique de l'anticipation dans le but de conserver de bonnes propriétés algorithmiques et limiter l'ajout matériel. Cette transformation donne lieu à des

techniques d'approximations plutôt que des techniques de transformations car elles ne conservent pas l'exactitude de l'algorithme original. Une technique très intéressante est l'anticipation relaxée que nous présentons dans la sous-section 3.4.2.

### 3.4.2 Anticipation relaxée

La technique de l'anticipation relaxée permet d'atteindre de forts débits de calculs sans toutefois augmenter de façon dramatique la surface d'intégration. La technique s'applique essentiellement en deux phases:

1. Application d'une technique d'anticipation vue à la section 3.3 .

2. Tronquer la fonctionnalité de certains blocs de l'algorithme pipeliné de telle sorte que l'impact sur le comportement de la convergence soit minimal.

Alors que la phase 1 permet de créer une architecture unique, la phase 2 permet d'appliquer une vaste étendue d'approximations ce qui permet de créer une multitude d'architectures distinctes. Par contre, puisque l'étape 2 altère les caractéristiques de l'algorithme, il est important d'effectuer une analyse de stabilité sur l'architecture choisie. Pour expliquer le principe de l'anticipation relaxée, appliquons la technique sur une équation récursive du premier ordre qui varie dans le temps. Soit l'équation (3.11).

$$x(n+1) = a(n)x(n) + b(n)u(n) \quad (3.11)$$

Selon l'étape 1, on applique la technique de l'anticipation ce qui donne (3.12)

$$x(n+M) = \left[ \prod_{i=0}^{M-1} a(n+i) \right] x(n) + \sum_{i=0}^{M-1} \left\{ \left[ \prod_{j=1}^i a(n-M-j) \right] \cdot b(n+M-1-i) u(n+M-1-i) \right\} \quad (3.12)$$

On remarque ici que la complexité de (3.12) est beaucoup plus importante que dans (3.11). Cette complexité est causée par la préservation de l'exactitude de l'algorithme sériel. On peut alors modifier ou relaxer l'équation (3.12) par différentes techniques au dépend d'une légère dégradation du comportement de la convergence. Les trois principaux types de relaxations sont: la relaxation de somme, la relaxation du produit et la relaxation du délai [SHA98].

Pour appliquer la relaxation, il est nécessaire de connaître le comportement des variables du système. La qualité des relaxations dépend de la qualité des hypothèses. Par exemple, si on considère que la valeur de  $a(n)$  est voisine de 1 et que le produit  $b(n)u(n)$  varie lentement sur une séquence de  $M$  termes, on peut relaxer le terme de sommation de (3.12) pour obtenir (3.13).

$$x(n+M) = \left[ \prod_{i=0}^{M-1} a(n+i) \right] x(n) + Mb(n+M-1)u(n+M-1) \quad (3.13)$$

Le résultat obtenu en (3.13) est appelé la relaxation de somme. Si la valeur de  $a(n)$  est voisine de 1 et qu'elle varie lentement sur  $M$  cycles, on peut appliquer la relaxation du produit sur le premier terme de (3.12), ce qui donne (3.14).

$$x(n+M) = [1 - M(1 - a(n+M-1))]x(n) + Mb(n+M-1)u(n+M-1) \quad (3.14)$$

Enfin, si on considère que le produit  $b(n)u(n)$  varie lentement sur  $M$  échantillons, on peut appliquer la relaxation du délai ce qui donne (3.15).

$$x(n+M) = [1 - M(1 - a(n+M-1))]x(n) + Mb(n+M-D_1)u(n+M-D_1) \quad (3.15)$$

On voit ici que la relaxation peut prendre différentes formes que l'on applique séparément ou en conjonction. Même si la technique de l'anticipation relaxée donne de très bons compromis sur l'implantation des algorithmes récursifs, nous retrouvons d'autres techniques que nous présentons à la section 3.4.3.

### 3.4.3 Autres méthodes

On retrouve dans la littérature quelques méthodes de transformation de la technique de l'anticipation qui sont différentes de l'anticipation relaxée. Il est bon de noter que ces techniques sont très souvent des dérivées ou des cas particuliers de la technique de l'anticipation relaxée.

La première technique souvent rencontrée s'appelle *Delayed LMS algorithm* (DLMS) [LON89]. Cette technique s'applique à l'algorithme LMS et elle représente un cas particulier de l'anticipation relaxée. L'application de la technique sur (2.7) et (2.8) donne le résultat des équations (3.16) et (3.17).

$$e(n - D) = s(n - d - D) - \hat{x}(n - D) \quad (3.16)$$

$$\mathbf{w}(n + 1) = \mathbf{w}(n) + \mu \tilde{\mathbf{y}}(n - D) e(n - D) \quad (3.17)$$

On voit ici qu'il s'agit d'une relaxation du délai et de la somme suite à l'application de l'anticipation sur les équations originales. Le grand désavantage du *DLMS* est sa lenteur de convergence. Pour améliorer la vitesse de convergence, [MAT99] présente une transformation de l'algorithme *DLMS* qui s'avère efficace. L'architecture utilise par contre une grande surface ce qui limite son champ d'application.

On présente aussi un autre type d'anticipation dans [SHA99]. La technique développée est nommée l'anticipation distribuée. Son principe repose sur l'utilisation des échantillons passés distribués de façon non uniforme. Il est alors possible de préserver la stabilité sans augmenter la surface d'utilisation. Cette technique s'applique surtout sur des algorithmes d'ordre supérieur à 1.

### 3.5 Application à l'égalisation adaptative des canaux

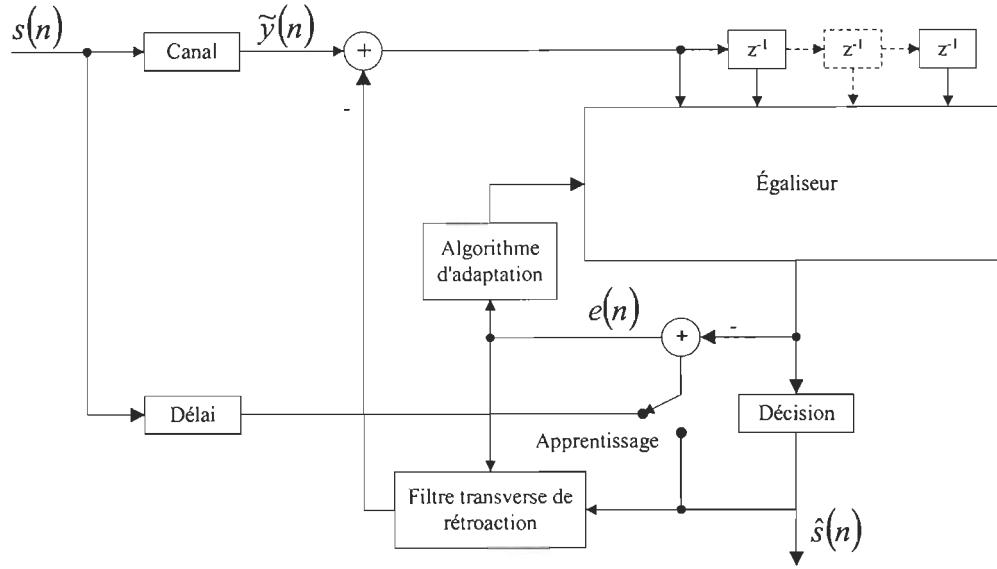

L'application de la technique de l'anticipation relaxée se prête bien à la problématique d'égalisation des canaux. En effet, pour que la réalisation matérielle soit intéressante, l'architecture ne doit pas utiliser trop de surface et fonctionner à des débits les plus élevés possible. Quelques applications reliées à l'égalisation des canaux utilisant la technique de l'anticipation relaxée ont été publiées. On retrouve d'ailleurs dans [SHA95] le cas de

réalisation d'un égaliseur *DFE* adapté par l'algorithme *LMS*. L'architecture pipelinée fonctionne à une vitesse 48 fois supérieure à celle de l'architecture serielle.

Nous allons maintenant montrer une application de la méthode de l'anticipation relaxée sur l'architecture d'un filtre transverse linéaire adapté par l'algorithme *LMS*. Le schéma de la Figure 2.15 montre le contexte d'utilisation. Les équations du *LMS* sériel sont données par les équations (3.18) et (3.19)

$$e(n) = s(n-d) - \mathbf{w}^T \tilde{\mathbf{y}}(n) \quad (3.18)$$

$$\mathbf{w}(n) = \mathbf{w}(n-1) + \mu \tilde{\mathbf{y}}(n) e(n) \quad (3.19)$$

La sortie du canal  $\tilde{\mathbf{y}}(n)$  est définie par (3.20) ( $N$  représente le nombre d'entrées de l'égaliseur)

$$\tilde{\mathbf{y}}(n) = [\tilde{y}(n) \ \tilde{y}(n-1) \ \tilde{y}(n-2) \dots \tilde{y}(n-N+1)]^T \quad (3.20)$$

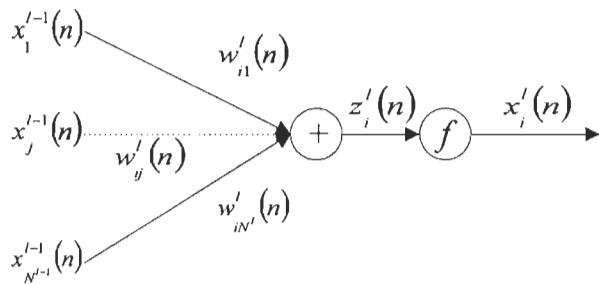

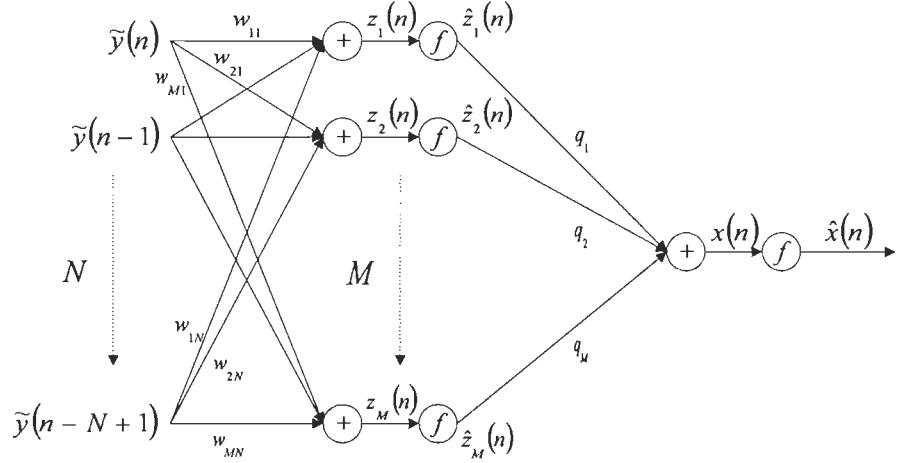

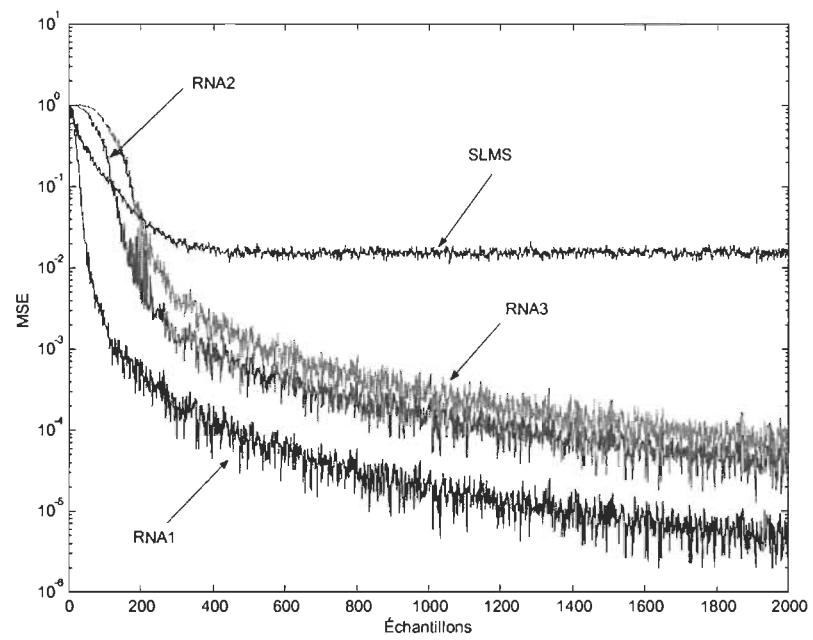

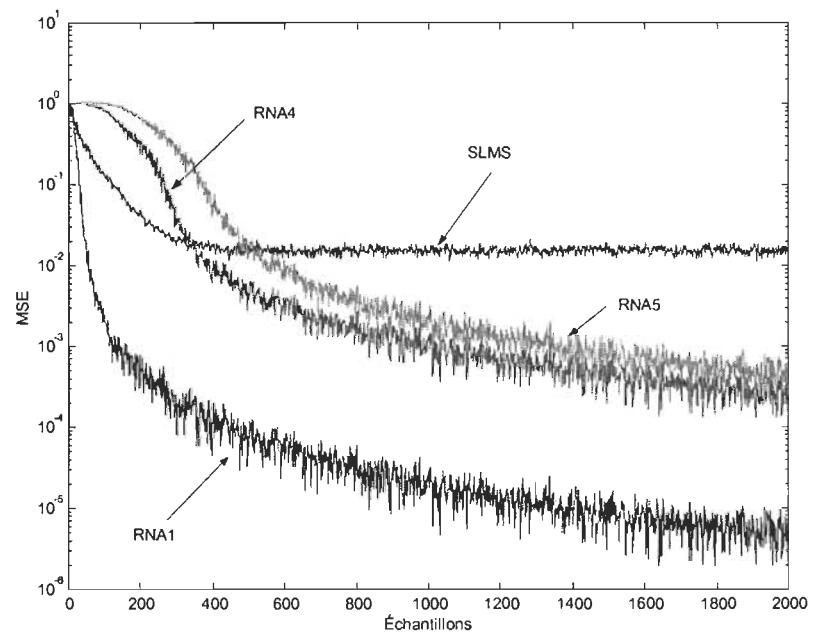

L'architecture de l'algorithme est donnée à la Figure 3.7. Dans cette architecture le chemin critique est donné par .(3.21)