UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

MÉMOIRE PRÉSENTÉ À

L'UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

COMME EXIGENCE PARTIELLE

DE LA MAÎTRISE EN GÉNIE ÉLECTRIQUE

PAR

MOURAD ZAKHAMA

IMPLANTATION EN TECHNOLOGIE ITGE (VLSI) D'UN

FILTRE ADAPTATIF BASÉ SUR LA LOGIQUE FLOUE POUR

L'ÉGALISATION DE CANAUX NON LINÉAIRES

AVRIL 2000

Université du Québec à Trois-Rivières

Service de la bibliothèque

Avertissement

L'auteur de ce mémoire ou de cette thèse a autorisé l'Université du Québec à Trois-Rivières à diffuser, à des fins non lucratives, une copie de son mémoire ou de sa thèse.

Cette diffusion n'entraîne pas une renonciation de la part de l'auteur à ses droits de propriété intellectuelle, incluant le droit d'auteur, sur ce mémoire ou cette thèse. Notamment, la reproduction ou la publication de la totalité ou d'une partie importante de ce mémoire ou de cette thèse requiert son autorisation.

## Résumé

*Ce travail vise principalement à apporter une contribution pour l'amélioration des systèmes de télécommunication, et plus particulièrement la résolution du problème d'égalisation de canaux. Lors d'une communication numérique, le signal transmis à travers le canal subit une suite de déformation de caractère linéaire et non-linéaire dépendant des caractéristiques du canal. Généralement ces dernières sont inconnues et variables dans le temps. Les déformations introduites sont corrigées au niveau du récepteur par une technique appelée égalisation de canaux. L'égaliseur estime à priori les caractéristiques du canal par la réception d'un paquet de données connues transmises par l'émetteur.*

*Le but de ce mémoire est l'étude d'une nouvelle méthode d'égalisation de canaux; utilisant la technique de la logique floue, ainsi que de présenter une architecture hautement parallèle à haut débit pour les canaux linéaires ou non-linéaires, variables et invariables dans le temps.*

*Se référant aux travaux de Wang & Mendel'93 on a pu faire les simulations sur Matlab de l'égaliseur. Notre tâche était d'adapter l'algorithme afin de le préparer pour une implantation en technologie d'intégration à très grande échelle (ITGE – VLSI). La complexité de calcul importante de cet égaliseur rendait difficile son intégration sur*

*silicium. Ainsi, une étude approfondie de la structure de l'algorithme à intégrer nous a permis d'introduire des simplifications au niveau du filtre et de son adaptation. De plus, grâce à la forme récurrente des équations utilisées, cela nous a permis d'arriver à une architecture systolique pour un égaliseur non-linéaire. D'une première proposition d'architecture, nous avons appliqué des simplifications améliorant de façon significative la surface d'intégration et la vitesse de calcul. L'architecture ainsi dérivée se compose seulement de quatre (4) processeurs élémentaires (PE) et ce peu importe le nombre de fonctions d'appartenance pourvu qu'il soit possible d'utiliser un seul retard sur le signal reçu pour égaliser.*

*Les résultats des performances de l'architecture systolique proposée ont été évalués d'une part pour une technologie CMOS de  $0.5 \mu\text{m}$  de HP obtenue de la société canadienne de micro-électronique (SCM - CMC) et d'autre part sur une structure logique reconfigurable (FPGA-Field Programmable Gates Array) XC4036EX de la compagnie Xilinx. L'évaluation des performances obtenues après synthèse à l'aide des outils de Synopsys, nous a permis d'atteindre une fréquence d'horloge de 40 MHz et 15 MHz pour les technologies CMOS  $0,5 \mu\text{m}$  et FPGA respectivement.*

*Enfin, nous avons aussi proposé comment ajouter l'algorithme d'adaptation de type LMS à l'architecture afin d'adapter les coefficients du filtre à logique floue.*

## *Remerciements*

*Je tiens à exprimer ma profonde gratitude et mes sincères remerciements à mon directeur de recherche, Daniel MASSICOTTE, pour m'avoir fait l'honneur de diriger mon travail de recherche. Je tiens aussi à le remercier pour la confiance et le soutien moral qu'il m'a accordé tout au long de mes études. Son jugement et ses critiques m'ont permis d'acquérir des qualités inestimables en recherche.*

*La seconde mention ira à mes parents qui m'ont permis de réaliser un rêve, celui de continuer mes études au Canada, et atteindre mes objectifs de carrière. Spécialement mon père, Mansour, qui m'a soutenu moralement et financièrement tout au long de mes études.*

*Je remercie aussi ma mère, Saïda qui n'a pas cessé de me prodiguer ces conseils et son soutien. Ma sincère reconnaissance va aussi à mes frères : Mehdi et Sami ainsi qu'à mes sœurs : Mouna et Marwa. Je témoigne aussi de la gratitude à tous mes oncles, tantes, cousins, et amis pour leur amour, support et compréhension.*

*Finalement, je tiens à remercier mes coéquipiers du Laboratoire de signaux et systèmes intégrés (LSSI) de l'Université du Québec à Trois-Rivières, ainsi que toute personne qui m'a aidé à réaliser ce mémoire.*

## *Liste des abréviations et symboles*

### *Symboles*

|                      |                                                           |

|----------------------|-----------------------------------------------------------|

| $e$                  | <i>Erreur de correction</i>                               |

| $s$                  | <i>Symbole transmis</i>                                   |

| $W$                  | <i>Coefficients à adapter</i>                             |

| $w$                  | <i>Poids de la couche cachée</i>                          |

| $\mu_{F_j^y}$        | <i>Degré d'appartenance à une fonction d'appartenance</i> |

| $p$                  | <i>Vecteur de sortie du bloc de fuzzification</i>         |

| $\theta$             | <i>Vecteur déterminant les règles d'inférence</i>         |

| $y$                  | <i>Sortie du canal</i>                                    |

| $\mu$                | <i>Pas d'apprentissage</i>                                |

| $\lambda$            | <i>Facteur d'oubli</i>                                    |

| $\eta$               | <i>Bruit additif du canal</i>                             |

| $\tilde{\bullet}$    | <i>Signal bruité</i>                                      |

| $\overline{\bullet}$ | <i>Signal déformé linéairement</i>                        |

| $\hat{\bullet}$      | <i>Estimé de</i>                                          |

### ***Abbreviations***

|             |                                                                           |

|-------------|---------------------------------------------------------------------------|

| <i>ASIC</i> | <i>Application Specific Integrated Circuit</i>                            |

| <i>BER</i>  | <i>Bit Error Rate</i>                                                     |

| <i>CLB</i>  | <i>Control Logic Blocs</i>                                                |

| <i>CSA</i>  | <i>Carry Save Adder</i>                                                   |

| <i>DFE</i>  | <i>Decision Feedback Equalizer</i>                                        |

| <i>DSP</i>  | <i>Digital Signal Processor</i>                                           |

| <i>FA</i>   | <i>Full Adder</i>                                                         |

| <i>FPGA</i> | <i>Field Programmable Gate Array</i>                                      |

| <i>IOB</i>  | <i>Input Output Blocs</i>                                                 |

| <i>ITGE</i> | <i>Intégration à très Grande Échelle</i>                                  |

| <i>LAN</i>  | <i>Local Area Network</i>                                                 |

| <i>LMS</i>  | <i>Least Mean Squares</i>                                                 |

| <i>PE</i>   | <i>Processeur Élémentaire</i>                                             |

| <i>RLS</i>  | <i>Recurcive Mean Squares</i>                                             |

| <i>VHDL</i> | <i>Very Large Scale Integration Circuit Hardware Description Language</i> |

# *Table des matières*

|                                                                 |             |

|-----------------------------------------------------------------|-------------|

| <i>Résumé</i>                                                   | <i>i</i>    |

| <i>Remerciements</i>                                            | <i>iii</i>  |

| <i>Liste des abréviations et symboles</i>                       | <i>iv</i>   |

| <i>Table des matières</i>                                       | <i>vi</i>   |

| <i>Table des figures</i>                                        | <i>x</i>    |

| <i>Liste des Tableaux</i>                                       | <i>xiii</i> |

| <i>Chapitre 1</i>                                               | <i>I</i>    |

| <i>Introduction</i>                                             | <i>I</i>    |

| 1.1    Problématique de recherche                               | <i>2</i>    |

| 1.2    Objectifs                                                | <i>5</i>    |

| 1.3    Méthodologie de recherche                                | <i>5</i>    |

| 1.4    Structure du rapport                                     | <i>6</i>    |

| <i>Chapitre 2</i>                                               | <i>9</i>    |

| <i>Algorithmes et architecture pour l'égalisation de canaux</i> | <i>9</i>    |

| 2.1    Canal de transmission                                    | <i>11</i>   |

|                                                   |                                                                  |           |

|---------------------------------------------------|------------------------------------------------------------------|-----------|

| 2.1.1                                             | Définition du canal                                              | 11        |

| 2.1.2                                             | Modélisation du canal                                            | 12        |

| <b>2.2</b>                                        | <b>Égalisation de canaux</b>                                     | <b>13</b> |

| 2.2.1                                             | Principe                                                         | 13        |

| 2.2.2                                             | Égalisation adaptative                                           | 14        |

| 2.2.3                                             | Égalisation autodidacte                                          | 16        |

| <b>2.3</b>                                        | <b>Algorithmes pour l'égalisation de canaux</b>                  | <b>16</b> |

| 2.3.1                                             | Algorithmes linéaires pour l'égalisation de canaux               | 16        |

| 2.3.2                                             | Algorithmes non-linéaires pour l'égalisation de canaux           | 18        |

| <b>2.4</b>                                        | <b>Architecture pour l'égalisation de canaux</b>                 | <b>20</b> |

| <b>2.5</b>                                        | <b>Justification d'une intégration en technologie ITGE</b>       | <b>20</b> |

| <b><i>Chapitre 3</i></b>                          |                                                                  | <b>22</b> |

| <b><i>Égaliseur basé sur la Logique floue</i></b> |                                                                  | <b>22</b> |

| <b>3.1</b>                                        | <b>Logique floue</b>                                             | <b>24</b> |

| 3.1.1                                             | Notions de base                                                  | 24        |

| 3.1.2                                             | Éléments d'un système à base de logique floue                    | 27        |

| 3.1.3                                             | Propriété de la logique floue                                    | 31        |

| 3.1.4                                             | Exemple d'application                                            | 32        |

| <b>3.2</b>                                        | <b>Application de la logique floue à l'égalisation de canaux</b> | <b>33</b> |

| 3.2.1                                             | Principe                                                         | 33        |

| 3.2.2                                             | Réalisation de l'égaliseur à base de logique floue               | 33        |

| <b>3.4</b>                                        | <b>Simulation dans l'environnement Matlab®</b>                   | <b>37</b> |

| 3.3.1                                             | Canaux utilisés                                                  | 38        |

|                                                |                                                           |           |

|------------------------------------------------|-----------------------------------------------------------|-----------|

| 3.3.2                                          | Influence du nombre de fonctions d'appartenances          | 38        |

| 3.3.3                                          | Comparaison de la logique floue avec LMS et RLS.          | 40        |

| 3.3.4                                          | Exemples de résultats de simulation                       | 42        |

| <b>3.5</b>                                     | <b>Égaliseur en vue d'une implantation ITGE</b>           | <b>44</b> |

| 3.5.1                                          | Contraintes d'implantation                                | 44        |

| 3.5.2                                          | Utilisation des fonctions canonique linéaire par morceaux | 45        |

| 3.5.3                                          | Simplification du calcul                                  | 47        |

| 3.5.4                                          | Utilisation de LMS pour l'adaptation                      | 48        |

| <b>4.6</b>                                     | <b>Conclusion</b>                                         | <b>50</b> |

| <b>Chapitre 4</b>                              |                                                           | <b>51</b> |

| <b><i>Implantation en technologie ITGE</i></b> |                                                           | <b>51</b> |

| <b>4.1</b>                                     | <b>Architecture Systolique</b>                            | <b>55</b> |

| 4.1.1                                          | Propriété des architectures systoliques                   | 55        |

| 4.1.2                                          | Différentes topologies de réseaux systoliques             | 57        |

| <b>4.2</b>                                     | <b>Étude de quantification</b>                            | <b>58</b> |

| 4.2.1                                          | Méthodes de quantification                                | 58        |

| 4.2.2                                          | Choix de la représentation à utiliser                     | 60        |

| 4.2.3                                          | Choix du nombre de bit                                    | 60        |

| <b>4.3</b>                                     | <b>Proposition d'une architecture systolique</b>          | <b>62</b> |

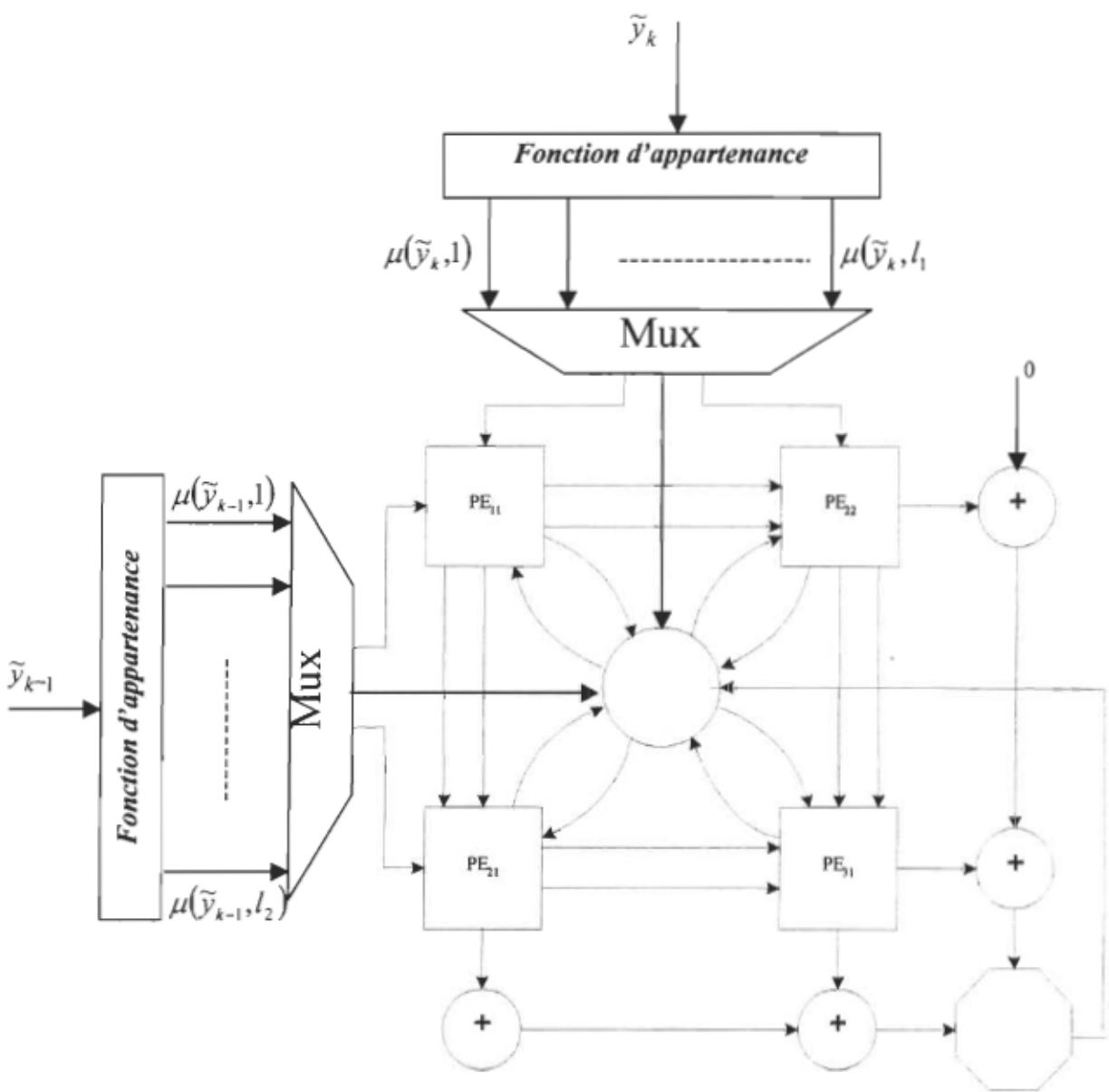

| 4.3.1                                          | Architecture Systolique                                   | 62        |

| 4.3.2                                          | Description des unités opératrices                        | 63        |

| 4.3.3                                          | Mode de fonctionnement du réseau systolique               | 66        |

| 4.3.4                                          | Simplification de l'architecture                          | 66        |

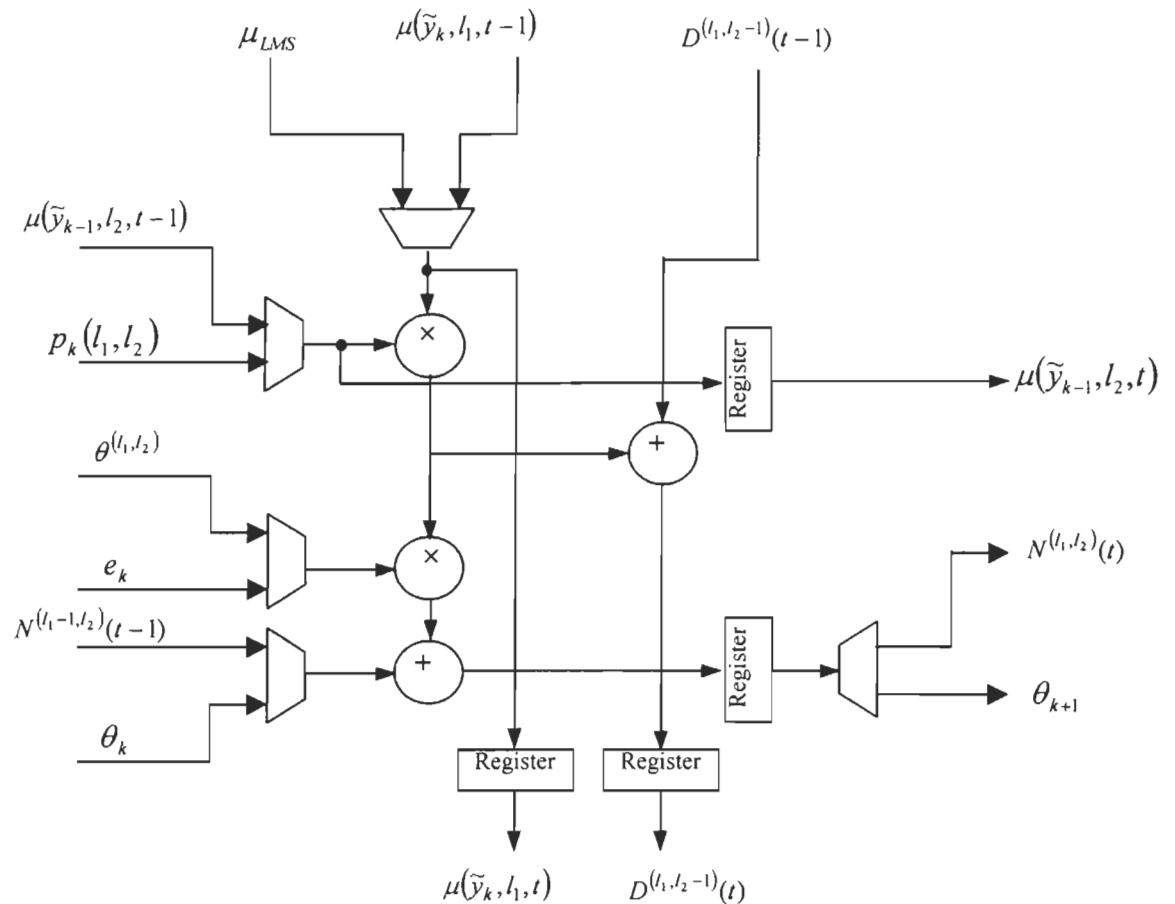

| 4.3.5                                          | Proposition de l'architecture adaptative                  | 70        |

|                                                                                   |                                       |           |

|-----------------------------------------------------------------------------------|---------------------------------------|-----------|

| <b>4.4</b>                                                                        | <b>Implantation de l'architecture</b> | <b>73</b> |

| 4.4.1                                                                             | Étape à suivre                        | 73        |

| 4.4.2                                                                             | Modélisation VHDL                     | 74        |

| 4.4.3                                                                             | Simulation fonctionnelle              | 74        |

| 4.4.4                                                                             | Synthèse en technologie CMOS          | 75        |

| 4.4.5                                                                             | Synthèse en technologie FPGA          | 76        |

| <b>4.5</b>                                                                        | <b>Conclusion</b>                     | <b>78</b> |

| <i>Chapitre 5</i>                                                                 |                                       | <b>80</b> |

| <i>Conclusion Générale</i>                                                        |                                       | <b>80</b> |

|  | <b>Bibliographie</b>                  | <b>83</b> |

| <i>ANNEXES</i>                                                                    |                                       | <b>88</b> |

# Table des figures

|                                                                                                     |    |

|-----------------------------------------------------------------------------------------------------|----|

| <i>Figure 1.1 : Principe d'une chaîne de transmission numérique</i>                                 | 4  |

| <i>Figure 1.2 : Structure du rapport</i>                                                            | 8  |

| <i>Figure 2.1 : schéma bloc d'un système de communication numérique</i>                             | 10 |

| <i>Figure 2.2 : Le canal de transmission[GLA96]</i>                                                 | 12 |

| <i>Figure 2.3 : Modélisation d'un canal de communication</i>                                        | 13 |

| <i>Figure 2.4 : Système d'égalisation de canaux adaptatif.</i>                                      | 15 |

| <i>Figure 2.5 : Schéma bloc d'un égaliseur aveugle[HAY96]</i>                                       | 16 |

| <i>Figure 2.6 : Filtre transverse [HAY96]</i>                                                       | 17 |

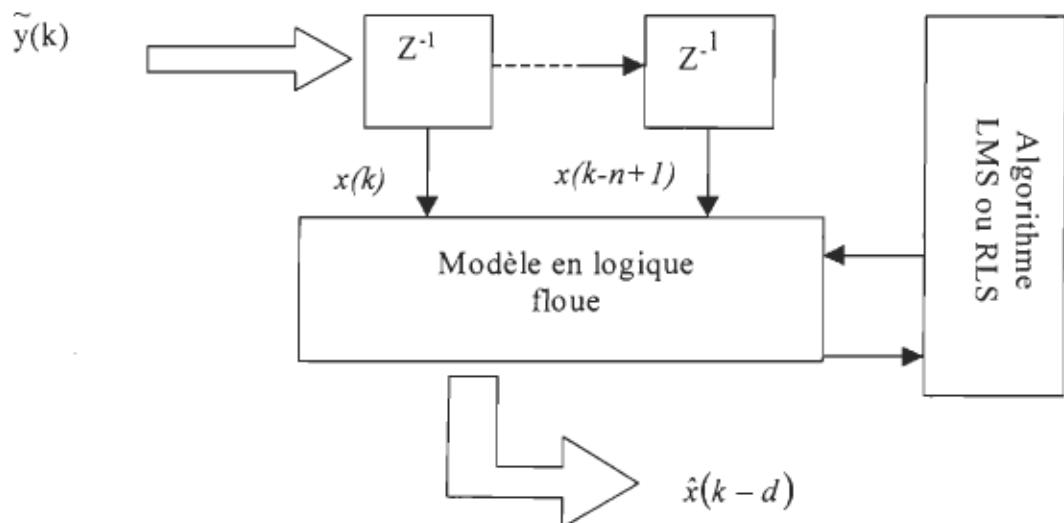

| <i>Figure 2.7 : Schéma simplifié de l'égaliseur à base de logique floue</i>                         | 19 |

| <i>Figure 3.1 : Analogie du raisonnement humain avec la logique floue</i>                           | 25 |

| <i>Figure 3.2 : Différents blocs d'un système à base de logique floue</i>                           | 27 |

| <i>Figure 3.3 : Fonction d'appartenance d'entrée au système</i>                                     | 28 |

| <i>Figure 3.4: Fuzzification – règles d'inférences – défuzzification</i>                            | 29 |

| <i>Figure 3.5 : logique classique et données imprécises</i>                                         | 32 |

| <i>Figure 3.6 : Logique floue et données imprécises</i>                                             | 32 |

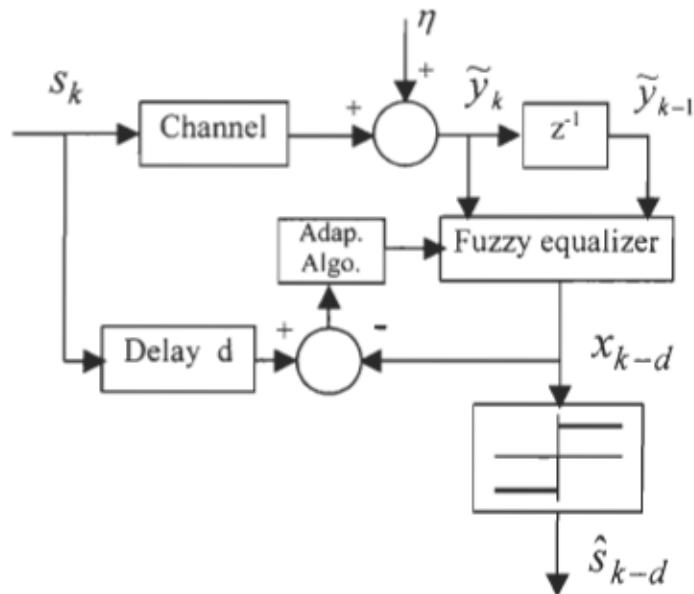

| <i>Figure 3.7 Égaliseur de canaux à base de logique floue</i>                                       | 37 |

| <i>Figure 3.8 : Influence du nombre de fonction d'appartenance (en utilisant un canal linéaire)</i> | 39 |

|                                                                                                                                                        |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| <i>Figure 3.9 : Influence du nombre de fonction d'appartenance (en utilisant un canal non-linéaire)</i>                                                | 40 |

| <i>Figure 3.10 : comparaison de la logique floue avec RLS et LMS pour un canal linéaire</i>                                                            | 41 |

| <i>Figure 3.11 : comparaison de la logique floue avec RLS et LMS pour un canal non-linéaire</i>                                                        | 41 |

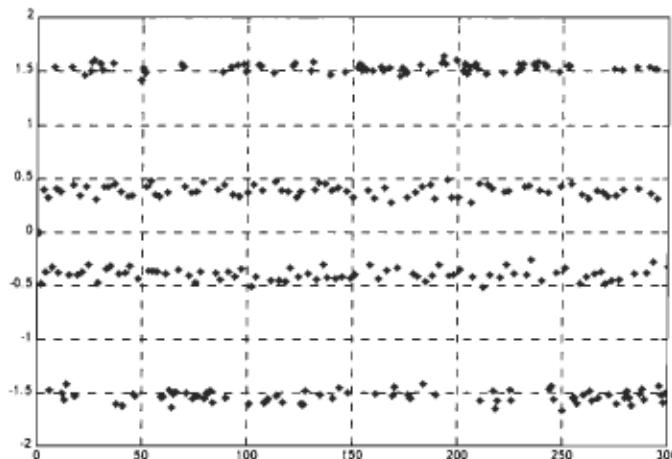

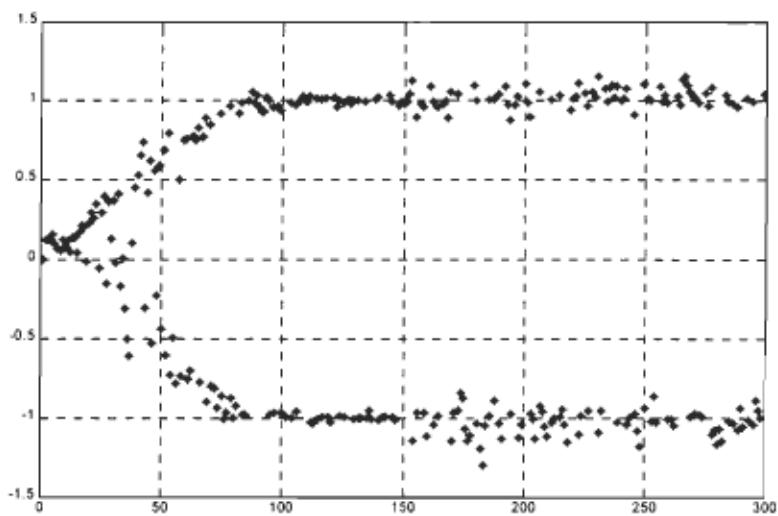

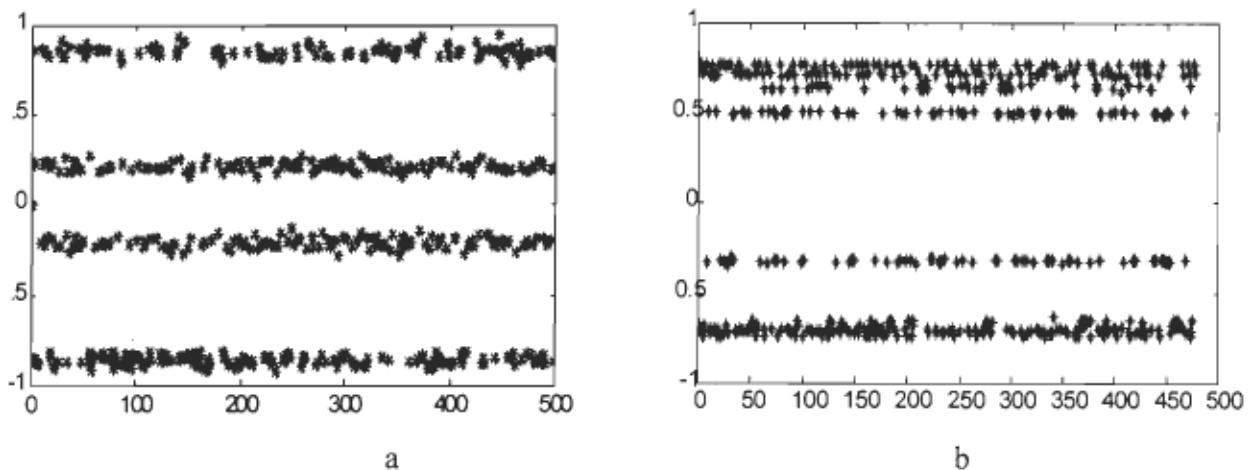

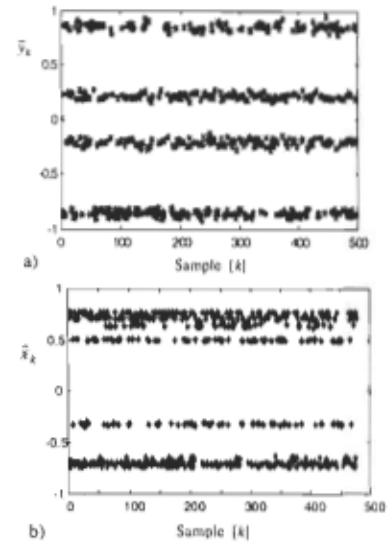

| <i>Figure 3.12 : signal de sortie du canal avec SNR=20dB ( BER=50%)</i>                                                                                | 42 |

| <i>Figure 3.13 : Signal reconstitué avec MF=7 (BER = 1%)</i>                                                                                           | 43 |

| <i>Figure 3.14 : Signal reconstitué avec MF=5 (BER =1.6%)</i>                                                                                          | 43 |

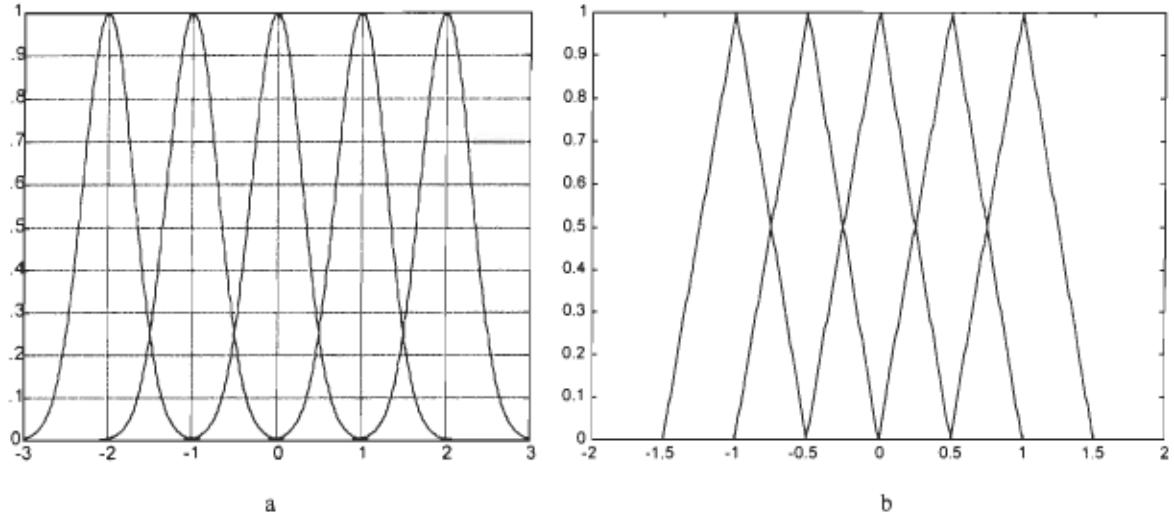

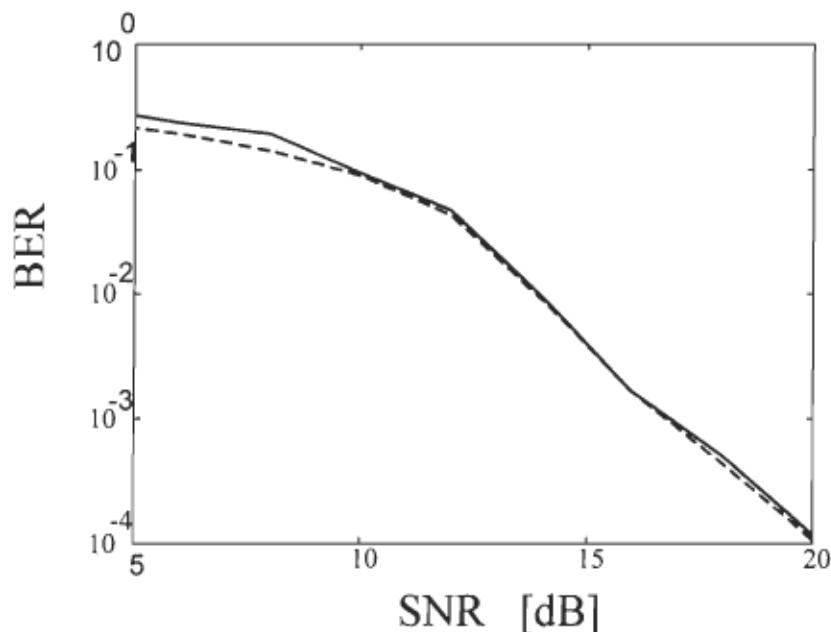

| <i>Figure 3.15 : Forme des fonctions d'appartenances a) gaussiennes b) canonique linéaire par morceau (CLM)</i>                                        | 45 |

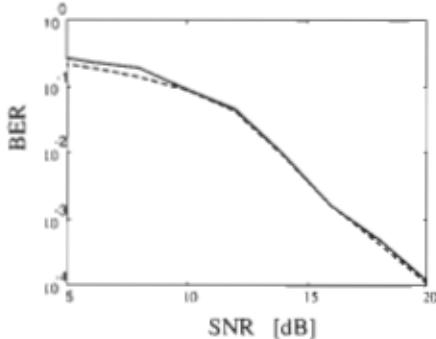

| <i>Figure 3.16 : Comparaison du BER pour l'égalisation d'un canal non-linéaire</i>                                                                     | 46 |

| <i>Ligne continue : Fonctions d'appartenance CLM; Ligne interrompue : Fonctions d'appartenance gaussienne; 1000 échantillons, moyenne de 15 essais</i> | 46 |

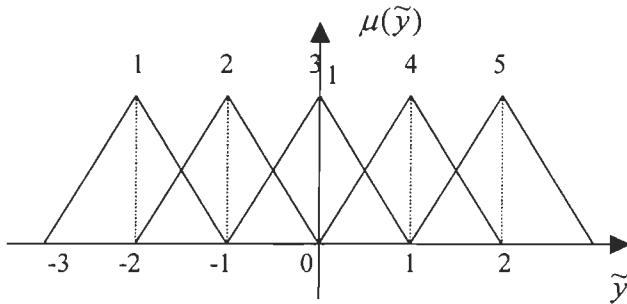

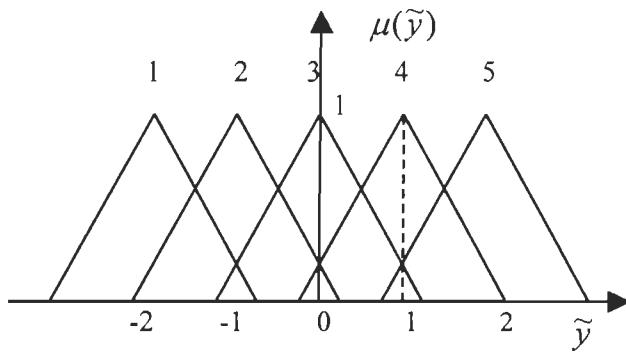

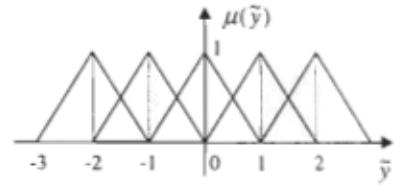

| <i>Figure 3.17 : Fonctions d'appartenance CLM avec dc=1</i>                                                                                            | 47 |

| <i>Figure 3.18 : Fonctions d'appartenance CLM avec dc=2</i>                                                                                            | 47 |

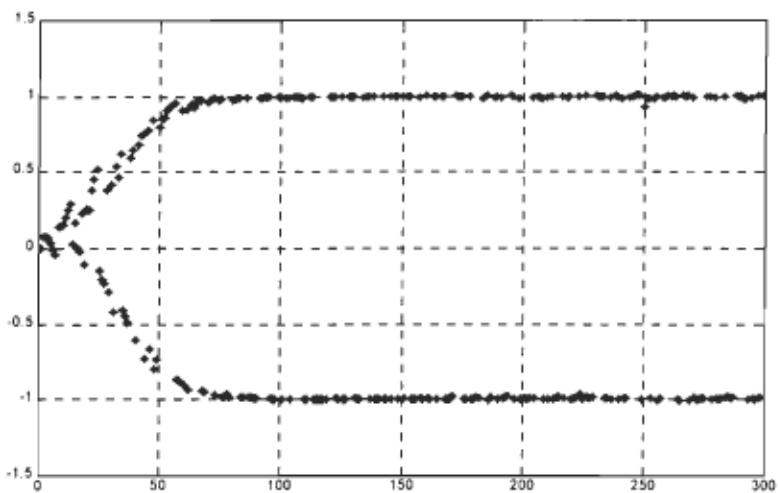

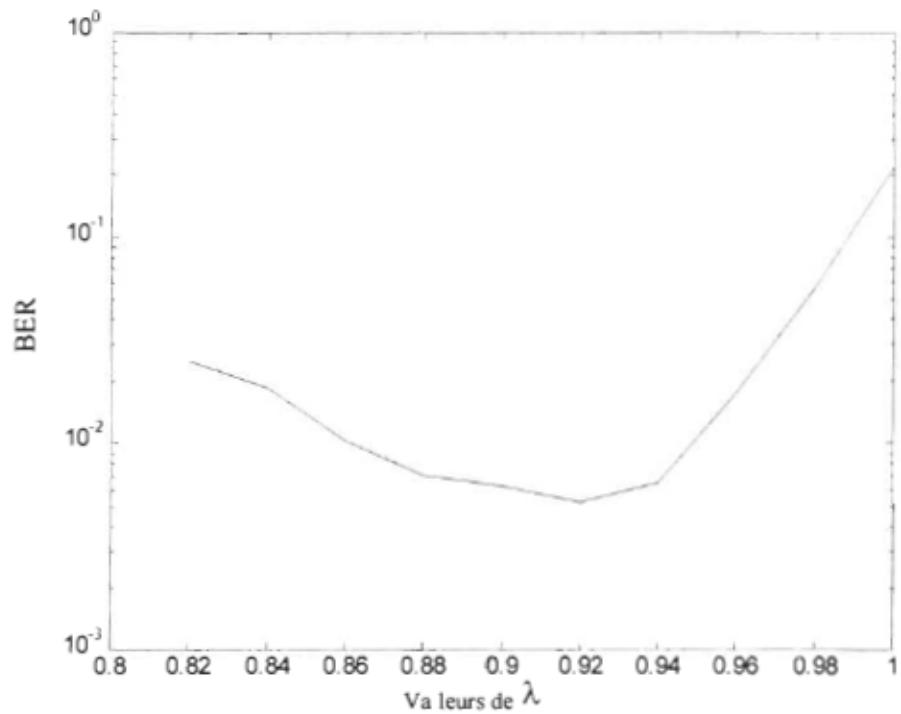

| <i>Figure 3.19 : Optimisation de <math>\lambda</math></i>                                                                                              | 49 |

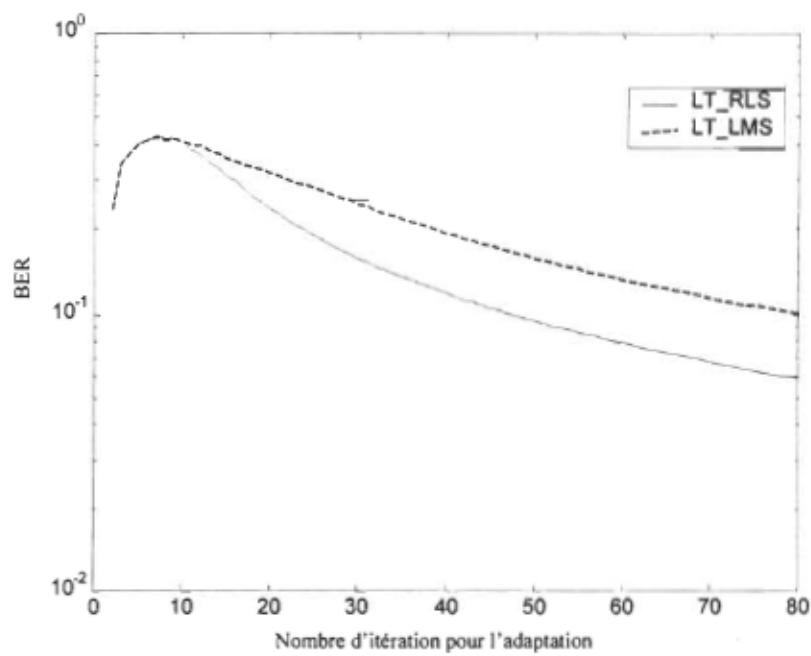

| <i>Figure 3.20 : Vitesse de convergence de RLS et LMS</i>                                                                                              | 49 |

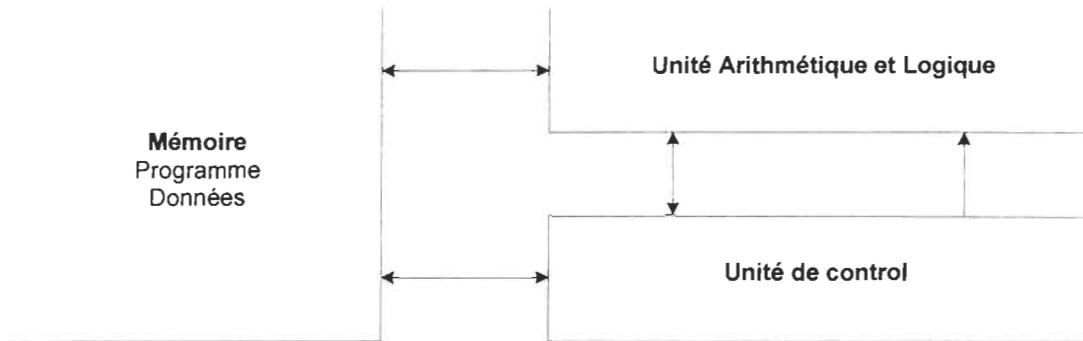

| <i>Figure 4. 1 : Le modèle séquentiel</i>                                                                                                              | 52 |

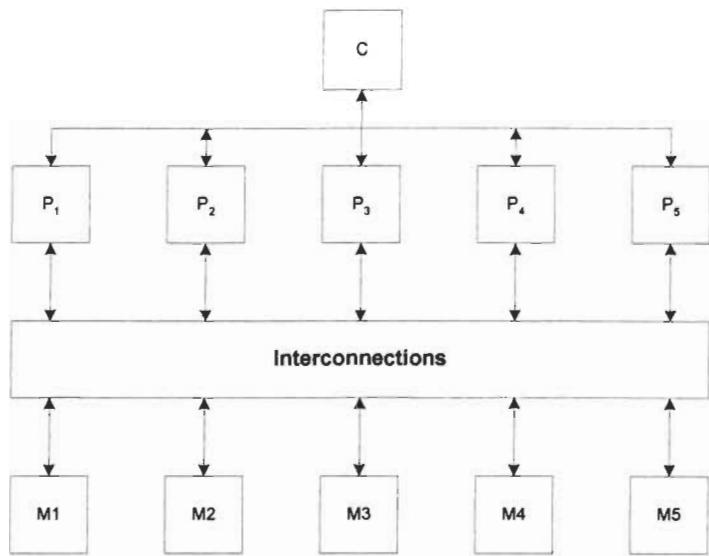

| <i>Figure 4. 2 : Architecture SIMD [COS93]</i>                                                                                                         | 53 |

| <i>Figure 4. 3 : Architecture MIMD [COS93]</i>                                                                                                         | 53 |

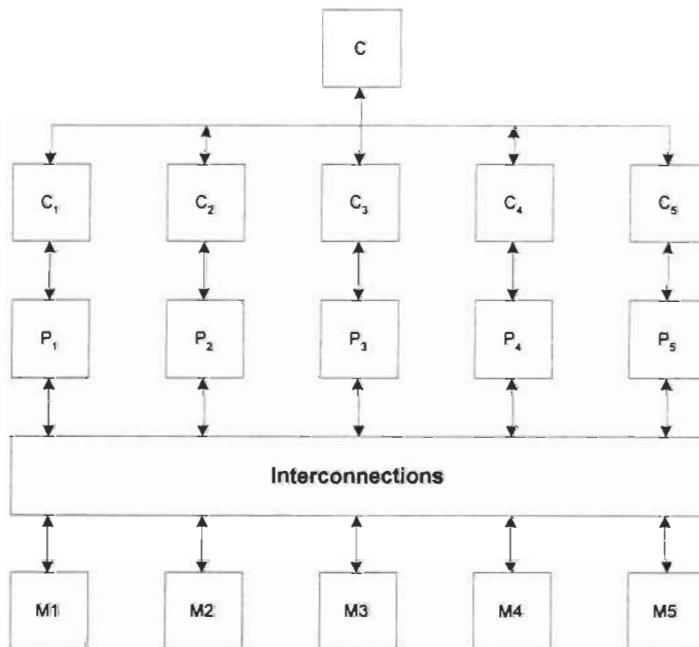

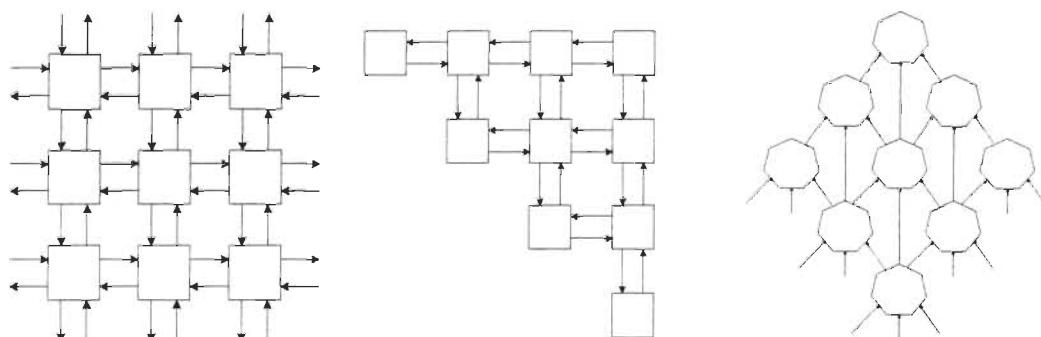

| <i>Figure 4.4 : Architectures Systoliques à topologie a) carré b) triangulaire</i>                                                                     | 54 |

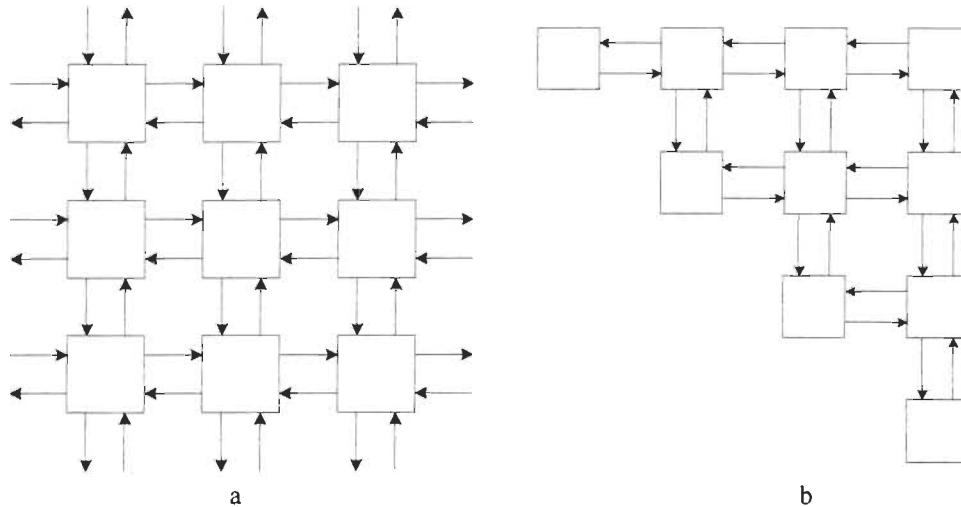

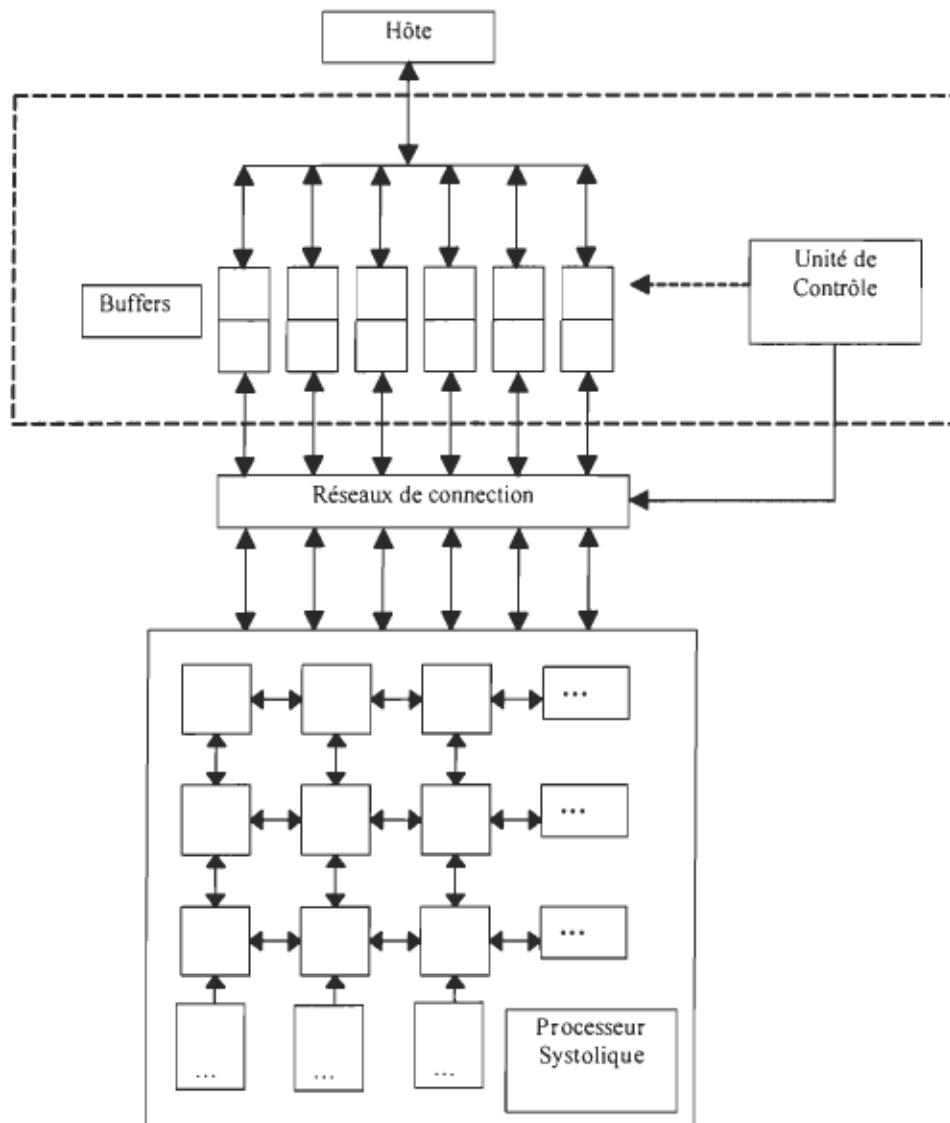

| <i>Figure 4.5 : Intégration d'un réseau systolique dans un Système [QUI89]</i>                                                                         | 56 |

|                                                                                                                                   |    |

|-----------------------------------------------------------------------------------------------------------------------------------|----|

| <i>Figure 4.6 : Réseau systolique carré, triangulaire et hexagonal</i>                                                            | 57 |

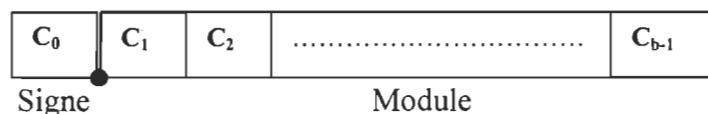

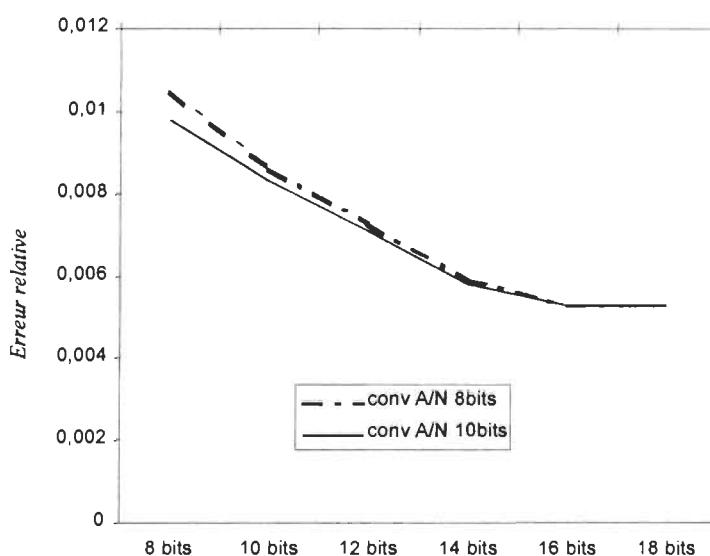

| <i>Figure 4.7a: Choix du nombre de bit du convertisseur A/N</i>                                                                   | 60 |

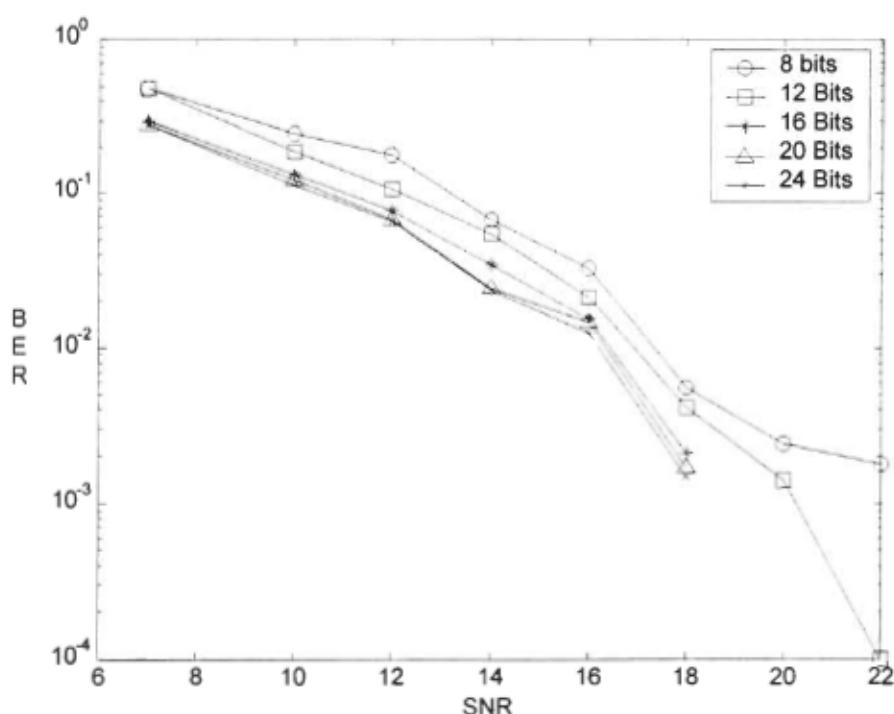

| <i>Figure 4.7b : Résultat de quantification (LF_LMS)</i>                                                                          | 61 |

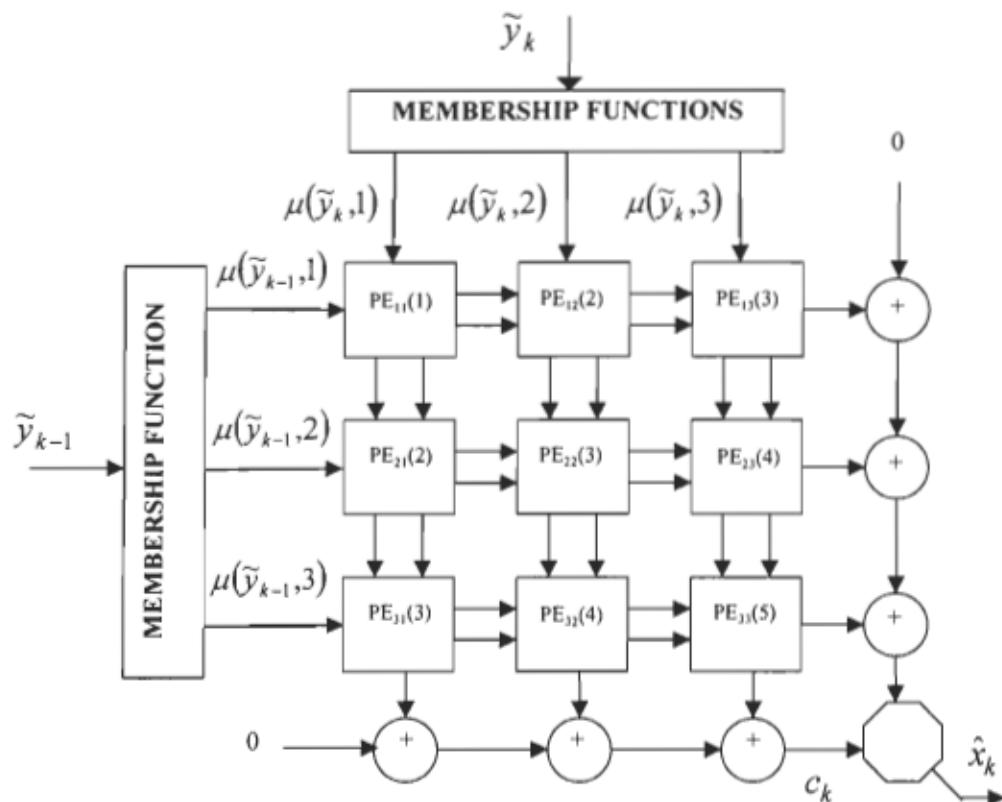

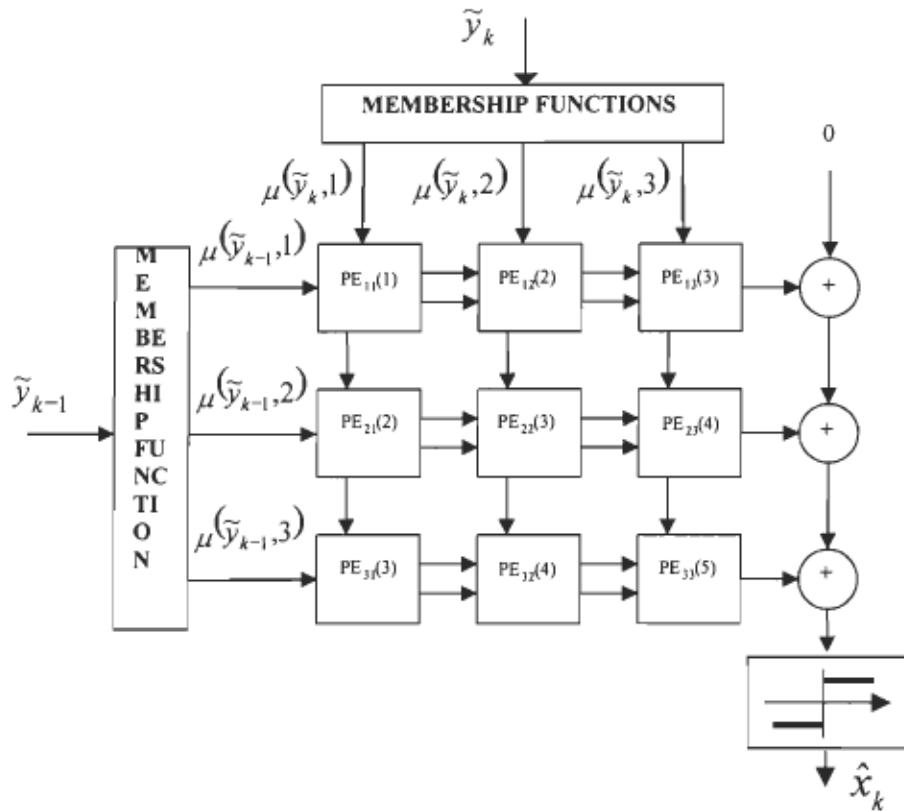

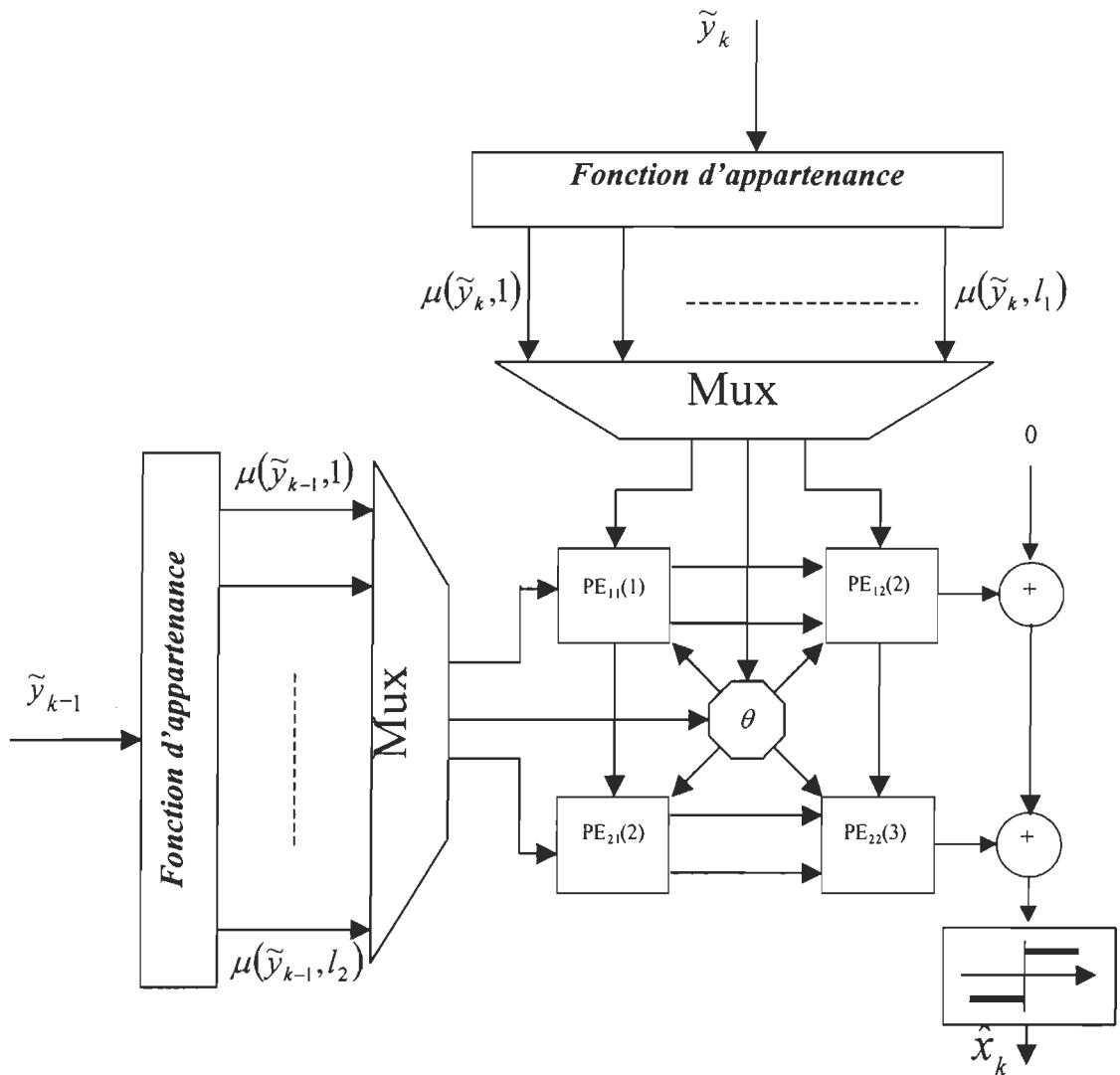

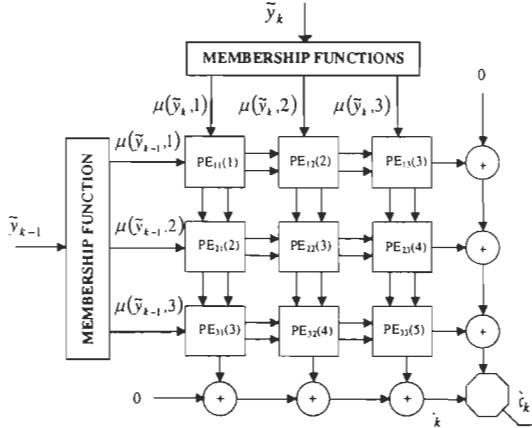

| <i>Figure 4.8 : Architecture systolique pour l'égaliseur à base de logique floue pour <math>m_j=3</math> (<math>j=1,2</math>)</i> | 63 |

| <i>Figure 4.9 : Différentes Cellules constituants le réseau systolique</i>                                                        | 63 |

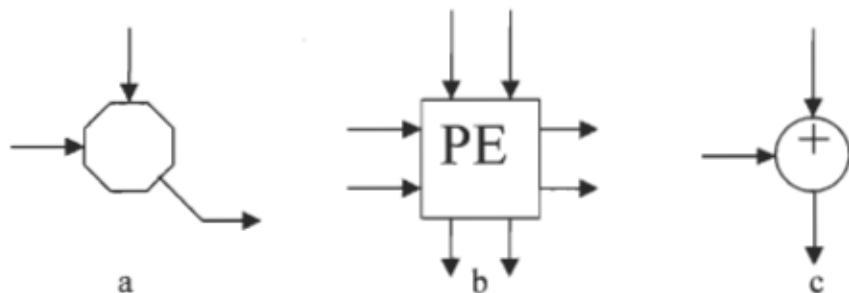

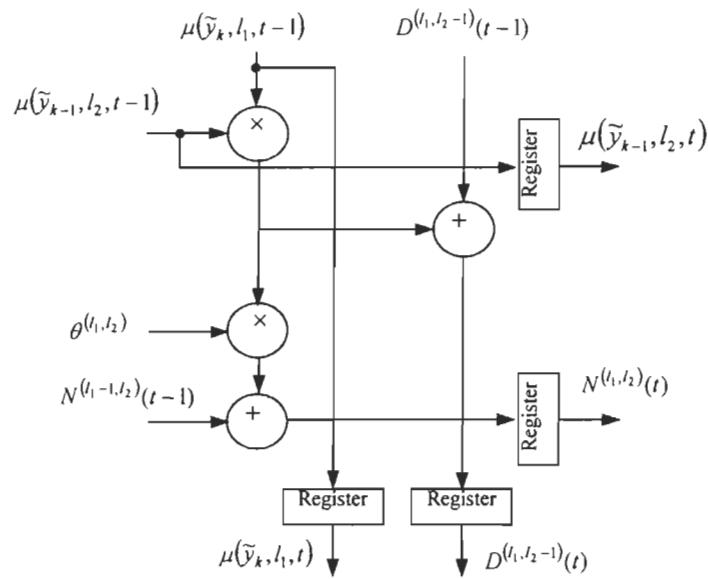

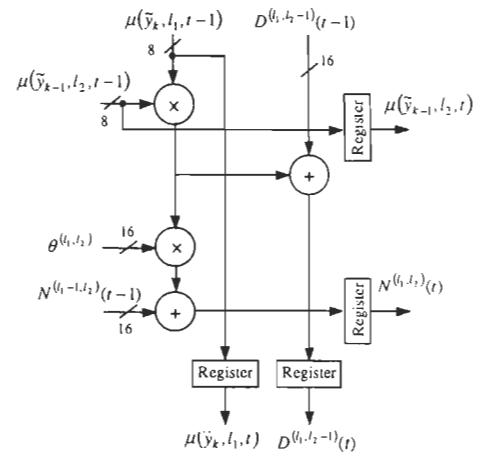

| <i>Figure 4.10 : Architecture interne de PE1</i>                                                                                  | 65 |

| <i>Figure 4.11 : Architecture de PE2</i>                                                                                          | 65 |

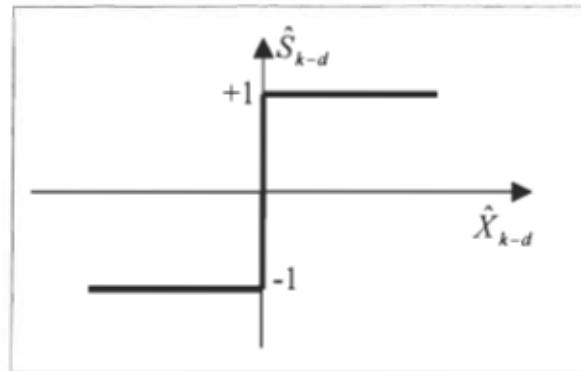

| <i>Figure 4.12 : Fonction de saturation</i>                                                                                       | 67 |

| <i>Figure 4.13 : Schéma blocue du système d'égalisation utilisant la fonction de saturation</i>                                   | 67 |

| <i>Figure 4.14 : Architecture simplifiée (utilisation de la fonction de saturation et omission du calcul du dénominateur)</i>     | 68 |

| <i>Figure 4.15 : Architecture compacte tenant compte de toutes les Simplifications</i>                                            | 70 |

| <i>Figure 4.16 : Architecture de l'égaliseur de canaux Adaptatif</i>                                                              | 72 |

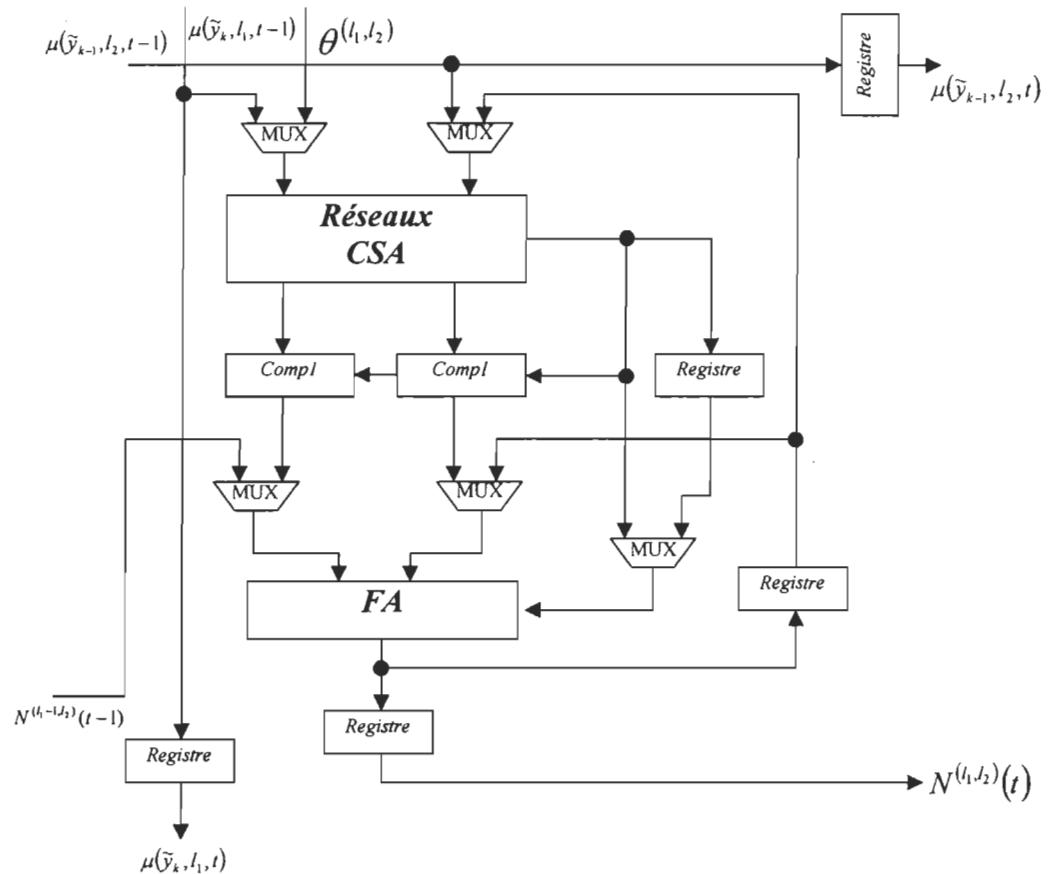

| <i>Figure 4.17 : Architecture interne de PE3</i>                                                                                  | 73 |

| <i>Figure 4.18 : Résultat de simulation du code VHDL</i>                                                                          | 75 |

| a. <i>Signal de sortie du canal b. Signal à la sortie de l'égaliseur</i>                                                          | 75 |

| <i>Figure 4.19 : l'architecture de la carte Aristotle de Mirotech</i>                                                             | 77 |

# *Liste des Tableaux*

|                                                                                     |    |

|-------------------------------------------------------------------------------------|----|

| <i>Tableau 2.1 : Sommaire des méthodes classiques [HAY93]</i>                       | 17 |

| <i>Tableau 3.1 : Algorithme LMS et RLS pour l'adaptation de <math>\theta</math></i> | 35 |

| <i>Tableau 4.1 : Résultats de synthèse</i>                                          | 76 |

| <i>Tableau 4.2 Résultats de Synthèse sur FPGA</i>                                   | 78 |

# ***Chapitre 1***

## ***Introduction***

On peut estimer que l'histoire des télécommunications a commencé en 1832 avec la découverte par le physicien américain Morse du mode de transmission codé. Parallèlement la téléphonie s'est développée. Marconi réalisa en 1899 la première liaison télégraphique par ondes hertzienne entre la France et l'Angleterre. En 1962 le satellite Telstar a permis la première liaison de télévision transocéanique. Ceci n'était qu'un point de départ pour le développement des moyens de communications. Le besoin de plus en plus croissant de la transmission temps réel et l'augmentation du volume des données transmises, va nous amener à améliorer la qualité et la quantité des données qui voyagent à travers les supports physiques. De nos jours on a tendance à faire le traitement numérique de l'information.

La théorie de la transmission de l'information a connu un formidable essor depuis que les travaux de Shannon (1948) ont démontré la possibilité théorique d'une transmission fiable.

Elle fait appel à des nombreuses disciplines : codage source, codage canal, égalisation et, plus généralement, à ce qui est convenu d'appeler la théorie de l'information. Deux grandes classes de techniques permettent d'assurer la fiabilité d'une transmission : le codage canal qui vise à coder le message émis de telle sorte que le récepteur soit à même de corriger la plupart des erreurs de transmission, et l'égalisation, dont l'objectif est d'exploiter au mieux la bande passante du média (canal de transmission).

Pour l'égalisation de canaux, théoriquement, l'algorithme de Viterbi [PRO95] permet d'avoir la transmission la plus fiable possible. Cependant, deux points limitent son usage : d'une part il présente une forte complexité calculatoire et d'autre part, il suppose que le récepteur connaît les distorsions dues à la transmission alors que les canaux de transmission réels sont inconnus et variables au cours du temps.

La méthode qu'on va développer dans ce mémoire est celle d'un égaliseur de canaux adaptatifs pour les canaux linéaires et non-linéaires basés sur la logique floue.

## 1.1 Problématique de recherche

La plupart des canaux de communication, entre autres les canaux téléphoniques, modems et certains canaux de radio, sont caractérisés par le passage d'un signal dans un canal de communication à bande passante limitée. De ce fait, si la vitesse de transmission du message est supérieure à la fréquence de coupure du canal, le signal transmis à travers ce canal va subir une distorsion qui dépend des caractéristiques de ce dernier. Pour augmenter le débit de transmission en télécommunication plusieurs méthodes ont été utilisées, telle que la compression de données [MAR95]. Ces dernières n'ont pas satisfait les exigences de plus en plus croissantes en terme de débit. Deux solutions sont possibles : soit changer le canal

de transmission pour augmenter sa bande passante ou bien prévoir un système de codage à l'émission et de correction à la réception. La première solution est assez coûteuse car les supports de transmission sont déjà existants et leur remplacement est difficile en plus il y a des supports de transmission qu'on ne peut pas changer entre autre l'air pour la transmission hertzienne. La seconde solution est celle qui permet d'utiliser les mêmes installations pour mieux servir l'utilisateur. Cette dernière consiste à planter au niveau du récepteur un système qui permet de récupérer l'information ou signal perturbé ou modifié, c'est ce qu'on appelle système d'égalisation de canaux. L'égaliseur a pour rôle d'estimer le signal transmis à partir du signal au récepteur. En absence de bruit l'égaliseur est simplement un filtre inverse dont le rôle est de rendre plate la réponse impulsionale de l'ensemble canal & égaliseur. Par contre lorsque le canal est bruité un simple filtre inverse amplifie considérablement le bruit surtout dans les régions où le signal utile est faible. Ce qui donne un signal totalement différent de celui qui était à l'entrée du canal. Pour remédier à ce problème on a souvent utilisé des méthodes d'égalisation des canaux basées sur le filtre linéaire transverse [HAY96]. La procédure d'étalonnage où la présence d'un canal non invariant et non stationnaire oblige une adaptation du modèle. Plusieurs algorithmes d'adaptations sont possibles mais seulement quelques-uns sont envisageables pour une intégration en technologie d'intégration à très grande échelle (ITGE - en anglais VLSI - Very Large Scale Integration). Les méthodes les plus fréquemment utilisées sont l'algorithme du gradient stochastique (LMS - Least Mean Square) et l'algorithme des moindres carrés récursifs (RLS - Recursive Least Squares).

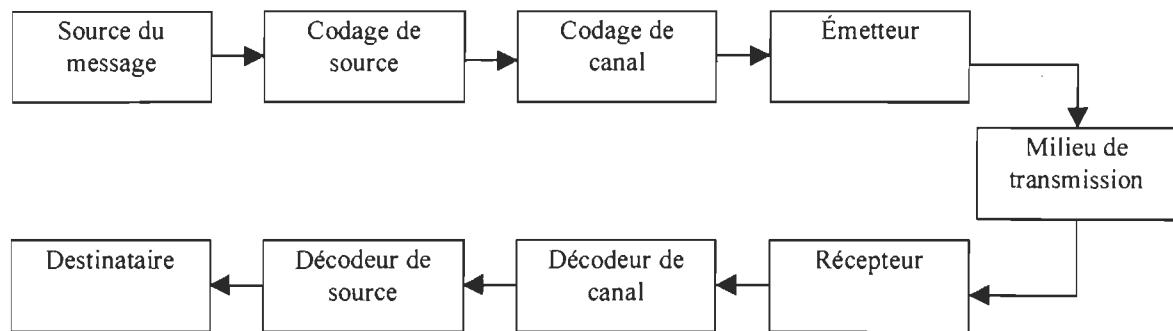

Le schéma de principe de la chaîne de transmission numérique est représenté sur la figure 1.1 [GLA96]. On peut distinguer : la source de message, le milieu de transmission

(ou canal de transmission), et le destinataire qui sont les données du problème. Le codage et le décodage de source, le codage et le décodage de canal, l'émetteur et le récepteur sont les degrés de liberté du constructeur pour réaliser le système de transmission.

*Figure 1.1 : Principe d'une chaîne de transmission numérique*

Le problème à résoudre dans ce projet est de proposer une méthode d'égalisation convenant aux canaux linéaires et non linéaires et pouvant satisfaire les contraintes et critères d'implantation en technologie ITGE. Pour cela, on va étudier la possibilité d'implanter un égalisateur adaptatif en se basant sur la technique de la logique floue. L'égaliseur à base de la logique floue, se caractérise par le fait qu'il présente des équations récurrentes menants à la possibilité d'une architecture ITGE hautement parallèle. En outre la logique floue présente un processus non linéaire qui se prête bien à la correction de canal de communication non linéaire. De plus, l'étude de la structure de l'algorithme par logique floue révèle la présence de plusieurs termes nuls dans l'étape de fuzzification, d'où la possibilité d'avoir une simplification significative de la complexité de calcul et de la surface d'intégration de l'architecture associée.

## 1.2 Objectifs

Le but de ce travail est de proposer un algorithme adaptatif performant pour les canaux linéaires et non linéaires. Il s'agit ensuite de simplifier et optimiser les différentes parties de l'algorithme pour pouvoir l'implanter en technologie VLSI (FPGA, ASIC). La recherche du compromis débit de calcul et surface d'intégration va nous permettre d'arriver avec une architecture numérique hautement parallèle. L'intégration en technologie CMOS ou sur FPGA nous permettra d'évaluer les performances de l'architecture en terme de latence, débit et surface d'intégration.

## 1.3 Méthodologie de recherche

A la suite d'une recherche bibliographique sur les algorithmes et architectures ITGE pour l'égalisation de canaux non linéaires, nous allons pouvoir justifier le choix de notre modèle basé sur la logique floue. En se basant sur les travaux de Wang & Mendel<sup>1</sup> [WAN93], qui ont proposé un égaliseur adaptatif à base de la logique floue avec adaptation des paramètres par un algorithme LMS ou RLS, nous allons étudier la possibilité d'implanter ce filtre en technologie ITGE.

Nous aurons à valider les performances de ce filtre par des résultats de simulation dans l'environnement Matlab® et par la suite il faudra étudier les caractéristiques du filtre mais sans adaptation des paramètres. Ceci va nous permettre d'évaluer la robustesse de ce type d'égaliseur vis-à-vis de la variation du niveau de bruit. Lors de l'étude de l'implantation de cet égaliseur, notre tâche sera de modifier l'algorithme afin de faciliter son implantation.

---

<sup>1</sup> Article publié dans le journal IEEE : « fuzzy adaptative filter with application to non-linear channel equalization » c'est l'article sur lequel se base notre étude.

On sait déjà que l'algorithme RLS présente une très grande complexité de calcul. Par conséquent on va étudier l'utilisation de l'algorithme LMS pour une implantation ITGE.

Nous proposerons une architecture systolique en considérant le canal comme étant invariant et par la suite nous proposerons une architecture pour le modèle adaptatif. La proposition d'une telle architecture exigera la recherche du compromis débit de calcul et surface d'intégration. La validation de l'architecture proposée se fera par la modélisation, la simulation et la synthèse du code VHDL avec les outils de Mentor Graphics® et Synopsis®. La synthèse des résultats fera état des performances de l'algorithme et de l'architecture systolique proposée. Un exemple de mise en œuvre de l'égaliseur proposé sera réalisé dans un circuit FPGA-DSP.

## **1.4 Structure du rapport**

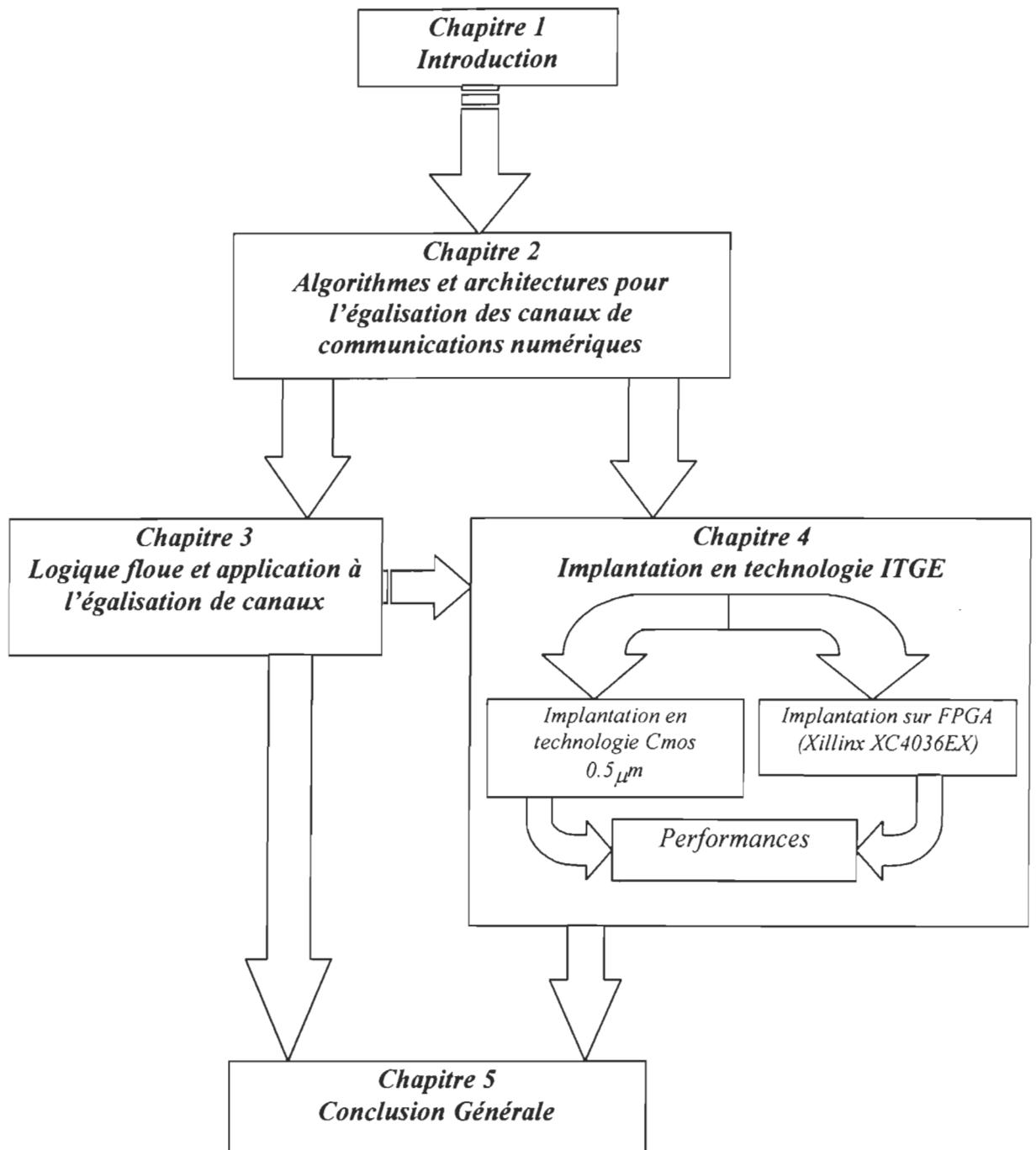

Ce mémoire se divise essentiellement en quatre chapitres (voir figure 1.2). Le premier chapitre sera consacré à expliciter la problématique de recherche, les objectifs ainsi que la méthodologie suivie tout au long de la réalisation de ce travail.

Dans le second chapitre, on commencera par définir le canal de transmission dans la section 2.1. par la suite on définira la problématique d'égalisation de canaux à la section 2.2. Au niveau de la section 2.3 on présentera les algorithmes d'égalisation de canaux que ce soit linéaire ou non-linéaire. Ensuite on présentera au niveau de la section 2.4 les différentes architectures retrouvées dans la littérature. La section 2.5 portera sur la justification du choix d'une technique pour l'égalisation de canaux, celle utilisant la logique floue. Cette technique sera détaillée dans le chapitre 3. À la section 3.2 on expliquera comment

---

appliquer la logique floue pour résoudre le problème d'égalisation de canaux. Enfin, au niveau de la section 3.3, on essayera d'apporter les simplifications nécessaires à l'algorithme proposé afin de le préparer à une implantation en technologie ITGE.

Le chapitre 4 portera sur les architectures proposées et leurs implantations. On commencera par une étude de quantification au niveau de la section 4.2, laquelle nous permettra de fixer le nombre de bits à utiliser dans l'architecture. Ensuite on proposera une architecture systolique dans la section 4.3. enfin on étudiera, dans la section 4.4, deux types d'implantation : celle pour un ASIC en technologie CMOS 0.5 µm dans la section 4.4.4 et celle d'une implantation en technologie FPGA de la compagnie Xilinx dans la section 4.4.5. et on terminera avec une conclusion générale.

*Figure 1.2 : Structure du rapport*

## *Chapitre 2*

# *Algorithmes et architectures pour l'égalisation de canaux*

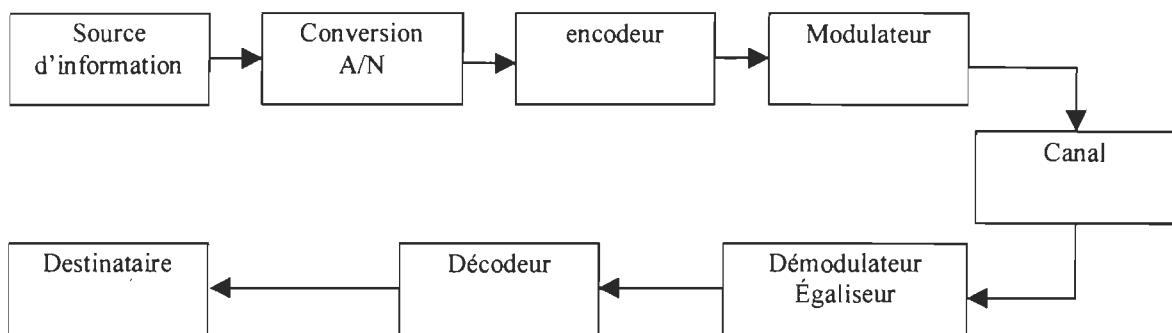

Il existe plusieurs formes sous lesquelles une information peut être présentée. On peut faire la transmission de la voix d'un signal vidéo, par conséquent l'information à transmettre peut être de type numérique ou analogique. On a toujours tendance à ramener à une représentation numérique par un convertisseur analogique à numérique (A/N). D'une manière générale et comme c'est présenté sur la figure 2.1, les systèmes de communication numérique commencent par un convertisseur A/N qui permet de représenter l'information sous forme binaire, ensuite on traite le signal numérisé pour lui appliquer une méthode de codage ou de compression. Ceci se passe dans le bloc encodeur. Le dernier élément qui permettra d'avoir le module d'émission est le modulateur. Il a pour rôle de convertir le signal numérique en un signal analogique pouvant être transmis dans un canal qui constitue

le médium de communication. Il peut s'agir d'un câble coaxial, bifilaire, une fibre optique ou encore l'air. Une fois le signal arrivé au récepteur, on commence par démoduler le signal afin d'obtenir l'information transmise. Au niveau du démodulateur il y aura un système qui permettra d'annuler ou de corriger les effets de distorsion apportés par le canal. C'est ce qu'on appelle l'égalisation de canaux.

*Figure 2.1 : schéma bloqué d'un système de communication numérique*

On trouve dans la littérature plusieurs algorithmes pour l'égalisation de canaux linéaires et non linéaires. De plus, l'intégration en technologie ITGE est très rare. Ce chapitre couvrira le domaine de recherche scientifique au niveau algorithmique et architectural d'égalisation de canaux linéaires et non linéaires. Par conséquent on va exposer certaines méthodes trouvées dans la littérature permettants de résoudre le problème d'égalisation de canaux linéaires et non linéaires. On va commencer par définir le canal de transmission dans le paragraphe 2.1, ensuite on expliquera la problématique d'égalisation de canaux à la section 2.2. La section 2.3 sera consacrée aux algorithmes d'égalisation de canaux. Ensuite on survolera le domaine de l'intégration ITGE de ce type d'algorithmes à la section 2.4. enfin, on aura à justifier l'utilisation de la logique floue pour la suite du travail.

## 2.1 Canal de transmission

### 2.1.1 Définition du canal

La plupart des canaux de communication entre autres les canaux téléphoniques, certains canaux de radio, sont caractérisés par une bande passante présentant des évanouissements d'amplitude et des non-linéarités de phase. Par conséquent, pour l'étude de la distorsion apportée par le canal, on peut caractériser chaque canal par sa réponse en fréquence  $C(f)$  comme suit :

$$C(f) = A(f) \cdot e^{j\theta(f)} \quad (2.1)$$

où  $A(f)$  est la réponse en amplitude du canal,  $\theta(f)$  est la réponse en phase du canal.

Une autre caractéristique souvent utilisée pour caractériser un canal de transmission est l'enveloppe de délai définie comme suit:

$$\tau(f) = -\frac{1}{2\pi} \frac{d\theta(f)}{df} \quad (2.2)$$

Un canal est dit idéal si dans la bande de fréquence du signal transmis la réponse en amplitude du canal  $A(f)$  est constante et la réponse,  $\theta(f)$ , est linéaire (ou  $\tau(f)=constante$ ) pour toutes les fréquences. Si  $A(f)$  n'est pas constante la distorsion subit par le signal est dite d'amplitude alors que si  $\tau(f)$  n'est pas constante la distorsion est dite de délai ou de phase. En résumé les termes  $A(f)$  et  $\theta(f)$  ou  $\tau(f)$ , définissent les caractéristiques du médium de transmission qui influent sur le signal qui traverse le canal en le distordant, ce qui donne un  $BER \neq 0$  sur le signal de sortie du canal. En plus de cette déformation apportée au signal

s'ajoute le bruit qui sera mesuré comme étant le rapport entre le signal transmis et le bruit ce qui définit le SNR.

### 2.1.2 Modélisation du canal

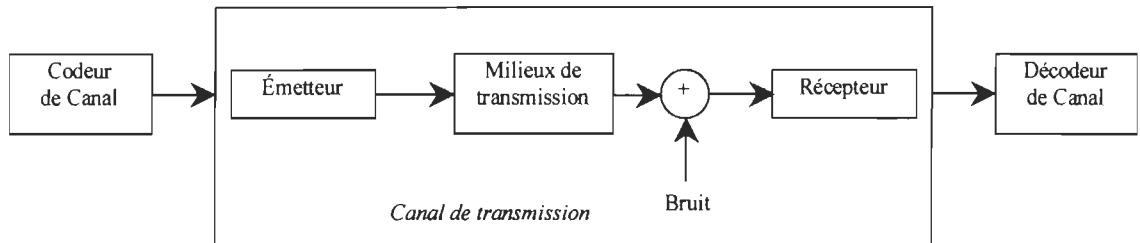

D'après la théorie du codage, un canal de transmission inclut toutes les fonctions situées entre la sortie du codeur du canal et l'entrée du décodeur [GLA96], voir figure 2.2.

Figure 2.2 : Le canal de transmission[GLA96]

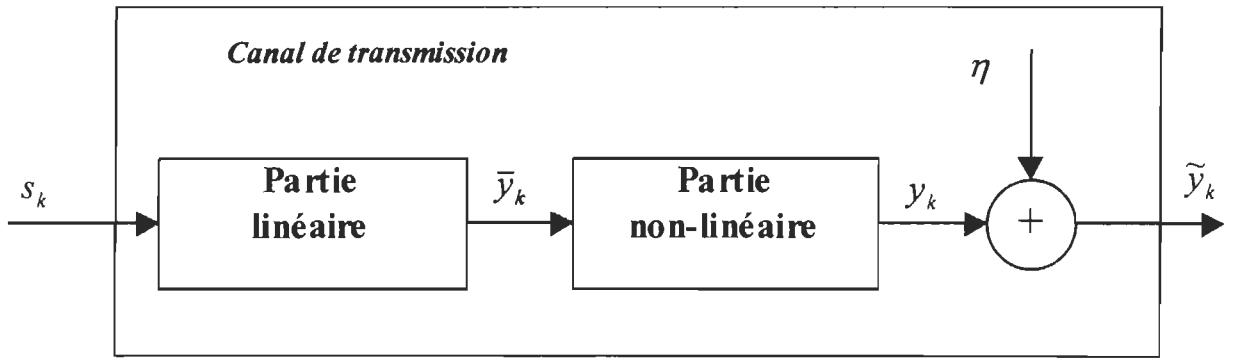

Les distorsions ou les déformations apportées au signal original peuvent parvenir de l'émetteur, du milieu de transmission, du bruit additif et du récepteur. L'émetteur est le bloc qui permet de transformer le signal numérique en un signal analogique, par l'ajout de la porteuse, ce qui le rend transportable par un canal. Le milieu de transmission peut être de l'air, un câble coaxial ou bifilaire, une fibre optique..., les caractéristiques du milieu introduisent des déformations sur le signal. Au niveau du récepteur on se trouve avec un signal analogique déformé dont la démodulation va encore introduire des distorsions. Toutes ces déformations subies par le signal au cours de son trajet depuis le codeur jusqu'au décodeur sont apportées par le canal de transmission. Ces distorsions peuvent être de caractère linéaire ou non-linéaire, stationnaires ou variables dans le temps. Dans le langage mathématique on peut remplacer la figure 2.2 par la figure 2.3. Le canal est

essentiellement composé de la partie linéaire qui reflète la réponse impulsionnelle du canal, généralement modélisée par un filtre passe bas, et une partie non-linéaire due aux autres composantes du canal de communication. En plus on aura un bruit additionnel inévitable  $\eta$  s'additionnant au signal  $y_k$  pour donner le signal  $\tilde{y}_k$  qui constitue la sortie du canal de transmission. Ce signal est l'image du signal  $s_k$  après avoir traversé le canal de transmission.

Figure 2.3 : Modélisation d'un canal de communication

## 2.2 Égalisation de canaux

### 2.2.1 Principe

L'origine du terme égalisation se comprend aisément dans le domaine des fréquences. Dans un égaliseur graphique de chaîne HI-FI [BRO97], des curseurs permettent d'ajuster des filtres passe bande autour de certaines fréquences. En réglant correctement les différents curseurs, l'utilisateur modifie à sa guise le spectre du signal issue de la source. Avant de parvenir à l'oreille de l'auditeur, le son est déformé par la réponse de la pièce d'écoute. La mise en cascade des déformations spectrales dues à la pièce et celles dues à l'égaliseur

graphique correctement réglé, permet d'obtenir une réponse globale plate sur la bande audio. La réponse de la chaîne liant la source à l'auditeur a été égalisé.

Dans le domaine des télécommunications, les données émises traversent un canal de transmission et les différents dispositifs électroniques associés à l'émetteur et au récepteur. Le rôle de l'égaliseur est alors de réduire au mieux les distorsions apportées par ces éléments. Pour compenser ces distorsions on utilise un filtre linéaire avec des paramètres ajustables suivant les caractéristiques du canal. Ces filtres ajustables sont appelés des égaliseurs ou encore égaliseurs de canaux. Pour les canaux avec une réponse en fréquence inconnue mais invariante dans le temps, on mesure les caractéristiques du canal et on ajuste en fonction les paramètres de l'égaliseur. Ces paramètres restent fixes durant la transmission des données. Ce type d'égaliseur est appelé égaliseur pré-établit (preset equalizer).

Lorsque le canal de transmission n'est plus invariant dans le temps, les techniques adaptatives de traitement permettent de concevoir des algorithmes estimants en permanence les paramètres pour l'égaliseur en minimisant un certain critère. On parle alors d'égalisation adaptative. Les algorithmes d'adaptation utilisés sont dits à décision rétroactive et les plus fréquemment utilisés sont les algorithmes LMS et RLS.

### 2.2.2 Égalisation adaptative

La différence avec les égaliseurs pré-établit est que les paramètres de l'égaliseur adaptatif ne sont pas fixes, mais ils seront adaptés par l'envoi d'un paquet de données connues  $s(k)$ .

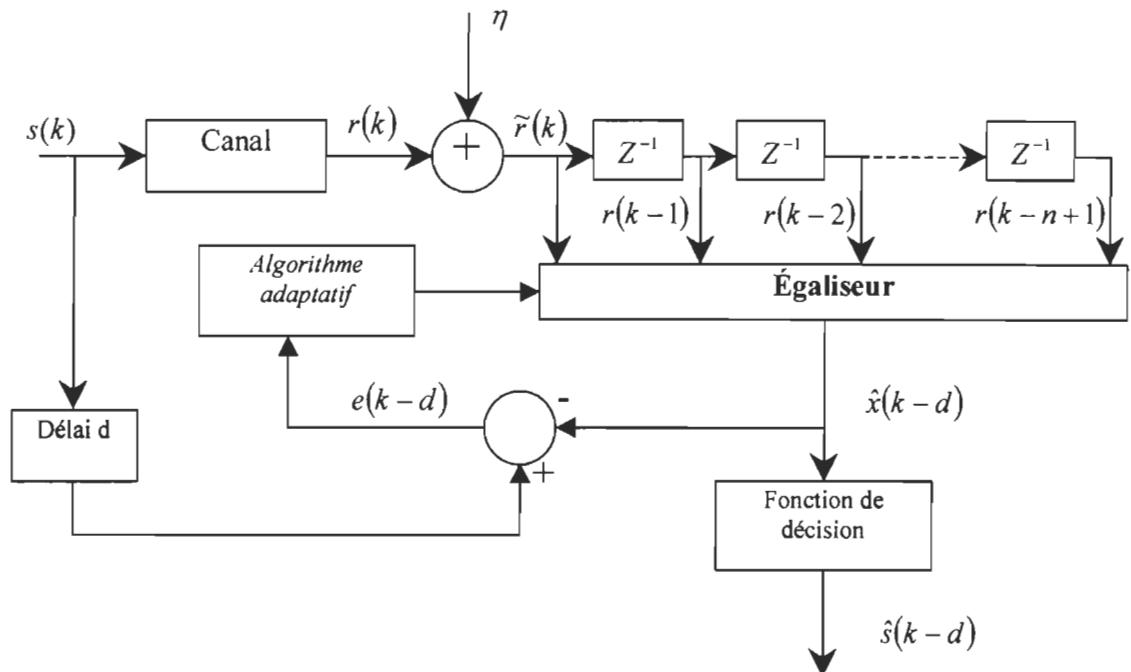

La figure 2.4 présente un égaliseur adaptatif,  $s(k)$  est la séquence de données provenant de l'émetteur traversant un canal qui y introduit des déformations dues à ces caractéristiques

linéaires ou non-linéaires. La sortie du canal est le signal  $r(k)$  corrompu par un bruit additif  $\eta(k)$  nous donne le signal  $\tilde{r}(k)$ . A partir de l'erreur de reconstitution  $e(k-d)$  les paramètres du filtre sont optimisés par un algorithme de minimisation d'erreur. L'adaptation des paramètres prendra un certain nombre de cycles afin de converger vers un minimum d'erreur de correction. Une fois que l'égaliseur est adapté au canal les paramètres de l'égaliseur sont conservés constants pour toute la durée de la communication, c'est le cas de la communication par modem. Par contre, si le canal varie l'adaptation doit assurer la poursuite des variations du canal par l'ajustement des paramètres de l'égaliseur, ce qui en général ne cause pas de problème pour de faibles variations. Dans le cas d'une variation brusque ou rapide du canal (milieu hostile), le temps d'adaptation devient critique et dépendra de l'algorithme utilisé et de sa mise en œuvre. Le signal de sortie de l'égaliseur  $\hat{x}(k-d)$  passe ensuite par une fonction de décision pour donner le signal  $\hat{s}(k-d)$ .

Figure 2.4 : Système d'égalisation de canaux adaptatif.

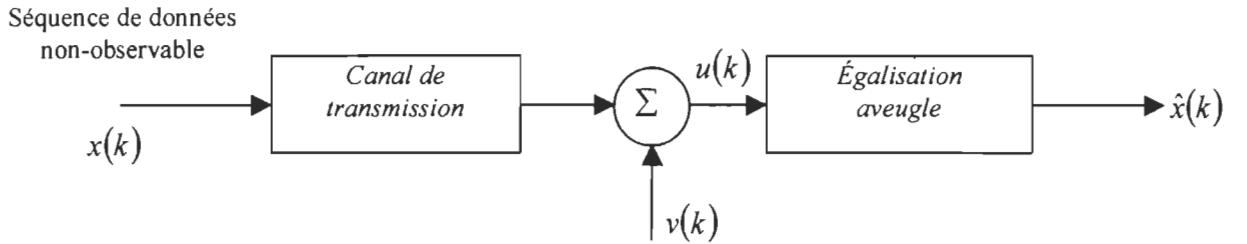

### 2.2.3 Égalisation autodidacte

Il n'est pas toujours possible de disposer d'une séquence d'apprentissage de la part de l'émetteur, De ce fait un autre type d'égalisation est utilisé, c'est ce qu'on appelle auto égalisation ou égalisation aveugle en anglais c'est "blind equalization". Le but de l'égalisation aveugle est de pouvoir reconstituer les données émises  $x(k)$  à partir de la seule observation de la sortie du canal  $u(k)$  (voir figure 2.5). On trouve principalement trois types d'algorithmes [PRO95] : L'égalisation aveugle basée sur le maximum de similitude, et les statistiques sur le signal d'ordre deux ou plus.

Figure 2.5 : Schéma bloc d'un égaliseur aveugle[HAY96]

## 2.3 Algorithmes pour l'égalisation de canaux

### 2.3.1 Algorithmes linéaires pour l'égalisation de canaux

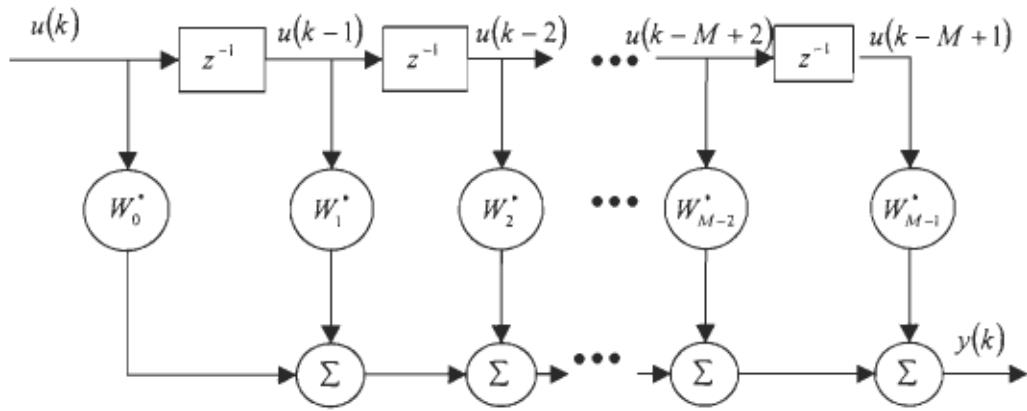

L'algorithme le plus couramment utilisé est le filtre linéaire transverse souvent appelé filtre à réponse impulsionnelle finie (RIF - FIR - Finit Impulse Response) présenté sur la figure 2.6. Il est défini par la relation de convolution linéaire suivante :

$$y(k) = \sum_{n=0}^{M-1} w(n)u(k-n) \quad (2.3)$$

Figure 2.6 : Filtre transverse [HAY96]

Les algorithmes d'adaptation des coefficients  $W$  les plus souvent utilisés sont LMS et RLS [HAY96]. Malheureusement, l'équation (2.3) ne s'applique que pour des systèmes de communication ayant un canal linéaire. L'égalisation de canaux linéaires se fait bien avec ces derniers, sauf que dans la pratique il est très rare de traiter des canaux linéaires. Le cas le plus général est celui des systèmes non linéaires. La logique floue [WAN93], [SAR95], [LEE94] et les réseaux de neurones [VID99], [KEC94] comme le montre plusieurs exemples dans la littérature, sont de plus en plus utilisés pour la modélisation de systèmes complexes. Ils s'apprêtent aussi bien pour les systèmes linéaires que non-linéaires. Le tableau 2.1 présente les principales équations permettant de modéliser le filtre LMS et RLS.

Tableau 2.1 : Sommaire des méthodes classiques [HAY93]

| LMS                                                               |       |

|-------------------------------------------------------------------|-------|

| $\hat{x}(k) = \mathbf{w}^T \tilde{\mathbf{y}}(k)$                 | (2.4) |

| $e(k) = s(k-d) - \hat{x}(k)$                                      | (2.5) |

| $\mathbf{w}(k+1) = \mathbf{w}(k) + \mu \tilde{\mathbf{y}}(k)e(k)$ | (2.6) |

| RLS                                                                                                                                          |        |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------|

| $\hat{x}(k) = \mathbf{w}^T \tilde{\mathbf{y}}(k)$                                                                                            | (2.7)  |

| $P(k) = \frac{1}{\lambda} P(k-1) - \frac{1}{\lambda} K(k) \tilde{\mathbf{y}}^T(k) P(k-1)$                                                    | (2.8)  |

| $K(k) = \frac{1}{\lambda} * \frac{P(k-1) \tilde{\mathbf{y}}(k)}{1 + \frac{1}{\lambda} \tilde{\mathbf{y}}^T(k) P(k-1) \tilde{\mathbf{y}}(k)}$ | (2.9)  |

| $\mathbf{w}(k) = \mathbf{w}(k-1) + K(k) e(k)$                                                                                                | (2.10) |

| $e(k+1) = s(k-d) - \hat{x}(k)$                                                                                                               | (2.11) |

### 2.3.2 Algorithmes non-linéaires pour l'égalisation de canaux

Les principaux égaliseurs non linéaires sont basés sur la structure DFE adaptative (DFE:"Decision Feedback Equalizer"). La structure dotée d'une partie transversale et d'une partie récursive avec décision dans la boucle de retour est appelée structure à décision dans la boucle ou à retour de décision (DFE). Cette structure est tout particulièrement adaptée aux systèmes numériques de communication. Une structure DFE permet d'égaliser des canaux beaucoup plus sévères qu'un simple filtre transverse linéaire.

Les coefficients du filtre transverse, de longueur finie, sont périodiquement actualisés de façon à minimiser un certain critère. Cette actualisation des coefficients est généralement réalisée après chaque décision. L'optimisation de ces paramètres se fait avec un algorithme linéaire tel que LMS ou RLS.

Considérons le cas d'un DFE utilisant LMS pour l'adaptation.

$$\hat{x}(k) = \sum_{n=1}^N w(n) v(n) \quad (2.12)$$

$$\hat{s}(k) = D(\hat{x}(k)) \quad (2.13)$$

Où w sont les K coefficients du filtre et v les entrées. La fonction D est une fonction non-linéaire de décision. La mise à jour des coefficients peut se faire à partir de l'équation :

$$W(k+1) = W(k) + \mu v(k)e(k) \quad (2.14)$$

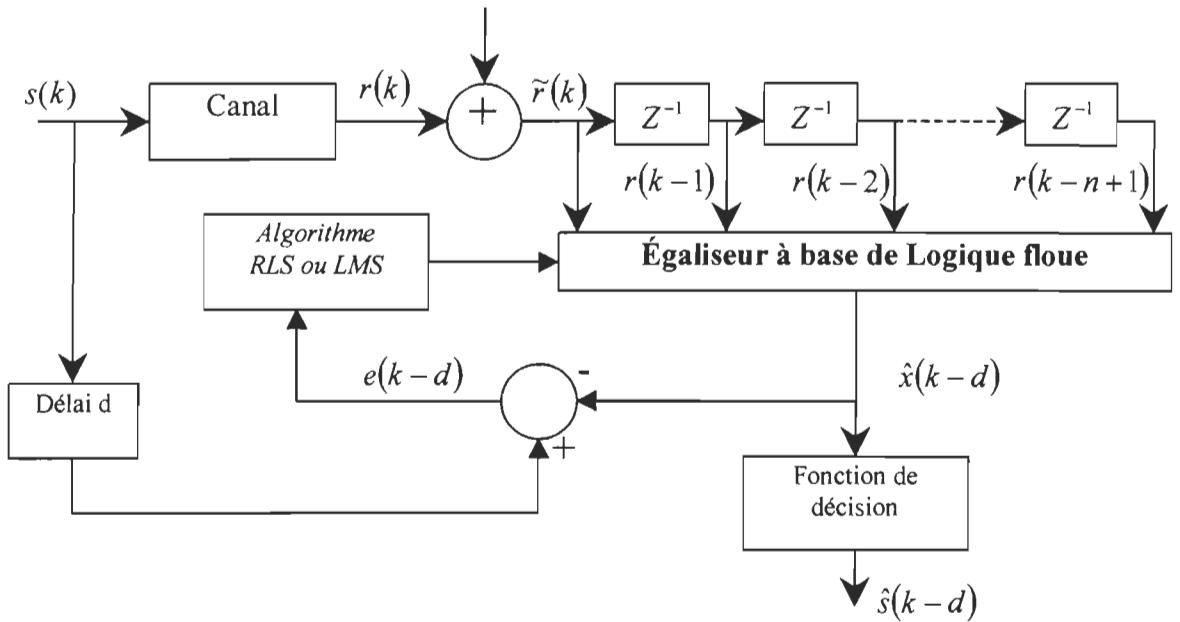

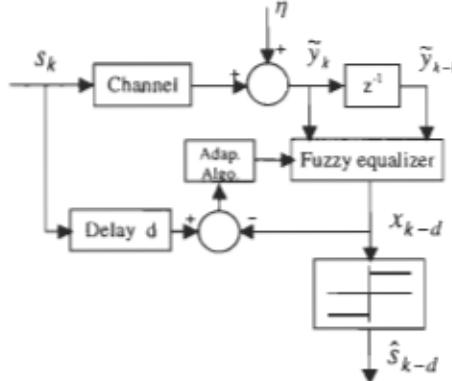

La figure 2.7 présente un exemple d'égaliseur de canaux non linéaires basé sur la logique floue utilisant LMS ou RLS pour l'adaptation des paramètres. Cet égaliseur va être détaillé dans les prochains chapitres. En effet c'est l'algorithme que l'on va implanter en technologie ITGE.

Figure 2.7 : Schéma simplifié de l'égaliseur à base de logique floue

$\tilde{y}(k)$  est l'échantillon d'entrée à l'instant k

$x(k)$  est le signal d'entrée à l'égaliseur à l'instant k

$x(k-n+1)$  est le signal d'entrée à l'égaliseur avec un retard n

$\hat{x}(k-d)$  est la sortie du canal après un délai d

## 2.4 Architecture pour l'égalisation de canaux

Plusieurs algorithmes ont été développés pour l'égalisation de canaux linéaires et non linéaires, cependant l'implantation en technologie ITGE reste limitée. La plupart des égaliseurs implantés sont analogiques. On peut citer l'exemple de processeur analogique réalisé par [CHO93] pour un système de réception.

Xue et Hu ont présenté un réseau de neurones partiellement connecté pour le système de GSM (Global System for Mobile communication) en Europe [XUE96]. Cette approche convient à une implantation ITGE. Vidal a présenté un réseau de neurones basé sur l'utilisation d'une fonction canonique linéaire par morceaux (CLM - en anglais Piecewise Linear) pour l'égalisation de canaux non linéaires [VID99]. Une autre architecture pour l'égalisation de canaux basée sur la logique floue a été développé par [PAT98].

## 2.5 Justification d'une intégration en technologie ITGE

Dans le domaine de la communication numérique plusieurs projets ont été fait pour améliorer la qualité et le volume des données transmises. Parmi les éléments constituants le système de télécommunication, c'est l'égalisation de canaux qui permet à l'utilisateur d'aller au-delà de la bande passante du canal. Les implantations pratiques des égaliseurs ont été souvent faites analogiquement. De nos jours nous tendons vers l'utilisation des circuits numériques qui présentent une très grande fiabilité et robustesse au bruit. L'intégration ITGE d'égaliseurs de canaux numériques est encore au stade de la recherche. C'est un sujet d'actualité et rare sont les articles publiés. L'application de la logique floue à la télécommunication est encore un domaine ouvert et qui mènera à des solutions intéressantes dans les prochaines années. L'intégration d'un égaliseur de canaux à base de

logique floue est donc un sujet original. En plus la logique floue s'apprête bien aux systèmes non linéaires. L'algorithme d'égalisation de canaux basé sur la logique floue proposé par Wang et Mandel [WAN93] (Annexe F) s'applique aussi bien pour les canaux linéaires que non-linéaires et l'étude de sa structure révèle la présence d'équations récurrentes pouvant conduire à une implantation ITGE avec une architecture hautement parallèle. En plus, comme on va le voir dans le chapitre 3, la simulation de l'algorithme à base de logique floue nous a permis d'obtenir des résultats très satisfaisants. C'est pour ces raisons qu'on a choisi de faire l'étude de cet algorithme pour l'implanter en technologie ITGE.

## *Chapitre 3*

### *Égaliseur basé sur la Logique floue*

Les démarches fondamentales de l'activité industrielle et économique, telle la conception des produits, la gestion des systèmes ou la prise de décision, posent des problèmes de complexité croissante, où, pour certains d'entre eux, une différence majeure tient à ce que les informations fournies ne sont pas précises ou ne peuvent être traitées dans un cadre probabiliste. Face à cette difficulté, les approches numériques, pourtant bien développées (les mathématiques de la décision ou de la théorie de la commande) ou symboliques, (l'intelligence artificielle et les systèmes à base de connaissances), ce sont avérées d'une efficacité limitée. Ce qui a poussé les scientifiques à s'intéresser à la formalisation des connaissances subjectives. Un pas décisif semble avoir été fait en 1965, avec le concept d'ensemble flou, proposé par Lotfi ZADEH [ZAD65], professeur de l'université de Californie à Berkeley.

De manière générale, la résolution d'un problème d'automatisme demande tout d'abord une modélisation mathématique du système à piloter, le plus souvent sous forme d'équations différentielles, permettant de calculer par exemple la commande optimale. Dans la pratique, cependant, il est rare de définir un modèle mathématique exact et simple à exploiter. Ces difficultés ont conduit Zadeh à proposer un moyen de décrire les relations entre les variables d'un système, et à publier un article d'une quinzaine de pages intitulé « fuzzy sets » (ensembles flous) [ZAD65], dix ans après il publia « the concept of linguistic variable and it's application to approximate reasonning » [ZAD75]. Ce qui a amené à introduire des concepts constitutifs la logique floue. Cette nouvelle technique de traitement des systèmes donne une approche plutôt pragmatique, permettant d'inclure aussi des expériences acquises par des opérateurs. Une série de travaux publiée par la suite ont contribué à l'échafaudage de cette théorie sur laquelle travaillent aujourd'hui plusieurs équipes universitaires et industrielles.

Les premières applications industrielles de la logique floue datent des années 70. En 1975 E.H Madani expérimenta un régulateur floue qu'il perfectionna dans les années suivantes. Cependant le vrai essor applicatif et médiatique n'est apparu que vers la fin des années 80, en grande partie grâce à l'intérêt que lui a porté le Japon. Aujourd'hui, la logique floue est de grande actualité, il s'agit d'une nouvelle méthode de traitement et de prise de décisions. Elle est surtout utilisée dans le domaine du réglage et de la commande de processus industriels.

Récemment on commence à entendre parler de la logique floue dans le domaine de la télécommunication et de l'informatique. Parmi ces applications on peut citer la réalisation d'un processeur RISC (Reduced Instruction Set Computer) pour la logique floue [EDD95],

en outre dans le domaine de la télécommunication Wang & Mandel ont proposé un algorithme pour l'égalisation de canaux linéaires et non linéaires à base de la logique floue [WAN93].

Dans ce chapitre on va commencer par présenter le vocabulaire utilisé, donner les notions de base de la logique floue, à savoir la notion d'ensemble flou, opérateurs logiques, variables linguistiques, et fonctions d'appartenance ensuite on détaillera les différents blocs constituants un système à base de logique floue : la fuzzification, les règles d'inférence et la défuzzification et on terminera cette première section par les caractéristiques et cas d'application de cette logique. La section 3.2 de ce chapitre sera consacrée à l'application de la logique floue à l'égalisation de canaux, entre autre la présentation du système d'égalisation et sa formalisation. Par la suite on présentera les résultats de simulation dans l'environnement Matlab<sup>®</sup> de l'égaliseur ainsi formulé. Et on terminera à la section 3.3 par une formulation d'un algorithme en vue d'une implantation en technologie ITGE.

### 3.1 Logique floue

#### 3.1.1 Notions de base

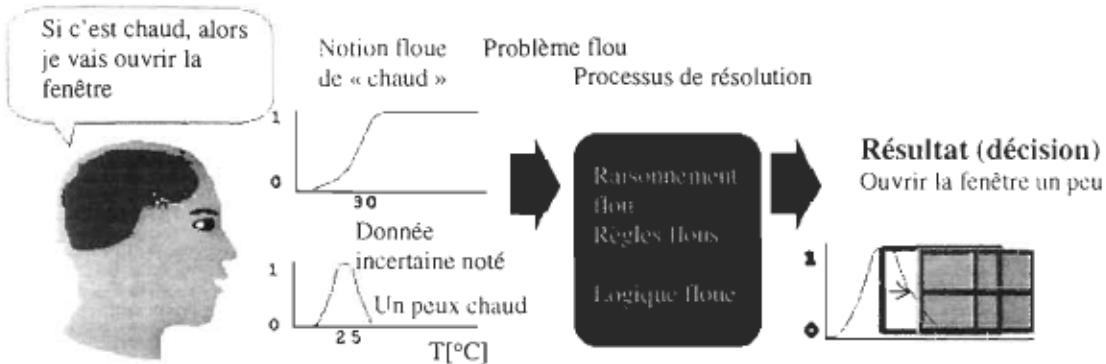

Le raisonnement par logique floue ressemble en quelque sorte au raisonnement humain, la figure 3.1 en donne un exemple : une personne dans une chambre, ressent que la température est un peu élevée. Dépendamment de la température de la chambre la personne va ouvrir la fenêtre à un certain degré.

Figure 3.1 : Analogie du raisonnement humain avec la logique floue

➤ *définition d'un ensemble flou*

Soit un ensemble de référence (ou univers)  $U$ , on définit un ensemble flou  $A$  dans  $U$  par la donnée d'une application  $\mu_A$  de  $U$  dans l'intervalle réel  $[0,1]$ . À tout élément  $x \in U$  on associe une valeur  $\mu_A(x)$  tel que

$$0 \leq \mu_A(x) \leq 1 \quad (\mu_A : U \rightarrow [0,1]) \quad (3.1)$$

L'application  $\mu_A$  est appelée fonction d'appartenance de l'ensemble flou  $A$ . À tout élément  $x$  de  $U$ , la valeur  $\mu_A$  associée n'est pas nécessairement égal à 0 ou 1, elle est à priori quelconque et désigne le degré d'appartenance de  $x$  à l'ensemble  $A$ . On peut distinguer trois cas :

- $\mu_A(x)=0$  : C'est-à-dire que  $x$  ne satisfait pas du tout la propriété vague sous-entendue par  $A$ .

- $\mu_A(x)=1$  : C'est-à-dire  $x$  satisfait pleinement la propriété vague définie par  $A$

-  $\mu_A(x) \neq 0,1$  : On dit que  $x$  appartient partiellement à l'ensemble flou A. On peut dire aussi que  $x$  ne satisfait que partiellement à un certain degré  $\mu_A(x)$  la propriété vague définit par A.

➤ *variables linguistiques & Opérateurs logiques*

La notion de variable linguistique a été introduite par Zadeh ; Elle suggère d'emblée que les valeurs de ces variables ne sont pas numériques, mais plutôt symboliques, en termes de mots ou d'expression du langage naturel. De manière générale on définit une variable linguistique comme appartenant à un intervalle  $[0,1]$  et associée à la fonction d'appartenance  $\mu_A$ .

Les variables linguistiques sont reliées entre elles par des opérateurs logique pour former ce qu'on appelle les règles d'inférence. Lorsque plusieurs variables d'entrée (prémisses) contribuent à faire varier une sortie, l'implication logique utilise les opérateurs booléens classiques «ou » et le « et » par exemple:

Si ( température est « fraîche » ou degré hygrométrique est « humide » alors « ouverture du robinet « grand ouverte »)

Dans cette implication, comment trouver le facteur d'appartenance de la sortie (ouverture du robinet) ? Il existe plusieurs façon de faire, la plus répandue semble celle qui a été formulé par Mandani comme suit:

À l'opérateur logique « ou » est associé la fonction MAX.

À l'opérateur logique « et » est associé la fonction MIN.

À l'opérateur logique « non » est associé la fonction complément à 1.

Ainsi, pour deux variables d'entrée  $x_1$  et  $x_2$  qui impliquent une variable de sortie  $s$  avec des coefficients d'appartenance respectifs  $\mu_1$ ,  $\mu_2$  et  $\delta$ :

$(x_1 \in E_1 \text{ ou } x_2 \in E_2) \text{ implique } (s \in S_1)$

on aura  $\delta = \max(\mu_1, \mu_2)$

$(x_1 \in E_1 \text{ et } x_2 \in E_2) \text{ implique } (s \in S_1)$

on aura  $\delta = \min(\mu_1, \mu_2)$

où  $E_1$  et  $E_2$  sont les deux ensembles flous dans l'espace d'entrée et  $S_1$  l'ensemble flou de sortie.

### 3.1.2 Éléments d'un système à base de logique floue

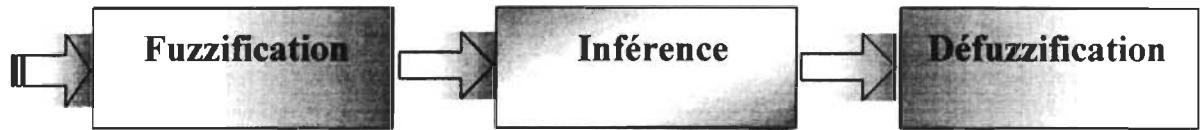

Tout système à base de logique floue peut être décomposé essentiellement en trois blocs (voir figure 3.2) : fuzzification, inférence et défuzzification.

Figure 3.2 : Différents blocs d'un système à base de logique floue

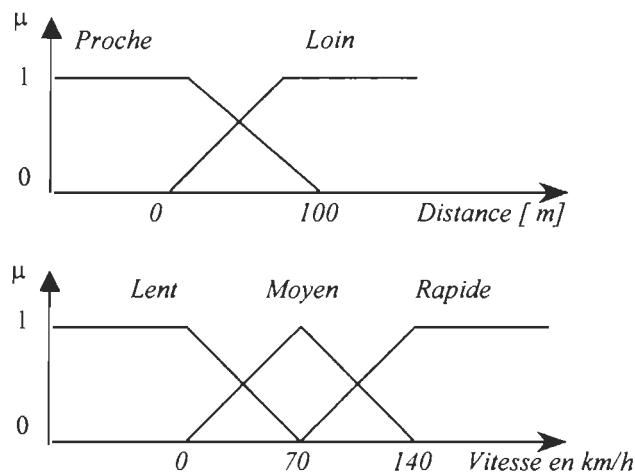

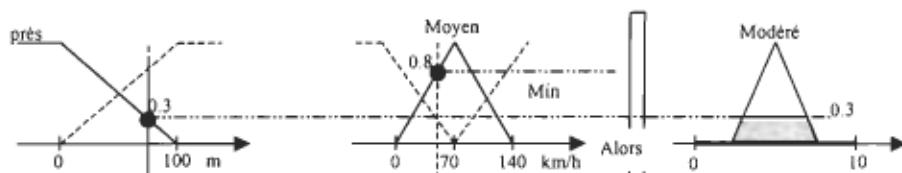

On va définir ces trois blocs par un exemple pratique tiré de [MAU97]. Dans cet exemple nous désirons doser le freinage d'un véhicule (variable de sortie) en fonction de la vitesse et la distance à l'obstacle (variables d'entrée).

#### ➤ *Fuzzification des variables*

Dans cette partie on définit les variables d'entrée et on caractérise, de manière numérique, l'imprécision qui peut exister sur ces valeurs.

Entrée<sup>2</sup>

*Vitesse du véhicule (de 0 à 140 km/h) :*      *lent*                  *moyen*                  *rapide*

*Proximité de l'obstacle (de 0 à 100m) :*      *proche*                  *éloigné*

Sortie

*Freinage (sur une échelle de 0 à 10) :*      *Faible*                  *Modéré*                  *énergique*

On choisit une forme triangulaire (voir figure 3.3) pour les fonctions d'appartenance sauf aux extrémités.

Figure 3.3 : Fonction d'appartenance d'entrée au système

#### ➤ Formulation des règles d'inférence

Dans le bloc inférence, les valeurs des variables linguistiques sont liées par plusieurs règles qui doivent tenir compte du comportement statique et dynamique du système à régler ainsi que du but du réglage envisagé. Ces règles sont formulées sous la forme suivante:

*Si [(obstacle == proche) et (vitesse == moyenne)] alors (freinage =modéré)*

*Si [(vitesse == rapide)] alors (freinage = énergique)*

<sup>2</sup> « vitesse du véhicule » et « proximité de l'obstacle » sont les variables linguistiques. Lent, moyen, Rapide sont les ensembles fous.

*Si [obstacle == loin] et [vitesse == lente] alors [freinage =faible]*

La figure 3.4 résume l'application des trois règles d'inférences. supposons le cas où les valeurs des variables d'entrée sont:

Distance à l'obstacle 60m ce qui implique que l'obstacle est près à 30% et loin à 70%.

Vitesse du véhicule 56km/h ce qui implique que la vitesse est moyenne à 80% et rapide à 0%.

#### Règle 1

#### Règle 2

#### Règle 3

Figure 3.4: Fuzzification – règles d'inférences – défuzzification

Nous observons que plusieurs combinaisons de valeurs des variables d'entrée n'interviennent pas dans les prémisses. Par exemple :

*Si [ (obstacle == loin) et (vitesse == rapide) ]* n'est pas cité ce qui signifie que l'expert n'a pas d'opinion sur cette situation.

La somme logique (ou) de tous ces ensembles flous conduit, en dernier ressort, à un ensemble flou final dont la forme est la conséquence de l'opération MAX. C'est à partir de cette forme qu'on doit tirer la décision à prendre. Ceci détermine l'opération de défuzzification.

#### ➤ *Défuzzification*

Cette étape permet d'affecter une valeur précise comprise entre 0 et 10 au freinage, déduite de l'ensemble floue de sortie. Il existe plusieurs méthodes :

#### *Méthode COG ( The center of gravity of the area )*

On cherche le centre de gravité de la surface obtenue. L'abscisse donne la valeur de freinage défuzzifiée. Soit  $Z$  l'abscisse de la courbe qui définit la surface de défuzzification (figure 3.4). Les coefficients  $W_i$  désignent la valeur correspondante à chaque  $Z_i$  le  $i^{\text{eme}}$  échantillon d'entrée sur un nombre total de  $n$  échantillons

$$Z_{\text{out}} = \frac{\sum_{i=0}^n w_i \cdot z_i}{\sum_{i=0}^n w_i} \quad (3.2)$$

Par la méthode de défuzzification par le centre de gravité on obtient dans notre exemple une valeur de  $Z_{\text{out}}=0.35$ , Donc on aura un freinage de 3.5 sur une échelle de 0 à 10.

### **Méthode MOA ( The middle of the area )**

$$\sum_{i=0}^h w_i = \sum_{i=h}^n w_i \quad Z_h = Z_{out} \quad (3.3)$$

Où  $0 < h < n$ ,  $h$  représente l'indice pour lequel l'égalité de l'équation (3.3) est vérifiée et  $n$  est le nombre total de coefficients  $w_i$ . Avec cette méthode on trouve  $Z_h=3.5$  avec  $n=20$

### **Méthode MOM**

$$z_{out} = \frac{\sum_{i \in M} z_i}{|M|} \quad M = \arg_i \text{Max}\{w_i\} \quad (3.4)$$

#### **3.1.3 Propriété de la logique floue**

##### *➤ Avantage par rapport aux méthodes conventionnelles*

Les méthodes conventionnelles se basent sur une modélisation adéquate du système à corriger mises souvent sous forme de fonction de transfert analytique ou d'équations d'états. Cela nécessite des notions avancées du modèle mathématique du problème. Par contre, la logique floue donne une approche plutôt pragmatique, permettant d'inclure des expériences acquises par des opérateurs.

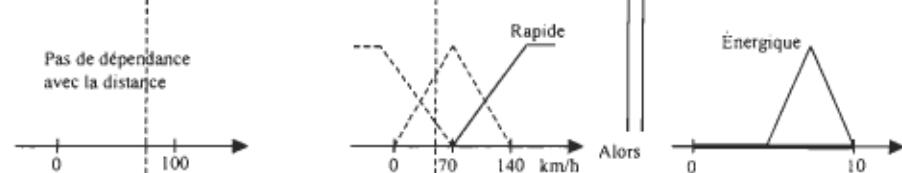

##### *➤ Prise en compte des données imprécises ou incertaines*

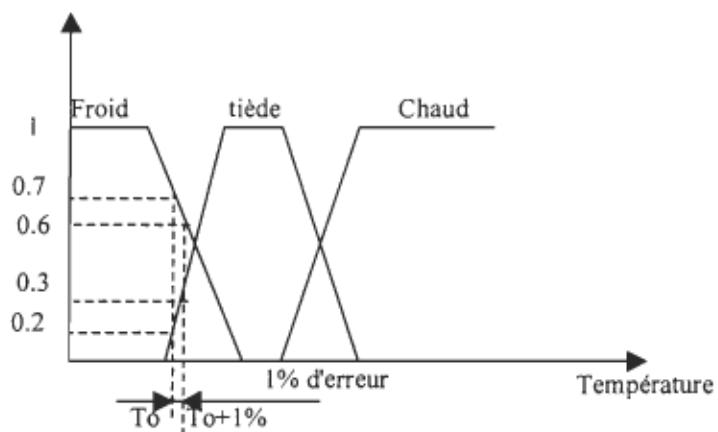

Il est très important de ne pas être obligé de seuiller tout de suite les notions d'entrée d'un système de décision, car une erreur de 1% sur la valeur du seuil peut provoquer une erreur de 100% sur la décision. C'est ce que montre la figure 3.5 dans le cas simple où la décision est justement l'appartenance ou non à l'ensemble défini par ce seuil.

Figure 3.5 : logique classique et données imprécises

La logique floue permet de manipuler des notions sémantiquement contradictoires mais numériquement non exclusives (figure 3.6).

Figure 3.6 : Logique floue et données imprécises

### 3.1.4 Exemple d'application

L'application de la logique floue a été très utilisée par les industries japonaises en grande partie pour la régulation d'appareils de grande consommation telle que la machine à laver,

le réfrigérateur, la mise au point automatique pour les appareils photos aussi pour les tunneliers, le contrôle du débit de la température de l'eau, le four de verrerie, le métro, etc.

### 3.2 Application de la logique floue à l'égalisation de canaux

#### 3.2.1 Principe

Selon le principe énoncé à la section 2.3.2 (figure 2.4), l'idée est d'accorder à chaque  $x(k)$  échantillon d'entrée à l'instant  $n$  un degré d'appartenance à chacune des fonctions d'appartenance qui couvrent l'espace d'entrée. Cette étape va déterminer le bloc de fuzzification. La seconde étape consiste à utiliser un algorithme adaptatif qui permet de construire les règles d'inférence en optimisant l'erreur entre la sortie du canal et le signal idéal. La dernière étape consiste à extraire la décision à prendre à partir de ces règles ce qui va constituer le bloc de défuzzification. La sortie de ce bloc va fournir l'estimé  $\hat{s}(k)$ . En se basant sur ce principe de l'égaliseur [WAN93] on va développer le fonctionnement de l'algorithme proposé et faire une étude approfondie qui permettra de le simplifier pour une implantation ultérieure.

#### 3.2.2 Réalisation de l'égaliseur à base de logique floue

Considérons le vecteur  $\tilde{r}(k)$  de valeurs réelles et une séquence de valeurs réelles  $s(k)$ , Avec  $k=1, 2 \dots, K$  est l'index de temps.

$$\tilde{r}(k) \in U = [C_1^-, C_1^+] \times [C_2^-, C_2^+] \times \dots \times [C_n^-, C_n^+] \subset R^n \quad (3.5)$$

Où  $[C_i^-, C_i^+]$  représente les intervalles des ensembles flous d'entrée et  $n$  le nombre total d'intervalles. À chaque instant  $n$  on a les valeurs  $\tilde{r}(k)$  et  $s(k)$ , le problème est de déterminer le filtre adaptatif à chaque instant  $n$ . C'est ici où intervient le filtre RLS pour minimiser le

critère  $J(k)$ . La fonction  $f_k$  fait correspondre aux valeurs de l'ensemble d'entrée une valeur réelle  $\hat{x}(k)$  qui correspond à la sortie de l'égaliseur.

$$f_k : U \subset R'' \rightarrow R$$

$$J(k) = \sum_{i=0}^k \lambda^{k-i} [s(i) - f_k(\tilde{r}(i))]^2 \quad (3.6)$$

$\lambda$  est dit le facteur d'oubli.

Comme on a vu dans le paragraphe précédent, il faut définir des fonctions d'appartenance pour réaliser le bloc de fuzzification. ces fonctions sont définies par  $\mu_{F_i^j}(X_i)$  pour chaque intervalle  $[C_i^-, C_i^+]$ . En se referant à [WAN93], les équations des fonctions d'appartenance sont définies comme suit :

$$\mu_{F_i^j}(x_i) = \exp \left[ -\frac{1}{2} \left( \frac{x_i - \bar{x}_i}{0.3} \right)^2 \right] \quad (3.7)$$

$\bar{x}_i^j$  définit la valeur où la fonction d'appartenance  $\mu_{F_i^j}$  attend sa valeur maximale.

$$x_i = \tilde{r}(k)$$

La deuxième étape est la réalisation du bloc d'inférence qui est formé de règles :

$$R^{(j_1 \dots j_n)} : Si \ X_1 \in F_1^{j_1} \ et \dots \ et \ X_n \in F_n^{j_n} \ Alors \ d \in G^{(j_1 \dots j_n)}$$

Ces règles seront déterminées par un filtre adaptatif tel que RLS ou LMS qui permet de les construire en minimisant à chaque itération l'erreur  $e(n)$  définie comme suit.

$$e(k) = s(k) - \hat{x}(k) \quad (3.8)$$

Dans notre cas ces règles sont représentées par le vecteur  $\theta$  défini par l'équation (3.9). Ce dernier est une concaténation de  $m_2$  vecteurs dont chacun est composé de  $m_1$  éléments [WAN93].

$$\begin{aligned} \theta = & \left[ \theta^{(1,1,\dots,1)}(x), \dots, \theta^{(m_1,1,\dots,1)}(x) \right. \\ & \theta^{(1,2,\dots,1)}(x), \dots, \theta^{(m_1,2,\dots,1)}(x) \\ & \dots \\ & \left. \theta^{(1,m_2,\dots,m_n)}(x), \dots, \theta^{(m_1,m_2,\dots,m_n)}(x) \right] \end{aligned} \quad (3.9)$$

Les valeurs du vecteur  $\theta$  sont adaptées par l'algorithme LMS, Eq. (3.10), ou l'algorithme RLS, Es. (3.11), résumé dans le tableau 3.1.

Tableau 3.1 : Algorithme LMS et RLS pour l'adaptation de  $\theta$

|                                                                                                                                                   |        |

|---------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| LMS :                                                                                                                                             |        |

| $\theta(k+1) = \theta(k) + \mu.e(k).P$                                                                                                            | (3.10) |

| $e(k) = S(k) - \hat{x}(k)$                                                                                                                        |        |

| RLS                                                                                                                                               |        |

| $\varphi(k) = p(x(k))$                                                                                                                            | (3.11) |

| $P(k) = \frac{1}{\lambda} \left[ P(k-1) - P(k-1)\varphi(k) \left( \lambda + \varphi^T(k)P(k-1)\varphi(k) \right)^{-1} \varphi^T(k)P(k-1) \right]$ |        |

| $K(k) = P(k-1)\varphi(k) \left[ \lambda + \varphi^T(k)P(k-1)\varphi(k) \right]^{-1}$                                                              |        |

| $\theta(k) = \theta(k-1) + K(n)(S(k) - \varphi^T(k)\theta(k-1))$                                                                                  |        |

La dernière étape est d'extraire la décision à prendre de ces règles ce qui constitue l'étape de défuzzification. Cette étape peut être réalisée par plusieurs méthodes. Dans notre cas on utilise la méthode de centroïde [WAN92]. Le résultat de la défuzzification est donné par l'équation (3.12):

$$\hat{x}_k(\tilde{r}) = \frac{\sum_{j_1=1}^{m_1} \dots \sum_{j_k=1}^{m_k} \theta^{(j_1, \dots, j_k)} \cdot (\mu_{F_1^{j_1}}(\tilde{r}_1), \dots, \mu_{F_k^{j_k}}(\tilde{r}_k))}{\sum_{j_1=1}^{m_1} \dots \sum_{j_k=1}^{m_k} (\mu_{F_1^{j_1}}(\tilde{r}_1), \dots, \mu_{F_k^{j_k}}(\tilde{r}_k))} \quad (3.12)$$

$$p^{(j_1, \dots, j_k)}(\tilde{r}) = \frac{\mu_{F_1^{j_1}}(\tilde{r}_1), \dots, \mu_{F_k^{j_k}}(\tilde{r}_k)}{\sum_{j_1=1}^{m_1} \dots \sum_{j_k=1}^{m_k} (\mu_{F_1^{j_1}}(\tilde{r}_1), \dots, \mu_{F_k^{j_k}}(\tilde{r}_k))} \quad (3.13)$$

$p^{(j_1, \dots, j_k)}(\tilde{r})$  représente les fonctions floues qui font associer à chaque  $\tilde{r}$ , valeur d'entrée à l'égaliseur une valeur qui sera déterminée en fonction de son appartenance aux différents ensembles flous donnés par la fonction d'appartenance  $\mu_{F_i^{j_i}}$ . Il s'écrit de la manière suivante :

$$p = \left[ p^{(1,1,\dots,1)}(\tilde{r}), \dots, p^{(m_1,1,\dots,1)}(\tilde{r}) \right. \\ \left. p^{(1,2,\dots,1)}(\tilde{r}), \dots, p^{(m_1,2,\dots,1)}(\tilde{r}) \right. \\ \vdots \\ \left. p^{(1,m_2,\dots,m_k)}(\tilde{r}), \dots, p^{(m_1,m_2,\dots,m_k)}(\tilde{r}) \right] \quad (3.14)$$

En se basant sur (3.12) et (3.13) on peut écrire

$$\hat{x}_k(\tilde{r}) = p^T(\tilde{r}) \cdot \theta \quad (3.15)$$

Enfin l'égaliseur ainsi formulé peut être représenté d'une manière schématique la figure 3.7.

Figure 3.7 Égaliseur de canaux à base de logique floue

### 3.4 Simulation dans l'environnement Matlab®

Dans cette section on aura à valider le fonctionnement de l'algorithme d'égalisation de canaux à base de logique floue formulé au paragraphe précédent. Par conséquent, on a à comparer ces performances par rapport à d'autres algorithmes tels que LMS et RLS. Les programmes Matlab sont disponibles à l'annexe A. En outre on présentera sa robustesse au bruit et à la non-linéarité du canal. La base de la comparaison est le BER « Bit Error Rate » qui est défini en terme de pourcentage par l'équation (3.16).

$$BER = \frac{\text{Nombre de bits erronés}}{\text{Nombre de bits transmis}} \times 100 \quad (3.16)$$

Le BER est le quotient du nombre de bits erronés par le nombre total de bits transmis. C'est un indicateur très utile pour évaluer la vitesse de convergence des algorithmes et leur robustesse au bruit. Il est le plus souvent représenté sur une échelle logarithmique.

### 3.3.1 Canaux utilisés

On va utiliser deux types de canaux pour la simulation et la comparaison des différents algorithmes :

➤ *Canal linéaire selon [HAY96]*

$$h_k = \begin{cases} \frac{1}{2} \left[ 1 + \cos\left(\frac{2\pi}{W}(k-2)\right) \right], & n = 1, 2, 3 \\ 0 & \text{sinon} \end{cases} \quad (3.17)$$

C'est un canal dont la réponse impulsionnelle  $h_n$  est à trois points,  $W$  est le paramètre qui définit la largeur du canal.

➤ *Canal non-linéaire selon [WAN93],[VID99]*

On va choisir deux types de canaux non linéaires le premier représenté par l'équation (3.18), proposé par [WAN93] et le deuxième par l'équation (3.19), est fortement non linéaire [VID99].

Canal 1 :

$$\tilde{y}(k) = s(k) + 0.5s(k-1) - 0.9[s(k) + 0.5s(k-1)]^3 + \eta(k) \quad (3.18)$$

Canal 2 :

$$y_n = 0.5x + x^2 + x^3 \\ \text{où } x = 0.25s(k-2) + s(k-1) + 0.25s(k) \quad (3.19)$$

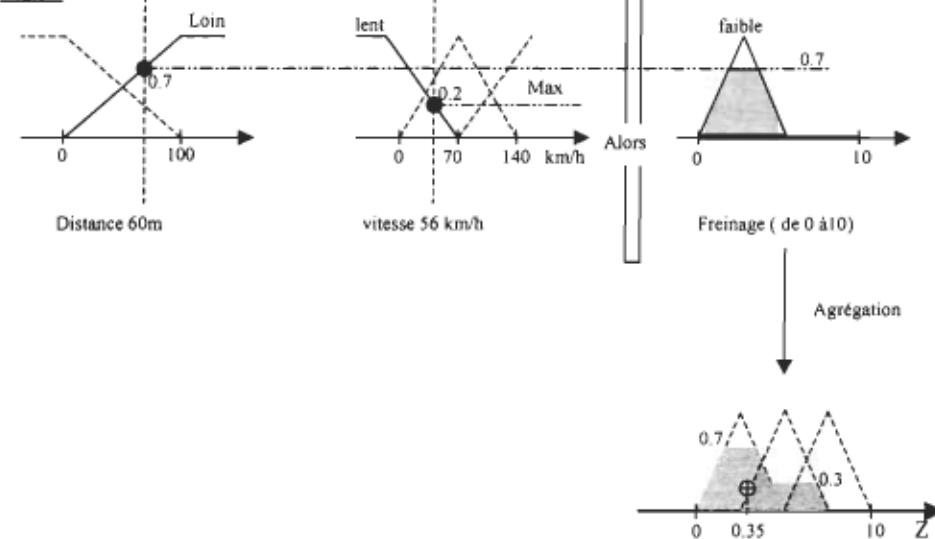

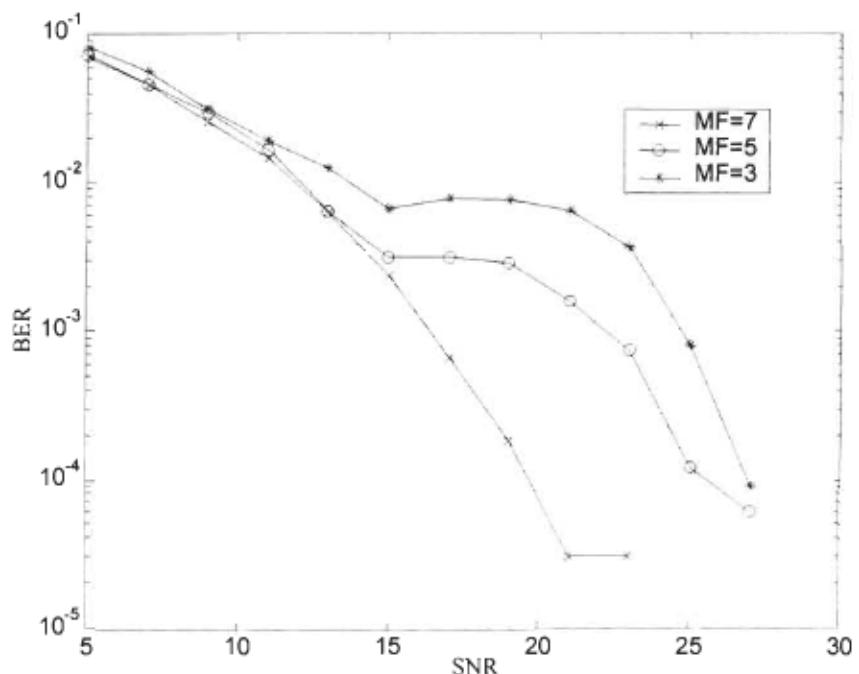

### 3.3.2 Influence du nombre de fonctions d'appartenance

Pour choisir le nombre de fonction d'appartenance ("Membership Function", MF) au niveau du bloc de fuzzification on va comparer les résultats de simulation pour MF=3, 5 et 7 pour le canal linéaire de l'équation (3.17) et non linéaire de l'équation(3.19). La figure 3.8 indique la variation du BER en fonction du SNR « Signal Noise Rate » utilisant LMS

pour l'adaptation des paramètres. Le nombre d'échantillons  $k$ , pour l'adaptation est fixé à 500 avec  $\mu=0.2$ . La valeur de  $\mu$  influe sur la vitesse de convergence de LMS vers un minimum d'erreur. Une valeur très élevée peut conduire le système à diverger. Donc on a choisi d'avoir une valeur moyenne de  $\mu$  pour assurer une convergence rapide.

Figure 3.8 : Influence du nombre de fonction d'appartenance (en utilisant un canal linéaire)

On remarque que pour un canal linéaire, la qualité de l'égalisation s'améliore en fonction du nombre de fonctions d'appartenance. Le BER devient acceptable pour  $MF \geq 7$ .

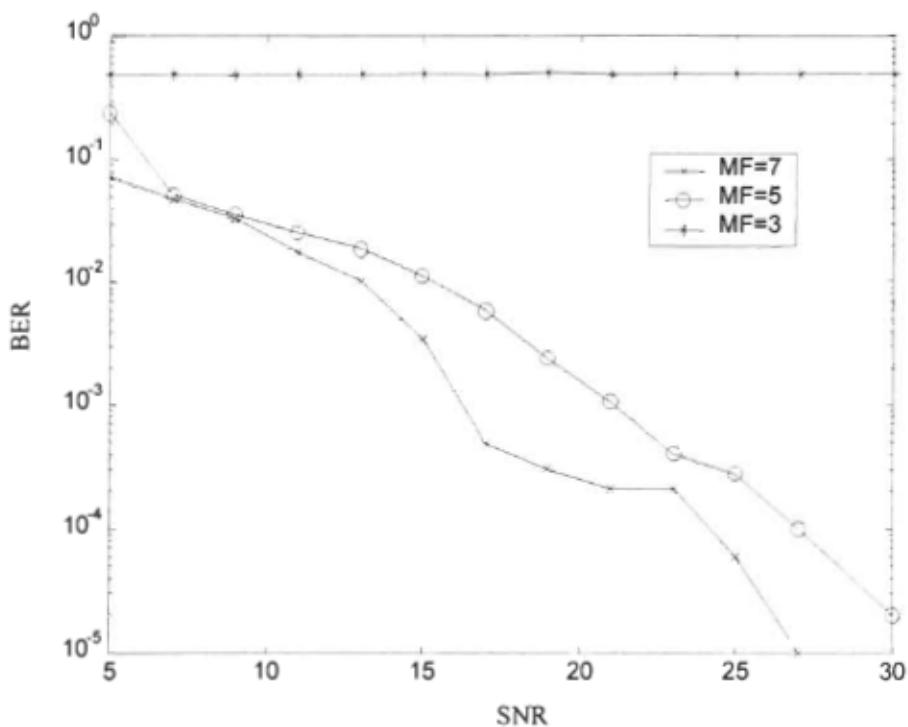

Les mêmes simulations ont été réalisées pour le canal non-linéaire donné par l'équation (3.19). la figure 3.9 résume les résultats obtenus.

Figure 3.9 : Influence du nombre de fonction d'appartenance (en utilisant un canal non-linéaire)

On remarque que pour un canal non-linéaire trois fonctions d'appartenance dans le bloc de fuzzification n'est pas suffisant pour éliminer l'effet du canal.

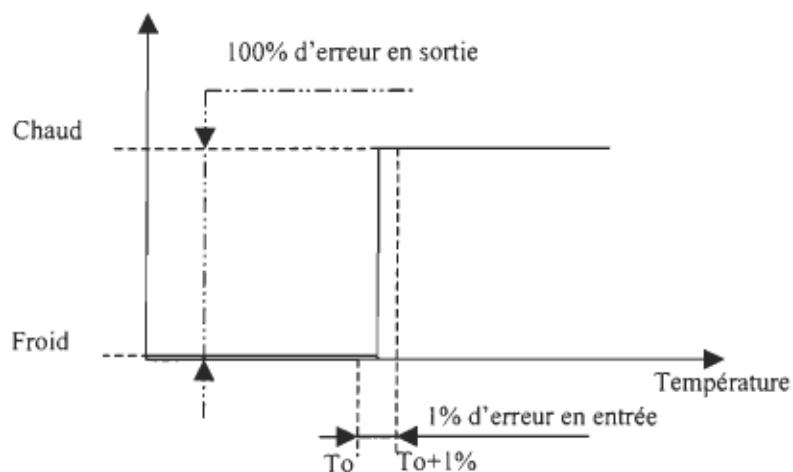

### 3.3.3 Comparaison de la logique floue avec LMS et RLS.

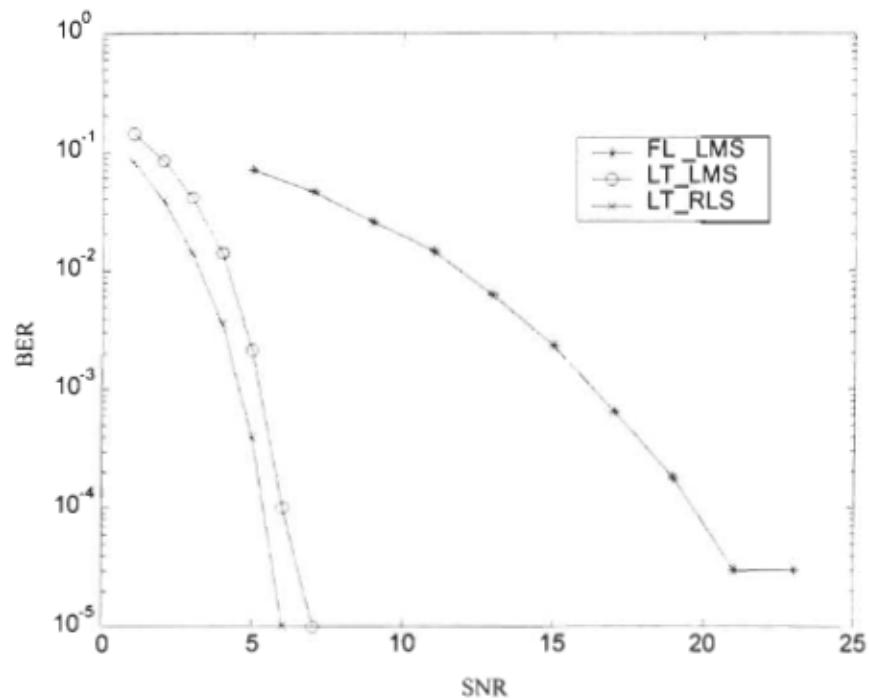

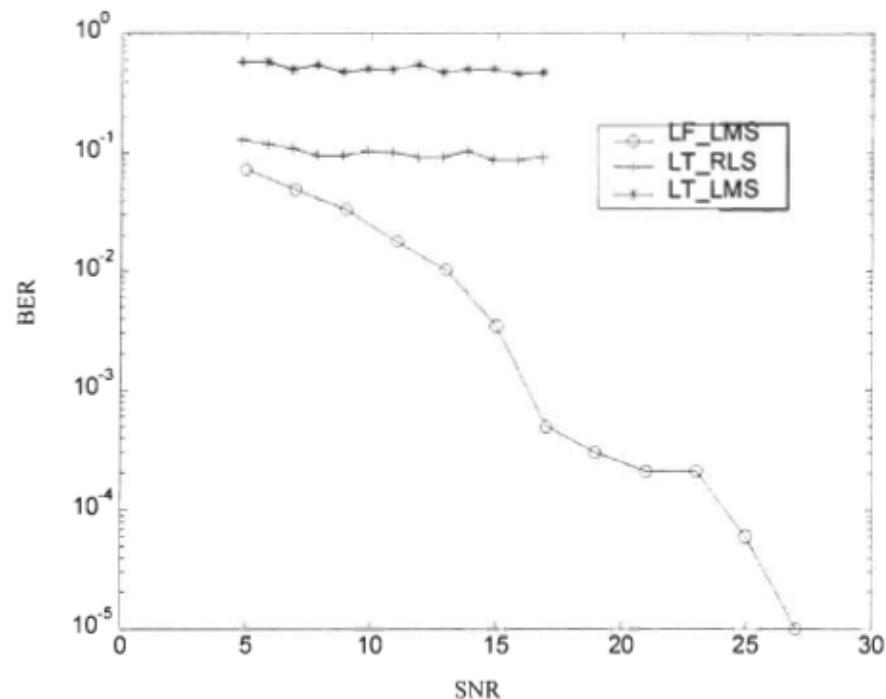

Pour justifier l'utilisation de l'algorithme d'égalisation de canaux non-linéaires à base de logique floue, on doit le comparer à d'autres méthodes. La figure 3.10 permet de le comparer l'algorithme basé sur la logique floue avec adaptation des paramètres par LMS (LF\_LMS), avec les filtres transverses linéaires RLS et LMS (LT\_LMS, LT\_RLS) pour le canal linéaire défini par l'équation 3.17. La figure (3.11) donne le résultat de simulation pour le canal non-linéaire donné par l'équation (3.19).

Figure 3.10 : comparaison de la logique floue avec RLS et LMS pour un canal linéaire