UNIVERSITÉ DU QUÉBEC

MÉMOIRE PRÉSENTÉ À

L'UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

COMME EXIGENCE PARTIELLE

DE LA MAÎTRISE EN GÉNIE ÉLECTRIQUE

PAR

HUGUES ACHIGUI JEAZET

CONVERTISSEUR ANALOGIQUE-NUMÉRIQUE À APPROXIMATIONS

SUCCESSIVES OPÉRANT À I-V DANS UN PROCÉDÉ CMOS SUBMICRONIQUE

JUILLET 2011

Université du Québec à Trois-Rivières

Service de la bibliothèque

Avertissement

L'auteur de ce mémoire ou de cette thèse a autorisé l'Université du Québec à Trois-Rivières à diffuser, à des fins non lucratives, une copie de son mémoire ou de sa thèse.

Cette diffusion n'entraîne pas une renonciation de la part de l'auteur à ses droits de propriété intellectuelle, incluant le droit d'auteur, sur ce mémoire ou cette thèse. Notamment, la reproduction ou la publication de la totalité ou d'une partie importante de ce mémoire ou de cette thèse requiert son autorisation.

*À ma famille*

## ***REMERCIEMENTS***

Tout d'abord, je tiens à remercier mon directeur de recherche, M. Christian J. B. FAYOMI, professeur à l'Université du Québec à Montréal, de m'avoir donné l'opportunité de travailler avec lui dans ce monde si pointu qu'est la microélectronique. Sa patience et son engouement dans mes travaux de recherches m'ont été d'un grand support.

J'aimerais ensuite remercier mon codirecteur, M. Daniel Massicotte, professeur à l'Université du Québec à Trois-Rivières, qui m'a intégré dans son équipe de recherche. Ses années d'expérience m'ont permis d'accroître mes connaissances dans l'univers de la microélectronique, et de m'appesantir sur les défis critiques et le sens des responsabilités.

J'exprime aussi ma gratitude aux membres de ma famille, pour leur support, toute la patience qu'ils ont su démontrer jusqu'ici, tout au long de mon parcours scolaire. Un merci spécial à ma maman Élise ACHIGUI et mon papa Benjamin ACHIGUI, qui chaque jour, n'ont cessé de me motiver et me pousser à exceller dans ce travail. Un merci tout particulier à mes frères Hervé FACPONG ACHIGUI, Joseph MESSI ACHIGUI et Kuété ACHIGUI, à mes sœurs Bertille Claire MAFOKOU, Sylvie FOYET ACHIGUI et Barbette NONGNI ACHIGUI. Un merci spécial à ma feu tante Laurentine MASSI et son époux Paul NINGINI. Un merci à tous mes oncles, à toutes mes tantes, ainsi qu'à toutes mes cousines et cousins.

Je m'en voudrais si je n'adressais pas un merci spécial à Mr. Jean Bosco ÉTOA ÉTOA et son épouse Suzanne ÉTOA ÉTOA. Un merci également à Emmanuel BOUENDEU, Maurice WOBENG, Erick DJOUMESSI, Marcel EPANYA, Arsène MELANOUE, Jean-Yves KAZOCK ainsi qu'à leurs épouses et enfants respectifs pour leurs encadrements et leurs précieux conseils.

Merci à mes amis Paul Moreau SENDJO, Pierre FOKAM, Ghislain DOMTUÉ, Adeline AZANGUE, Alain TCHOKOMANI, Leonel DJOUMESSI, Yves MBIANDA, Baldé

MAMADOU, Dalton COLOMBO, Carl BARIBEAU, Mathieu VAILLANCOURT, Louis-Philippe RISPOLI, Linda CHOUMELE, Diane MATSOM, Jeanine FEUDJO, Ariane NDONDA et Aïchatou DICKO pour leur soutien quotidien.

Je n'oublierais pas mes collègues et amis du local PK-4690 pour l'aide, l'appui et la bonne atmosphère. Un merci particulier s'adresse à Claude CHAGNON et Guy PARADIS, pour avoir mis à ma disposition tout le matériel dont j'ai eu besoin durant mes travaux de recherche.

Pour finir, toute ma reconnaissance aux personnes qui ont contribuées de près ou de loin à la réalisation de ce projet de maîtrise.

## RÉSUMÉ

L'intérêt porté vers les systèmes numériques a connu un essor sans précédent au cours des deux dernières décennies. Ceci étant principalement dû à la demande des applications qui nécessitent des méthodes numériques. Tout cela a été rendu possible grâce aux merveilles de la technologie CMOS. Cette technologie est plus appropriée aux applications analogiques et numériques. La première raison est que les circuits VLSI sont typiquement implémentés en CMOS.

La réduction d'échelle des technologies microélectroniques a permis d'améliorer certains aspects des circuits électroniques. L'un de ces aspects est la consommation d'énergie dans l'univers des applications biomédicales. La notion d'application biomédicale renvoie vers le traitement du signal, en conséquence, il y a des composants qui interagissent. Cette interaction consiste à faire cohabiter les signaux analogiques et composants numériques. La cohabitation de ces deux domaines nécessitent un convertisseur analogique numérique ou numérique-analogique qui, a priori, sont des éléments de traduction entre les domaines analogiques et numériques.

Les convertisseurs analogiques numériques (CAN) sont des composants qui occupent une place prépondérante dans les circuits électroniques. Il existe plusieurs architectures de convertisseur, mais le choix d'une architecture dépend considérablement de la nature de l'application et de sa capacité à consommer l'énergie. Cette variété au niveau architectural justifie la raison pour laquelle les travaux sur les CAN restent une quête perpétuelle vers la recherche d'un éventail de connaissances jusqu'ici non acquises.

Le présent mémoire vise à proposer des solutions innovatrices à la conception des convertisseurs analogiques numériques à approximations successives opérant à 1V et dédiés au domaine biomédical. Les principales sources de consommation d'énergie dans un convertisseur analogique numérique à approximations successives sont: le comparateur et le convertisseur numérique-analogique. Nous présentons une nouvelle

architecture de comparateur qui emploie une technique connue sous le nom de “Suiveur de tension inversée” (*FLIPPED VOLTAGE FOLLOWER*) au niveau de la paire d’entrée différentielle. Ce comparateur est ensuite utilisé dans deux architectures distinctes de convertisseur analogique numérique à approximations successives ayant une résolution de 8 et 10-bits, un taux de conversion qui varie de 1 M à 1.25 M-échantillons par seconde (MS/s). Ces architectures ont été implémentées dans la technologie CMOS 0.18  $\mu\text{m}$ .

Pour vérifier et valider la fonctionnalité de ces convertisseurs analogiques numériques proposés, nous avons réalisé le dessin des masques afin de s’assurer que ces architectures fonctionnent aussi bien en implémentation pré et post dessin des masques. Les résultats des simulations du convertisseur analogique numérique à approximation successive à 10 bits permettent de constater qu’il réalise un facteur de mérite (FOM) de 0.27 pJ/pas-de-conversion, un taux de conversion égale à 1 MS/s, un rapport signal sur bruit (S/B) de 57.86 dB sous une tension d’alimentation de 1 Volt. Les résultats de mesure du comparateur permettent de constater qu’échantillonné à 20 MHz, le comparateur réalise une résolution de 12 bits et dissipe une puissance de 63.5  $\mu\text{W}$ .

## ***LISTE DES FIGURES***

|                |                                                                                                                                                                                           |          |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Figure 2.1 :   | Schéma bloc d'un CAN à approximations successives. ....                                                                                                                                   | 5        |

| Figure 2.2:    | Arbre de recherche binaire d'un CAN-AS durant le processus d'identification du code                                                                                                       | 110..... |

| Figure 2.3 :   | Fonction de transfert illustrant l'erreur de tension d'un CAN à 3 bits.....                                                                                                               | 9        |

| Figure 2.4 :   | Fonction de transfert illustrant l'erreur de gain d'un CAN à 3 bits. ....                                                                                                                 | 9        |

| Figure 2.5 :   | Exemple de mesure du DNL d'un CAN à 3 bits.....                                                                                                                                           | 11       |

| Figure 2.6 :   | Exemple de mesure de l'INL d'un CAN à 3 bits.....                                                                                                                                         | 12       |

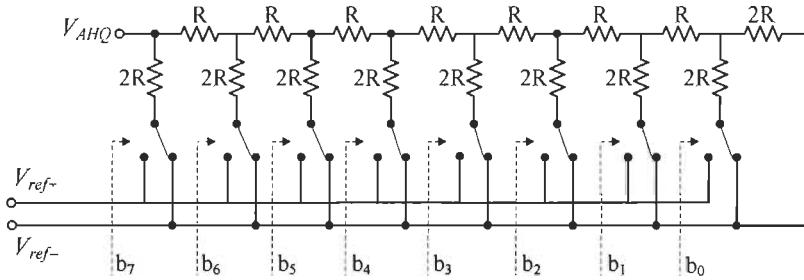

| Figure 3.1:    | Schématique d'un CNA de type R-2R (Tiré de [MOR00]). .....                                                                                                                                | 16       |

| Figure 3.2:    | Schématique du circuit d'E/B (tiré de [MOR00])......                                                                                                                                      | 17       |

| Figure 3.3:    | Comparateur à verrou utilisant une approche à mode courant (Tiré de [MOR00]). .....                                                                                                       | 18       |

| Figure 3.4:    | CNA traditionnel en mode tension (Tiré de [FAY01]).....                                                                                                                                   | 19       |

| Figure 3.5:    | Circuit d'un échantillonneur bloqueur (Tiré de [FAY01]) .....                                                                                                                             | 19       |

| Figure 3.6:    | Schématique de l'E/B (Tiré de [FAY01]): (a) Commutateur amorcé à compensation et (b) Commutateur dummy amorcé. .....                                                                      | 20       |

| Figure 3.7 :   | CNA à mode courant basé uniquement sur les transistors de type pMOS (Tiré de [FAY01]). .....                                                                                              | 21       |

| Figure 3.8 :   | Schématique d'un Amp-op à basse tension utilisé pour convertir le courant en tension (Tiré de [FAY01]).....                                                                               | 21       |

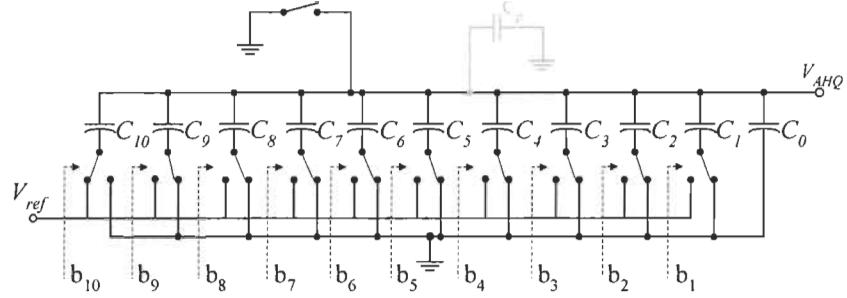

| Figure 3.9 :   | Schématique du CNA à réseau de capacités pondérées en binaire (Tiré de [McC75])....                                                                                                       | 22       |

| Figure 3.10 :  | Circuit équivalent d'un réseau conventionnel de capacités pondérées en binaire à 2 bits durant le mode échantillonnage : (a) Circuit lorsque $C_{MSB}=C$ et (b) lorsque $C_{MSB}=2C$ .... | 23       |

| Figure 3.11 :  | Circuit équivalent du C-CNA: Mode attente. ....                                                                                                                                           | 24       |

| Figure 3.12 :  | Circuit équivalent du C-CNA: Première étape de conversion. ....                                                                                                                           | 25       |

| Figure 3.13 :  | Schéma bloc du C-CNA conventionnel à 2 bits lorsque $b1 = 1$ .....                                                                                                                        | 28       |

| Figure 3.14 :  | Schéma bloc C-CNA à 2 bits lorsque $b1=0$ .....                                                                                                                                           | 28       |

| Figure 3.15 :  | C-CNA à n-bits formé d'un réseau CFPB (Tiré de [GIN07]).....                                                                                                                              | 30       |

| Figure 3.16 :  | Schéma bloc d'un C-CNA à 2 bits (Tiré de [GIN07]).....                                                                                                                                    | 30       |

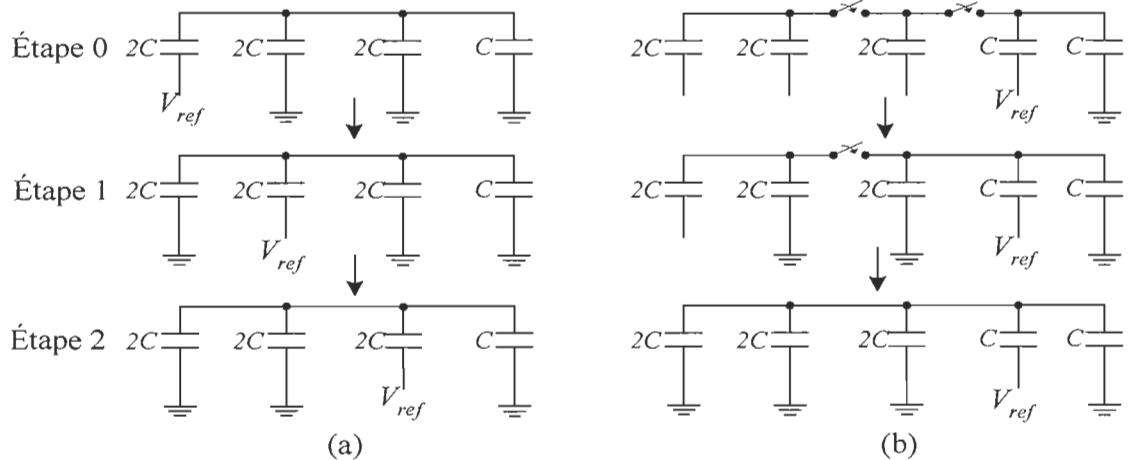

| Figure 3.17 :  | Méthode de commutation du C-CNA (Tiré de [GIN07]): (a) 1er cycle binaire et (b) commutation des capacités durant la transition “descendante”.....                                         | 31       |

| Figure 3.18. : | Schéma bloc d'un C-CNA à 3 bits (Tiré de [JEO08]). .....                                                                                                                                  | 32       |

|               |                                                                                                                                                                                      |    |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 3.19 : | Transition des commutateurs pour l'identification du code 000: (a) C-CNA conventionnel à 3-bits et (b) C-CNA à 3 bits avec des capacités à jonctions fractionnées (Tiré de [JEO08]). | 33 |

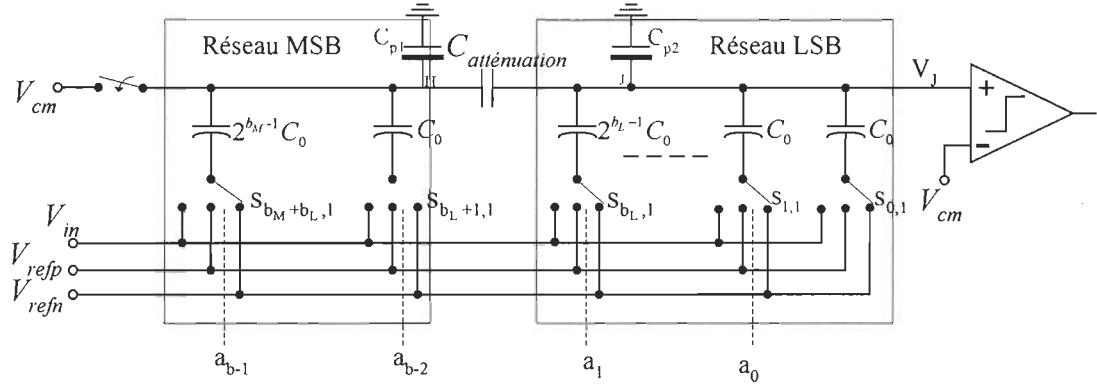

| Figure 3.20 : | Schéma bloc d'un CNA à charges pondérées utilisant une capacité d'atténuation (Tiré de [BAK05]).                                                                                     | 34 |

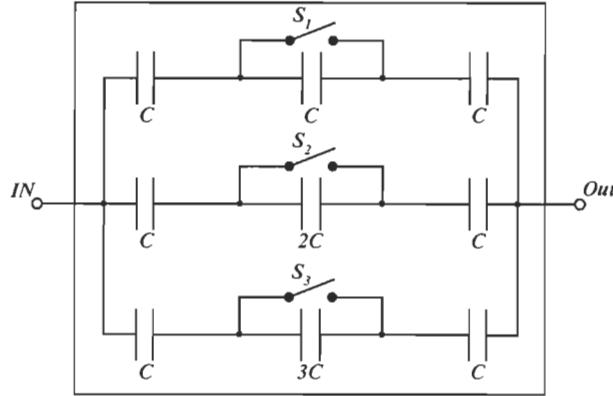

| Figure 3.21 : | Schéma bloc d'une capacité réglable (Tiré de [ABD07]).                                                                                                                               | 35 |

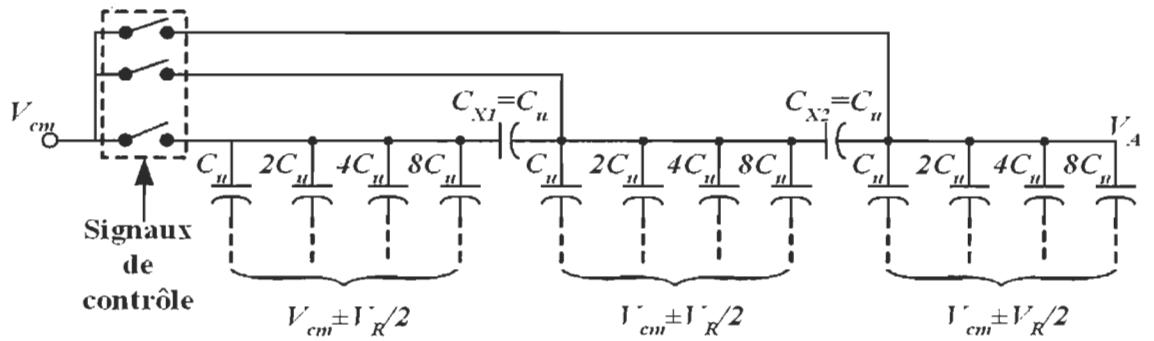

| Figure 3.22 : | C-CNA avec deux capacités d'atténuation (Tiré de [AGN08]).                                                                                                                           | 35 |

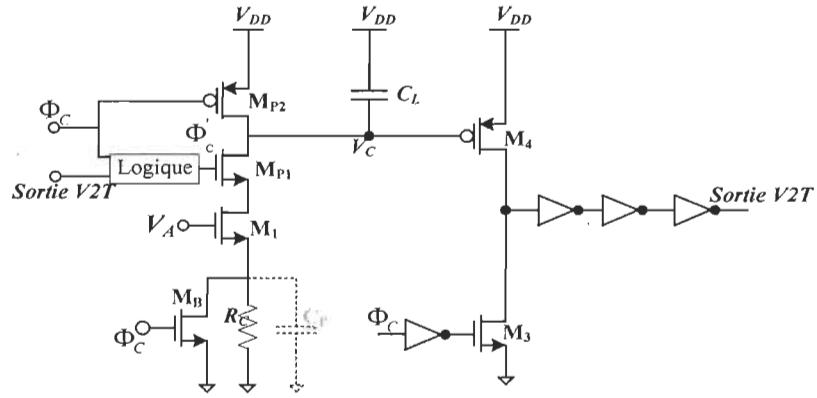

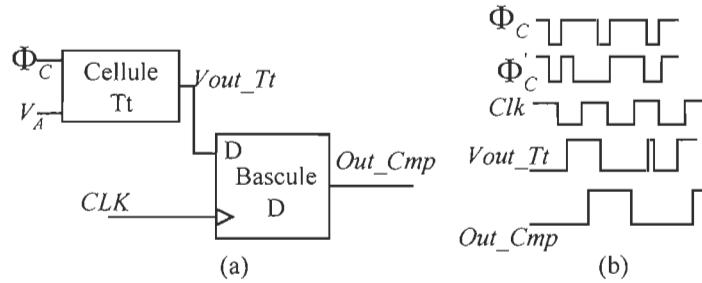

| Figure 3.23 : | Schéma bloc de la cellule tension-temps (Tt) (Tiré de [AGN08]).                                                                                                                      | 36 |

| Figure 3.24 : | Schématique du comparateur (Tiré de [AGN08]): (a) Bloc comparateur à domaine temporel et (b) diagramme temporel.                                                                     | 36 |

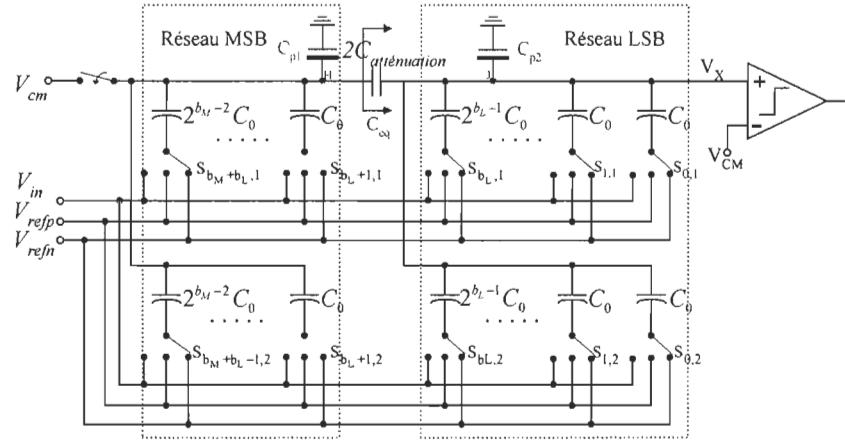

| Figure 3.25 : | C-CNA basé sur un réseau en série de capacités fractionné en ( $bM + bL$ ) (Tiré de [YAN08]).                                                                                        | 38 |

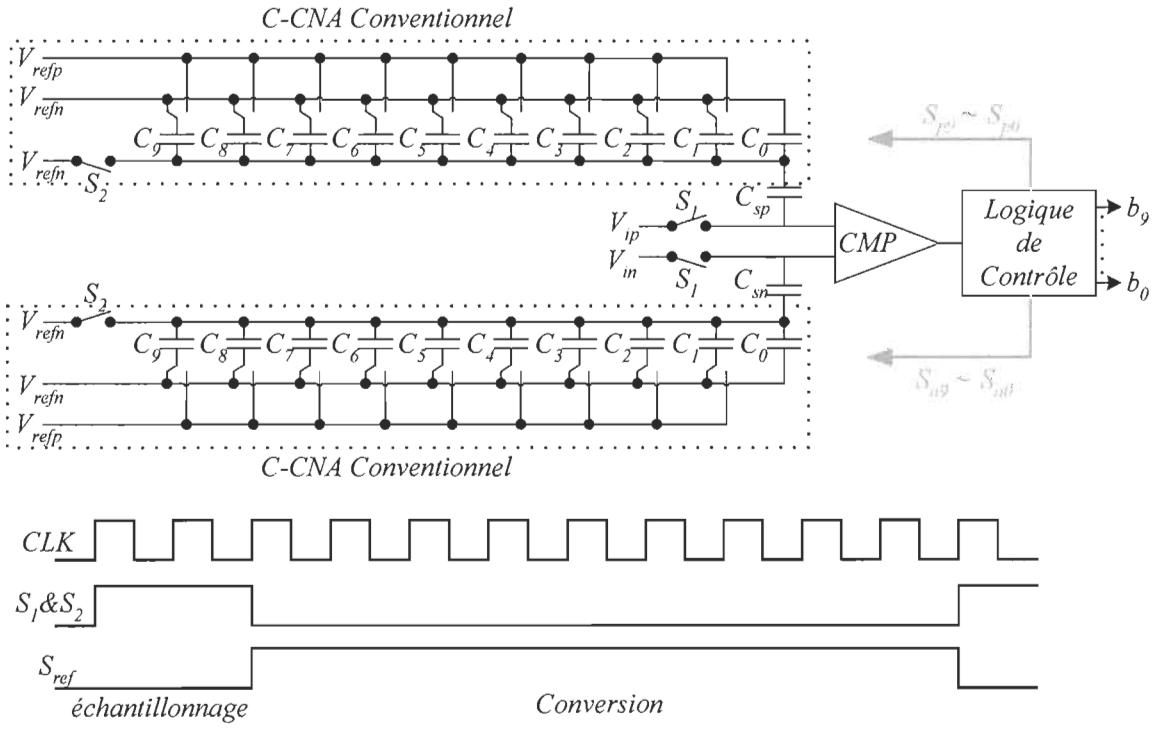

| Figure 3.26 : | Schéma bloc du C-CNA à basse capacité d'entrée et son diagramme de temps (Tiré de [GUA09]).                                                                                          | 39 |

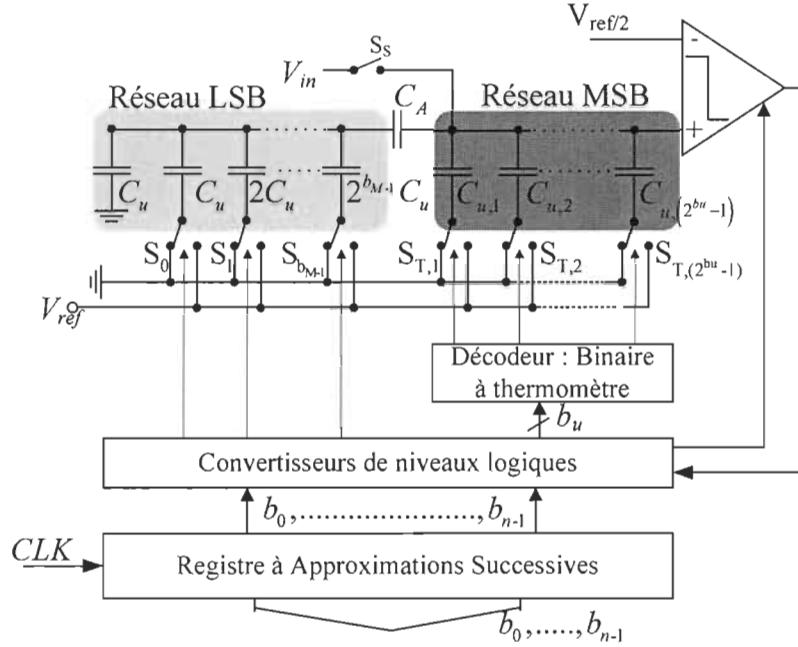

| Figure 3.27 : | Schématique d'un CAN-AS basé le C-CNA (Tiré de [LOT09]).                                                                                                                             | 40 |

| Figure 3.28 : | Convertisseur de niveau logique (Tiré de [LOT09]).                                                                                                                                   | 41 |

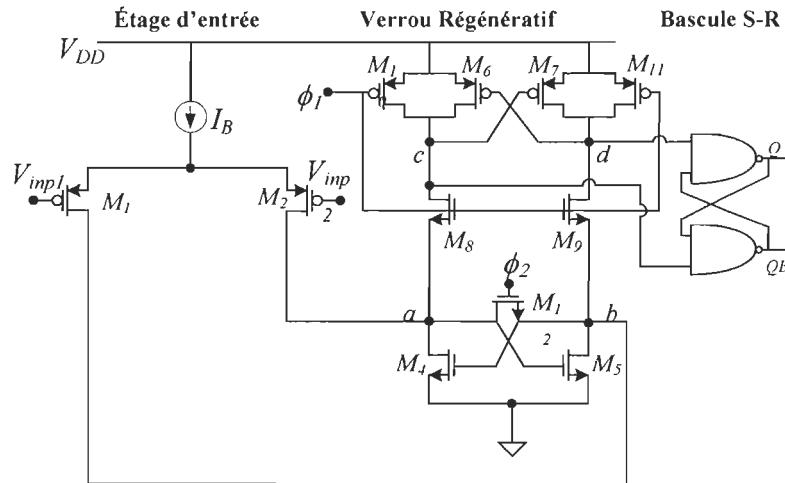

| Figure 4.1 :  | Schématique du comparateur CMOS (Tiré de [YIN92]).                                                                                                                                   | 46 |

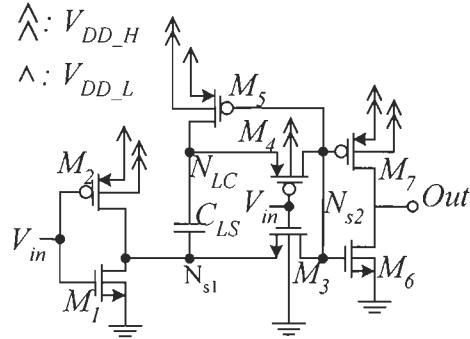

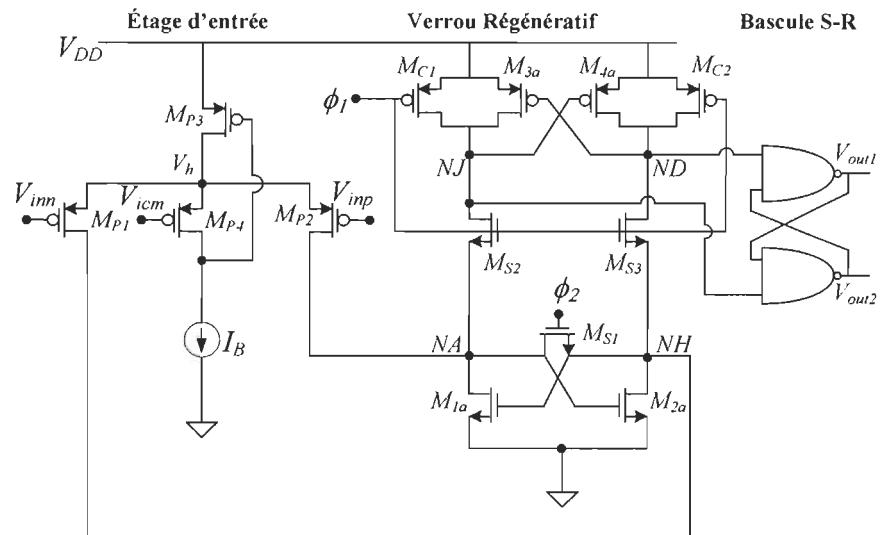

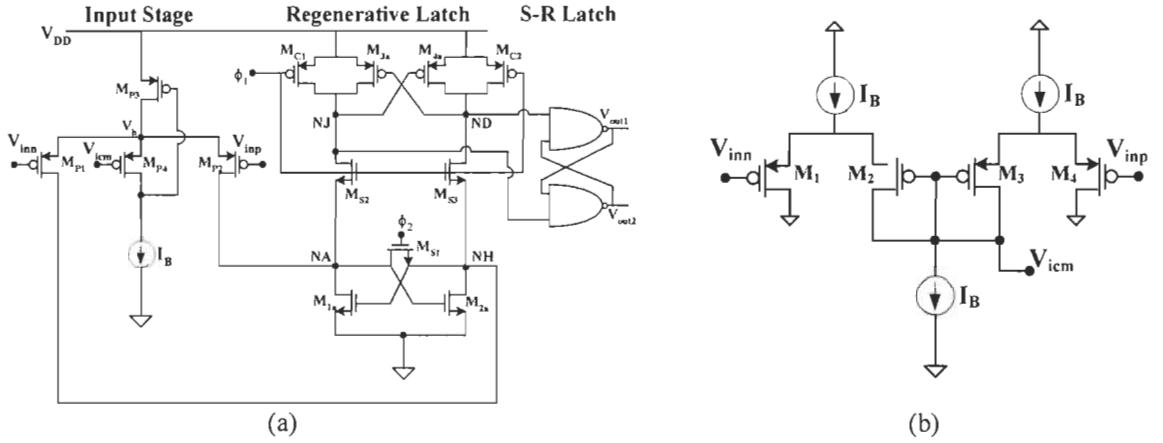

| Figure 4.2 :  | Schématique du comparateur dynamique proposé utilisant la cellule FVF.                                                                                                               | 46 |

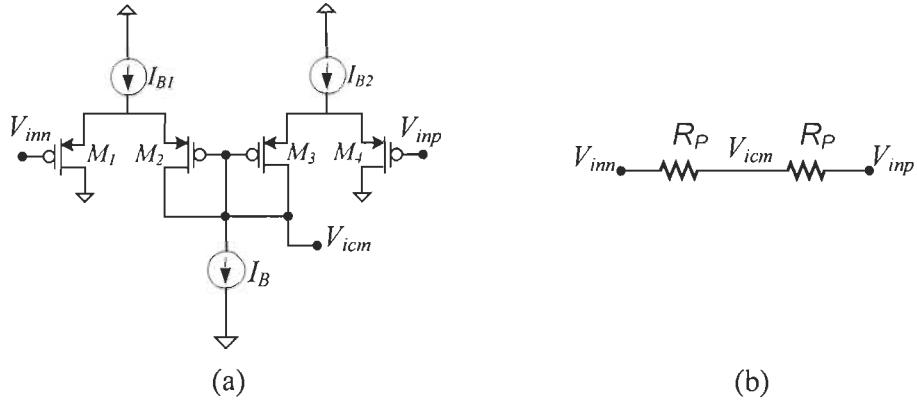

| Figure 4.3 :  | Schématique d'un circuit de détection en mode commun: (a) basé sur des transistors CMOS et (b) basé sur deux résistances en série.                                                   | 49 |

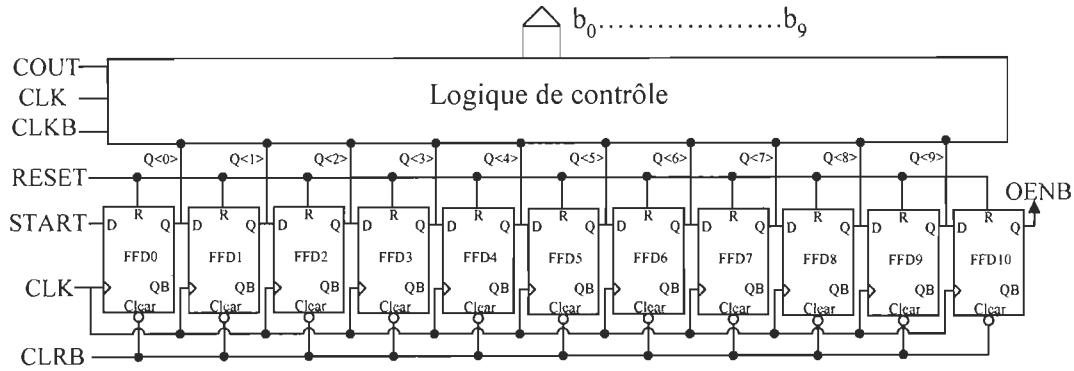

| Figure 4.4 :  | Schéma bloc du circuit du RAS.                                                                                                                                                       | 56 |

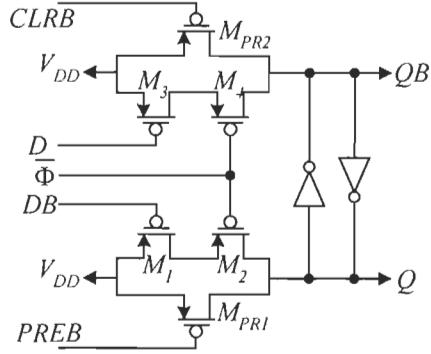

| Figure 4.5 :  | Schématique du Verrou utilisé dans le RAS.                                                                                                                                           | 57 |

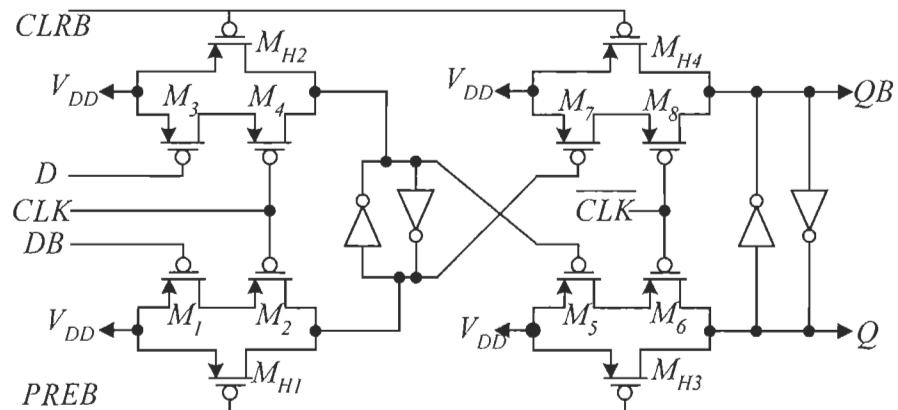

| Figure 4.6 :  | Schématique de la bascule D utilisée dans le RAS.                                                                                                                                    | 57 |

| Figure 4.7 :  | Schéma bloc d'un CNA 8 bits à structure R-2R.                                                                                                                                        | 59 |

| Figure 4.8 :  | Schéma bloc d'un CNA conventionnel à 10 bits.                                                                                                                                        | 61 |

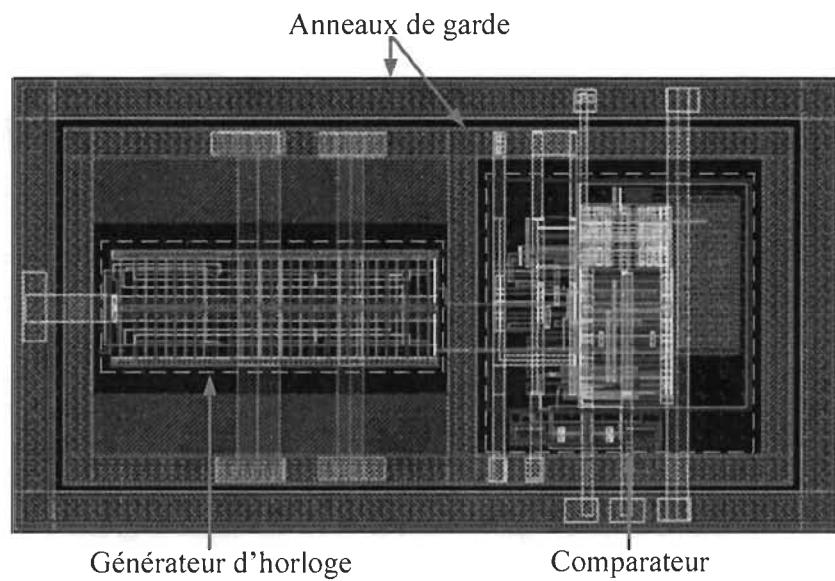

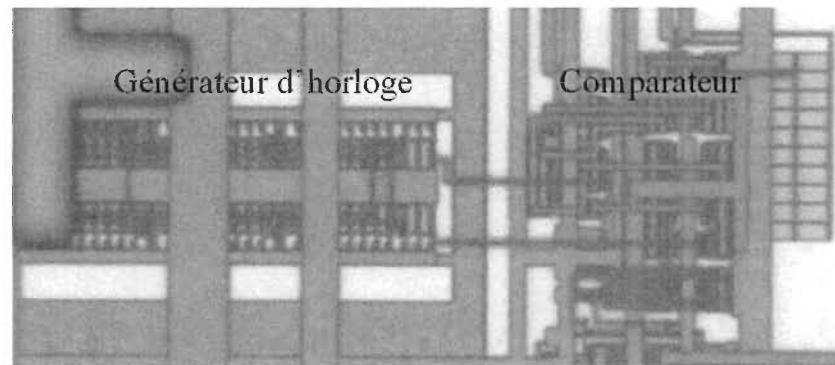

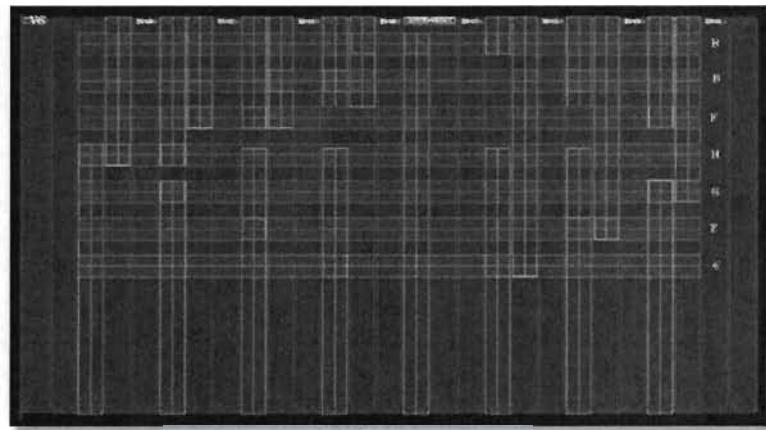

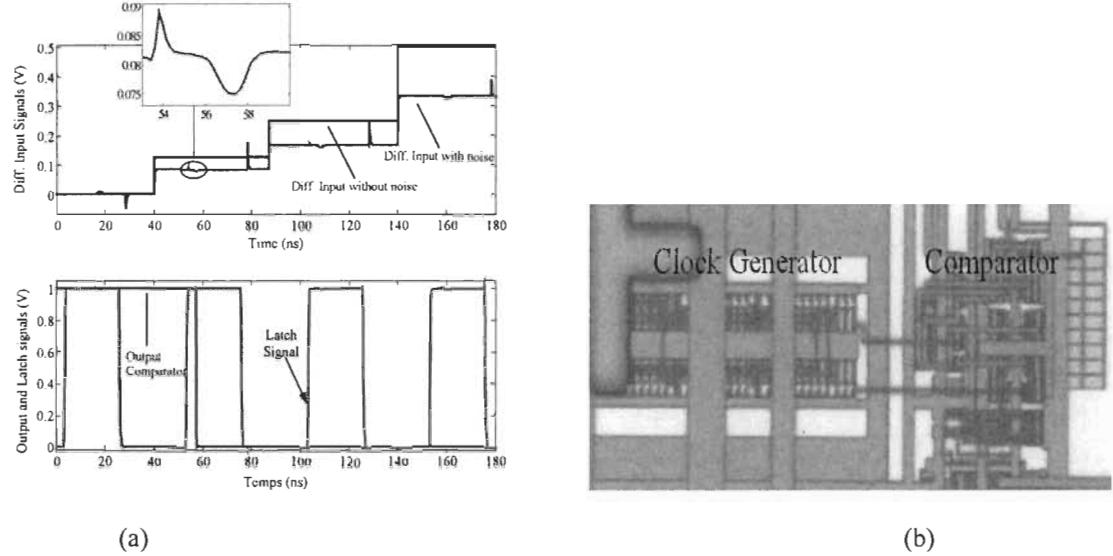

| Figure 5.1 :  | Dessin de masques du comparateur et du générateur d'horloge.                                                                                                                         | 67 |

| Figure 5.2 :  | Microphotographie du comparateur et générateur d'horloge.                                                                                                                            | 67 |

| Figure 5.3 :  | Dessin des masques du CNA de type R-2R à 8 bits présenté à la figure 4.6.                                                                                                            | 69 |

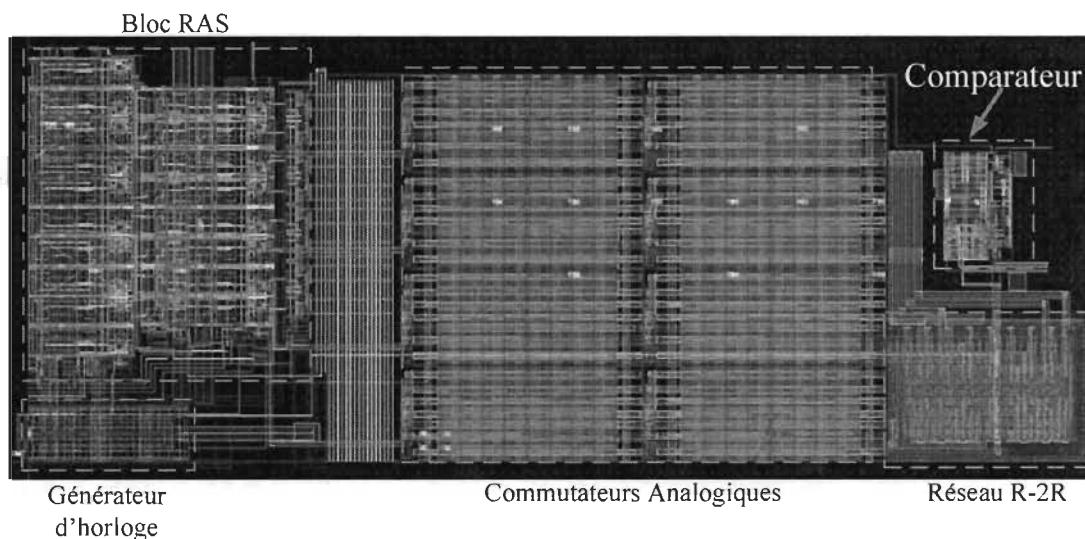

| Figure 5.4 :  | Dessin des masques du CAN-AS à 8 bits de type R-2R.                                                                                                                                  | 69 |

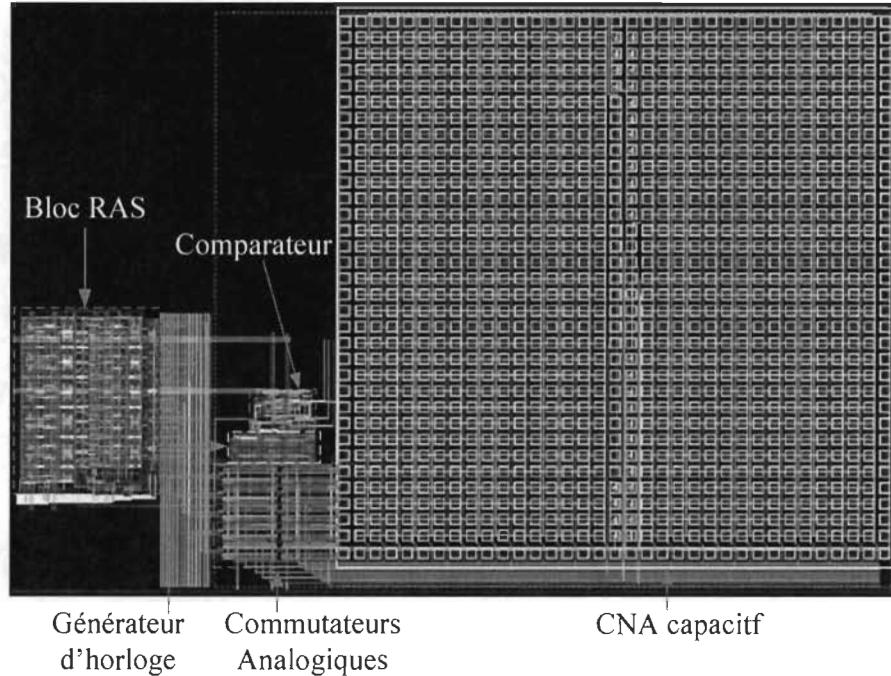

| Figure 5.5 :  | Plan du dessin des masques du réseau de capacités.                                                                                                                                   | 71 |

| Figure 5.6 :  | Dessin des masques du CAN-AS à 10 bits basé sur un CNA à capacités pondérées en binaire tel que présenté à la figure 4.8.                                                            | 73 |

|               |                                                                                                                                                                                                                                                             |    |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

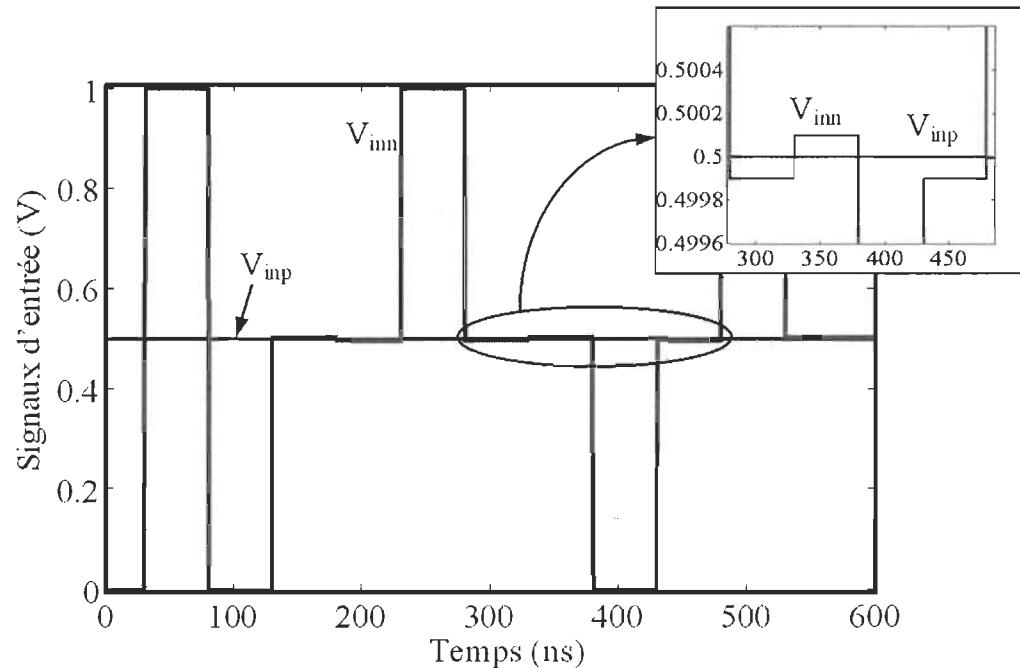

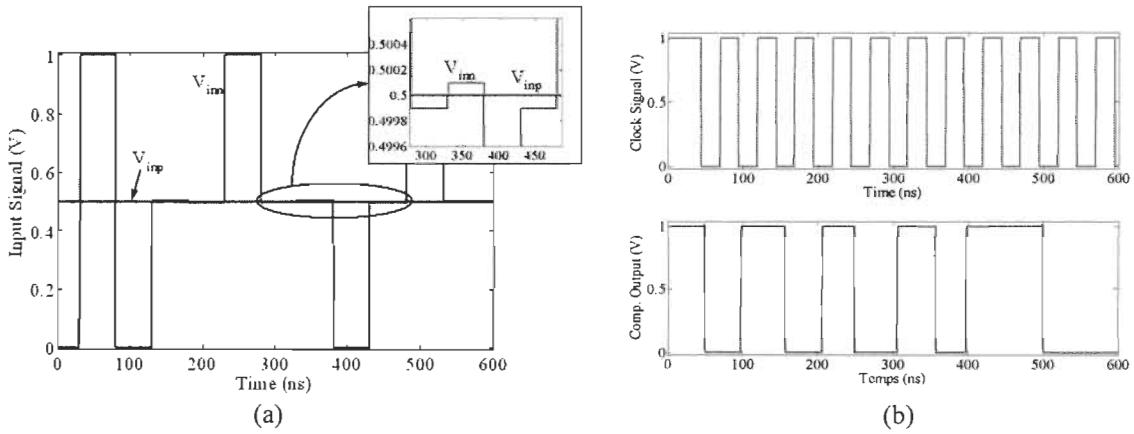

| Figure 5.7 :  | Signaux appliqués à l'entrée du comparateur: Un signal dynamique d'amplitude 1 V crête à crête comparé et un signal de référence fixé à la tension en mode commun, soit 0.5 V.                                                                              | 74 |

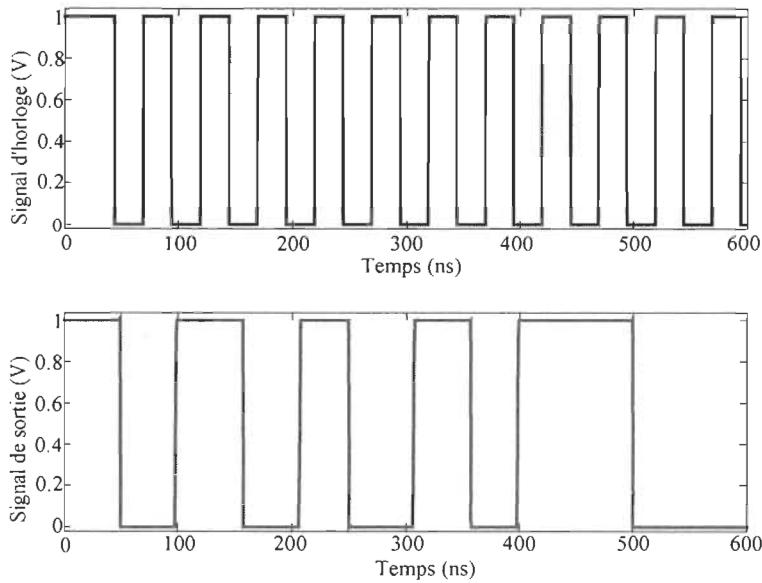

| Figure 5.8 :  | Signal d'horloge à 20 MHz et signal de sortie du comparateur simulé.                                                                                                                                                                                        | 75 |

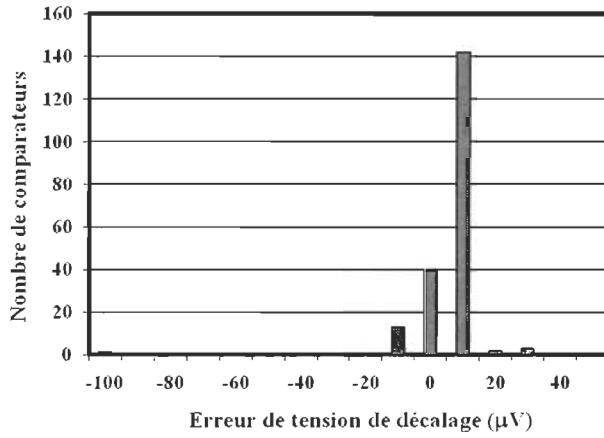

| Figure 5.9 :  | Histogramme de l'erreur de tension de décalage du comparateur.                                                                                                                                                                                              | 75 |

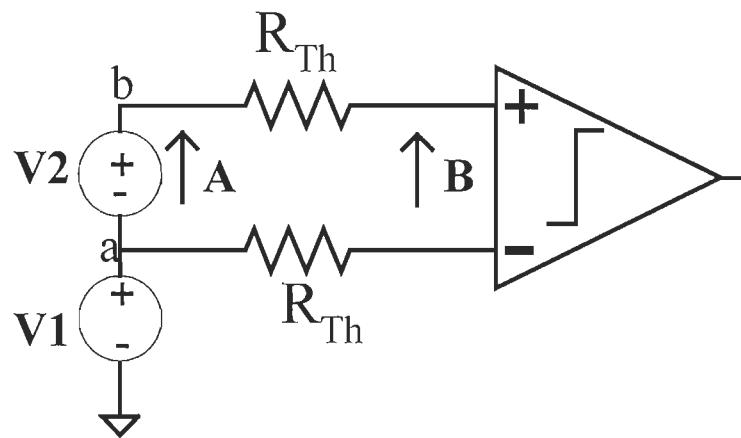

| Figure 5.10 : | Circuit d'évaluation du bruit de rebond (Tiré de [FIG06]).                                                                                                                                                                                                  | 76 |

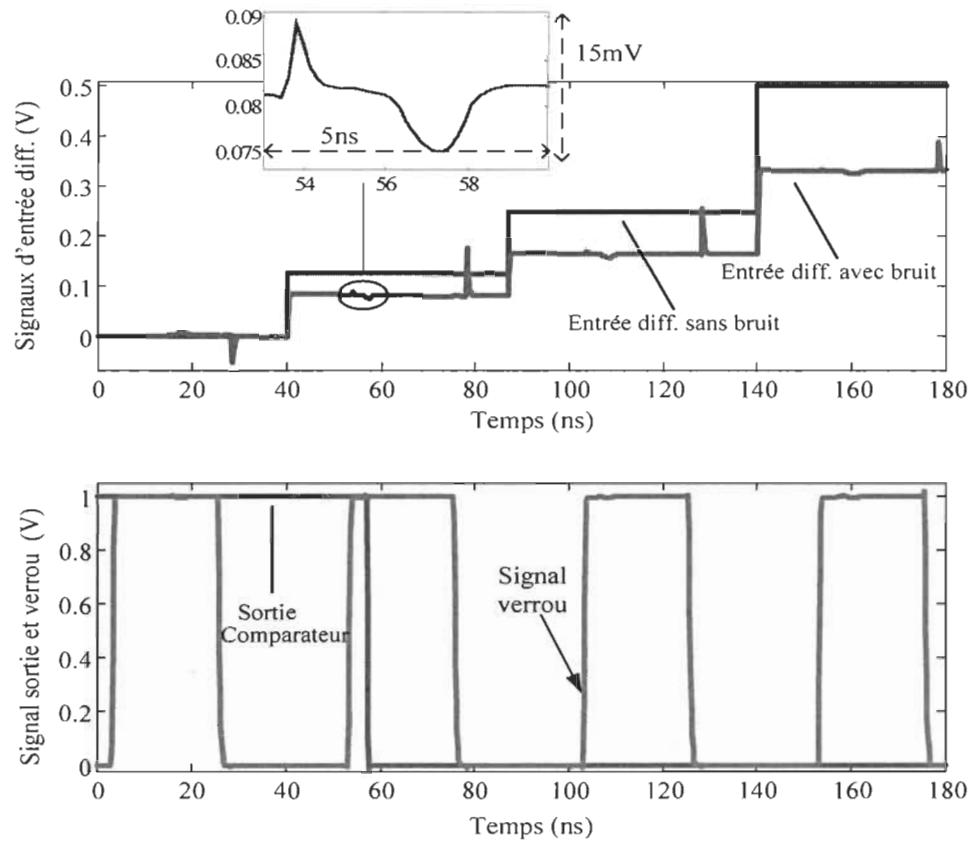

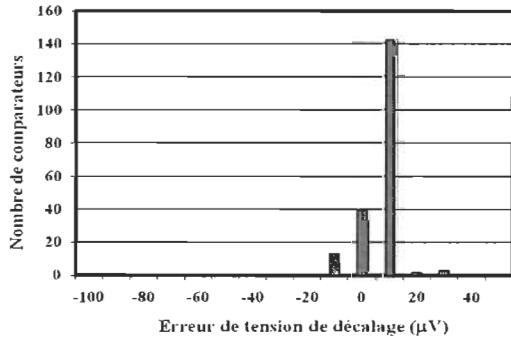

| Figure 5.11 : | Impact du bruit de rebond sur la performance du comparateur.                                                                                                                                                                                                | 77 |

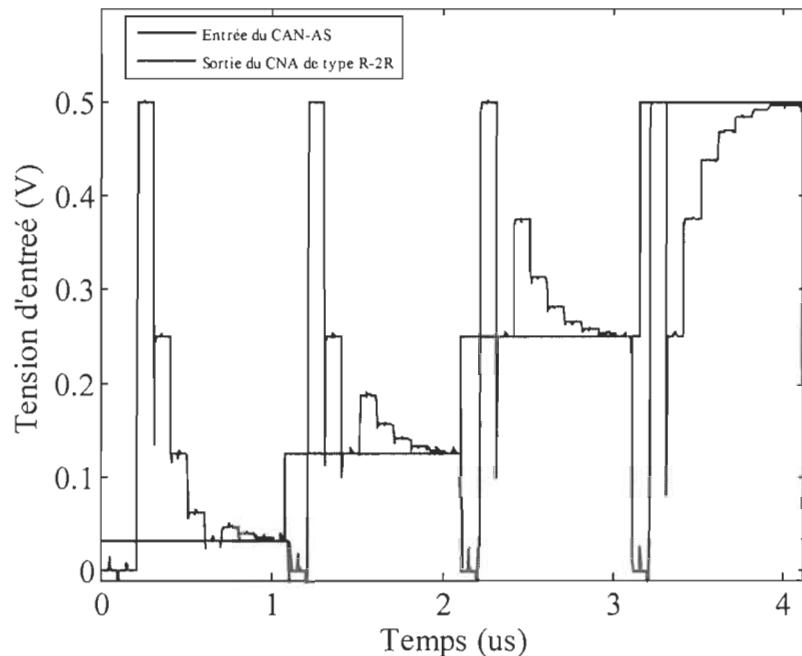

| Figure 5.12 : | Simulation du CAN à 8 bits de type R-2R (fig. 5.4) pour quatre conversions sous une fréquence d'horloge de 10 MHz (Taux de sortie à 1.25 MS/s).                                                                                                             | 78 |

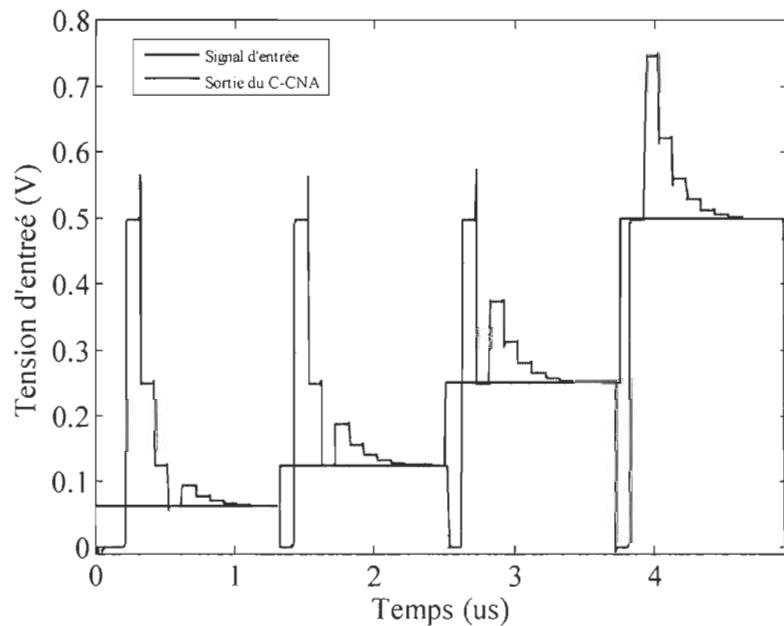

| Figure 5.13 : | Simulation du CAN-AS à 10 bits basé sur un C-CNA (fig. 5.6) pour quatre conversions sous une fréquence d'horloge de 10 MHz (Taux de sortie à 1 MS/s).                                                                                                       | 79 |

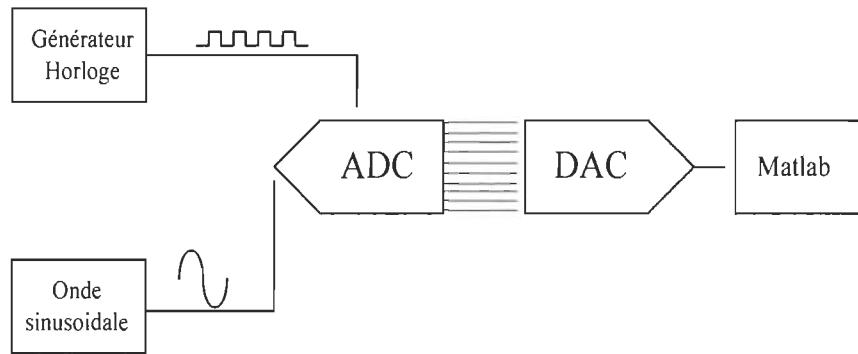

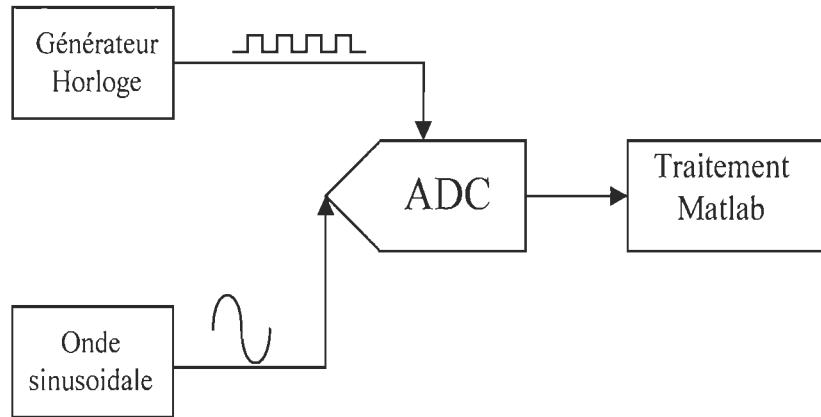

| Figure 5.14 : | Configuration de test permettant de reconstituer l'onde sinusoïdal d'entrée.                                                                                                                                                                                | 81 |

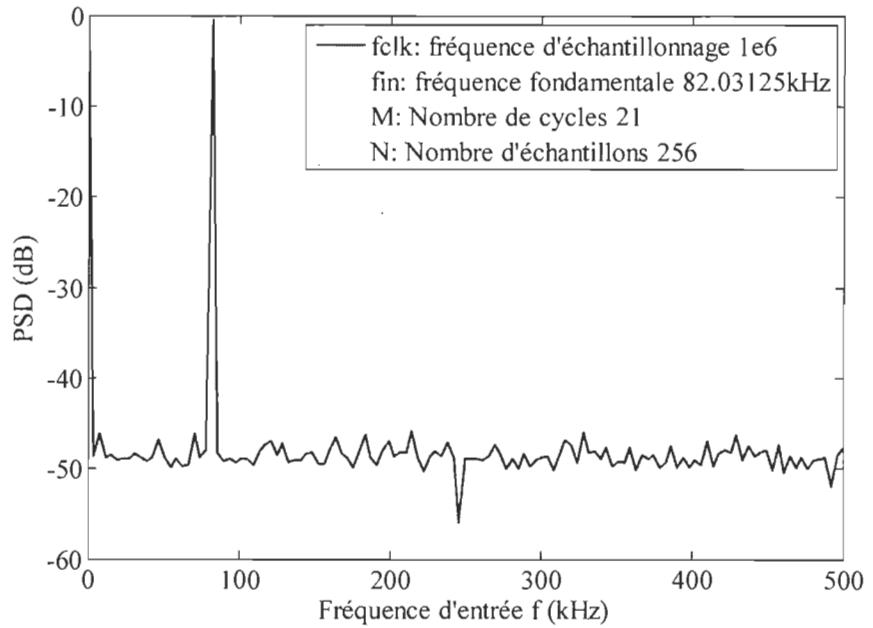

| Figure 5.15 : | Spectre de sortie simulé du CAN-AS à 8 bits de type R-2R (fig. 5.4) avec un signal sinusoïdal de fréquence 82.03125 kHz, une amplitude 300 mV crête à crête, un signal d'horloge de 1 MHz et sous une tension d'alimentation VDD= 1 V.                      | 82 |

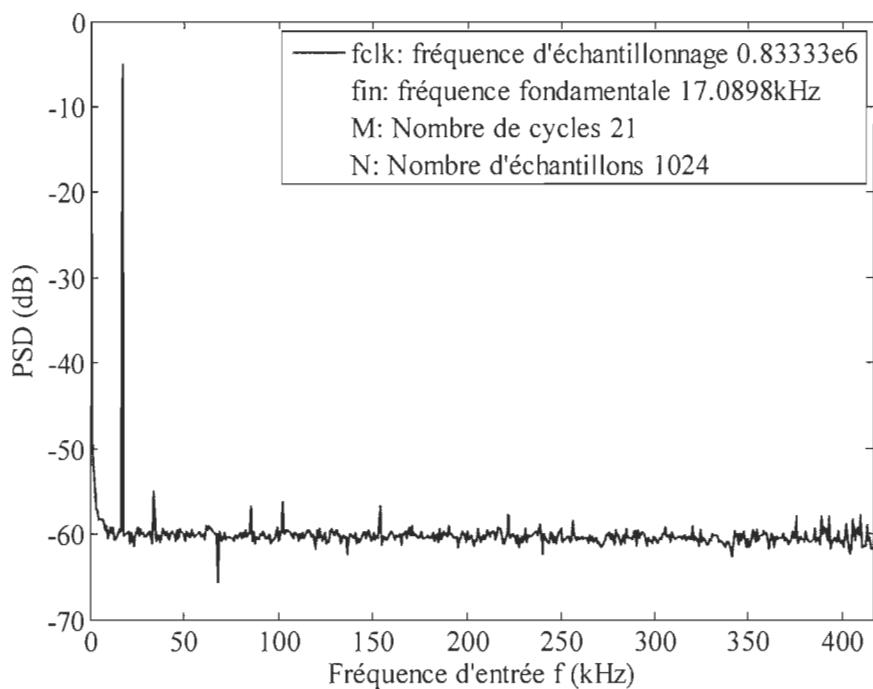

| Figure 5.16 : | Densité de sortie simulée du CAN-AS à 10 bits basé sur un C-CNA (fig. 5.6) avec un signal sinusoïdal de fréquence 17.08984375 kHz en entrée.                                                                                                                | 83 |

| Figure 5.17 : | Schéma bloc de la configuration de test utilisé pour évaluer les paramètres statiques.                                                                                                                                                                      | 85 |

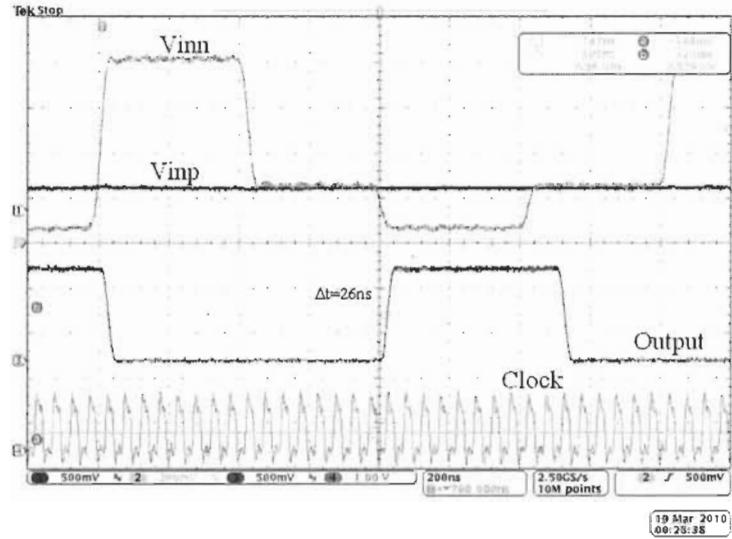

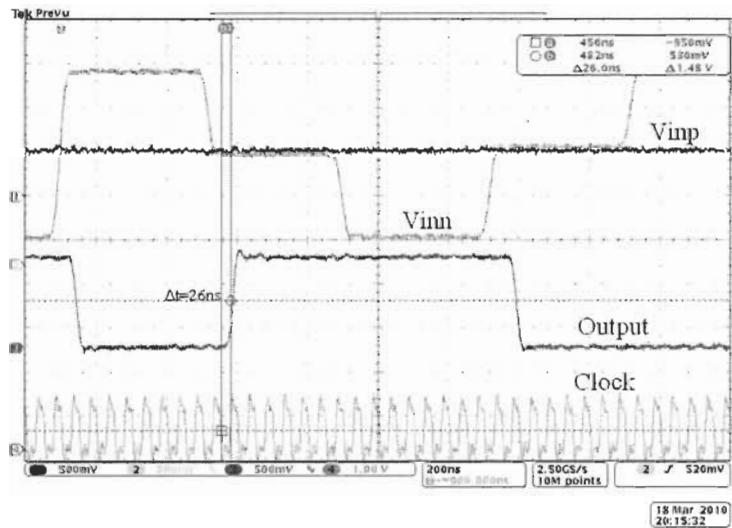

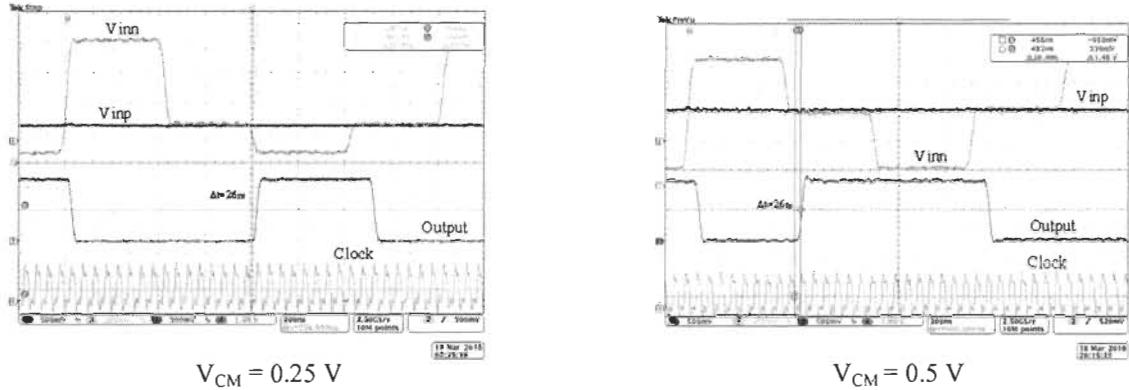

| Figure 5.18 : | Résultats des mesures du comparateur: Un signal d'entrée avec 1 Vpp, suivi d'une entrée inversée d'environ 0.245 mV, avec un niveau de référence en mode commun établi à 0.25 V et 0.5 V dans chaque régime d'opération. Le signal d'horloge est de 20 MHz. | 87 |

## ***LISTE DES TABLEAUX***

|               |                                                                                                                       |    |

|---------------|-----------------------------------------------------------------------------------------------------------------------|----|

| Tableau 3.1 : | Résumé de quelques métriques de performances des CAN-AS rapportés dans la littérature.....                            | 43 |

| Tableau 4.1:  | Dimensions des transistors utilisés dans le comparateur de la figure 4.2. ....                                        | 47 |

| Tableau 4.2:  | Dimensions des transistors utilisés dans le circuit de la figure 4.5 .....                                            | 58 |

| Tableau 4.3:  | Dimensions des transistors utilisés dans le le circuit de la figure 4.6 .....                                         | 58 |

| Tableau 4.4:  | Estimation des valeurs minimales de C0 en fonction de la résolution du CAN-AS telle proposée par Baker [BAK05]. ..... | 62 |

| Tableau 5.1 : | Résumé des performances du CAN-AS à 8 bits de type R-2R .....                                                         | 82 |

| Tableau 5.2 : | Résumé des performances du CAN-AS à 10 bits de type capacitif.....                                                    | 84 |

| Tableau 5.3:  | Comparaison du CAN-AS proposé avec certains travaux présentés dans la littérature....                                 | 86 |

## ***LISTE DES ABRÉVIATIONS***

|        |                                                                                         |

|--------|-----------------------------------------------------------------------------------------|

| AC     | Alternative current (courant alternatif)                                                |

| amp-op | Amplificateur opérationnel                                                              |

| A/N    | Analogique à numérique                                                                  |

| AS     | Approximations successives                                                              |

| BSIM   | Berkeley Short-channel IGFET Model                                                      |

| CAO    | Conception assistée par ordinateur                                                      |

| CAN    | Convertisseur analogique à numérique                                                    |

| C-CNA  | Convertisseur numérique analogique capacitif                                            |

| CAN-AS | Convertisseur analogique à numérique à approximations successives                       |

| CFS    | Capacité fractionnées en série                                                          |

| CFPB   | Capacités fragmentées pondérées en binaire                                              |

| CMOS   | Complementary Metal Oxide Semiconductor (Oxyde de métal semi-conducteur complémentaire) |

| CNA    | Convertisseur analogique numérique                                                      |

| DC     | Direct current (courant direct)                                                         |

| DNL    | Differential non-linearity (Non-linéarité différentielle)                               |

| E/B    | Échantillonneur Bloqueur                                                                |

| ENOB   | Effective number of bits (nombre effectif de bits)                                      |

| FFT    | Fast Fourier Transform (Transformée de Fourier Rapide)                                  |

| FVF    | Flipped Voltage Follower (Suiveur de tension inversée)                                  |

| GEMC   | Gamme d'entrée en mode commun                                                           |

| INL    | Integral non-linearity (Non-linéarité intégrale)                                        |

| LSB    | Least significant bit (Bit le moins significatif)                                       |

| MSB    | Most significant byte (Bit le plus significatif)                                        |

| RAS    | Registre à approximations successives                                                   |

|      |                                               |

|------|-----------------------------------------------|

| S-R  | Set-Reset (Activer-réinitialier)              |

| RMS  | Root means square (Valeur efficace)           |

| S/B  | Rapport signal sur bruit                      |

| TSPC | True Single Phase Clock Logic                 |

| TSMC | Taiwan Semiconductor Manufactured corporation |

| Tt   | Tension à temps                               |

| SCF  | Série de capacités fractionnées               |

| CMC  | Canadian Microelectronics Corporation         |

## ***LISTE DES SYMBOLES***

|                    |                                                      |

|--------------------|------------------------------------------------------|

| A                  | Ampère                                               |

| CLK                | Signal d'horloge                                     |

| F <sub>s</sub>     | Fréquence d'Échantillonnage                          |

| C <sub>H</sub>     | Capacité de maintien                                 |

| b                  | bits                                                 |

| dB                 | décibel                                              |

| fF                 | femto- Farad, capacité                               |

| F <sub>s</sub>     | Fréquence d'Échantillonnage                          |

| I <sub>B</sub>     | Courant de polarisation                              |

| gm                 | Transconductance                                     |

| m                  | mètre                                                |

| n                  | Nombre de bits                                       |

| R                  | Résistance                                           |

| R <sub>ON</sub>    | Resistance de commutation du transistor              |

| μm                 | micro-mètre                                          |

| V <sub>in</sub>    | Signal d'entrée analogique                           |

| V <sub>HAI</sub>   | Signal de sortie du CNA                              |

| V <sub>MID</sub>   | Signal de mode commun                                |

| V <sub>FS</sub>    | Tension pleine échelle                               |

| V <sub>ref</sub>   | Tension de référence                                 |

| V <sub>DD</sub>    | Tension d'alimentation                               |

| V <sub>FS</sub>    | Tension pleine échelle                               |

| V <sub>icm</sub>   | Tension en mode commun                               |

| V <sub>Dssat</sub> | Tension efficace (overdrive voltage) d'un transistor |

| V <sub>DS</sub>    | Tension drain-source d'un transistor                 |

| Φ <sub>b12</sub>   | Signal à niveau logique doublé                       |

|          |                        |

|----------|------------------------|

| W        | Largeur du transistor  |

| L        | Longueur du transistor |

| M        | Facteur multiplicateur |

| $\Omega$ | Ohm, résistance        |

| $\sigma$ | Sigma                  |

## ***TABLE DES MATIÈRES***

|                                                                                          |      |

|------------------------------------------------------------------------------------------|------|

| RÉSUMÉ .....                                                                             | v    |

| LISTE DES FIGURES .....                                                                  | VII  |

| LISTE DES TABLEAUX .....                                                                 | X    |

| LISTE DES ABRÉVIATIONS .....                                                             | XI   |

| LISTE DES SYMBOLES .....                                                                 | XIII |

| TABLE DES MATIÈRES .....                                                                 | XV   |

| CHAPITRE 1 .....                                                                         | 1    |

| INTRODUCTION .....                                                                       | 1    |

| 1.1 MOTIVATION.....                                                                      | 1    |

| 1.2 OBJECTIFS DE RECHERCHE ET MÉTHODOLOGIE .....                                         | 2    |

| 1.3 ORGANISATION DU MÉMOIRE .....                                                        | 3    |

| CHAPITRE 2.....                                                                          | 4    |

| PRINCIPE DE FONCTIONNEMENT DES CONVERTISSEURS À APPROXIMATIONS SUCCESSIVES .....         | 4    |

| 2.1 MODE D'OPÉRATION DU CAN À APPROXIMATIONS SUCCESSIVES .....                           | 4    |

| 2.2 IMPACT DES MÉTRIQUES DE PERFORMANCES STATIQUES SUR UNE ARCHITECTURE DU CAN-AS.....   | 8    |

| 2.2.1 <i>L'ERREUR DE TENSION DE DÉCALAGE ET DE GAIN</i> .....                            | 8    |

| 2.2.2 <i>ERREUR DE NON-LINÉARITÉ DIFFÉRENTIELLE</i> .....                                | 10   |

| 2.2.3 <i>ERREUR DE NON-LINÉARITÉ INTÉGRALE</i> .....                                     | 11   |

| 2.3 IMPACT DES MÉTRIQUES DE PERFORMANCES DYNAMIQUES SUR UNE ARCHITECTURE DU CAN-AS ..... | 12   |

| 2.3.1 <i>IMPACT DU RAPPORT SIGNAL SUR BRUIT DANS UN CAN-AS</i> .....                     | 12   |

|                                                    |                                                                                                    |    |

|----------------------------------------------------|----------------------------------------------------------------------------------------------------|----|

| 2.3.2                                              | <i>AUTRES PARAMÈTRES DYNAMIQUES ASSOCIÉS AU CAN-AS .....</i>                                       | 13 |

| 2.3.3                                              | <i>IMPACTS LIÉS AU RÉGULATEUR DE TENSION.....</i>                                                  | 13 |

| CHAPITRE 3.....                                    |                                                                                                    | 15 |

| REVUE DE LITTÉRATURE SUR LES CAN-AS .....          |                                                                                                    | 15 |

| 3.1                                                | CAN-AS BASÉ SUR LES CNA DE TYPE R-2R .....                                                         | 15 |

| 3.2                                                | CAN-AS BASÉ SUR UN CNA À DIVISEUR DE COURANT .....                                                 | 20 |

| 3.3                                                | CAN-AS BASÉ SUR UN CNA CAPACITIF .....                                                             | 22 |

| 3.4                                                | RÉSUMÉ DES TRAVAUX PRÉSENTÉS DANS LA LITTÉRATURE : .....                                           | 42 |

| CHAPITRE 4.....                                    |                                                                                                    | 44 |

| PROPOSITION D'UN CAN-AS CMOS À BASSE TENSION ..... |                                                                                                    | 44 |

| 4.1                                                | TECHNIQUE DE CONCEPTION D'UN COMPARATEUR ANALOGIQUE CMOS À BASSE TENSION ET À BASSE PUISSANCE..... | 44 |

| 4.1.1                                              | <i>COMPARATEUR TENSION BASÉ SUR LA CELLULE FVF.....</i>                                            | 45 |

| 4.1.1.1                                            | <i>ÉTAGE D'ENTRÉE DIFFÉRENTIELLE DE CLASSE AB.....</i>                                             | 47 |

| 4.1.1.2                                            | <i>VERROU RÉGÉNÉRATIF .....</i>                                                                    | 50 |

| 4.1.1.3                                            | <i>CONTRAINTE DE CONCEPTION ET ANALYSE DES PERFORMANCES .....</i>                                  | 51 |

| 4.2                                                | TECHNIQUES DE CONCEPTION À BASSE TENSION D'UN CAN À APPROXIMATION SUCCESSIVE.....                  | 54 |

| 4.2.1                                              | <i>CONCEPTION D'UN ÉCHANTILLONNEUR-BLOQUEUR À BASSE TENSION ET BASSE PUISSANCE .....</i>           | 54 |

| 4.2.2                                              | <i>CONCEPTION D'UN COMPARATEUR À BASSE TENSION ET BASSE PUISSANCE ....</i>                         | 55 |

| 4.2.3                                              | <i>CONCEPTION DU REGISTRE À APPROXIMATION SUCCESSIVE .....</i>                                     | 55 |

| 4.2.4                                              | <i>CONVERTISSEUR NUMÉRIQUE ANALOGIQUE DÉDIÉ AU CAN-AS .....</i>                                    | 58 |

| 4.2.4.1                                            | <i>CNA BASÉ SUR LE RÉSEAU R-2R EN MODE TENSION.....</i>                                            | 59 |

| 4.2.4.2                                            | <i>CNA À RÉSEAU DE CAPACITÉS PONDÉRÉES EN BINAIRE .....</i>                                        | 60 |

| 4.2.5                                              | <i>TECHNIQUE DE CONCEPTION DU RÉSEAU DE COMMUTATEURS .....</i>                                     | 63 |

|                                                                                                                       |    |

|-----------------------------------------------------------------------------------------------------------------------|----|

| CHAPITRE 5.....                                                                                                       | 65 |

| RÉSULTATS ET DISCUSSION .....                                                                                         | 65 |

| 5.1 ENVIRONNEMENT DE CONCEPTION ET TECHNOLOGIE UTILISÉES .....                                                        | 65 |

| 5.2 DESSIN DE MASQUES .....                                                                                           | 66 |

| 5.2.1 <i>RÉALISATION DU DESSIN DE MASQUE DU COMPARATEUR BASÉ SUR LA CELLULE FVF .....</i>                             | 66 |

| 5.2.2 <i>RÉALISATION DU DESSIN DE MASQUES D 'UN CNA BASÉ SUR LE RÉSEAU R-2R</i>                                       | 68 |

| 5.2.3 <i>RÉALISATION DU DESSIN DE MASQUES DU CNA À CAPACITÉS PONDÉRÉES DE FAÇON BINAIRE .....</i>                     | 70 |

| 5.3 RÉSULTATS DE SIMULATION POST-DESSIN DES MASQUES.....                                                              | 73 |

| 5.3.1 <i>SIMULATION FONCTIONNELLE DU COMPARATEUR BASÉ SUR LA CELLULE "FLIPPED VOLTAGE FOLLOWER" .....</i>             | 73 |

| 5.3.2 <i>SIMULATION FONCTIONNELLE DU CAN-AS.....</i>                                                                  | 77 |

| 5.3.2.1 <i>MESURE DES PERFORMANCES DYNAMIQUES DU CAN-AS .....</i>                                                     | 80 |

| 5.3.2.2 <i>MESURE DES PERFORMANCES STATIQUES DU CAN-AS .....</i>                                                      | 84 |

| 5.3.4 <i>COMPARAISON DES PERFORMANCES DU CAN-AS.....</i>                                                              | 85 |

| 5.4 RESULTATS EXPERIMENTAUX DU COMPARATEUR .....                                                                      | 86 |

| CHAPITRE 6.....                                                                                                       | 89 |

| CONCLUSION ET DÉVÉLOPPEMENTS FUTURS.....                                                                              | 90 |

| 6.1 VUE D'ENSEMBLE DU PROJET ET DIFFICULTÉS RENCONTRÉES .....                                                         | 90 |

| 6.2 RECOMMANDATION POUR DES TRAVAUX FUTURS.....                                                                       | 91 |

| RÉFÉRENCES .....                                                                                                      | 92 |

| ANNEXES.....                                                                                                          | 97 |

| Low-Voltage, High-Speed CMOS Analog Latched Voltage Comparator using the<br>"Flipped Voltage Follower" as Input Stage |    |

# *Chapitre 1*

## ***INTRODUCTION***

### **1.1 Motivation**

Ces dernières années, beaucoup d'attentions ont été portées sur la réduction de la tension d'alimentation ainsi qu'à la dissipation de puissance dans les circuits intégrés CMOS analogiques et mixtes. Cette réduction, principalement dictée par le besoin croissant de dispositifs et d'accessoires microélectroniques portatifs, est en train d'amener les dispositifs CMOS au point de blocage. Il n'est pas question d'arrêter le développement des technologies CMOS, mais encore une fois, on se trouve devant une nécessité incontournable d'innovation.

Le transistor MOSFET est le composant le plus utilisé dans la conception des circuits électroniques, il offre une grande flexibilité avec sa couche de silicium qui est un bon semi-conducteur. Son principe de fonctionnement a permis jusqu'aujourd'hui d'atteindre l'échelle du micro et nanomètre. L'un des milieux à qui profite le plus cet avancement est le biomédical. Pour réduire la consommation d'énergie dans une application biomédicale, il faut réduire la tension d'alimentation tout en maintenant la vitesse de fonctionnement à un niveau acceptable. L'un des systèmes clés que l'on retrouve dans des applications biomédicales est le convertisseur analogique-numérique (A/N) et numérique-analogique (N/A).

Les convertisseurs analogiques numériques sont des composants essentiels qui assurent la communication entre les signaux analogiques externes et la puce électronique numérique. Ils ne doivent pas nuire à la précision même si le matériel dans lequel ils sont intégrés se compose de dispositifs très imparfaits. L'ensemble des éléments de base qui contribue de près ou de loin au fonctionnement d'un convertisseur A/N ou N/A, justifie

toutes les connaissances acquises au cours des vingt dernières années en matière de conception en électronique dédiée à contourner les contraintes et les défaillances inhérentes aux circuits intégrés et aux procédés.

Beaucoup d'efforts ont été mis dans la réduction de la tension d'alimentation et la consommation d'énergie des circuits mixtes. Cependant, la diminution de la tension d'alimentation n'est pas forcément un avantage dans la conception analogique puisqu'elle entraîne certaines limites à savoir; le bon fonctionnement des commutateurs analogiques, la réduction de la plage d'entrée du circuit et la complexité à faire opérer les transistors dans leur région optimale.

Face à tous ces défis, plusieurs architectures de circuits ont été développées pour réaliser des convertisseurs analogiques numériques à approximations successives (CAN-AS) qui peuvent fonctionner à basse tension d'alimentation. Dans ce chapitre, les objectifs de la recherche et la méthodologie sont traités dans la section 1.2 tandis que la section 1.3 présente un résumé sur l'organisation du mémoire.

## 1.2 Objectifs de recherche et méthodologie

Ce mémoire vise à proposer des solutions innovatrices de conception et de réalisation de convertisseurs A/N à approximations successives opérant à basse tension dans les procédés CMOS submicroniques standard. L'accent sera mis sur des solutions matérielles qui n'exigent aucune modification du procédé.

La démarche suivante sera mise en œuvre afin d'atteindre cet objectif:

- ◆ Présentation du principe de fonctionnement des CAN-AS.

- ◆ Revue de littérature sur les CAN-AS.

- ◆ Réalisation des différents blocs (Comparateur, convertisseur N/A à réseau de résistance et capacités, le circuit de mode commun, la logique de contrôle et un registre à décalage) qui entrent dans la conception des CAN-AS.

- ◆ Validation des résultats, analyse et discussion avec développement futur.

### **1.3     Organisation du mémoire**

Ce mémoire s'articule de la manière suivante :

Dans le chapitre 1, nous présentons les motivations liées au projet, la problématique et la méthodologie à suivre pour atteindre les objectifs qui ont été fixés.

Dans le chapitre 2, le principe de fonctionnement du CAN-AS est présenté de façon explicite. Les paramètres statiques et dynamiques qui caractérisent le convertisseur analogique numérique (CAN) y sont discutés, ainsi que leurs impacts sur la performance des circuits.

Dans le chapitre 3, nous passerons en revue la littérature sur les CAN-AS qui fonctionnent à basse alimentation et faible puissance. Une attention particulière est portée sur la technologie utilisée, les architectures de convertisseur numérique analogique (CNA) capacitatives (C-CNA) et les comparateurs.

La conception et la réalisation au niveau physique d'un convertisseur CAN-AS à 8 et 10 bits de résolution, opérant à basse tension et basse puissance sont présentées dans le chapitre 4. Nous présentons aussi leur principe de fonctionnement, leurs avantages et quelques limites. Une description explicite a été faite des éléments de base qui constituent ces convertisseurs. Un prototype expérimental du comparateur a été fabriqué, et les résultats des mesures sont présentés dans le chapitre 5. La simulation fonctionnelle du CAN y est également présentée ainsi que ses métriques de performances.

Le chapitre 6 présente la conclusion et les développements futurs de nos travaux.

## *Chapitre 2*

### ***PRINCIPE DE FONCTIONNEMENT DES CONVERTISSEURS À APPROXIMATIONS SUCCESSIVES***

Les convertisseurs analogiques numériques à approximations successives sont des composants électroniques qui transforment un signal analogique (p. ex. la voix) en un signal numérique codé sous forme binaire c.-à-d., 1 ou 0. Ils se distinguent des autres architectures de convertisseurs de par leur particularité à posséder à la fois une résolution moyenne, un taux de conversion moyen, une faible dissipation de puissance, une bonne précision et une faible demande en surface. Cette topologie de convertisseur est plus attractive dans les applications biomédicales et les appareils portatifs.

Tout au long de cette section, nous allons présenter de façon détaillée le mode de fonctionnement d'un CAN-AS et ses métriques de performances.

#### **2.1 Mode d'opération du CAN à approximations successives**

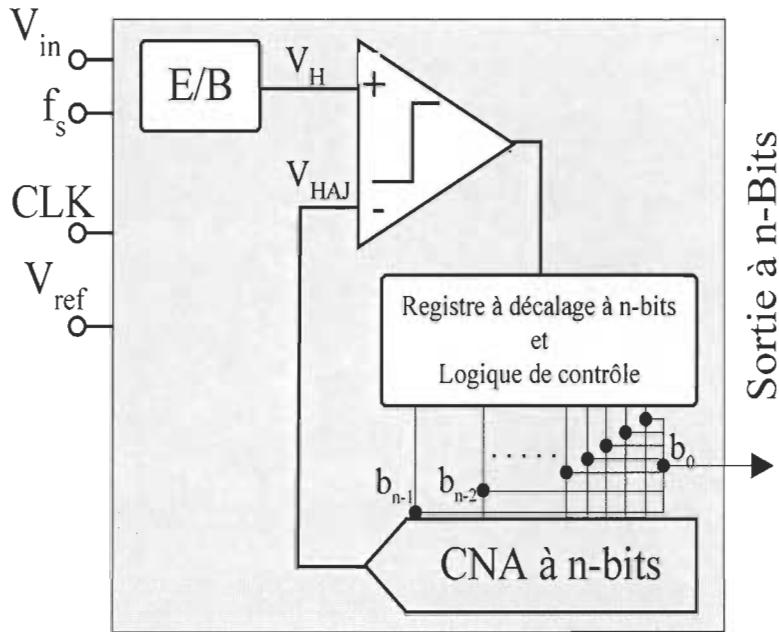

Pour une architecture qui rime avec simplicité, nous avons le CAN-AS dont le schéma bloc est décrit à la figure 2.1. Il est constitué d'un échantillonneur bloqueur (E/B), un comparateur, un registre à approximations successives, une logique de contrôle et un CNA. Cette topologie de circuit est très versatile, son mode d'opération est basé sur un algorithme de recherche binaire. Autrement dit, l'opération consiste à vérifier l'état de chaque bit issu de la logique numérique. Le résultat final de la conversion est récupéré au niveau du bloc numérique. L'une des particularités associées à cette architecture est que son taux de conversion est une fraction de sa fréquence d'horloge. Ceci étant dû à l'algorithme d'approximations successives [RAZ95].

Figure 2.1 : Schéma bloc d'un CAN à approximations successives.

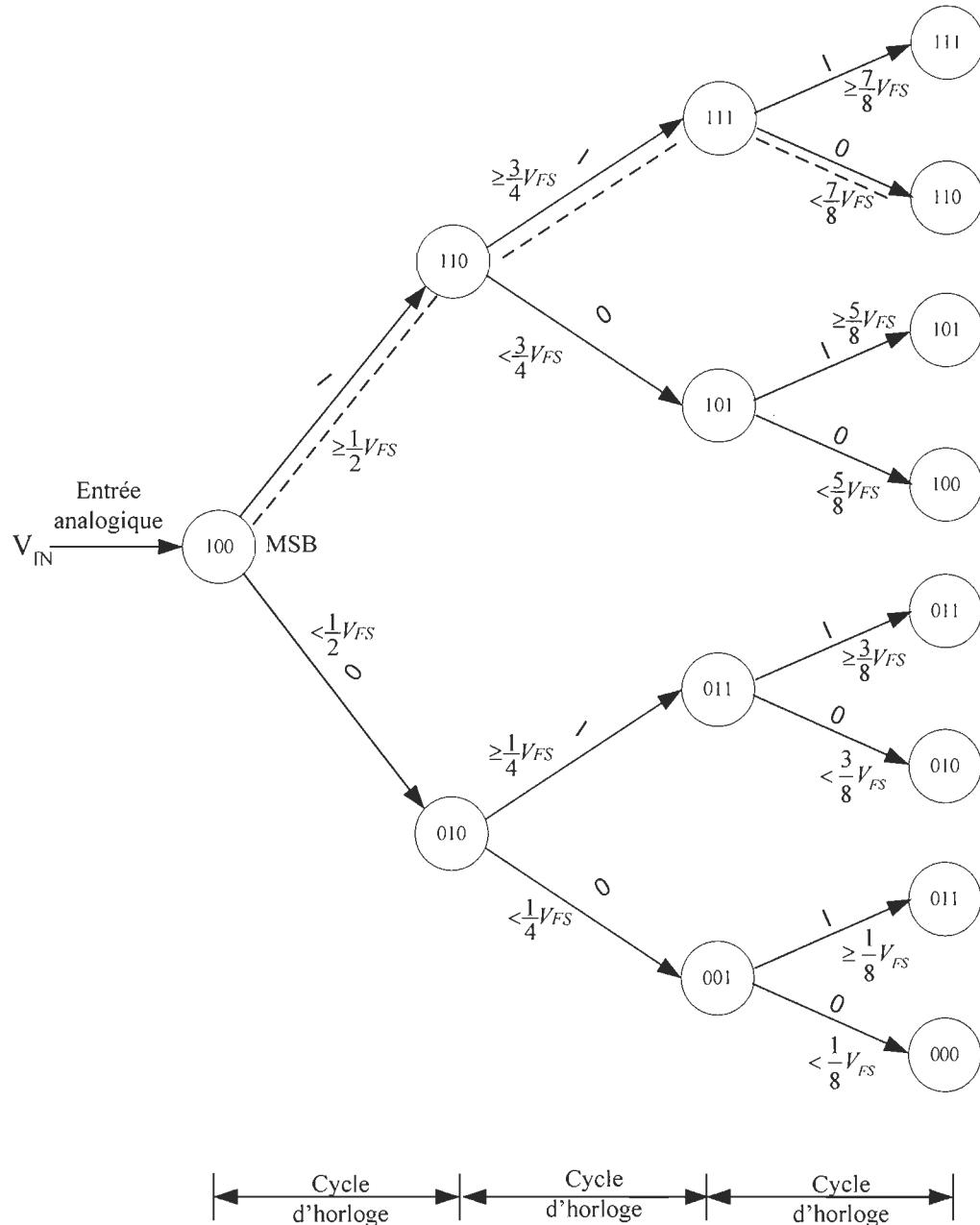

Bien qu'il existe plusieurs topologies au niveau circuiterie, le principe de fonctionnement reste le même. Le signal d'entrée analogique ( $V_{in}$ ) est échantillonné sur l'entrée positive ( $V_H$ ) du comparateur. Par la suite, l'algorithme de recherche binaire se met en marche. Le registre à décalage à  $n$  bits est fixé à mi-échelle (c.-à-d., 10<sup>n-1</sup>00 où le bit  $b_{n-1}$  est mis à 1). Ce code numérique est envoyé au convertisseur numérique analogique (CNA) et force sa tension de sortie ( $V_{HAJ}$ ) à  $\frac{1}{2} V_{ref}$  où  $V_{ref}$  est la tension de référence généralement fixé à  $V_{DD}$  (tension d'alimentation). Une comparaison est alors effectuée entre  $V_H$  et  $V_{HAJ}$  afin de déterminer si la tension à convertir ( $V_H$ ) est supérieure ou inférieure à la tension de sortie du CNA. Si  $V_H$  est supérieure à  $\frac{1}{2} V_{ref}$ , la sortie du comparateur est au niveau haut ou ‘1’ et l’état du bit  $b_{n-1}$  ou bit le plus significatif (*MSB – Must significant bit*) reste inchangé, soit ‘1’. Par contre, si  $V_H$  est inférieure à  $\frac{1}{2} V_{ref}$ , la sortie du comparateur est au niveau bas ou ‘0’ et le MSB est mis à ‘0’. À ce niveau, deux situations prévalent.

Advenant que la sortie du comparateur soit ‘1’, la logique de contrôle via le registre à décalage à n bits va fixer le bit  $b_{n-2}$  à 1 et les bits  $b_{n-3}$  à  $b_0$  sont mis à ‘0’. Pendant ce temps, le MSB reste à ‘1’ puisque son état a déjà été identifié. La sortie du CNA va maintenant être  $\frac{3}{4} V_{ref}$  et une nouvelle comparaison est ainsi effectuée entre  $V_H$  et  $\frac{3}{4} V_{ref}$ . Ensuite, dans le cas où la sortie du comparateur est de nouveau à ‘1’, le bit  $b_{n-1}$  reste inchangé et son état est donc identifié. La logique de contrôle via le registre à décalage va fixer le bit  $b_{n-3}$  à ‘1’ et les bits  $b_{n-4}$  à  $b_0$  sont mis à ‘0’. La nouvelle valeur de  $V_{H AJ}$  est  $\frac{7}{8} V_{ref}$  et une nouvelle comparaison est alors effectuée entre  $V_H$  et  $\frac{7}{8} V_{ref}$ .

Dans le cas où la sortie du comparateur est plutôt ‘0’, la logique de contrôle via le registre à décalage à n bits va d’abord remettre le MSB à zéro. Par la suite, le bit  $b_{n-2}$  est fixé à ‘1’ et les bits  $b_{n-3}$  à  $b_0$  sont mis à ‘0’. La sortie analogique du CNA va maintenant être à  $\frac{1}{4} V_{ref}$  et une nouvelle comparaison est ainsi effectuée entre  $V_H$  et  $\frac{1}{4} V_{ref}$  afin de déterminer l’état réel du bit  $b_{n-2}$ . En supposant que la sortie du comparateur est de nouveau à ‘0’, le bit  $b_{n-2}$  est remis à ‘0’ et son état est ainsi identifié. La logique de contrôle via le registre à décalage va fixer le bit  $b_{n-3}$  à ‘1’ et les bits  $b_{n-4}$  à  $b_0$  sont mis ‘0’. La valeur de la tension de sortie du CNA est maintenant égale à  $\frac{1}{8} V_{ref}$  et une nouvelle comparaison est alors effectuée entre  $V_H$  et  $\frac{1}{8} V_{ref}$ . On voit bien que l’identification d’un bit nécessite qu’on se fixe une hypothèse au préalable. En d’autres termes, c’est le principe d’approximation de façon subséquente.

Dépendamment que l’on soit dans l’une des situations établies ci-dessus, le processus va se répéter de la même manière jusqu’à ce que la tension de sortie ( $V_{H AJ}$ ) du CNA converge vers la valeur échantillonnée ( $V_H$ ). En d’autres termes, la conversion prend fin lorsque le bit  $b_0$  est identifié. L’algorithme de recherche binaire qu’utilise le CAN-AS est semblable à un arbre de partie dont chaque niveau correspond à un cycle d’horloge. Nous pouvons donc déduire que la conversion d’un mot de n bits requiert n coups d’horloge. Cependant, en fonction du concepteur, on peut ajouter un coup d’horloge pour l’initialisation et un autre coup d’horloge pour démarrer la conversion. La

figure 2.2 illustre le schéma bloc d'une recherche binaire sous forme d'un arbre de partie dans le cas d'un CAN-AS à trois (3) bits.

Figure 2.2: Arbre de recherche binaire d'un CAN-AS durant le processus d'identification du code 110.

## 2.2 Impact des métriques de performances statiques sur une architecture du CAN-AS

Les paramètres statiques qui caractérisent la performance des CAN-AS constituent l'ensemble d'erreurs qui affectent la précision du convertisseur quand il traite un signal continu. Plusieurs méthodes empiriques ont été développées afin d'évaluer ces paramètres. Nous avons la méthode de test basée sur l'histogramme d'une onde sinusoïdale et celle basée sur l'histogramme d'une rampe. Cependant, il est important de connaître les artefacts qui dégradent ces paramètres.

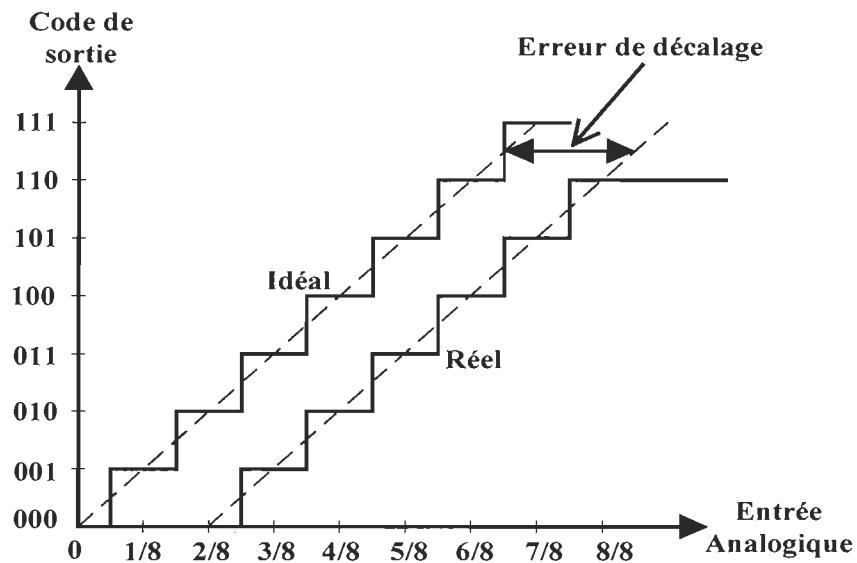

### 2.2.1 *L'erreur de tension de décalage et de gain*

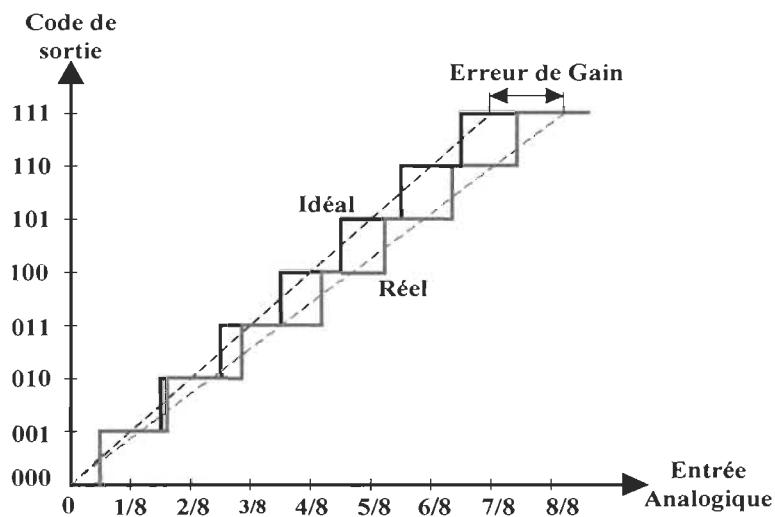

L'erreur de tension de décalage et l'erreur de gain sont des performances statiques qui peuvent être rencontrées dans tous les blocs constitutifs d'un CAN-AS. Elles peuvent être causées par le mésappariement entre les composants, la variation du gradient liée au courant, la variation de la tension de seuil et du procédé [BAK05]. Dans un CAN-AS, l'erreur de tension de décalage est associée au comparateur et au convertisseur numérique analogique, qui influencent fortement la précision d'une conversion et l'exactitude d'une résolution. Par exemple, un CAN-AS de 10 bits avec une erreur de tension de décalage égale à +10 mV, soit 10 LSB ( $10 \text{ mV} / [V_{FS} / 2^{10}]$ ) où  $V_{FS} = 1 \text{ V}$  (tension pleine échelle), ne pourra pas réaliser une résolution effective de 10 bits comme préalablement établi par ses caractéristiques.

Contrairement à l'erreur de tension, l'erreur de gain ou erreur pleine échelle est par définition la différence entre la pente de la droite longeant la fonction de transfert réelle du CAN et la pente de valeur 1 [BAK05]. Elle est mesurée sur la dernière transition de la fonction de transfert du CAN et s'exprime aussi en bit. Tout comme l'erreur de décalage, elle peut affecter la résolution du convertisseur. Cependant, on peut atténuer ou supprimer l'effet des ces erreurs à l'aide d'une simple calibration de la sortie du

convertisseur [BAK05]. Les figures 2.3 et 2.4 décrivent ces erreurs dans le cas d'un CAN à trois (3) bits.

Figure 2.3 : Fonction de transfert illustrant l'erreur de tension d'un CAN à 3 bits.

Figure 2.4 : Fonction de transfert illustrant l'erreur de gain d'un CAN à 3 bits.

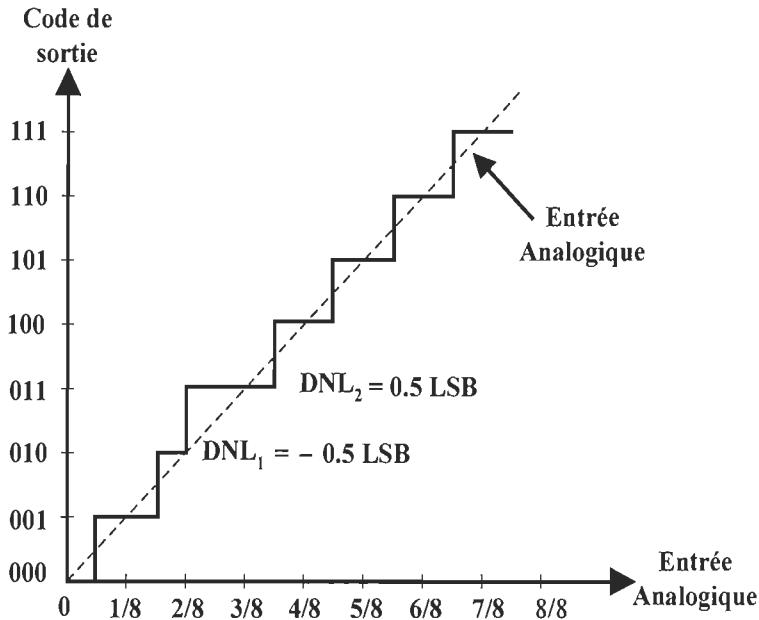

### 2.2.2 Erreur de non-linéarité différentielle

La non-linéarité différentielle (*DNL – Differential Non Linearity*) est la différence entre la largeur du palier réel dans la fonction de transfert et sa largeur idéale qui est 1 LSB par défaut [BAK05]. Ce paramètre est primordial dans le choix d'un CAN d'autant plus qu'il donne des informations sur la performance de ce dernier. Dans la littérature, il est rapporté que l'erreur de DNL doit être inférieure ou égale à  $\pm 0.5$  LSB afin de garantir une bonne linéarité et aucune absence de codes à la sortie du CAN. Un  $DNL < \pm 1$  LSB reste tolérable, mais ne garantit pas la présence de tous les codes [BAK05].

Les principaux facteurs qui affectent le paramètre de DNL sont: l'erreur de décalage au niveau du comparateur et du CNA, l'erreur d'appariement des résistances dans un CNA basé sur le réseau R-2R, l'effet des capacités parasites dans un CNA basé sur des capacités pondérées en binaire, la variation de la tension de seuil et la non-linéarité associée à l'échantillonneur bloqueur. Par exemple, un CAN-AS de 10 bits avec un  $DNL \leq \pm 4$  LSB n'a que 8 bits de résolution en pratique. La perte des bits est attribuable aux facteurs décrits ci-dessus, et une telle architecture possède une erreur de monotonicité. Celle-ci survient dans un CAN lorsque l'amplitude à la sortie devient très petite pour une augmentation de l'amplitude du signal d'entrée [RAZ95], autrement dit la croissante ou décroissance de la sortie en fonction du code d'entrée n'est pas assurée. Par ailleurs, d'autres sources d'erreurs pouvant limiter la performance du DNL ont été rapportées dans [OHN08], la première provient du décalage dans l'appariement des capacités utilisées dans le C-CNA, et la deuxième est une erreur dynamique, qui se produit sur des codes particuliers. La figure 2.5 montre la mesure du DNL dans le cas d'un CAN à trois (3) bits.

Figure 2.5 : Exemple de mesure du DNL d'un CAN à 3 bits.

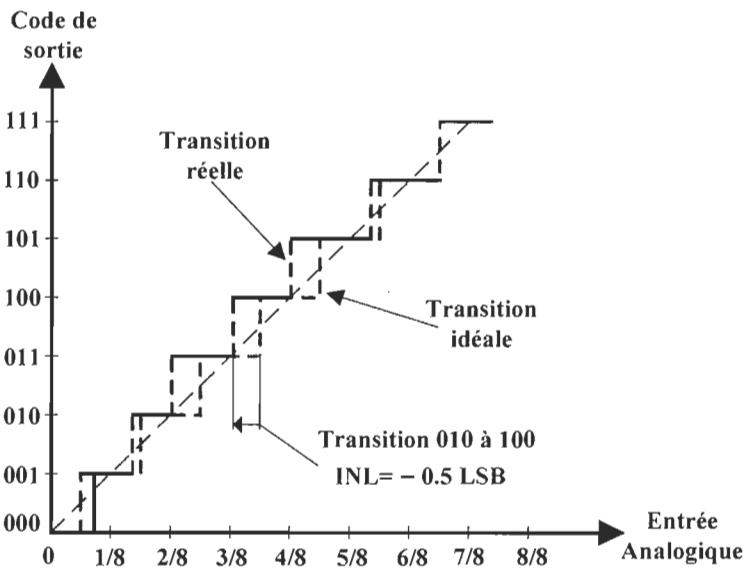

### 2.2.3 Erreur de Non-linéarité intégrale

La Non-linéarité intégrale (*INL* – *Integral Non Linearity*) est une mesure cumulative en ce sens qu'elle est l'intégrale de l'erreur de DNL, par conséquent, un bon INL garantit un bon DNL [BAK05]. Ce paramètre indique à quelle distance la valeur idéale de la fonction de transfert se situe par rapport à celle mesurée sur le convertisseur. L'INL spécifie aussi la marge d'erreur permise dans un CAN. Comme rapporté dans la littérature, cette marge d'erreur peut être de  $\pm 0.5$  LSB ou  $\pm 1$  LSB. Supposons un  $INL \leq \pm 1$  LSB, la précision dans un CAN à 10 bit sera de 0.048%. Tout comme le DNL, l'erreur d'INL se détériore sous l'effet des facteurs énoncés précédemment. Ces deux paramètres constituent un des critères primordiaux dans la sélection d'un CAN-AS. La figure 2.6 montre l'exemple de mesure de l'INL dans le cas d'un CAN à trois (3) bits.

Figure 2.6 : Exemple de mesure de l'INL d'un CAN à 3 bits.

### 2.3 Impact des métriques de performances dynamiques sur une architecture du CAN-AS

Les paramètres dynamiques d'un CAN-AS permettent de mieux comprendre sa réponse à haute fréquence, spécialement quand le signal d'entrée atteint une certaine amplitude pleine échelle.

#### 2.3.1 Impact du rapport signal sur bruit dans un CAN-AS

Le rapport signal sur bruit (S/B) révèle où la plage du bruit se situe dans un CAN. Un bon S/B est toujours ce qu'on recherche lorsqu'on conçoit un CAN, mais on est souvent confronté à certaines erreurs qui viennent détériorer cette valeur. Dans une architecture de CAN-AS, il y a plusieurs sources de bruit parmi lesquels on a le bruit de quantification introduit par le CNA et le comparateur, le bruit thermique associé aux résistances et capacités, le bruit associé à l'échantillonneur bloqueur (E/B) et le bruit venant du milieu externe par exemple, la source d'alimentation du circuit. Dans le cas d'un E/B, il faut s'assurer que le signal échantillonné soit le moins bruité possible et

n'oscille pas au-delà de  $\frac{1}{2}$  LSB. La contribution en bruit associée à ces facteurs affecte le bon fonctionnement des éléments de base qui constituent un CAN.

### 2.3.2 Autres paramètres dynamiques associés au CAN-AS

Le rapport signal sur bruit plus distorsion (S/B+D) est une fonction de la fréquence d'entrée. Elle permet d'identifier la fréquence maximale d'opération du circuit d'autant plus que la performance des circuits se dégrade considérablement au fur et à mesure que l'on s'approche de la fréquence de Nyquist (fréquence égale au double de la fréquence maximale du système [BAK05]). Le nombre effectif de bit (*ENOB – Effective Number Of Bits*) est une autre spécification qui nous informe sur la non-linéarité du CAN-AS.

Nous avons aussi des contraintes telles que l'injection de charges et l'erreur d'horloge qui proviennent de l'E/B. Ce dernier est généralement utilisé comme étage d'entrée dans un CAN afin de faciliter les exigences de temps, et comme étage de sortie dans un CNA pour supprimer les impulsions non désirées.

### 2.3.3 Impacts liés au régulateur de tension

Le circuit de régulation en tension représente aussi une source d'erreurs potentielles dans un CAN-AS. L'erreur introduite par ce circuit se résume en trois grands thèmes: la dérive en température, le bruit en tension et le régulateur de charge [BAK05].

Nous avons présenté succinctement le convertisseur analogique numérique à approximations successives et les facteurs qui influencent ses performances. Il en ressort dans un premier temps que tous les éléments constitutifs d'une architecture de CAN-AS, affectent d'une façon ou d'une autre la performance du circuit. Une étude approfondie sur les paramètres statiques et dynamiques ont permis de mieux comprendre l'impact que peut avoir chaque paramètre sur le fonctionnement du CAN.

Dans ce mémoire, nous allons dans la mesure du possible simuler ou mesurer certains de ces paramètres. Le prochain chapitre portera sur les récents travaux effectués au niveau des CAN-AS qui opèrent à basse tension et basse puissance.

## *Chapitre 3*

### ***REVUE DE LITTÉRATURE SUR LES CAN-AS***

Aujourd’hui, la plupart des traitements de signaux effectués dans les systèmes électroniques sont numériques, et la performance des CAN qui sont majoritairement utilisés pour interfaçer les signaux réels et analogiques au domaine numérique devient de plus en plus primordiale. Le développement rapide observé dans la technologie des circuits intégrés a permis d’améliorer l’efficacité des CAN. Dans le chapitre précédent, nous avons fait une introduction sur les CAN-AS. Cependant, il existe une variété de CAN-AS rangée suivant leur efficacité énergétique. Nous rapporterons les récents travaux qui ont été présentés à ce niveau, tout en explorant les tendances technologiques et quelques limites.

#### **3.1 CAN-AS basé sur les CNA de type R-2R**

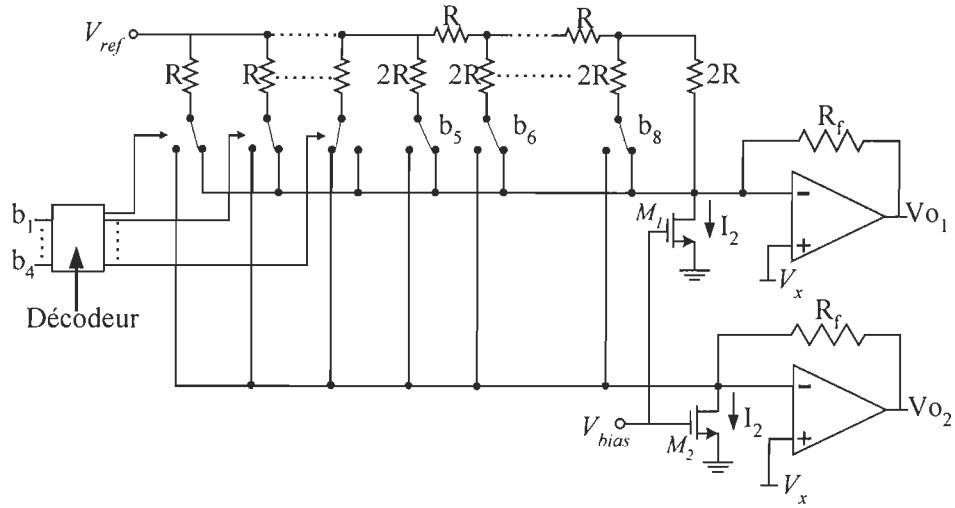

Pour une structure de CAN-AS qui a l’avantage principal de requérir moins d’espace, nous avons l’architecture basée sur un CNA qui utilise le réseau de résistances de R-2R. Mortezapour et al. [MOR00], proposent un CAN-AS à 8 bits qui opère à 1 V. Il est constitué d’un E/B comme étage d’entrée, un CNA de type R-2R segmenté en mode courant, un circuit de contrôle et un comparateur basé sur une approche dite mode courant. Le schéma bloc du CNA est décrit à la figure 3.1, il requiert deux amplificateurs opérationnels au niveau de sa sortie. Bien qu’un seul amplificateur opérationnel (amp-op) soit normalement requis, deux amp-op sont plutôt utilisés dans le cas où l’un des amp-op sert à mesurer la performance du CNA [MOR00]. L’amp-op utilisé à la sortie du réseau R-2R sert aussi à réduire le bruit, fixer une grosse impédance à la sortie du R-2R et produire une tension analogique à partir de la résistance  $R_f$ .

Figure 3.1: Schématique d'un CNA de type R-2R (Tiré de [MOR00]).

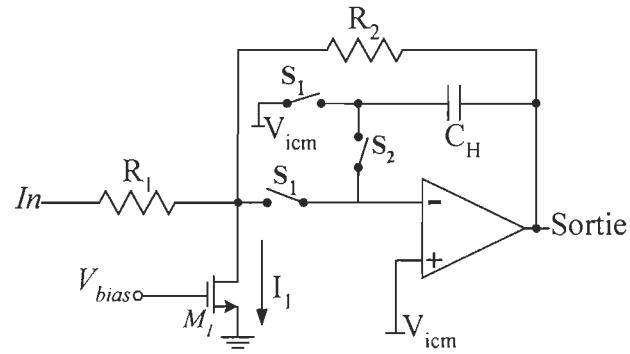

Mortezapour et al. [MOR00], proposent un E/B dont le schéma bloc est décrit à la figure 3.2. Le circuit est constitué d'un amp-op, des résistances, commutateurs et une capacité.

Quand le commutateur  $S_1$  est fermé, et  $S_2$  ouvert, l'E/B est en mode échantillonnage et le circuit équivalent est un amplificateur en configuration inverseur avec un gain égal à  $-R_2/R_1$ . La capacité de mémorisation  $C_H$  agit dans ce cas comme une capacité de charge pour l'amp-Op. Dans le but d'éradiquer la contrainte imposée par la tension d'alimentation sur l'E/B, les auteurs proposent une technique qui consiste à fixer la tension en mode commun  $V_{icm}$  proche de zéro, soit la tension efficace  $V_{DSSat}$  par exemple. Pour ce faire, un transistor  $M_1$  est connecté à l'entrée négative de l'amp-op et il est contrôlé par une tension de polarisation, de sorte que  $M_1$  ait assez de tension drain-source,  $V_{DS}$ , pour opérer comme une source de courant. L'expression du courant fournit par  $M_1$  peut être approximée par [MOR00]

$$I_1 = \left( \frac{V_{DD}}{2} - V_{icm} \right) \left( \frac{1}{R_2} + \frac{1}{R_1} \right) \quad (3.1)$$

L'un des avantages de cette technique est que la tension d'alimentation minimale requise pour faire fonctionner l'E/B est considérablement réduite. Au lieu de  $2*|V_{TH}| + 4V_{DSsat}$  sans courant  $I_1$ , on a plutôt une valeur approximée à  $|V_{TH}| + 3 V_{DSsat}$  avec le courant  $I_1$ . Notons dans ce cas que la paire d'entrée différentielle est constituée de transistor pMOS et la source de courant est un transistor nMOS. Advenant que la paire d'entrée différentielle soit formée de transistors nMOS et la source de courant par un transistor pMOS, alors  $V_{icm}$  devrait être fixée autour de  $V_{DD}$ .

Quand le  $S_1$  est ouvert, et  $S_2$  fermé, le signal prélevé est maintenant disponible au nœud de sortie. Le bruit moyen présent dans le signal échantillonné a été estimé dans [MOR00]. La technique du hacheur n'a pas été utilisée pour réduire le bruit.

Figure 3.2: Schématique du circuit d'E/B (tiré de [MOR00]).

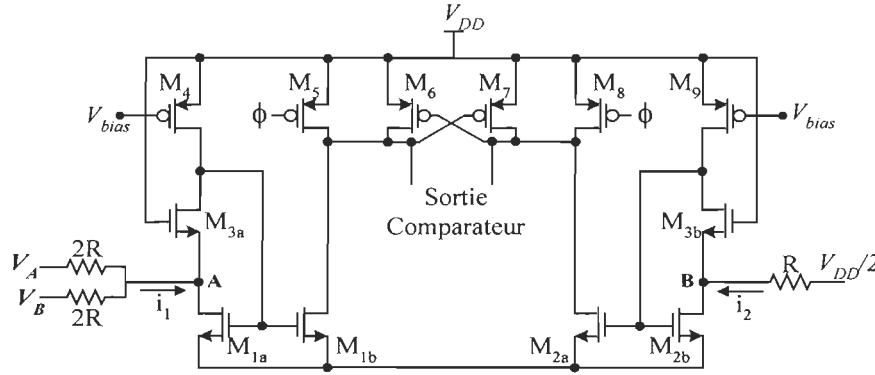

Les auteurs proposent aussi un comparateur à verrou utilisant une approche dite mode courant telle que décrite à la figure 3.3.

Figure 3.3: Comparateur à verrou utilisant une approche à mode courant (Tiré de [MOR00]).

Les nœuds A et B ont une très faible impédance, celle-ci peut être approximée par [MOR00]

$$R_A = \frac{1}{g_{M1a} g_{M3a} r_{o4}} \quad (3.2)$$

où  $g_{M1a}$ ,  $g_{M3a}$ , et  $r_{o4}$  sont respectivement, la transconductance de  $M_{1a}$ ,  $M_{3a}$ , et la résistance de sortie de  $M_4$ . Le courant  $i_1$  est proportionnel à la différence de tension produite entre  $V_A$  et  $V_B$ . Lorsque  $\Phi$  est au niveau haut, soit ‘1’, le courant  $i_1$  est comparé au courant  $i_2$  provenant de la tension de référence et un niveau logique correspondant est produit en sortie. Bien qu’ayant une large plage d’entrée, ce comparateur est limité en courant au niveau de la rétroaction action formée par  $M_6/M_7$ , puisque ceux-ci réalisent une opération de classe A [FIG06]. Par ailleurs, l’absence de gain en entrée affecte fortement le temps de réponse de ce comparateur.

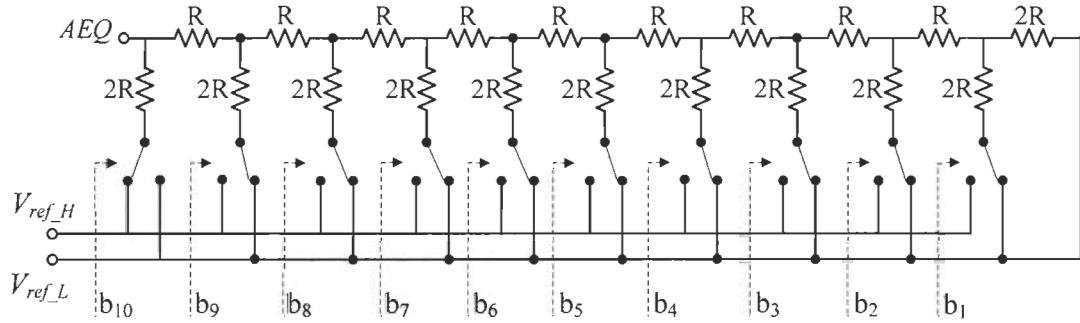

Une architecture similaire a été introduite par Fayomi et al. [FAY01]. Ce CAN-AS utilise un CNA de type R-2R en mode tension. Le schéma bloc est illustré à la figure 3.4. Ce circuit ne requiert pas un amplificateur opérationnel à son nœud de sortie AEQ, car, ce dernier va directement à un nœud de haute impédance [FAY01]. Les signaux de contrôle  $b_{10}$  à  $b_1$  proviennent du registre à approximation successive (RAS). Une tension analogique équivalente à la combinaison binaire des signaux est obtenue au nœud AEQ.

Figure 3.4: CNA traditionnel en mode tension (Tiré de [FAY01]).

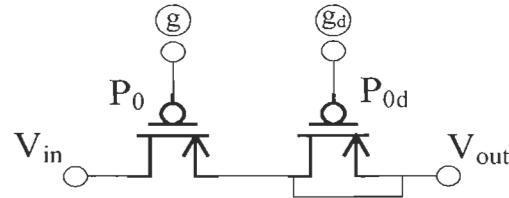

Au niveau de l'étage d'entrée, les auteurs proposent un E/B réalisé à partir d'un simple transistor. Le schéma bloc de l'E/B est présenté à la figure 3.5, il est constitué d'un transistor pMOS en série avec un autre transistor pMOS en configuration dummy.

Figure 3.5: Circuit d'un échantillonneur bloqueur (Tiré de [FAY01])

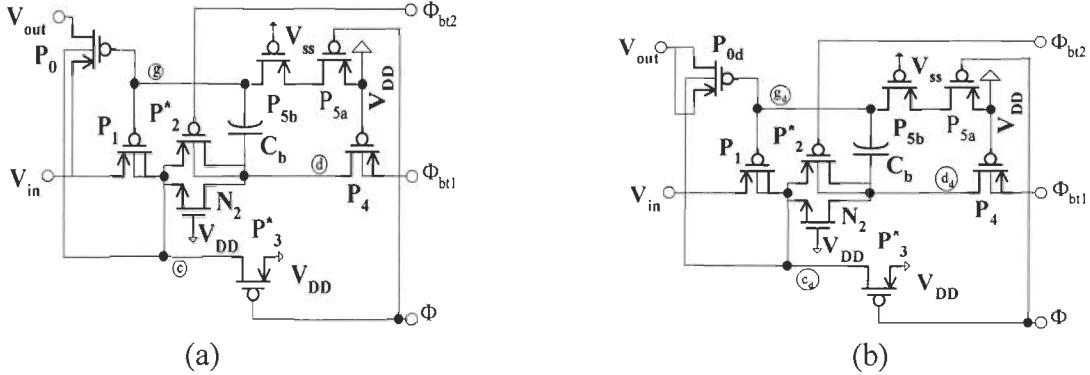

Étant donné la réduction de la plage d'entrée liée à l'utilisation d'une petite tension d'alimentation, les auteurs utilisent la technique de commutation amorcée (bootstrapped) pour surmonter cette limite. Elle consiste à produire des signaux de contrôle dont la plage d'amplitude se situe au-delà de la limite supérieure et inférieure de la tension d'alimentation initiale. La figure 3.6(a) décrit le circuit de contrôle du commutateur pMOS proposé tandis que, le commutateur dummy amorcé est présenté à la figure 3.6(b). L'usage du transistor pMOS est dû à sa conductance qui est relativement constante et sa charge du canal  $Q_{CH}$ , qui est indépendante du signal d'entrée [FAY01].

Figure 3.6: Schématique de l'E/B (Tiré de [FAY01]): (a) Commutateur amorcé à compensation et (b) Commutateur dummy amorcé.

Au niveau du comparateur, une architecture à entrée pleine échelle a été proposée. Telle que décrite dans [FAY08], le circuit à deux étages; Un étage d'entrée différentielle ayant deux paires complémentées de transistors (nMOS/pMOS) en parallèle et un verrou régénératif. Bien qu'ayant une entrée pleine échelle, l'architecture proposé par [FAY08], est sujette à une grande tension de décalage ce qui peut fortement affecter la performance du comparateur. Par ailleurs, la plage de fonctionnement de cet étage d'entrée varie, ceci dépendamment du niveau du signal d'entrée. Puisque la transconductance totale  $g_m$ , de la paire d'entrée différentielle varie à travers la gamme d'entrée en mode commun, le délai du comparateur pourrait varier [CHU99]. Fayomi et al. [FAY01] proposent un différentiateur de courant qui permet de contrôler  $g_m$ . En conséquence, on a une paire différentielle complémentée avec un  $g_m$  constant. Le circuit proposé dans le second étage est similaire à celui présenté dans [YUK85].

### 3.2 CAN-AS basé sur un CNA à diviseur de courant

Le CAN-AS basé sur un CNA à diviseur de courant est une architecture de circuit qui fut d'abord introduit par McCreary et al [McC75]. Au niveau du CNA, une nouvelle

topologie a été proposée par Fayomi et al. [FAY01]. Le schéma bloc est illustré à la figure 3.7.

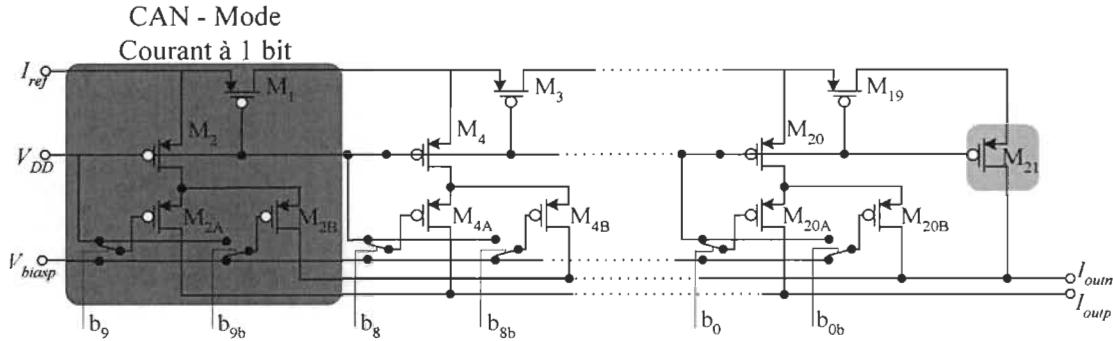

Figure 3.7 : CNA à mode courant basé uniquement sur les transistors de type pMOS (Tiré de [FAY01]).

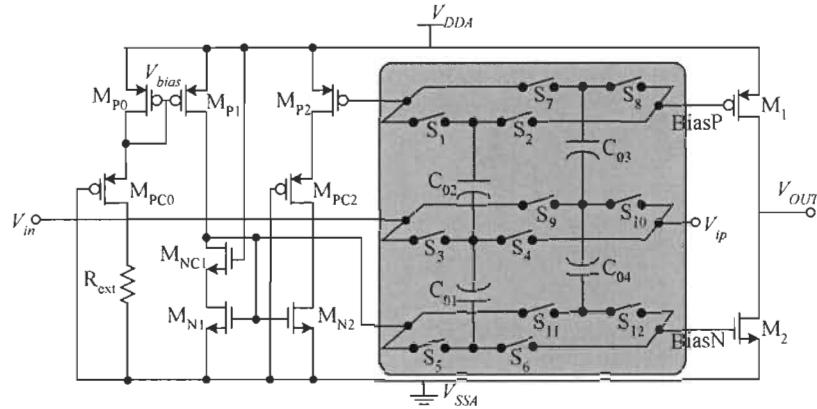

Le mode d'opération est basé sur le principe de division du courant linéaire [BUL92]. L'exigence de la tension de sortie dicte le choix des transistors pMOS à la place des nMOS [FAY01]. Étant donné qu'on prélève le courant en sortie, la présence d'un convertisseur de courant est nécessaire avant de relier le tout au comparateur. Pour ce faire, les auteurs proposent un amp-Op ayant une entrée et sortie qui réalise une opération de classe AB, c'est-à-dire pleine échelle. Le schéma bloc est illustré à la figure 3.8.

Figure 3.8 : Schématique d'un Amp-op à basse tension utilisé pour convertir le courant en tension (Tiré de [FAY01]).

Cette architecture est limitée par sa grande dissipation d'énergie, ce qui la rend moins attractive pour des applications qui opèrent à basse tension.

### 3.3 CAN-AS basé sur un CNA capacitif

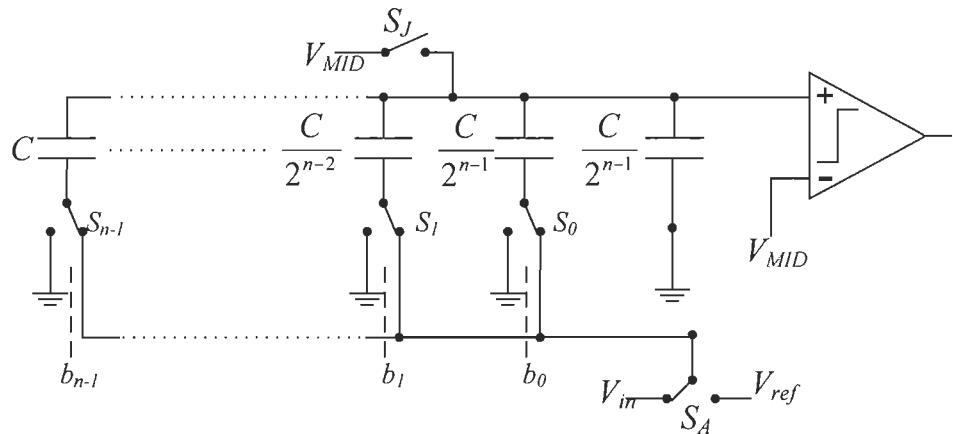

Le CAN-AS basé sur un CNA à capacités pondérées en binaire est une architecture de CAN très efficace en termes de dissipation d'énergie. Il est dédié aux systèmes à résolution et vitesse moyennes. McCreary et al. [McC75], introduisent une architecture de CAN-AS basé sur la technique de distribution de charges ou transfert de charges. Le schéma bloc du CNA est décrit à la figure 3.9.

Figure 3.9 : Schématique du CNA à réseau de capacités pondérées en binaire (Tiré de [McC75]).

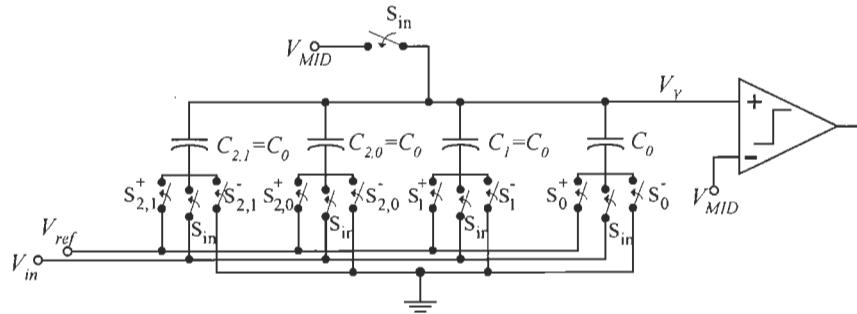

Le C-CNA est suivi d'un comparateur qui produit un niveau logique ‘1’ ou ‘0’. Les capacités placées en parallèle sont pondérées de façon binaire. Leur pondération va de  $C$ ,  $C/2$ ,  $C/4$ ,  $C/8$ , jusqu'à  $C/2^{n-1}$ ,  $n$  représente le nombre de bits et  $C$ , la capacité unitaire.  $V_{in}$  est la tension d'entrée,  $V_{ref}$  est la tension de référence soit,  $V_{DD}$  tandis que,  $V_{MID}$  est la tension à mi-échelle, soit  $\frac{1}{2} V_{DD}$  ou 0. La somme totale des capacités dans le réseau est égale à  $2C$ . Comme nous pouvons le constater, la différence fondamentale consiste à manipuler les charges au lieu des courants tels que présenté dans un CNA de type R-2R.

Ce faisant, le circuit du C-CNA devient très attrayant car la consommation du courant statique est presque nulle, mais il requiert une grande surface.

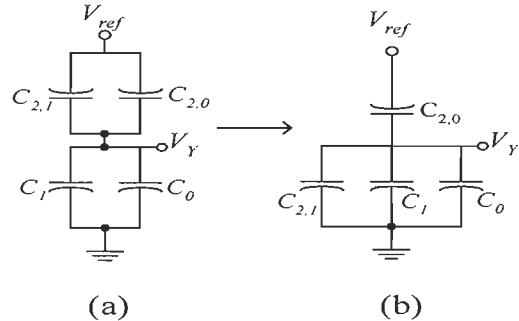

Dans le but de décrire le processus de redistribution des charges, nous allons considérer le cas d'un C-CNA à 2 bits ( $b_1$  et  $b_0$ ), tel qu'illustré à la figure 3.10, où  $C_{MSB}$  est la capacité du bit le plus significatif et correspond à la plus grosse capacité dans le réseau.

Figure 3.10 : Circuit équivalent d'un réseau conventionnel de capacités pondérées en binaire à 2 bits durant le mode échantillonnage : (a) Circuit lorsque  $C_{MSB}=C$  et (b) lorsque  $C_{MSB}=2C$ .

Le processus d'échantillonnage est inhérent dans l'architecture présentée ci-dessus, en conséquence, elle ne requiert pas un E/B. La conversion d'un mot numérique en une tension analogique nécessite trois mode d'opérations à savoir; le mode échantillonnage, le mode maintien en attente et le mode redistribution.

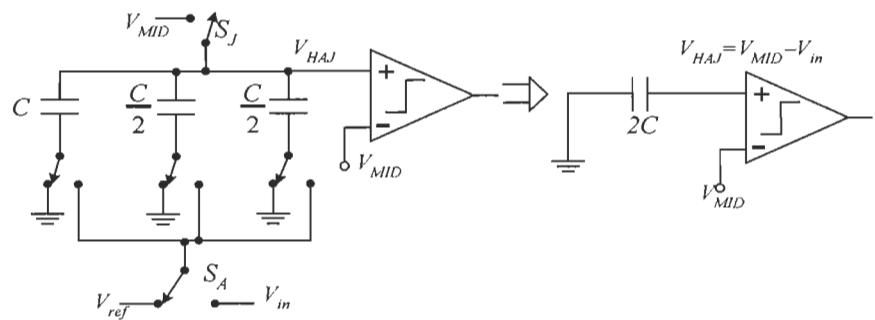

**Dans le mode échantillonnage** tel que présenté à la figure 3.10, le commutateur  $S_J$  est fermé, les plaques du haut du réseau de capacités sont connectées à  $V_{MID}$  qui est la tension en mode commun. Le commutateur  $S_A$  est relié au signal d'entrée  $V_{in}$ , ce qui permet de connecter les plaques du bas à  $V_{in}$ . La tension d'entrée est ainsi échantillonnée sur le nœud  $V_{HAI}$ . Une quantité de charges proportionnelle à la tension d'entrée  $V_{in}$  est ainsi stockée sur les plaques du haut de la chaîne de capacités. Cette charge peut s'exprimer à partir de l'équation (3.3)

$$Q_{in} = 2C_{eq}(V_{MID} - V_{in}) \quad (3.3)$$

où  $C_{eq}$  est la capacité totale équivalente,  $V_{in}$  est la tension d'entrée et  $V_{MID}$ , tension égale à  $\frac{1}{2} V_{DD}$  ou 0.

**Dans le mode maintien ou attente**, comme illustré à la figure 3.11, on déconnecte le commutateur  $S_J$  de  $V_{MID}$  et  $S_A$  est connecté à la tension de référence  $V_{ref}$ . Au niveau des capacités, toutes les plaques du bas du réseau de capacités se retrouvent connectées à la masse. L'application du principe de la conservation de charge permet de constater que la tension au niveau des plaques supérieures est maintenant  $V_{MID} - V_{in}$ . En conséquence, le circuit se comporte dans un premier temps comme un E/B.

Figure 3.11 : Circuit équivalent du C-CNA: Mode attente.

Figure 3.12 : Circuit équivalent du C-CNA: Première étape de conversion.

**Le mode redistribution** représente le début du processus de conversion, tel qu'illustré à la figure 3.12, c'est le premier cycle binaire. Il consiste à vérifier l'état du MSB c-à-d., le bit  $b_1$ . Préalablement,  $b_1$  est mis à ‘1’ et  $b_0$  est mis à ‘0’, ceci grâce à la logique de contrôle. La plaque du bas de la plus grosse capacité,  $C_{MSB}$ , est connectée à  $V_{ref}$  et le reste des plaques du bas sont connectées à la masse. La tension de sortie  $V_{HAI}$  qui est en partie déterminée par le rapport entre  $C_T$  et  $C_H$ , peut s'exprimer à partir de l'équation (3.4) comme démontré dans [McC75]

$$V_{HAI} = V_{MID} - V_{in} + \frac{C_T}{C_T + C_H} V_{ref} \quad (3.4)$$

où  $C_T$  est la capacité totale connectée à  $V_{ref}$ , et  $C_H$  est la capacité totale connectée à la masse.

$$C_T = \sum_{j=0}^n 2^{j-1} C \text{ Pour } j \text{ avec } S_j = 1 \quad (3.5)$$

$$C_H = \sum_{j=0}^n 2^{j-1} C \text{ Pour } j \text{ avec } S_j = 0 \quad (3.6)$$

De part le principe de fonctionnement d'un CAN-AS, la conversion d'un mot de  $n$  bits nécessitera  $n$  cycles d'horloges. Autrement dit, il s'agit de vérifier l'état de chaque bit jusqu'à la fin de la conversion. En posant  $C_T = C_H$ , la nouvelle expression de  $V_{HAI}$  devient

$$V_{HAD}(1) = V_{MID} - V_{in} + \frac{1}{2}V_{ref} \quad (3.7)$$

Nous remarquons que l'entrée positive du comparateur augmente par  $\frac{1}{2} V_{ref}$ .

Le comparateur sert à détecter le niveau de supériorité ou infériorité entre les tensions appliquées sur ses entrées et produit un niveau logique. La sortie du comparateur sera de logique ‘0’ si la tension  $V_{HAD} < 0$  et de logique ‘1’ si  $V_{HAD} > 0$ . Cette analogie se résume comme ci-dessous.

Si  $V_{HAD} > 0$  alors  $V_{in} < \frac{1}{2} V_{ref}$ , comme résultat, le MSB = 1. Par contre, si  $V_{HAD} < 0$  alors  $V_{in} > \frac{1}{2} V_{ref}$ , comme résultat, le MSB = 0. La sortie du comparateur décide de l'état final du bit à tester. La plaque inférieure de la capacité de MSB reste à  $V_{ref}$  si  $b_2 = 1$ , sinon  $b_2$  prend la valeur ‘0’. De manière similaire, le prochain MSB est déterminé. Le processus se répète jusqu'à l'identification du bit le moins significatif (LSB) qui marque ainsi la fin du processus conversion. Une expression générale de  $V_{HAD}$  dans le cas d'un C-CNA à 2 bits peut être approximée par

$$V_{HAD} = V_{MID} - V_{in} + V_{ref} \left( \frac{b_1}{2^1} + \frac{b_0}{2^2} \right) \quad (3.8)$$

où  $b_1$  et  $b_0$  représentent les valeurs binaires. Jusqu'ici, la méthode conventionnelle de commutation reste simple. Nous allons maintenant évaluer l'énergie consommée durant chaque cycle de conversion. Afin d'alléger les explications, nous utiliserons l'expression transition “montante” pour définir la connexion de la plaque du bas d'une capacité à  $V_{ref}$ , et l'expression transition “descendante” dénote quant à elle la connexion de la plaque du bas à  $V_{SS}$ , tension de référence minimale.

Ginsburg et al. [GIN05], proposent une méthode permettant d'évaluer l'énergie dissipée par le C-CNA durant chaque cycle de conversion. Supposons qu'à l'instant  $t = 0^-$ , la tension d'entrée a été complètement échantillonnée sur le réseau de capacités. À  $t = 0$ , la plaque du bas de la capacité  $C_2$  (capacité de MSB) est connectée à  $V_{ref}$  tandis que le reste des plaques inférieures restent connectées à la masse comme l'illustre la figure 3.13.

Le réseau de capacités est donc chargé à la valeur finale définie tel que donnée par l'équation (3.7). Supposons que  $Q_2$ , quantité de charges transférées au nœud  $V_{HAI}$  durant le premier cycle binaire, l'énergie totale  $E_{0 \rightarrow 1}$  correspondante à cet effort est définie par [GIN05]

$$E_{0 \rightarrow 1} = \int_{0^+}^{t_1} i_{REF}(t) V_{REF} dt = V_{REF} \int_{0^+}^{t_1} i_{REF}(t) dt \quad (3.9)$$

$$\text{avec } i_{REF} = -\frac{dQ}{dt}$$

De même,

$$\begin{cases} Q(0^+) = Q(0^-) = 2C_2[V_{HAI}(0)] \\ Q_{C_2}(t_1) = [(V_{HAI}(1) - V_{REF}) - (0 - 0)] \end{cases} \quad (3.10)$$

où  $Q$  représente la quantité de charges fournies par  $V_{ref}$  au C-CNA.

En développant (3.9), nous obtenons

$$\begin{aligned} E_{0 \rightarrow 1} &= -V_{REF} \int_{0^+}^{t_1} \frac{dQ_{C_2}(t)}{dt} dt = -V_{REF} \int_{Q_{C_2}(0^+)}^{Q_{C_2}(t_1)} Q_{C_2} \\ &= -V_{REF} (Q_{C_2}(t_1) - Q_{C_2}(0^+)) \\ &= CV_{REF}^2 \end{aligned} \quad (3.11)$$

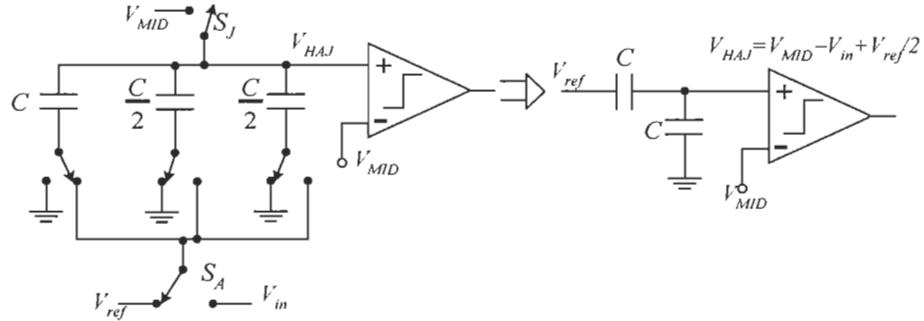

En somme, la consommation d'énergie nécessaire pour déterminer l'état de  $b_2$  est  $CV_{ref}^2$ . À la fin du premier cycle binaire, la valeur de la tension telle que donnée par l'équation (3.7) est comparée à la tension  $V_{MID}$ , et une décision est prise par le comparateur. Si  $V_{HAI} > V_{MID}$ , la sortie du comparateur est ‘1’, en conséquence la plaque inférieure de  $C_{MSB}$  reste connectée à  $V_{ref}$  c.-à-d.,  $b_1 = 1$  et on passe au prochain MSB. Par contre, si  $V_{HAI} < V_{MID}$ , la sortie est ‘0’ alors, cette plaque est plutôt connectée à la masse, c.-à-d.,  $b_1 = 0$  et aucun transfert de charge n'a lieu en vers  $C_{MSB}$ .

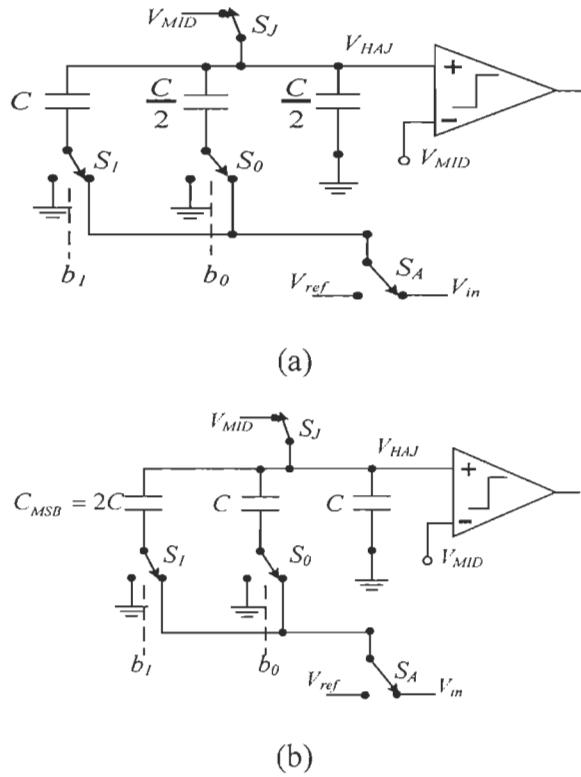

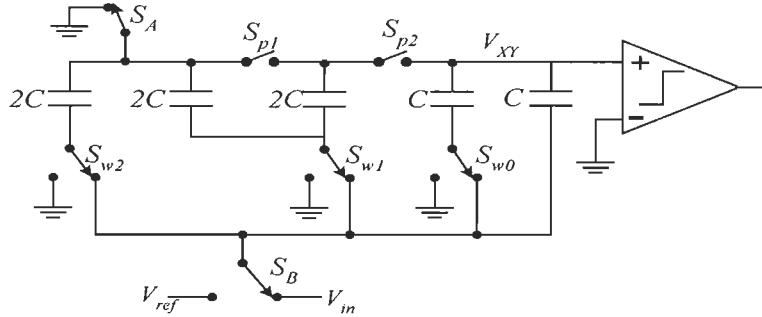

Durant le deuxième cycle binaire, on teste la valeur de  $b_0$ , deux situations se présentent à ce stade. Si  $b_1 = 1$ , on a une transition “montante” et le schéma bloc équivalent du C-CNA est décrit à la figure 3.13

Figure 3.13 : Schéma bloc du C-CNA conventionnel à 2 bits lorsque  $b_1 = 1$ .

La tension  $V_{H AJ}$  devient

$$V_{H AJ}(1) = V_{MID} - V_{in} + \frac{3}{4}V_{ref} \quad (3.12)$$

De même, l'énergie totale dissipée par  $V_{ref}$  durant cette transition s'exprime par l'équation (3.13) comme évalué dans [GIN05]

$$E_{l \rightarrow 2} = \frac{CV_{ref}^2}{4} \quad (3.13)$$

Dans le même ordre d'idée, si  $b_1 = 0$ , on a une transition “descendante” et la figure 3.14 représente le schéma bloc équivalent

Figure 3.14 : Schéma bloc C-CNA à 2 bits lorsque  $b_1=0$ .

L'expression de la tension  $V_{HAI}$  devient

$$V_{HAI}(1) = V_{MID} - V_m + \frac{1}{4}V_{ref} \quad (3.14)$$

En outre, l'énergie totale dissipée par  $V_{ref}$  durant cette transition s'exprime par [GIN05]

$$\begin{aligned} E_{1 \rightarrow 2} &= -V_{ref} \left[ \int_{t_0}^{t_1} \frac{dQ_{C_1}}{dt} dt + b_2 * \int_{t_1}^{t_2} \frac{dQ_{C_1}}{dt} dt \right] \\ &= -V_{ref} \left[ (Q_{C_1}(t_1) - Q_{C_1}(t_0)) + 0 \times [(Q_{C_1}(t_2) - Q_{C_1}(t_1))] \right] \\ &= \frac{5}{4} CV_{ref}^2 \end{aligned} \quad (3.15)$$

Nous venons d'estimer la dissipation d'énergie requise pour déterminer l'état des bits  $b_2$  et  $b_1$  par un CNA capacitif [McC75]. Au vue des équations (3.13) et (3.15), nous constatons que l'énergie requise durant la transition "montante" est inférieure à celle requise lors de la transition "descendante". Notons aussi que les deux premiers cycles de conversion consomment beaucoup d'énergie par comparaison aux restes des cycles de conversion [McC75]. Ceci est dû à la taille de la capacité de MSB qui prend plus de temps pour se charger.

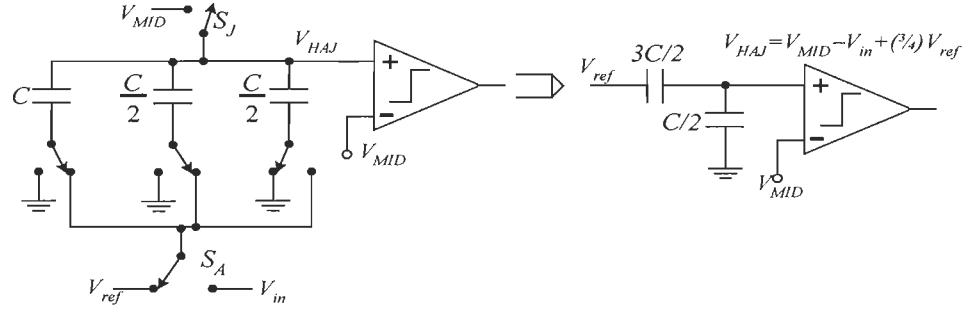

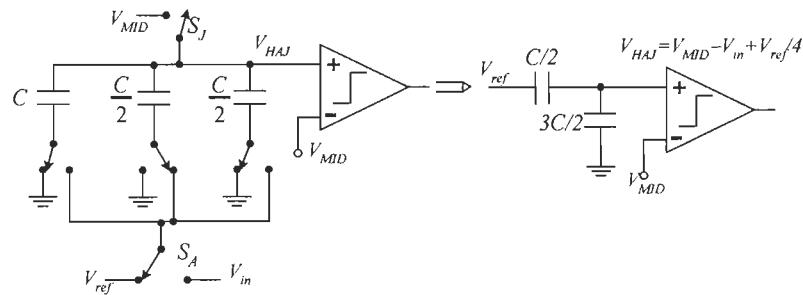

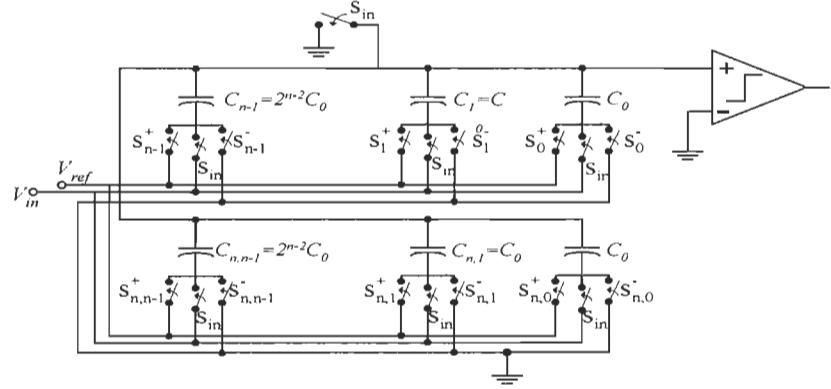

Ginsburg et al. [GIN07], proposent un CAN-AS à 5 bits basé sur un CNA à réseau de capacités fragmentées donc le schéma bloc est décrit à la figure 3.15. La technique consiste à fragmenter la capacité de MSB d'un C-CNA conventionnel [McC75] et ensuite, former deux chaînes de capacités en parallèle. La capacité totale du réseau de capacités fragmentées pondérées en binaire (CFPB) reste inchangée, soit  $2^n C_0$ . Cette technique permet de réduire à la fois la consommation d'énergie et la surface occupée par le CNA. L'algorithme de commutation de ces capacités a été amplement détaillé dans [GIN07].

Figure 3.15 : C-CNA à n-bits formé d'un réseau CFPB (Tiré de [GIN07]).