UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

ÉCOLE D'INGÉNIERIE

MÉMOIRE PRÉSENTÉ À

L'UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

COMME EXIGENCE PARTIELLE

À LA MAÎTRISE EN GÉNIE ÉLECTRIQUE (M.Sc.A)

PAR

FRÉDÉRIC MORIN

PIPELINE PAR VAGUES D'UNITÉS ARITHMÉTIQUES

POUR LA COMMUNICATION À TRÈS HAUT DÉBIT

AVRIL 2004

Université du Québec à Trois-Rivières

Service de la bibliothèque

Avertissement

L'auteur de ce mémoire ou de cette thèse a autorisé l'Université du Québec à Trois-Rivières à diffuser, à des fins non lucratives, une copie de son mémoire ou de sa thèse.

Cette diffusion n'entraîne pas une renonciation de la part de l'auteur à ses droits de propriété intellectuelle, incluant le droit d'auteur, sur ce mémoire ou cette thèse. Notamment, la reproduction ou la publication de la totalité ou d'une partie importante de ce mémoire ou de cette thèse requiert son autorisation.

---

« À Jennifer et à mes enfants Tristan et

Xavier...

...à la mémoire de ma mère,

Raymonde Élisabeth Béland...»

---

## **Remerciements**

J'aimerais, en premier lieu rendre hommage à ma douce moitié, Jennifer Anne Russett, qui m'a soutenu tout au long de mes études et durant cette quasi-interminable période de rédaction. Sa persévérance, sa patience, son amour et ces nombreux conseils inestimables m'ont permis enfin de terminer ce mémoire. Elle m'a donné les deux plus beaux cadeaux qu'un homme aurait pu espérer, mes enfants Tristan et Xavier. Je leurs dois à tous une grande partie des nombreuses heures investies dans ce travail.

Je tiens à remercier chaleureusement mon directeur de mémoire, le professeur Daniel Massicotte, pour son dévouement à la recherche scientifique et à ces connaissances qui m'ont permis de développer en moi un sens critique de la recherche scientifique, et surtout mon perfectionnement à la recherche en microélectronique. Je tiens aussi à le remercier pour l'intérêt qu'il a accordé à ce travail et pour son aide précieuse à la rédaction/correction de ce mémoire. Qu'il trouve ici l'expression de mon entière gratitude et le témoignage de mon amitié.

Je tiens à remercier de tout cœur les membres du jury, Professeur Tanguy Risset et Professeur Mansour Dahmane pour avoir évalué cette thèse et pour leurs commentaires qui

ont contribués à la qualité de ce mémoire.

Je remercie le corps professoral, le personnel du département et toutes les personnes, qui de près ou de loin ont su m'aider dans mon cheminement et à la réalisation de ce travail, qu'ils trouvent ici l'expression de ma gratitude et de ma sympathie.

Je remercie aussi les professeurs Daniel Massicotte, Kodjo Agbossou et Yves Dubé pour leurs supports financiers durant mes études de maîtrise. Sachez qu'ils m'ont été d'un grand soutien sans quoi j'aurais été forcé de mettre un terme à mes études.

Je voudrais aussi remercier tous mes coéquipiers du Laboratoire de signaux et systèmes intégrés de l'Université du Québec à Trois-Rivières pour leur soutiens, leurs conseils et pour avoir entretenu une atmosphère chaleureuse au sein du groupe.

Je voudrais également remercier mon collègue Martin Demontigny pour son aide et support moral, pour qui la robotique et l'asservissement non plus de secrets. Son amitié et ses précieux conseils m'ont permis de ne pas lâcher lors de moment difficile.

Finalement, je ne saurais passer sous silence mon entière gratitude à mon fidèle compagnon Martin Vidal pour les moments mémorables en sa compagnie. Ses conseils et ses connaissances inestimables furent très enrichissants et me serviront tout au long de ma vie professionnelle. Son dynamisme et son enthousiasme communicatif ont apporté d'heureux débats philosophiques et de fameux travaux d'équipes.

---

## Résumé

Ce mémoire propose une architecture et des unités arithmétiques utilisant la technique du pipeline par vagues comme méthodes d'intégration à très grande échelle (ITGE) sur silicium. Améliorer la qualité, augmenter la distance entre les stations de régénération du signal et si possible obtenir un gain en vitesse de transmission auquel l'information à travers un canal de communication numérique sera transmis sont tous possible si un algorithme adaptatif de reconstitution des données transmises est utilisé.

L'égalisation de canaux considérés comme algorithme adaptatif consiste à annuler les effets du canal afin de réduire les ISI et CCI. Il s'agit d'un traitement numérique qui consiste à filtrer le signal reçu avec la réponse impulsionnelle inverse du canal. Dans la plupart des cas comme la réponse impulsionnelle du canal est souvent inconnue, l'égaliseur sera adaptatif utilisant ainsi des données d'apprentissages.

Dans le cadre de cette recherche l'implantation d'une architecture systolique à base d'un réseau de neurone artificiel sera effectuée. Elle aura comme avantage d'être régulière au niveau structural et de simplifier les communications locales entre les processeurs élémentaires.

L'architecture sera basée sur une topologie multicouche utilisant une fonction de

---

décision de type canonique linéaire par morceaux nommée PL-MNN (*Piecewise Linear Multilayer Neural Network*). Chaque processeur aura une quantité de calculs assez élevés qui nécessite donc une étude sur les différentes techniques d'augmentation du débit et ainsi améliorer la vitesse auquelle notre architecture peut procéder à corriger les symboles.

La validation de l'architecture a été effectuée grâce à un modèle VHDL et un modèle analogique utilisant Pspice incluant les capacités parasites fût utilisée pour la validation et l'évaluation des performances Analog Artist® et Virtuoso® de Cadence®. La technologie CMOS de 0.5 µm (CMOSIS5, SPTM) offert par la société canadienne de microélectronique (CMC) et Hewlett Packard fût utilisée.

Finalement, l'objectif principal du travail de recherche est l'étude du pipeline par vagues pour le développement d'une architecture ITGE à très haut débit dédié à l'égalisation de canaux. Le pipeline par vagues que nous allons étudier a comme particularité d'être implantée à partir d'une cellule nommée NPCPL, réalisant les fonctions logiques de base et possédant des délais de propagation équilibrés. Le développement et la réalisation de cette cellule sont la base de ce travail de recherche. Cette méthode de pipeline a été proposée à un algorithme de reconstitution de signaux basé sur le filtre de Kalman [ELO98b], [MAS98]. Notre projet est une suite allant vers la réalisation des cellules de base en vue d'une fabrication.

---

# Table des matières

|                                                                    |      |

|--------------------------------------------------------------------|------|

| Remerciements .....                                                | III  |

| Résumé .....                                                       | V    |

| Liste des abréviations .....                                       | XVII |

| 1 Introduction .....                                               | 1    |

| 1.1 Problématique .....                                            | 3    |

| 1.2 Objectifs .....                                                | 9    |

| 1.3 Méthodologie .....                                             | 10   |

| 1.4 Organisation de ce mémoire .....                               | 11   |

| 2 Algorithmes d'égalisation de canaux de communication .....       | 13   |

| 2.1 Principe de l'égalisation de canaux .....                      | 20   |

| 2.2 Adaptation hors-ligne et en-ligne .....                        | 22   |

| 2.3 Algorithmes adaptatifs d'égalisation de canaux linéaires ..... | 24   |

| 2.4 Algorithmes basés sur la logique floue .....                   | 30   |

| 2.5 Algorithmes basés sur les réseaux de neurones .....            | 34   |

| 2.6 Choix de l'Égaliseur .....                                     | 40   |

| 2.7 Conclusion .....                                               | 42   |

| 3 Unités Arithmétiques entières .....                              | 44   |

---

|       |                                                       |    |

|-------|-------------------------------------------------------|----|

| 3.1   | Représentation des nombres binaires.....              | 45 |

| 3.2   | Additionneurs binaires .....                          | 51 |

| 3.2.1 | Additionneur partiel (HA).....                        | 52 |

| 3.2.2 | Additionneur entier (FA).....                         | 52 |

| 3.2.3 | Additionneur à retenue propagée (RCA) .....           | 54 |

| 3.2.4 | Additionneur à retenue anticipée (CLA).....           | 56 |

| 3.2.5 | Additionneur à conservation de la retenue (CSA) ..... | 57 |

| 3.2.6 | Additionneur à saut de la retenue.....                | 59 |

| 3.2.7 | Additionneur sériel .....                             | 60 |

| 3.2.8 | Autres additionneurs .....                            | 60 |

| 3.3   | Multiplicateurs.....                                  | 62 |

| 3.3.1 | Multiplieur à accumulation partielle.....             | 62 |

| 3.3.2 | Multiplieur parallèle .....                           | 68 |

| 3.3.3 | Multiplieur-Accumulateur (MAC).....                   | 75 |

| 3.4   | Choix des unités arithmétiques .....                  | 75 |

| 3.5   | Conclusion .....                                      | 75 |

| 4     | Les principales techniques pipeline.....              | 75 |

| 4.1   | Pipeline conventionnel.....                           | 75 |

| 4.2   | Pipeline Asynchrone .....                             | 75 |

| 4.3   | Pipeline par vagues .....                             | 75 |

| 4.3.1 | Calcul fondamental .....                              | 75 |

| 4.3.2 | Optimisation des délais de propagation.....           | 75 |

| 4.3.3 | Types de cellules disponibles .....                   | 75 |

---

|       |                                                                           |    |

|-------|---------------------------------------------------------------------------|----|

| 4.3.4 | Cellule NPCPL .....                                                       | 75 |

| 4.3.5 | Structure ITGE proposée pour le pipeline par vagues.....                  | 75 |

| 4.4   | Choix de la technique la plus appropriée à l'égalisation .....            | 75 |

| 4.5   | Conclusion .....                                                          | 75 |

| 5     | Réalisation d'U.A. pipeline par vagues.....                               | 75 |

| 5.1   | Intégration de la cellule NPCPL.....                                      | 75 |

| 5.1.1 | Dimension de la cellule.....                                              | 75 |

| 5.1.2 | Résultats de simulation.....                                              | 75 |

| 5.2   | Pipeline par vagues de l'additionneur et du multiplicateur .....          | 75 |

| 5.2.1 | Description .....                                                         | 75 |

| 5.2.2 | Résultats de simulation.....                                              | 75 |

| 5.3   | Pipeline par vagues du multiplicateur-accumulateur.....                   | 75 |

| 5.3.1 | Description .....                                                         | 75 |

| 5.3.2 | Résultats de simulation.....                                              | 75 |

| 5.4   | Évaluation des performances de l'architecture arithmétique proposée ..... | 75 |

| 5.4.1 | Débits et latence de l'architecture arithmétique proposée.....            | 75 |

| 5.5   | Conclusion .....                                                          | 75 |

| 6     | Application à l'égalisation de canaux .....                               | 75 |

| 6.1   | Contraintes et critères architecturaux en technologie ITGE.....           | 75 |

| 6.2   | Choix et description de l'architecture.....                               | 75 |

| 6.3   | Estimation de la surface de l'architecture.....                           | 75 |

| 6.4   | Conclusion .....                                                          | 75 |

| 7     | Conclusion .....                                                          | 75 |

---

|                                                     |    |

|-----------------------------------------------------|----|

| Bibliographie .....                                 | 75 |

| Annexe A (Articles).....                            | 75 |

| Annexe B (Modèle d'architecture en VHDL) .....      | 75 |

| Annexe C (Fichiers de commande et contrainte) ..... | 75 |

---

# Liste des Figures

|                                                                                    |    |

|------------------------------------------------------------------------------------|----|

| Figure 1.1) Concept du pipeline par vagues .....                                   | 7  |

| Figure 2.1) Communication numérique élémentaire.....                               | 14 |

| Figure 2.2) Canal avec bruit additif .....                                         | 15 |

| Figure 2.3) Canal linéaire invariant avec bruit additif.....                       | 16 |

| Figure 2.4) Canal linéaire variant avec bruit additif .....                        | 17 |

| Figure 2.5) Exemple d'un égalisateur de canaux .....                               | 18 |

| Figure 2.6) Exemple d'une transmission avant l'égalisateur (a), et après (b) ..... | 20 |

| Figure 2.7) Exemple d'un égalisateur adaptatif .....                               | 21 |

| Figure 2.8) Exemple d'une égalisation adaptative <i>zero-forcing</i> .....         | 25 |

| Figure 2.9) Architecture élémentaire de l'algorithme LMS.....                      | 26 |

| Figure 2.10) Architecture de l'égalisateur à retour de décision (DFE).....         | 28 |

| Figure 2.11) Égalisation aveugle ( <i>Blind equalisation</i> ).....                | 29 |

| Figure 2.12) Modèle de la logique floue dans un égalisateur de canaux .....        | 31 |

| Figure 2.13) Fonction d'appartenance canonique linéaire.....                       | 32 |

| Figure 2.14) Exemple de fonction d'activation.....                                 | 34 |

| Figure 2.15) Réseau multicouche récursif (PL-RNN) .....                            | 35 |

| Figure 2.16) Réseau de neurone multicouche non récursif (PL-MNN) .....             | 37 |

---

|                                                                                         |    |

|-----------------------------------------------------------------------------------------|----|

| Figure 2.17) Robustesse au bruit.....                                                   | 41 |

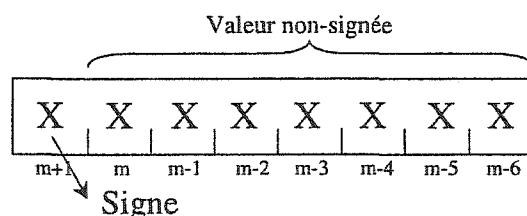

| Figure 3.1) Représentation signée.....                                                  | 45 |

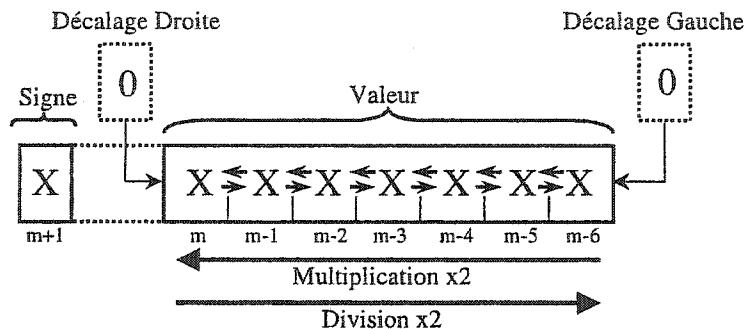

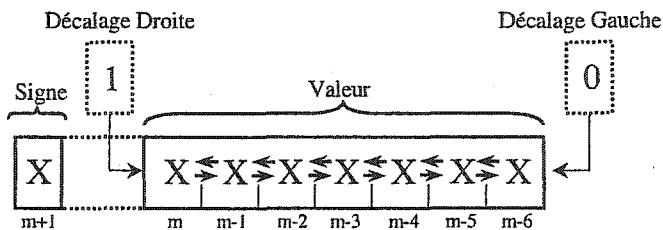

| Figure 3.2) Décalage d'une valeur positive et signe-module.....                         | 48 |

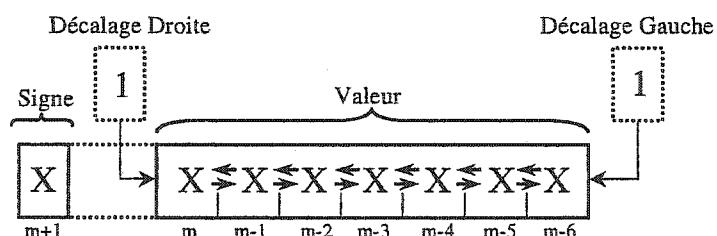

| Figure 3.3) Décalage de valeur négative en complément à un .....                        | 48 |

| Figure 3.4) Décalage de valeur négative en complément à deux .....                      | 49 |

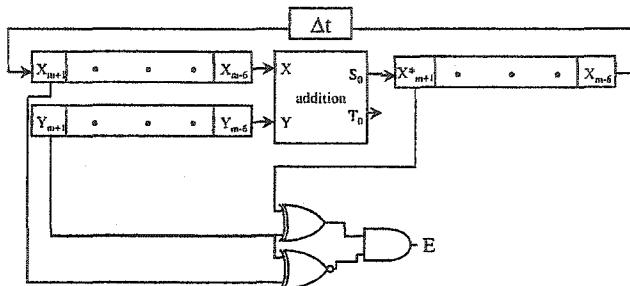

| Figure 3.5) Vérification du dépassement lors d'une accumulation en série .....          | 51 |

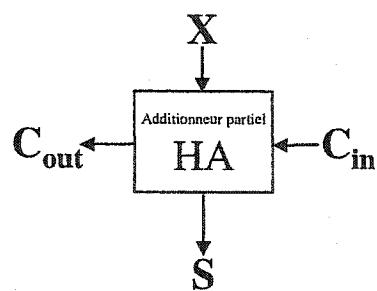

| Figure 3.6) Principe de l'additionneur partiel .....                                    | 52 |

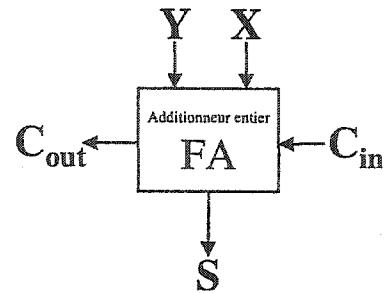

| Figure 3.7) Principe de l'additionneur entier .....                                     | 53 |

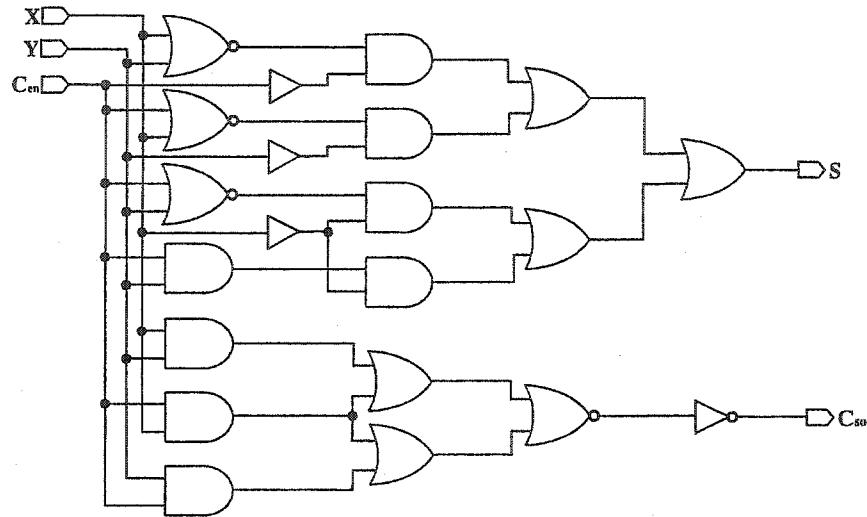

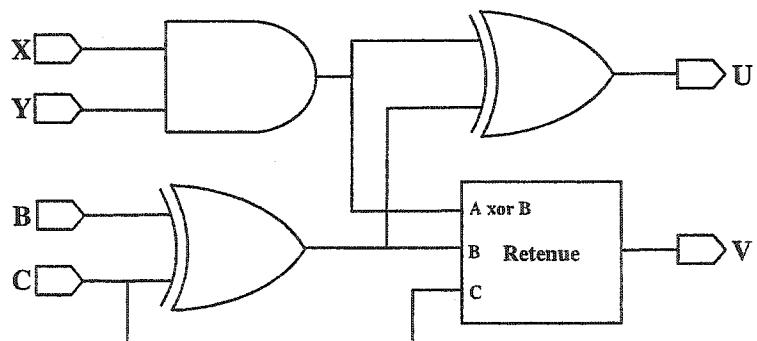

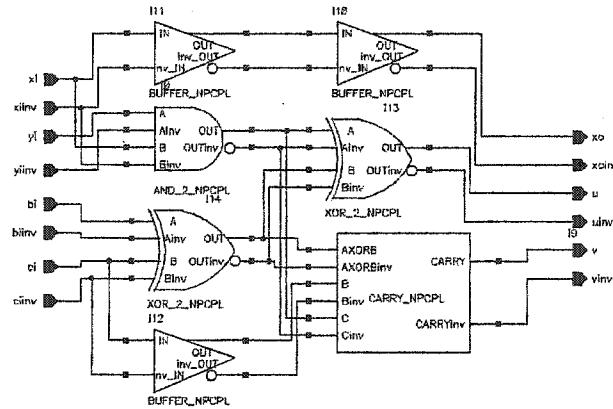

| Figure 3.8) Schématique d'une cellule FA avec délais équilibrés .....                   | 54 |

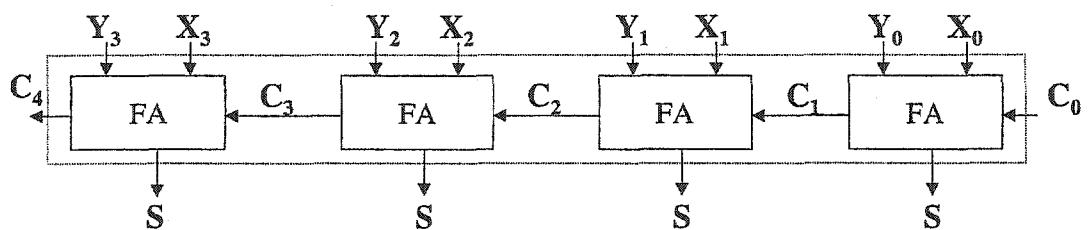

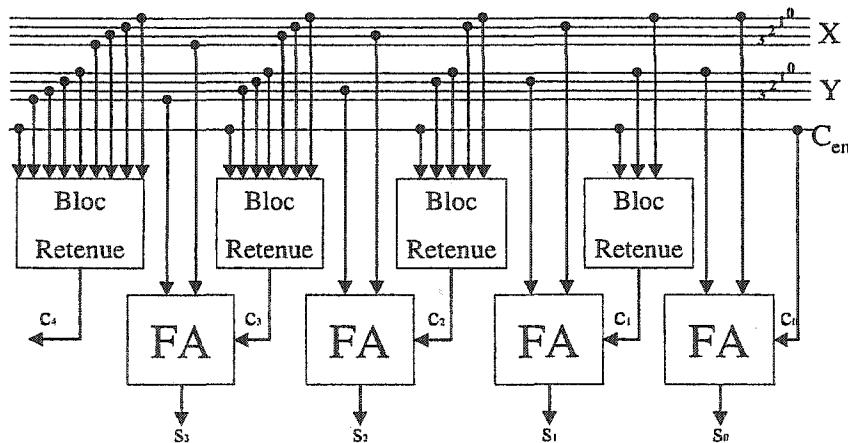

| Figure 3.9) L'additionneur à retenue propagée (RCA) .....                               | 55 |

| Figure 3.10) Délais en forme triangulaire (dénormalisation).....                        | 55 |

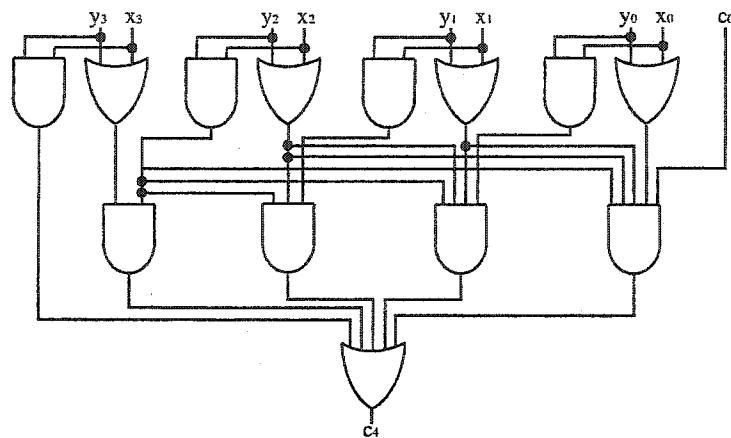

| Figure 3.11) Structure du CLA .....                                                     | 56 |

| Figure 3.12) Structure du bloc de retenue C <sub>4</sub> .....                          | 57 |

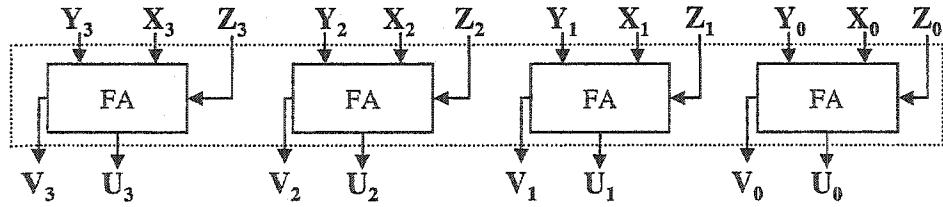

| Figure 3.13) Additionneur à conservation de la retenue (CSA).....                       | 58 |

| Figure 3.14) Schématique d'une cellule CSA modifiée (CSA 1-bit) .....                   | 58 |

| Figure 3.15) Structure de l'additionneur à saut de la retenue (4 bit blocs).....        | 59 |

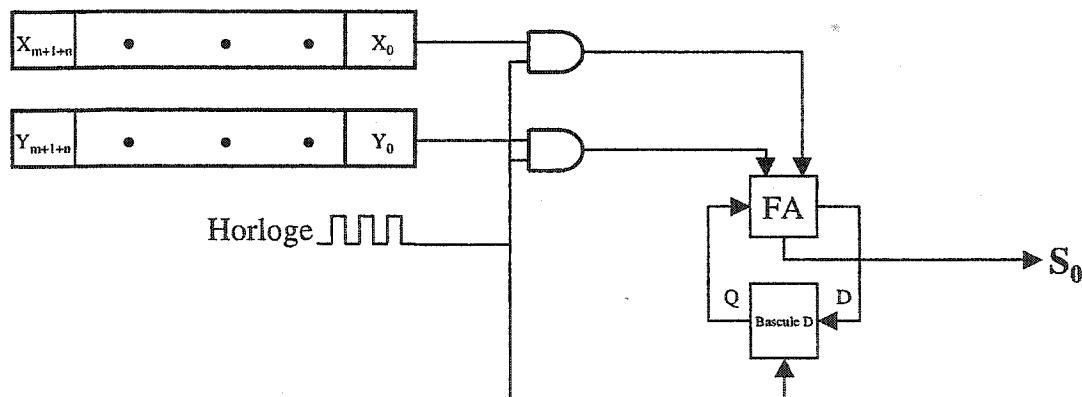

| Figure 3.16) Structure de l'additionneur sériel.....                                    | 60 |

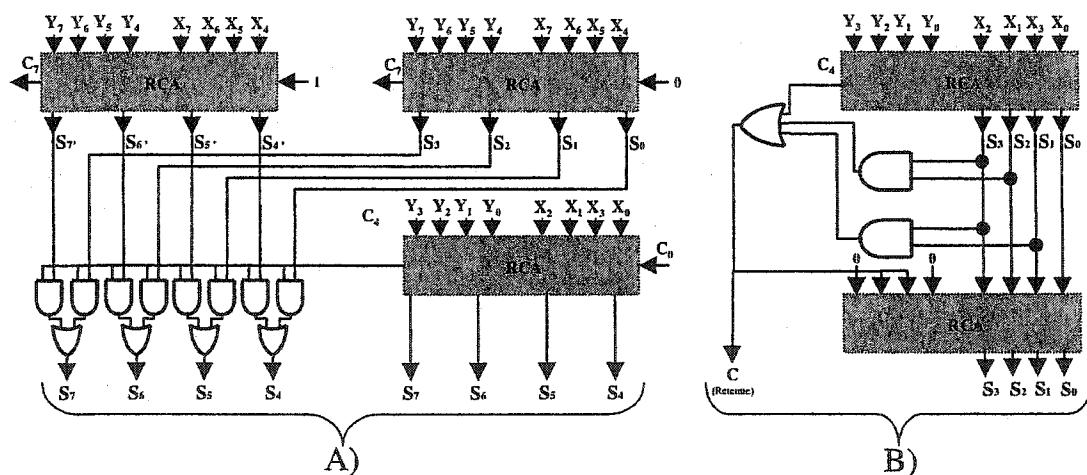

| Figure 3.17) Structure de L'additionneur : a) à saut de retenue, b) BCD .....           | 61 |

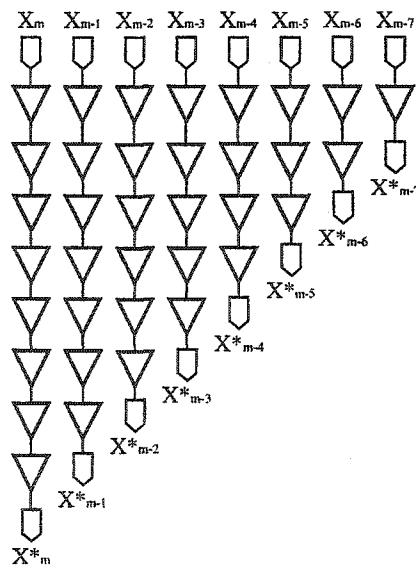

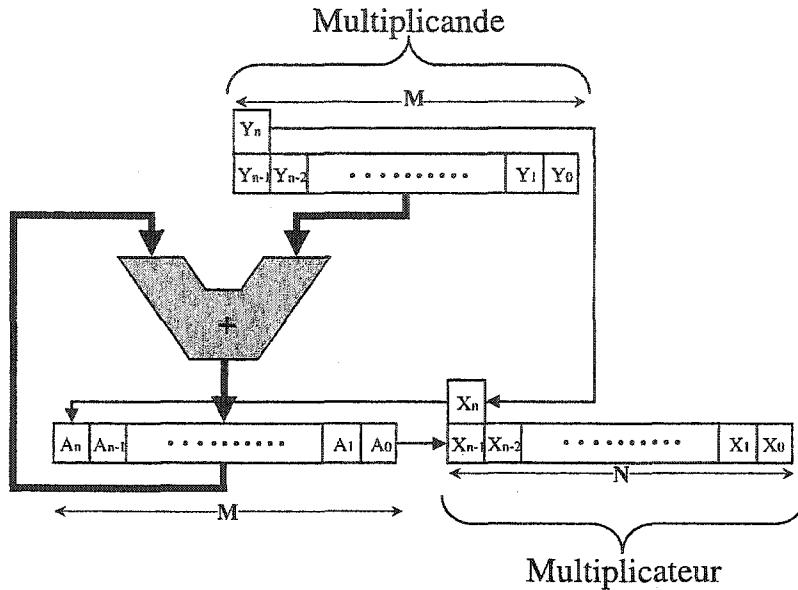

| Figure 3.18) Multiplication par accumulation partielle ( <u>Signe-module</u> ).....     | 64 |

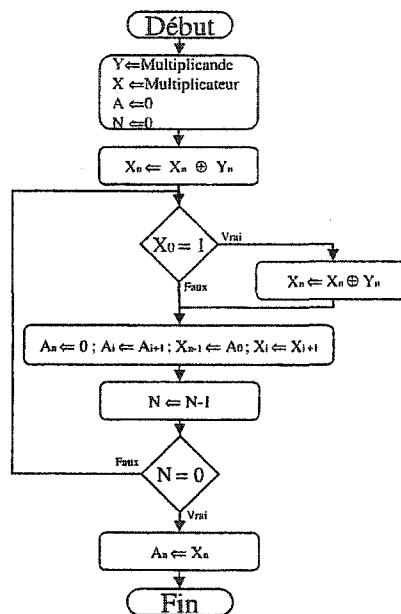

| Figure 3.19) Étapes d'une mult. par addition successif (signe-module).....              | 65 |

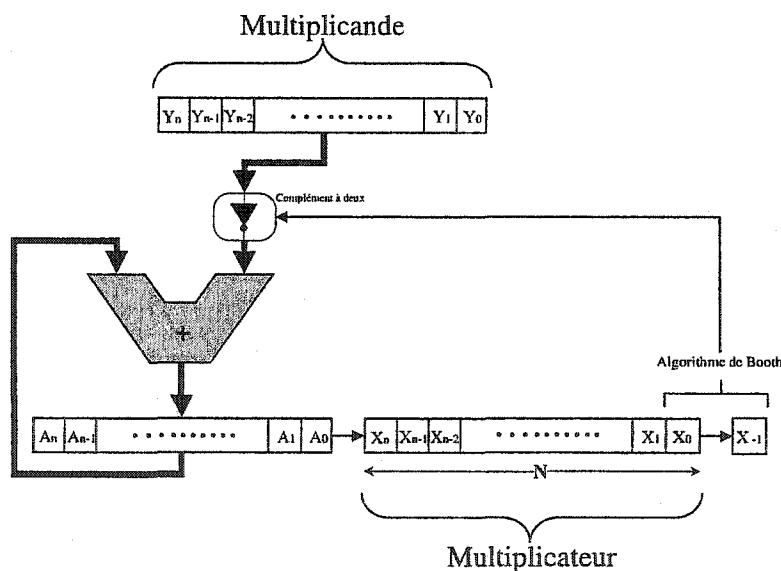

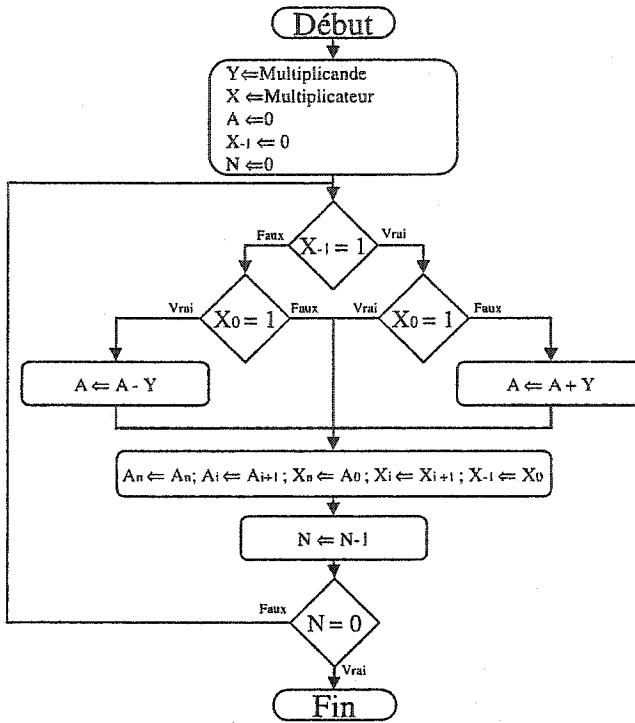

| Figure 3.20) Multiplication par accumulation partielle ( <u>Algorithme Booth</u> )..... | 66 |

| Figure 3.21) Étapes d'une mult. par addition successif (Algorithme Booth).....          | 68 |

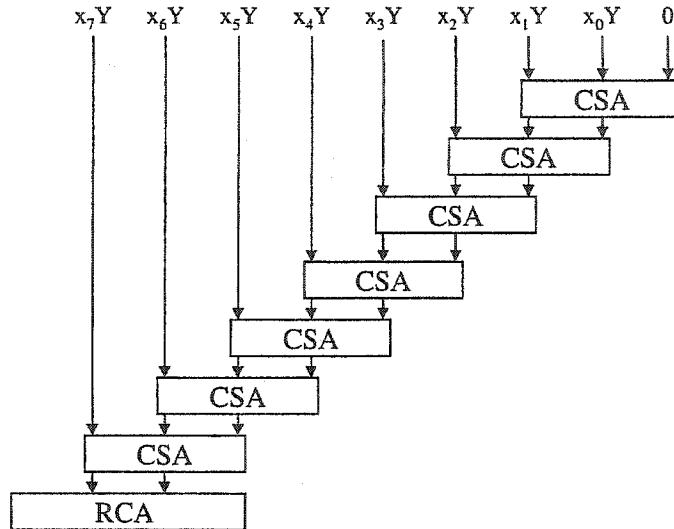

| Figure 3.22) Structure du Multiplieur Parallèle .....                                   | 69 |

---

|                                                                                    |    |

|------------------------------------------------------------------------------------|----|

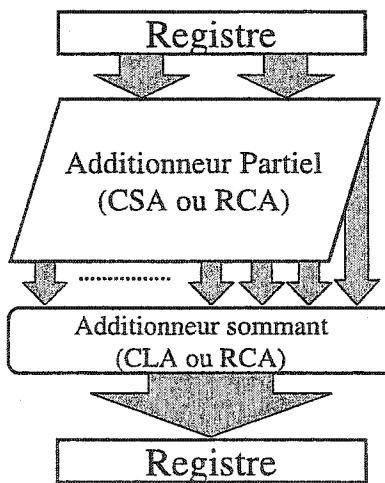

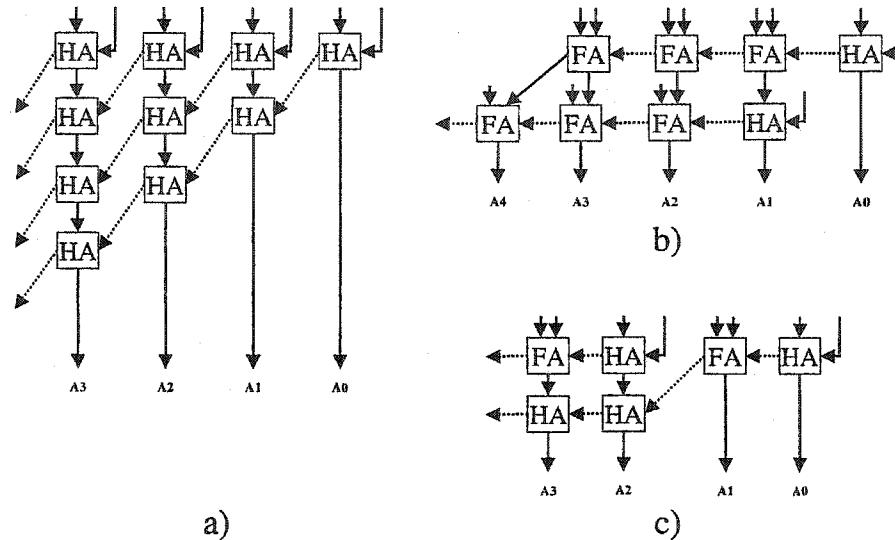

| Figure 3.23) Divers Type d'additionneur partiel.....                               | 70 |

| Figure 3.24) Structure du multiplicateur cellulaire .....                          | 72 |

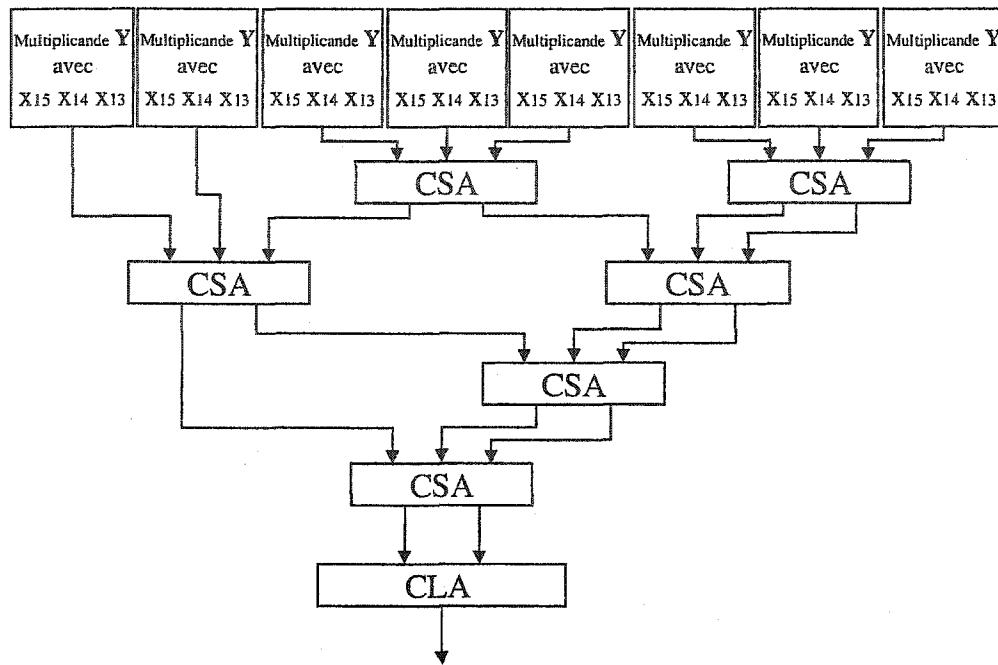

| Figure 3.25) Multiplieur Booth Modifié utilisant un arbre de Wallace .....         | 74 |

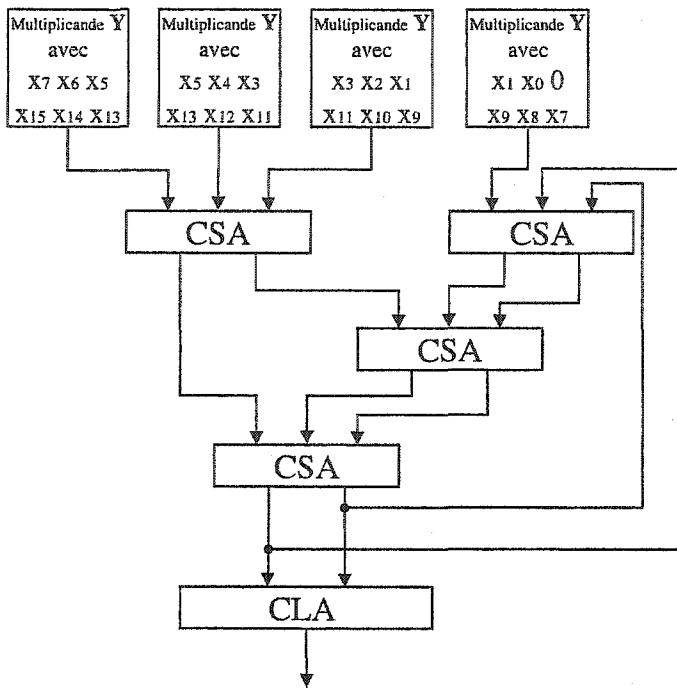

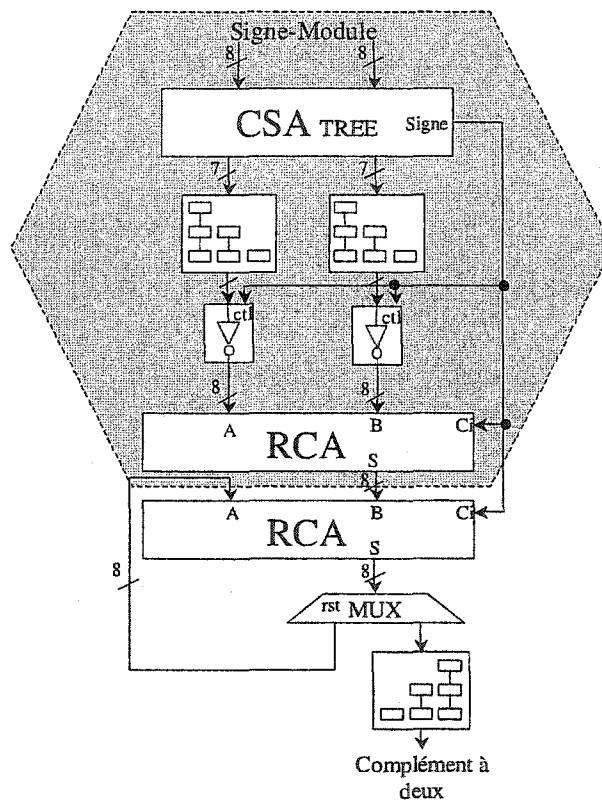

| Figure 3.26) Multiplieur Booth Modifié utilisant un arbre de Wallace récursif..... | 75 |

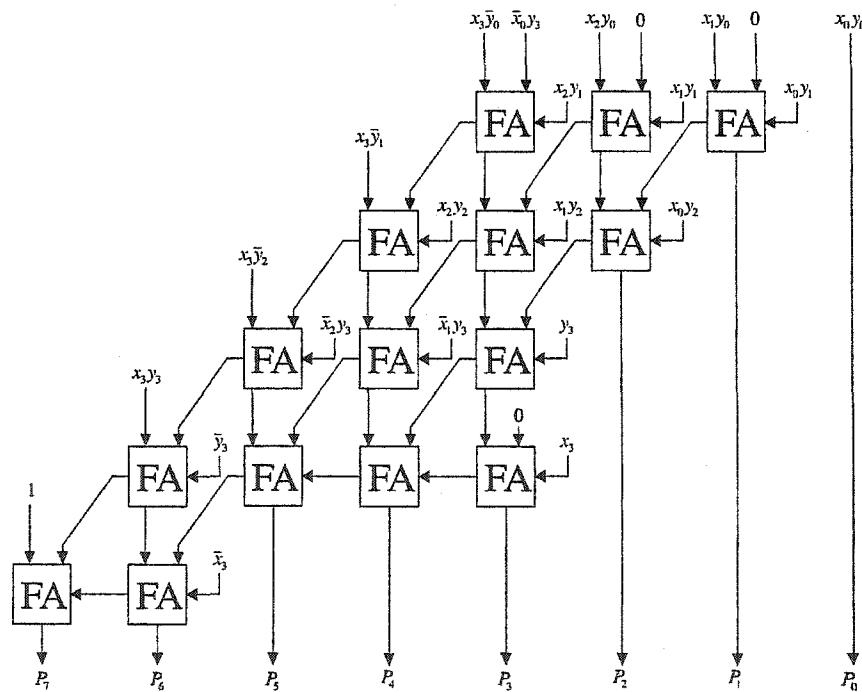

| Figure 3.27) L'algorithme de Baugh et Wooley pour un (N=M) bits.....               | 75 |

| Figure 3.28) Multiplieur complément à deux utilisant Baugh et Wooley.....          | 75 |

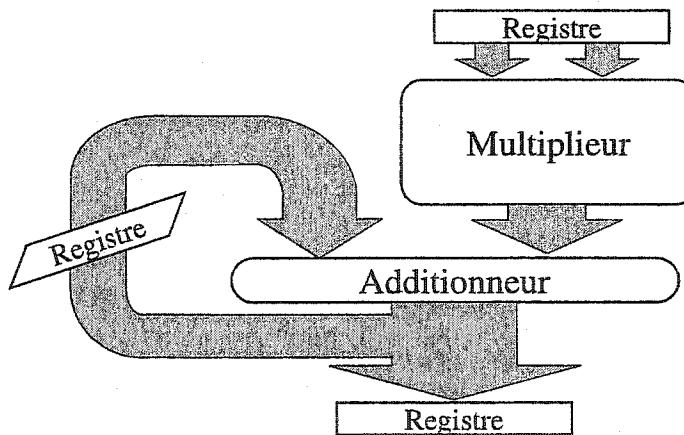

| Figure 3.29) Exemple de structure d'un multiplieur-accumulateur .....              | 75 |

| Figure 3.30) Concept d'un multiplieur-accumulateur (MAC).....                      | 75 |

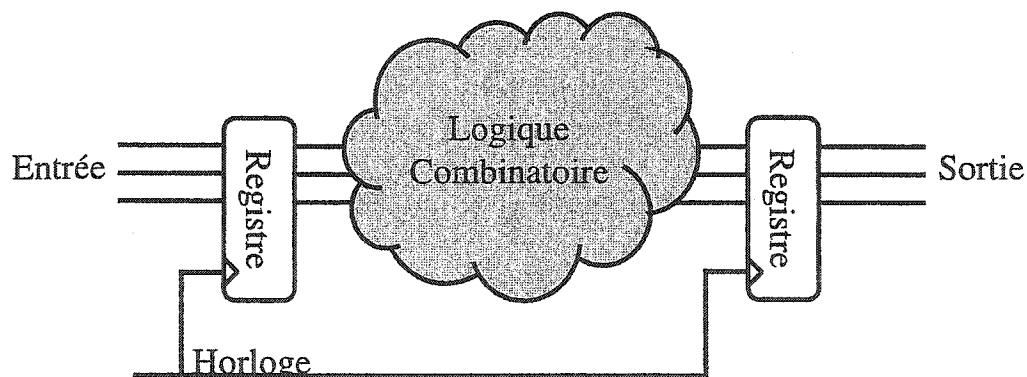

| Figure 4.1) Logique combinatoire synchrone .....                                   | 75 |

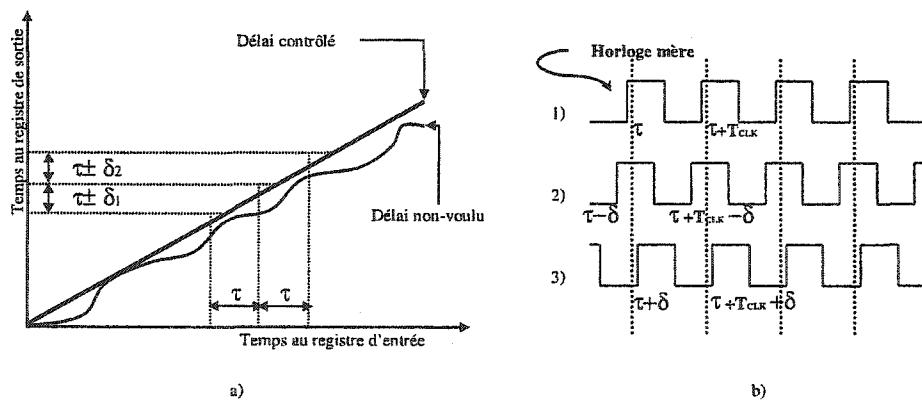

| Figure 4.2 Comparaison entre délai voulu et non-voulu, .....                       | 75 |

| Figure 4.3) Diagramme temporel d'un circuit combinatoire synchrone .....           | 75 |

| Figure 4.4) Circuit utilisant le pipeline synchrone. ....                          | 75 |

| Figure 4.5) Diagramme temporel d'un circuit combinatoire pipeline. ....            | 75 |

| Figure 4.6) Exemple de transmission à deux phases.....                             | 75 |

| Figure 4.7) Protocole mono-donné (micro-pipeline) .....                            | 75 |

| Figure 4.8) Protocole duo-donné (micro-pipeline) .....                             | 75 |

| Figure 4.9) FIFO asynchrone de type Sutherland. ....                               | 75 |

| Figure 4.10) Bascule Sutherland (a) Porte C de Muller (b) .....                    | 75 |

| Figure 4.11) Structure principale du micro-pipeline Sutherland .....               | 75 |

| Figure 4.12) Technique du pipeline par vagues. ....                                | 75 |

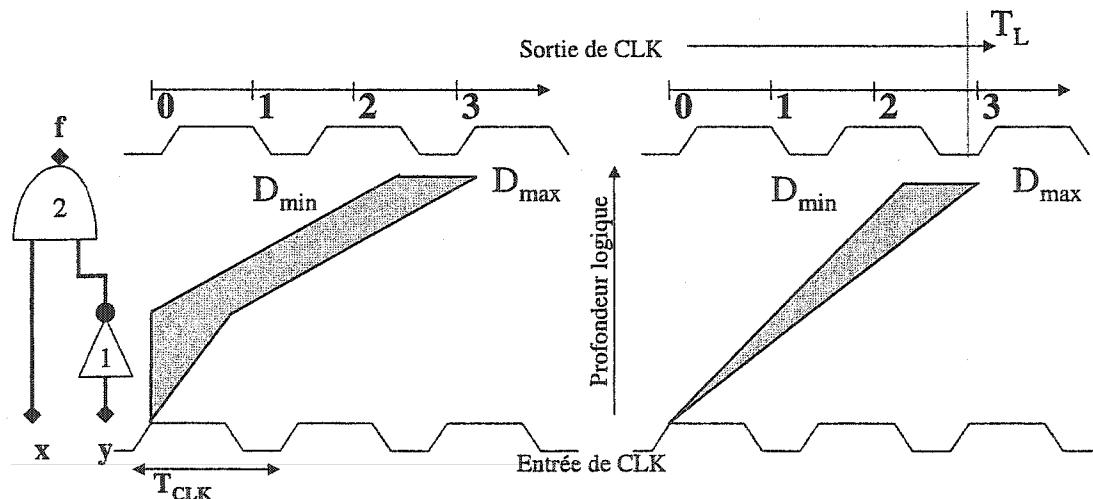

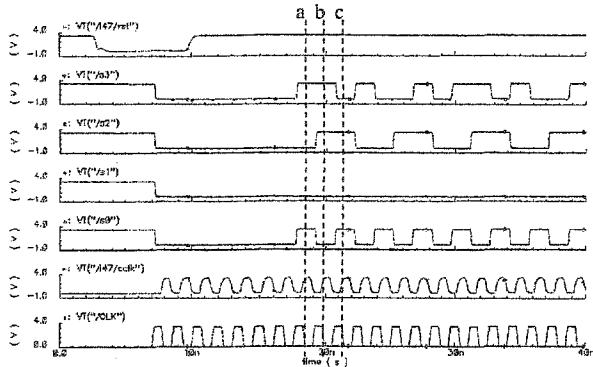

| Figure 4.13) Diagramme temporel d'un CLB pipeline par vagues.....                  | 75 |

| Figure 4.14) Type de structure rencontrée. ....                                    | 75 |

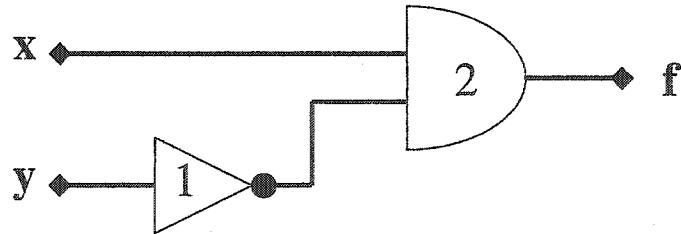

| Figure 4.15) Exemple de logique combinatoire .....                                 | 75 |

---

|                                                                              |    |

|------------------------------------------------------------------------------|----|

| Figure 4.16) Linéarisation temporel des chemins .....                        | 75 |

| Figure 4.17) Schéma temporel. ....                                           | 75 |

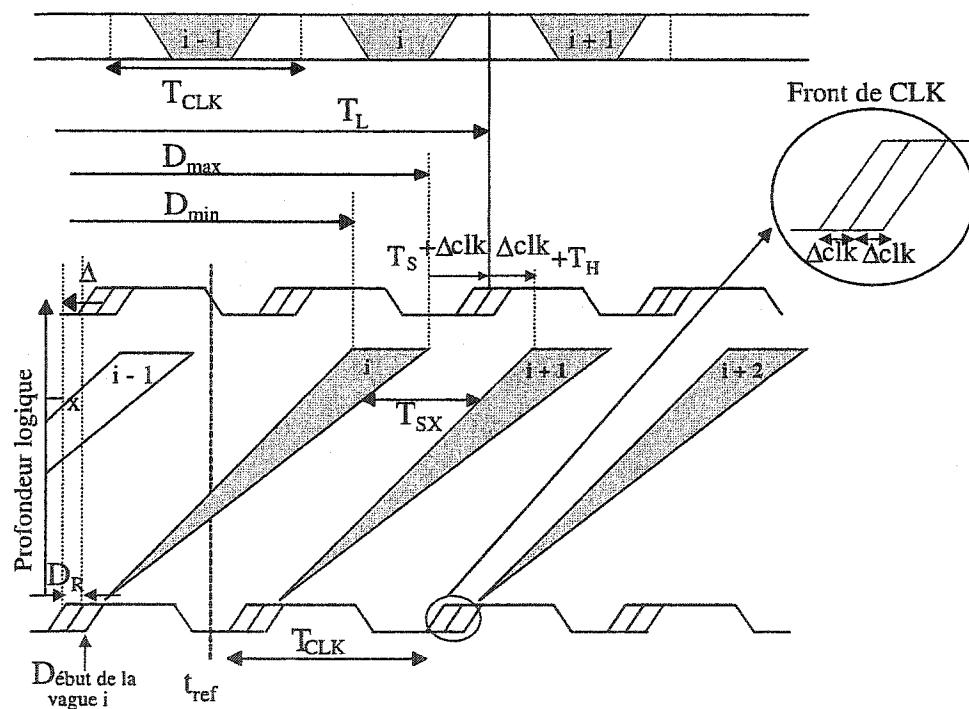

| Figure 4.18) Schéma Spatial temporel d'une CLB pipeline par vagues. ....     | 75 |

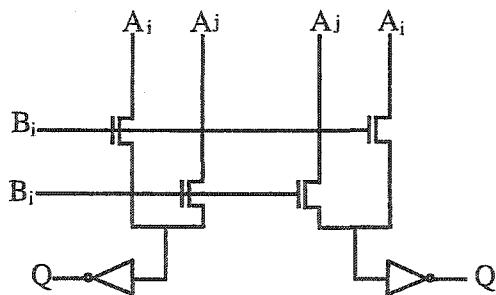

| Figure 4.19) Cellule NPCPL.....                                              | 75 |

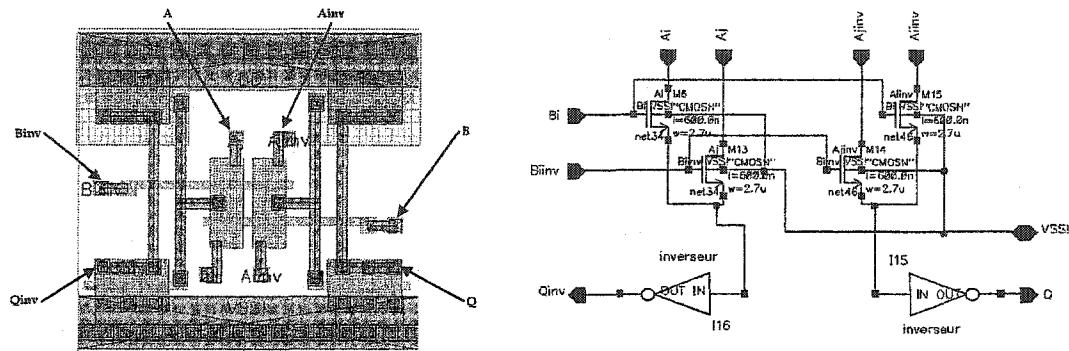

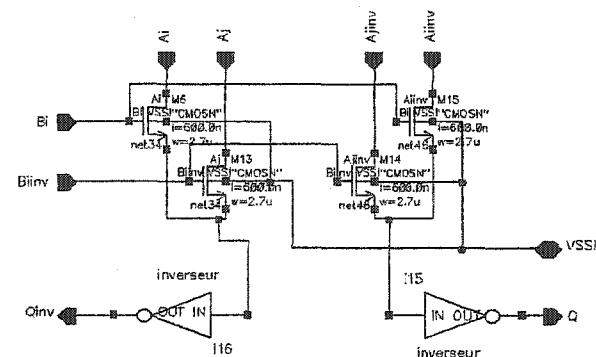

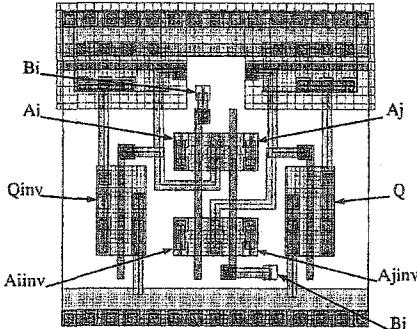

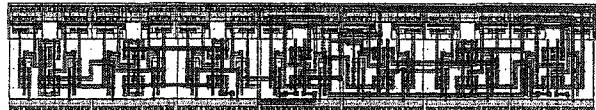

| Figure 5.1) Dessin de masque d'une cellule NPCPL et Schéma P-Spice®. ....    | 75 |

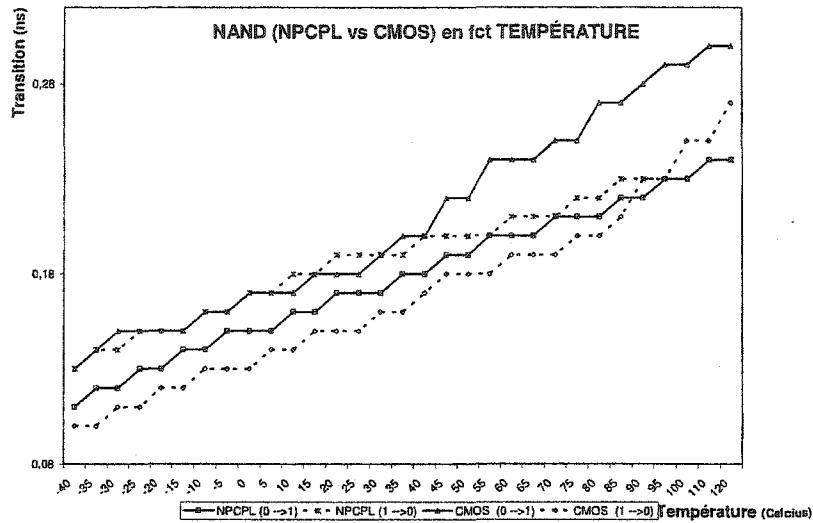

| Figure 5.2) Propagation en fonction de la température (Non-ET). ....         | 75 |

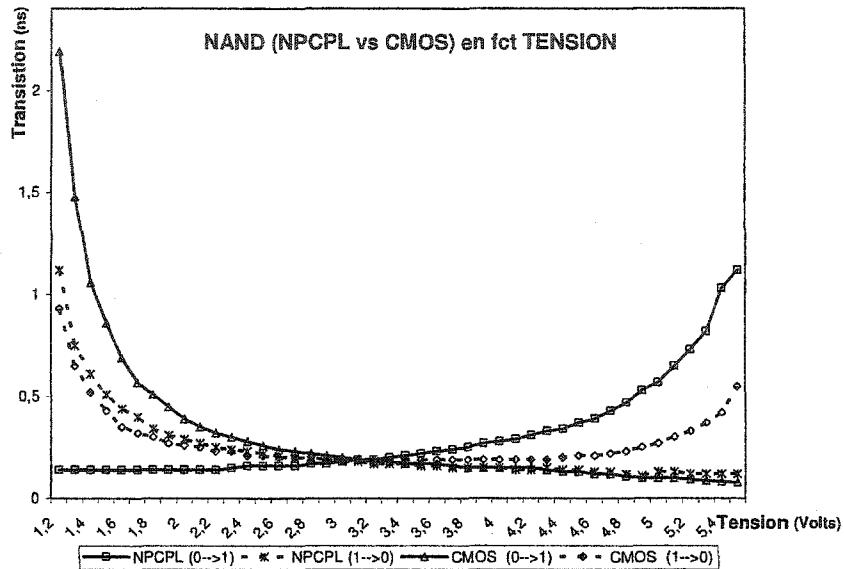

| Figure 5.3) Propagation en fonction de la tension (Non-ET). ....             | 75 |

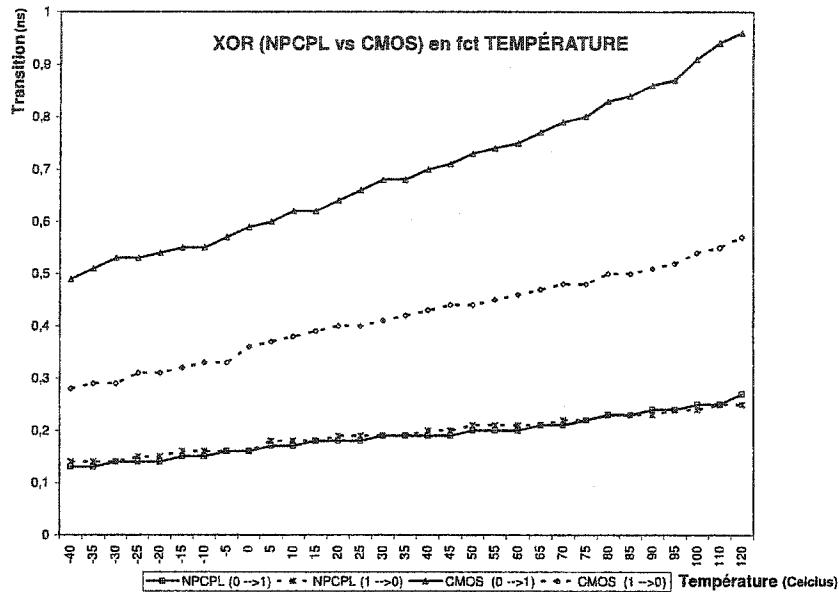

| Figure 5.4) Propagation en fonction de la température (OU-EX). ....          | 75 |

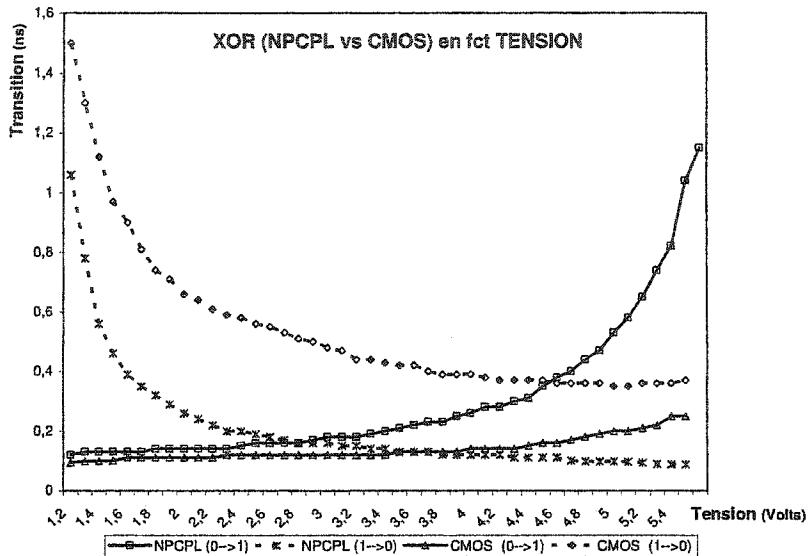

| Figure 5.5) Propagation en fonction de la tension (OU-EX). ....              | 75 |

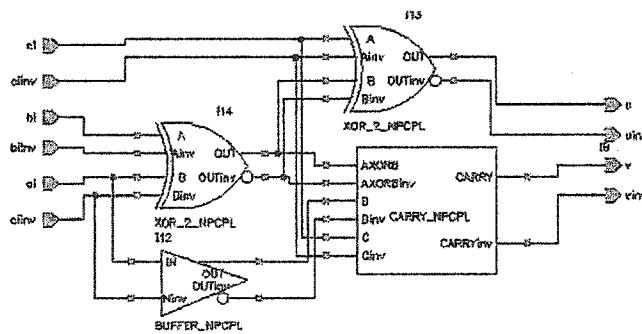

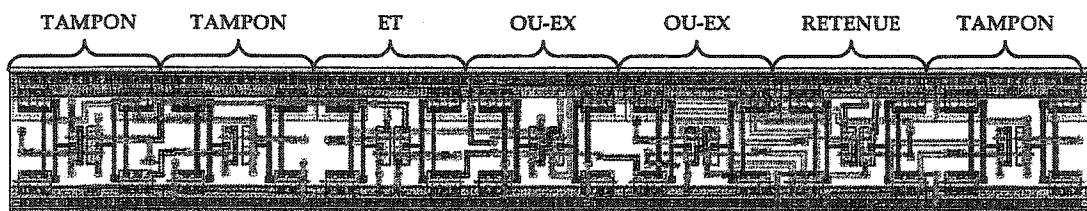

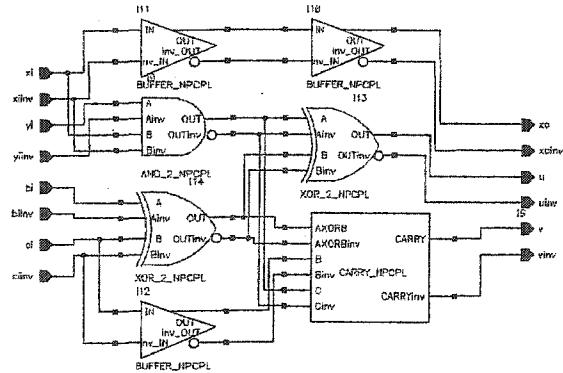

| Figure 5.6) Dessin de l'additionneur Entier (FA).....                        | 75 |

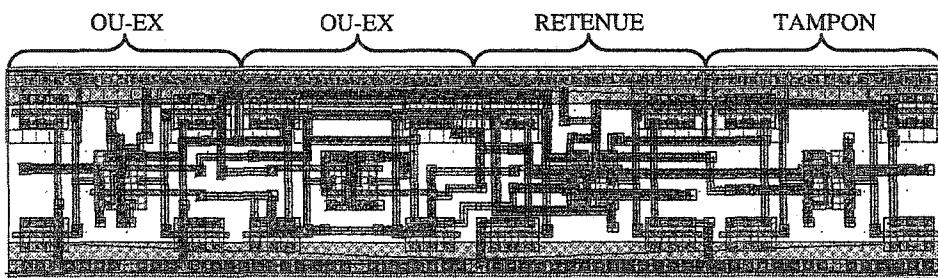

| Figure 5.7) Dessin de masque de notre addition entière.....                  | 75 |

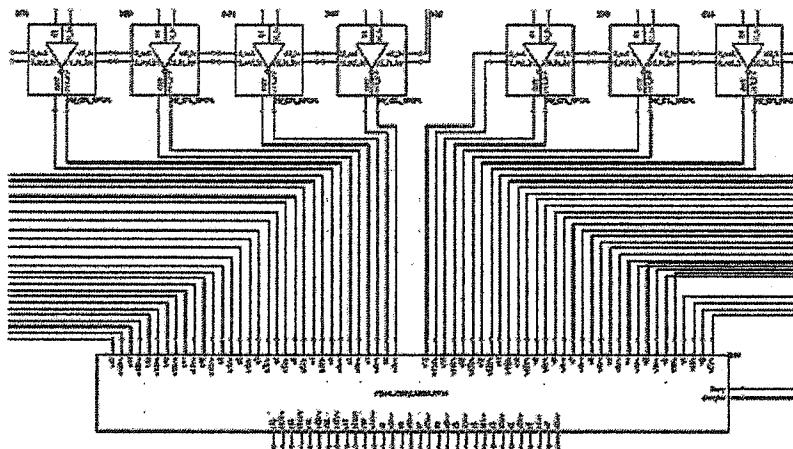

| Figure 5.8) Schématique de l'additionneur RCA. ....                          | 75 |

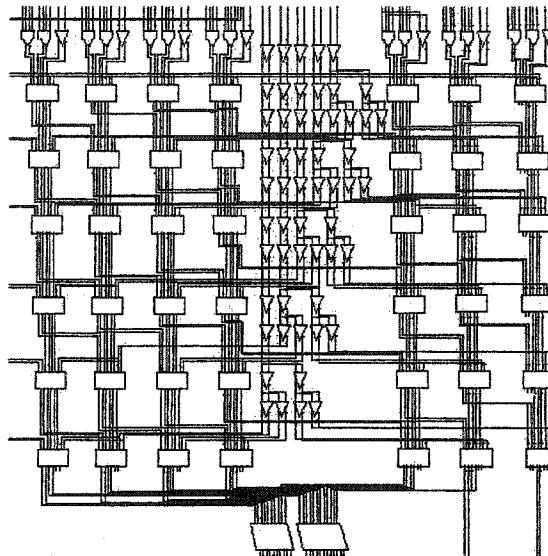

| Figure 5.9) L'additionneur RCA à l'intérieur de notre multiplieur (8x8)..... | 75 |

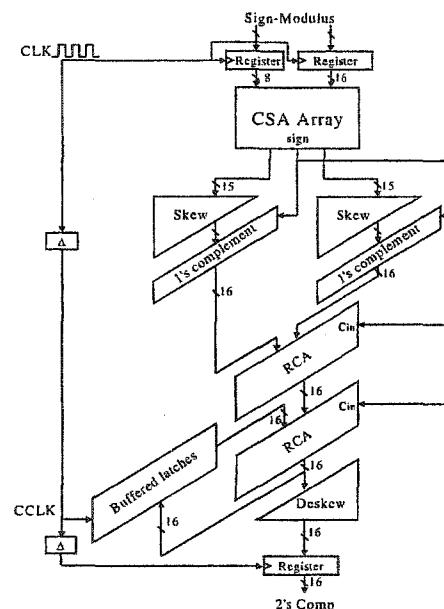

| Figure 5.10) Structure CSA+ Dessiné dans Analog Artist®. ....                | 75 |

| Figure 5.11) Dessin de masque du CSA+ conçu dans Virtuoso®.....              | 75 |

| Figure 5.12) L'arbre CSA+ et Triangle temporisateur de notre Mult 8x8.....   | 75 |

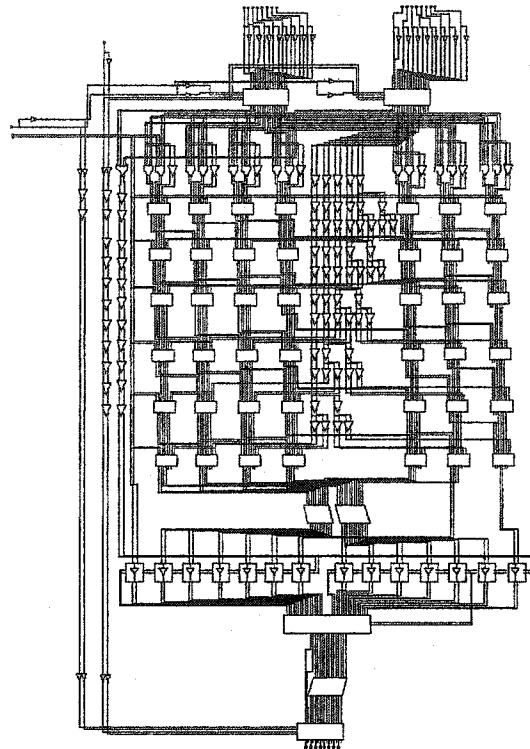

| Figure 5.13) Schématique du multiplieur (8x8).....                           | 75 |

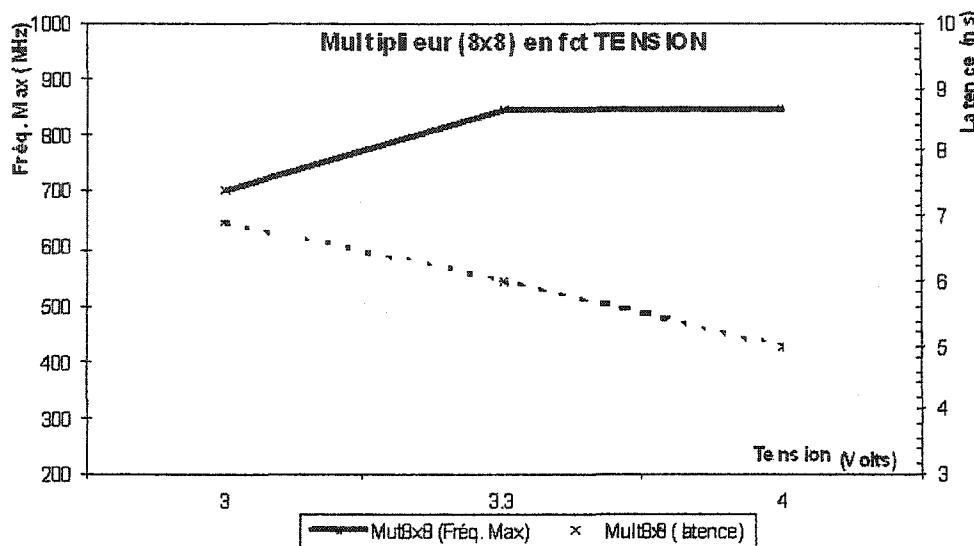

| Figure 5.14) Multiplieur 8x8 en fonction de la tension. ....                 | 75 |

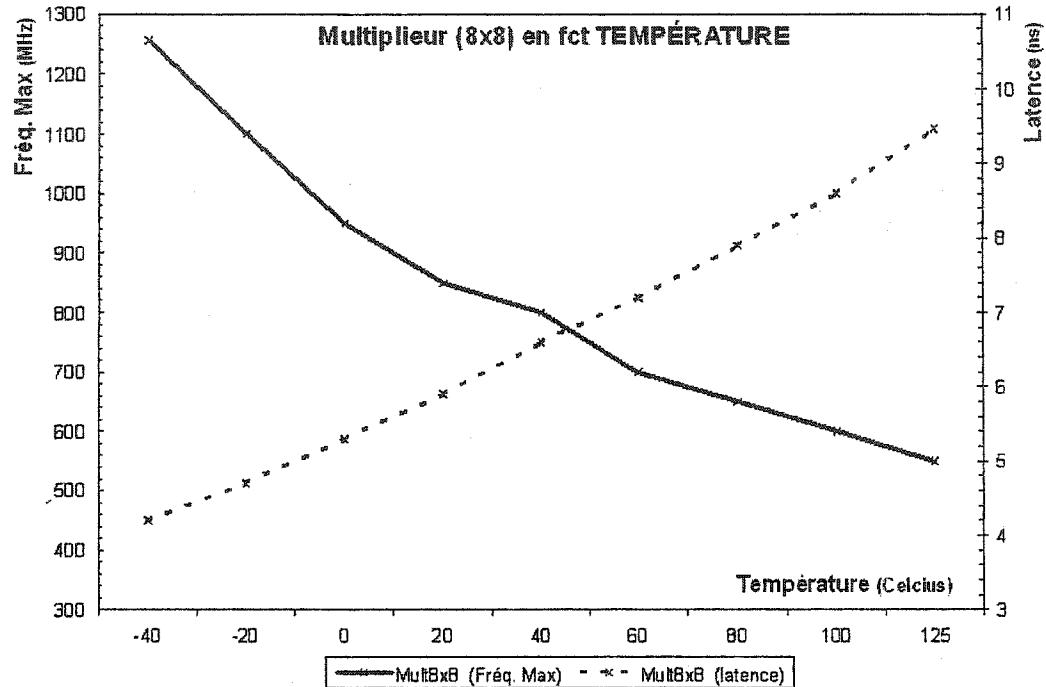

| Figure 5.15) Multiplieur 8x8 en fonction de la température. ....             | 75 |

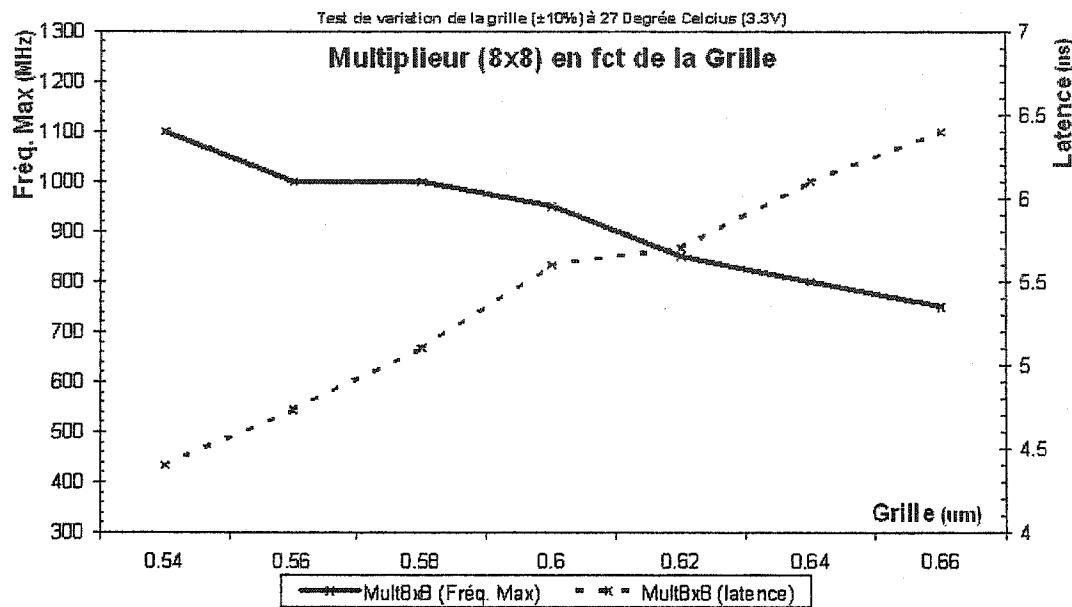

| Figure 5.16) Multiplieur 8x8 en fonction de la grille. ....                  | 75 |

| Figure 5.17) Valeur en sortie du Multiplicateur (8x8).....                   | 75 |

| Figure 5.18) Multiplieur (8x8) .....                                         | 75 |

| Figure 5.19) Multiplieur (8x8) avec broche entrée-sortie.....                | 75 |

|                                                                                                       |    |

|-------------------------------------------------------------------------------------------------------|----|

| Figure 5.20) Schématique du MAC (8x8) .....                                                           | 75 |

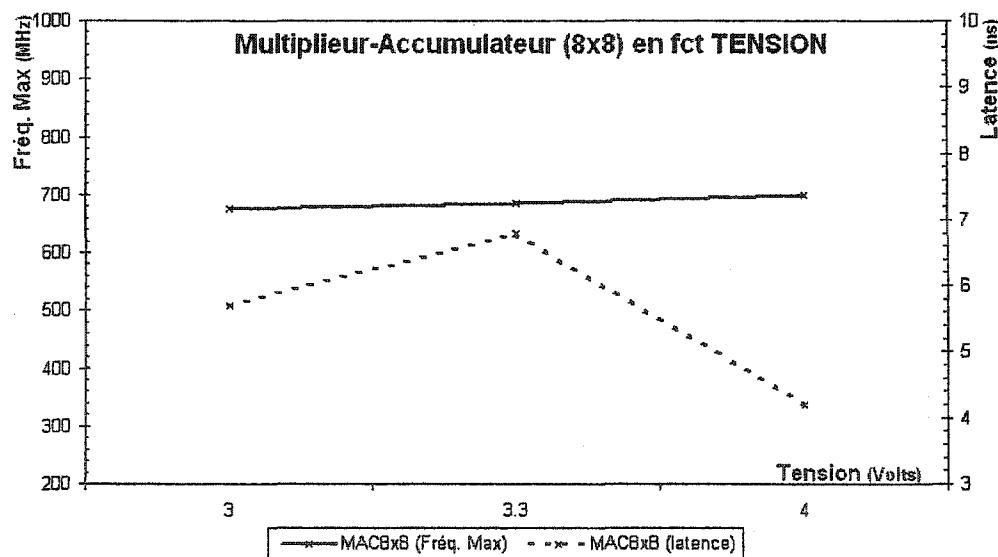

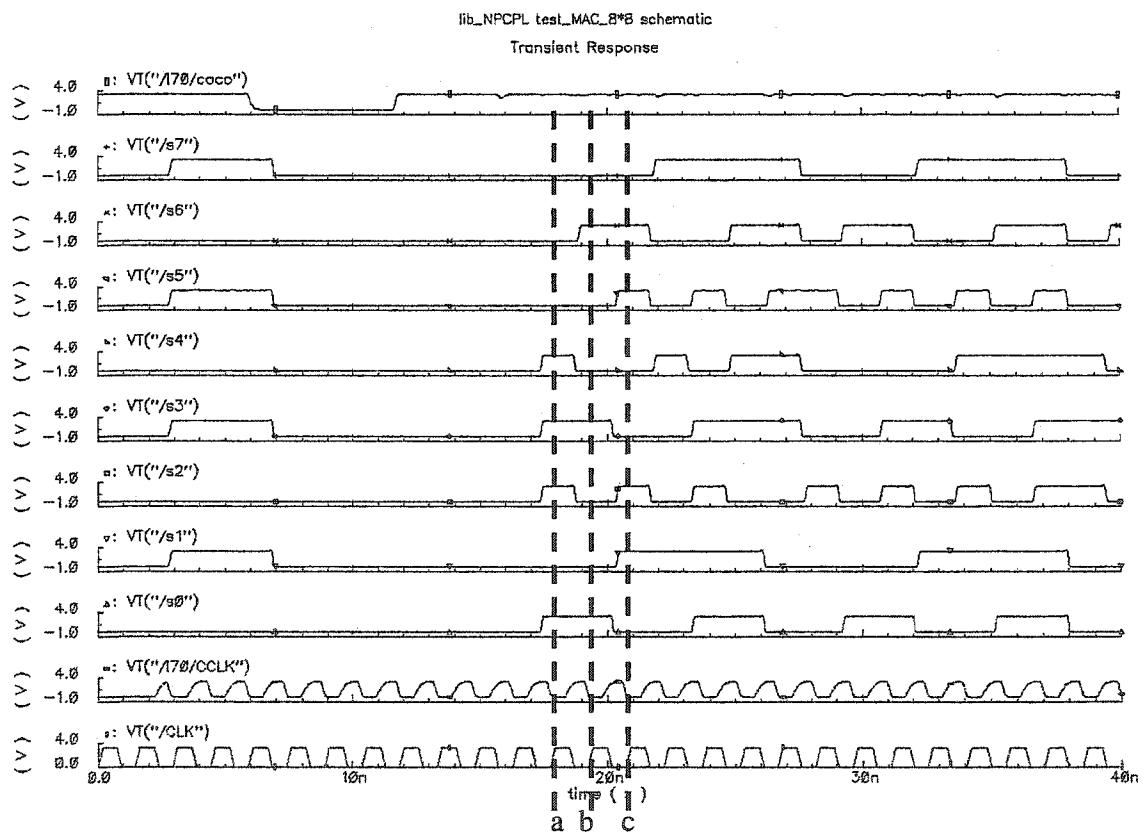

| Figure 5.21) MAC 8x8 en fonction de la tension.....                                                   | 75 |

| Figure 5.22) MAC 8x8 en fonction de la température.....                                               | 75 |

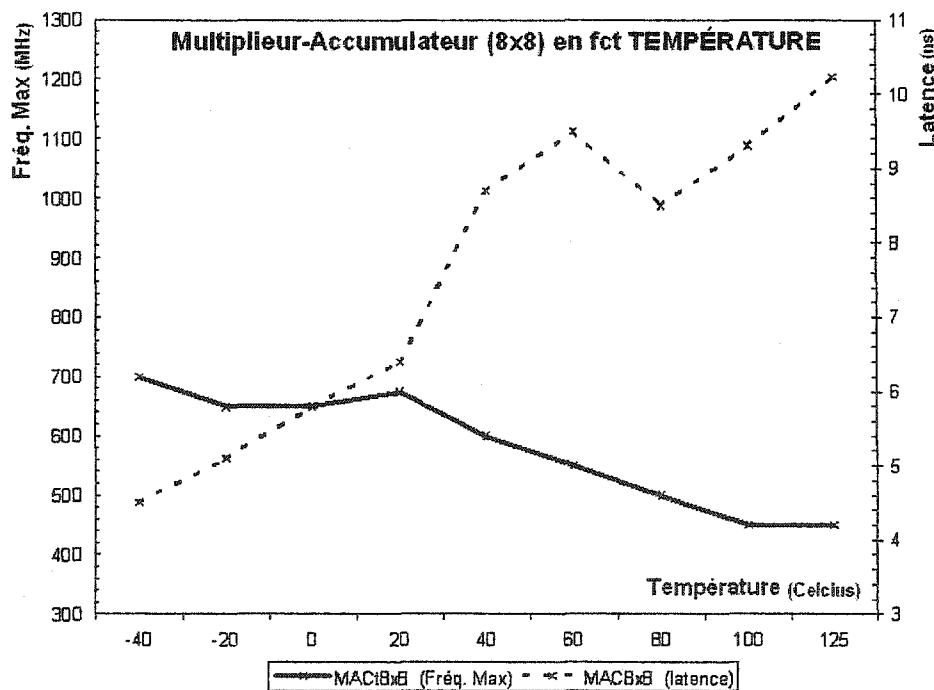

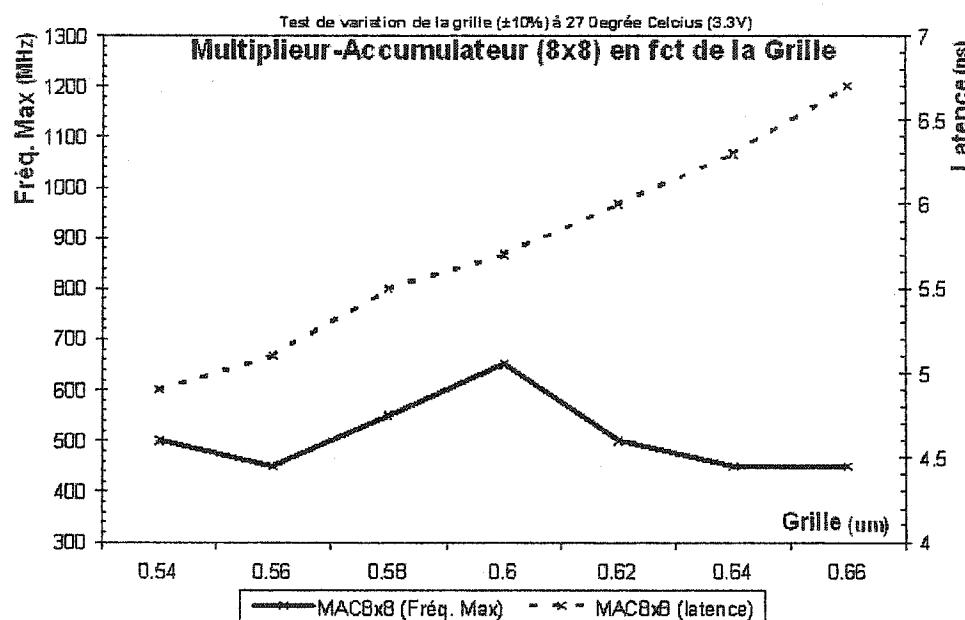

| Figure 5.23) MAC 8x8 en fonction de la grille.....                                                    | 75 |

| Figure 5.24) Valeur en sortie du MAC(8x8).....                                                        | 75 |

| Figure 5.25) MAC (8x8).....                                                                           | 75 |

| Figure 5.26) MAC (8x8) avec broche entrée-sortie .....                                                | 75 |

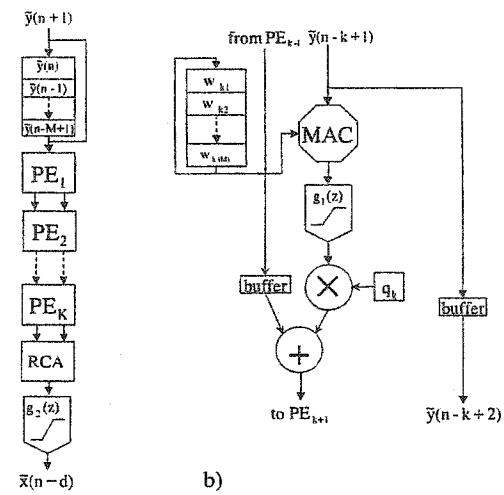

| Figure 6.1) L'architecture PL-MNN (a), Processeur élémentaire (b). ....                               | 75 |

| Figure 6.2) L'architecture PL-MNN (a), Processeur élémentaire (b) après<br>synthèse automatique ..... | 75 |

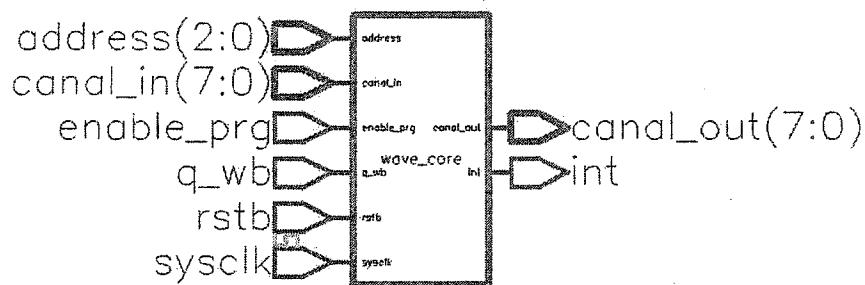

| Figure 6.3) Entrées/Sorties de l'architecture PL-MNN avec programmation<br>hors-ligne.....            | 75 |

---

## Liste des tableaux

|                                                                                |    |

|--------------------------------------------------------------------------------|----|

| Table 3.1) Opération reliée à l'algorithme de Booth (non-modifiée) .....       | 67 |

| Table 3.2) Opération reliée à l'algorithme de Booth (modifiée) .....           | 73 |

| Table 4.1) Fonction élémentaire de la cellule NPCPL. ....                      | 75 |

| Table 5.1) Résultat obtenu à Température ambiante et Procédé Normal.....       | 75 |

| Table 5.2) Dimensionnements et Puissances des U.A. fabriquée .....             | 75 |

| Table 5.3) Résultats et Tableau comparatif du MAC 8x8.....                     | 75 |

| Table 6.1) Estimation du # transistors utilisés par l'architecture PL-MNN..... | 75 |

---

## Liste des abréviations

|      |                                         |

|------|-----------------------------------------|

| ALU  | Arithmetic and Logic Unit               |

| ASIC | Application Specific Integrated Circuit |

| BER  | Bit Error Rate                          |

| CAO  | Conception Assistée par Ordinateur      |

| CCI  | Co-Channel Interference                 |

| CLA  | Carry Locking Adder                     |

| CLB  | Combinatory Logic Block                 |

| CMC  | Canadian Micro-electronic Corporation   |

| CMOS | Complementary Metal Oxide Semiconductor |

| CPL  | Complementary Pass Logic                |

| CSA  | Carry Save Adder                        |

| DPTL | Differential Pass Transistor Logic      |

| DPTL | Double Pass Transistor Logic            |

| FA   | Full Adder                              |

| IP   | Intellectual Property                   |

| ISI  | Inter Symbol Interferences              |

|        |                                                    |

|--------|----------------------------------------------------|

| ITGE   | Intégration à Très Grande Échelle                  |

| LSB    | Least Significant Bit                              |

| LSSI   | Laboratoire de Signaux et Systèmes Intégrés.       |

| MSB    | Most Significant Bit                               |

| NPCPL  | Normal Process Complementary Pass transistor Logic |

| PAM    | Pulse Amplitude Modulation                         |

| PE     | Processeur Élémentaire                             |

| PL-MNN | Piecewise Linear Multi-layer Neural Network        |

| PL-RNN | Piecewise Linear Recursive Neural Network          |

| QAM    | Quadratic Phase Amplitude Modulation               |

| RCA    | Ripple Carry Adder                                 |

| SCM    | Société Canadienne de Microélectronique            |

| SOC    | System On Chip                                     |

| TPL    | Tree Pass Logic                                    |

| VHDL   | VHSIC Hardware Description Language                |

| VLSI   | Very Large Scale Integrated                        |

| VHDL   | VHSIC Hardware Description Language                |

| VHSIC  | Very High Speed Integrated Circuit                 |

| WTGL   | Wave pipeline Transmission Gate Logic              |

---

# 1 Introduction

Les communications numériques se sont développées de façon phénoménale au cours des dernières années. Que l'on parle de transmissions par câble ou sans fil, les applications développées demandent de plus en plus de bandes passantes ce qui amène plusieurs problèmes dans la chaîne de transmission.

Tout d'abord, les récepteurs et les émetteurs doivent être en mesure de traiter un débit élevé d'information. À l'heure actuelle, il est facile de parler de transmissions approchant les 10Gbps sur les fibres optiques et les communications à 40Gbps sont presque une réalité sur silicium. Le traitement de l'information à ces débits constitue un véritable défi.

Pour les communications sans fils, les débits standard de transmission de la nouvelle génération seront de 2-3 Mbps. Les problèmes alors rencontrés sont différents. Lorsque les signaux transitent dans l'air, la durée des symboles transmis est allongée ce qui crée un chevauchement ou interférence entre les symboles (*ISI : Inter Symbol Interference*) [PRO95]. Un phénomène semblable se produit sur les fibres optiques; il s'agit de la diffusion de la lumière qui amène les signaux à utiliser un spectre de fréquence plus large que celui qui leur est attribué et à empiéter sur les canaux de communication de fréquences voisines que l'on nomme interférence entre les canaux (*CCI:Co-Channel*

---

*Interference). [CAM98]*

Afin de combattre ces altérations des transmissions et pour permettre une qualité de service acceptable, les principales méthodes de corrections d'erreur sont le codage et l'égalisation de canaux.

Le codage (Reed-Solomon, Viterbi, BCH, etc...) consiste à créer une redondance dans le message transmis afin de détecter et corriger les éventuelles erreurs à la réception. De façon générale, les codes qui possèdent un taux de redondance élevé, c'est-à-dire que le rapport entre le nombre de bits d'information et le nombre de bits transmis est faible, sont aptes à détecter et à corriger un plus grand nombre d'erreurs donc ayant une distance de Hamming élevée. Comme nous l'avons spécifié, l'information est diluée dans le message transmis, se traduisant donc par une perte de la bande passante allouée.

L'égalisation de canaux, quant à elle, consiste à annuler les effets du canal afin de réduire les ISI et CCI. Il s'agit d'un traitement numérique qui consiste à filtrer le signal reçu avec la réponse impulsionnelle inverse du canal. Dans la plupart des cas, comme la réponse impulsionnelle du canal est souvent inconnue, l'égaliseur est adaptatif.

L'implantation d'algorithme de traitement de signaux nécessite une plus grande quantité de calculs justifiés d'abord par la classe du problème ce devant d'être résolue. C'est-à-dire, quel médium et quel type de transmission aura-t-il lieu. Et d'autre part, la complexité des calculs devant être effectués par l'algorithme à être implanté. L'implantation d'une architecture au niveau ITGE pour le traitement numérique apporte de nouveaux problèmes qui ne sont pas rencontrés lorsque le traitement est effectué au niveau logiciel (*software*) ou

utilisant des architectures préfabriquées (DSP,  $\mu$ -contrôleur).

Dans cette étude, nous évaluerons d'une part la capacité des différents égaliseurs pouvant être implantés pour des applications à haut débit tel les communications par fibres optiques. Et d'autre part nous évaluerons les techniques d'augmentation du débit pouvant être implantées sur nos unités arithmétiques et logiques.

## 1.1 Problématique

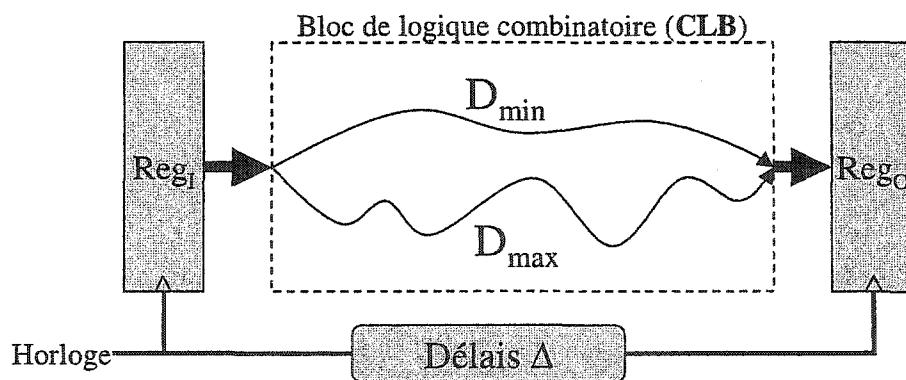

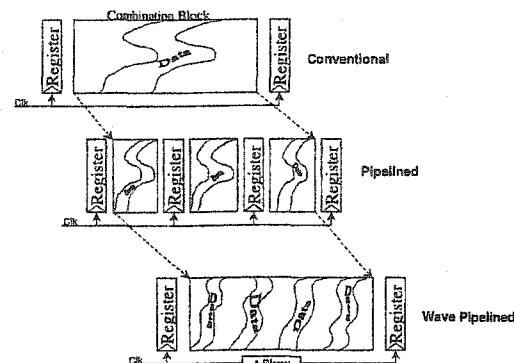

La méthode du pipeline est une méthode d'augmentation du débit à l'intérieur même d'un bloc de logique combinatoire (CLB). Cette méthode devient nécessaire lorsque les techniques conventionnelles, comme la parallélisation où la modification de la structure de l'algorithme ne permet plus d'augmenter le débit de l'architecture proposée. L'idée principale derrière cette étude est l'application du pipeline par vague pour la conception d'une architecture dédiée à l'égalisation de canaux.

L'utilisation d'une technique comme le pipeline conventionnel permet d'augmenter le débit d'une architecture sans nécessairement devoir diminuer l'échelle de la technologie qui sera choisie. Cependant, son utilisation a comme conséquence néfaste d'augmenter énormément les problèmes de synchronisations de l'horloge et la surface d'intégration. Ainsi, l'utilisation d'une technique d'augmentation de débits ne s'applique pas toujours. On doit d'abord vérifier s'il est réellement nécessaire d'augmenter la vitesse de traitement. Il existe des domaines non axés sur la rapidité de traitement des données, comme par

---

exemple, le domaine de la spectrométrie. Préférant ainsi des traitements portés sur la qualité (précision) des données échantillonnées que sur la quantité (rapidité). Ceci dit, il existe d'autres domaines par exemple, la télécommunication où la demande de vitesse est en constante évolution. Dès lors, nous tentons constamment d'augmenter le débit des architectures dédiées au traitement du signal en utilisant des algorithmes de plus en plus complexes par conséquent une augmentation assurée du nombre de calculs. Nous croyons fortement que l'utilisation d'algorithmes complexes sera de plus en plus nécessaire. Cette demande aura comme objectif d'augmenter substantiellement le débit de l'information transmise tout en compensant pour les limites de transmissions reliés au milieu physique du canal. Néanmoins, cette complexité algorithmique aura un lien direct avec l'augmentation de la latence au niveau architectural, plus particulièrement lors d'une intégration à très grande échelle, causée en général par les unités arithmétiques (multiplieurs, diviseurs, etc.) devant être utilisées. Alors, l'utilité de développer une architecture intégrée à très grande échelle devient une nécessité en contraste avec une implantation à l'intérieur d'architecture généralisée comme les DSP (*Digital Signal Processing*).

Les méthodes utilisant les techniques du pipeline ont comme rôle principal d'augmenter le débit à l'intérieur même de l'architecture lors d'intégration sur silicium. En effet, cette optimisation pointe directement au problème principal de limitation du débit en modifiant principalement les blocs de logique combinatoire constituant le berceau de l'engorgement des données. L'étude portera sur plusieurs types de pipeline, pour permettre de faire un choix éclairé d'une technique d'augmentation du débit pouvant être appliquée à notre

architecture.

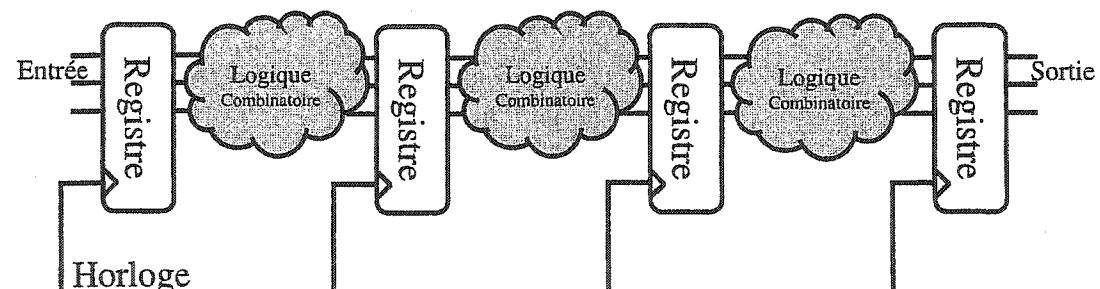

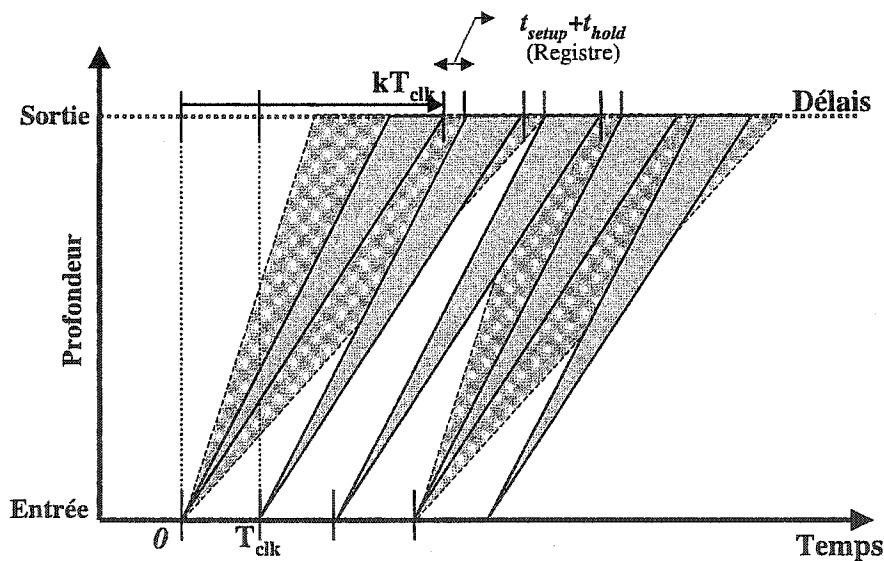

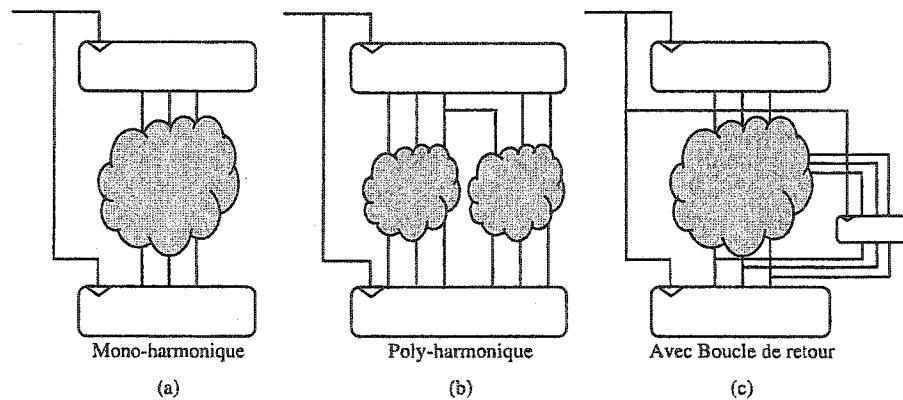

Les types de pipeline les plus connus sont : le pipeline conventionnel [ELO98], [GHO94], [JOU97], le micro-pipeline [BAR97], [DAY95], [NOO97], [SUT89], [TAY98], le pipeline Domino [HSI95], [LIE92], [WEI95], et le pipeline par vagues (synchrone et asynchrone) [BUR98], [CHU96], [COT96], [DAE98], [GHO95], [GRA92], [GRA93], [HAU98], [HUG91], [MAR97], [MAS98], [NOW94], [NOW94b], [NOW95], [NOW95b], [WON93]. En premier lieu, le pipeline conventionnel est constitué de plusieurs étages de registres à l'intérieur du bloc de logique combinatoire (CLB), ceci permet de stabiliser les données en introduisant des éléments synchrones (Temporisateur ou registre) à l'intérieur du CLB. En effet, la méthode du pipeline divise par un nombre N d'étages le bloc combinatoire et par le fait même augmente le débit par un facteur N. Cependant, l'utilisation du pipeline conventionnel emmène aussi une augmentation de surface et de puissance. De plus, il augmente le nombre de cycle total et le réseau d'horloge peut devenir une contrainte significative. Malgré ces défauts, il constitue toujours une excellente technique de maximisation du débit.

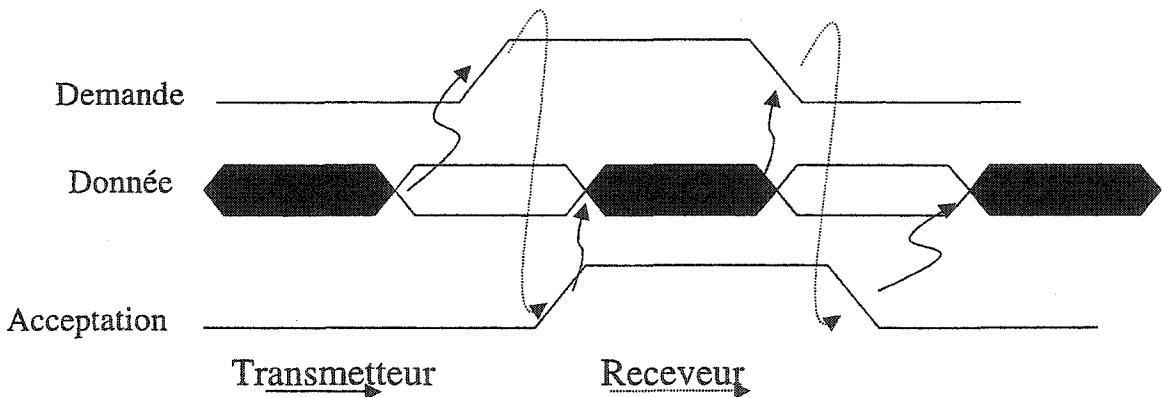

Le micro-pipeline a pour but la transmission de donnée asynchrone. C'est-à-dire, il est conçu sur le principe du receveur/transmetteur. L'avantage de ce type d'augmentation du débit réside dans l'application de transmission de donnée sans transmettre l'horloge, ce qui permet d'éviter une diminution de la pente et du déphasage temporel (*clock skew*) de l'horloge pendant la distribution de celle-ci. Le nombre d'étages transmis de cette façon permet des vitesses quasi comparables au pipeline conventionnel, sans les problèmes reliés

à la distribution de l'horloge.

Le pipeline Domino est constitué de portes logiques dynamiques de type Domino. Ce type de portes permet d'utiliser  $N+4$  transistors contrairement à une porte statique CMOS utilisant  $2N$  transistors où  $N$  représente le nombre de portes statiques de type P ou N qui seraient normalement utilisées [SAV88]. Sa consommation de puissance est semblable aux portes logiques statiques. Cependant, le principe de fonctionnement reste très complexe.

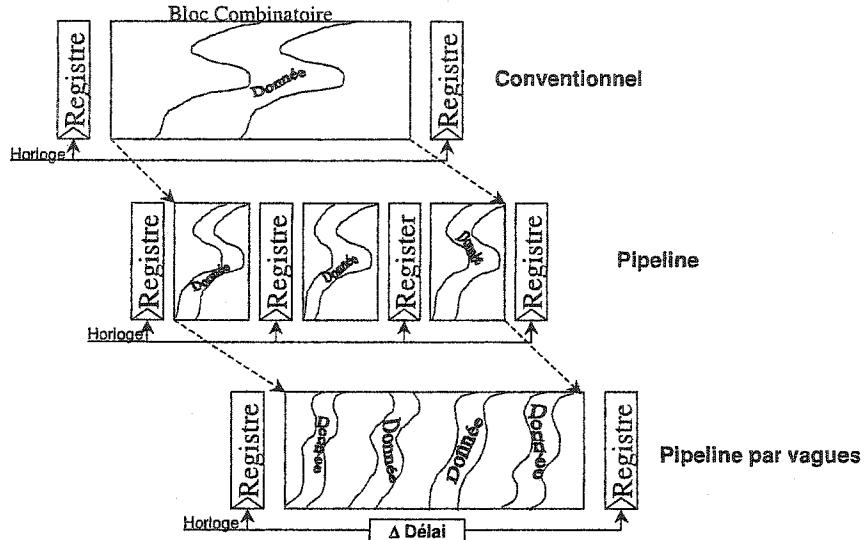

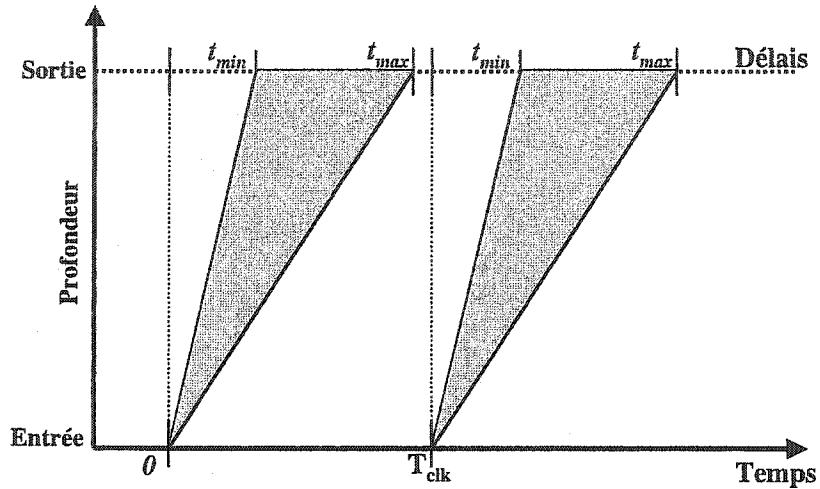

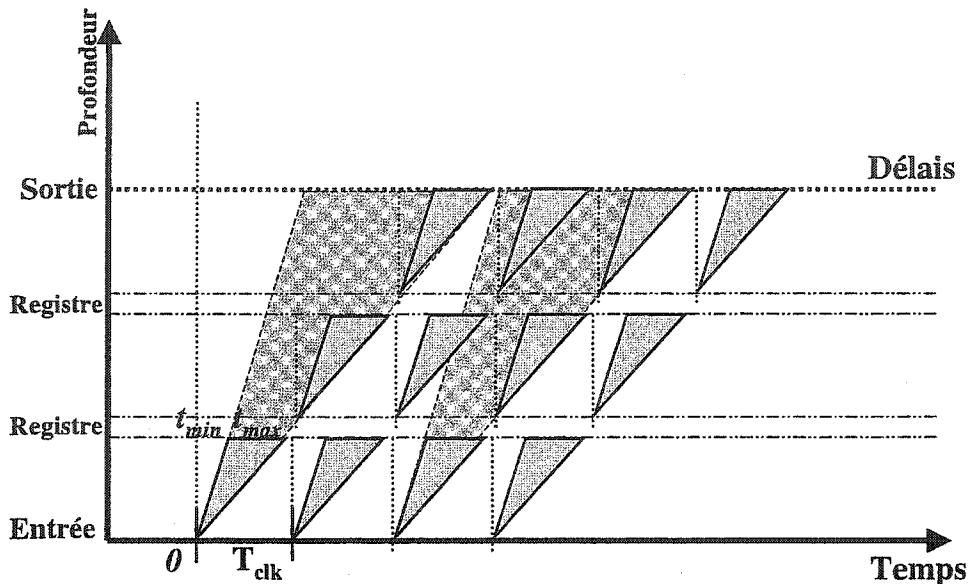

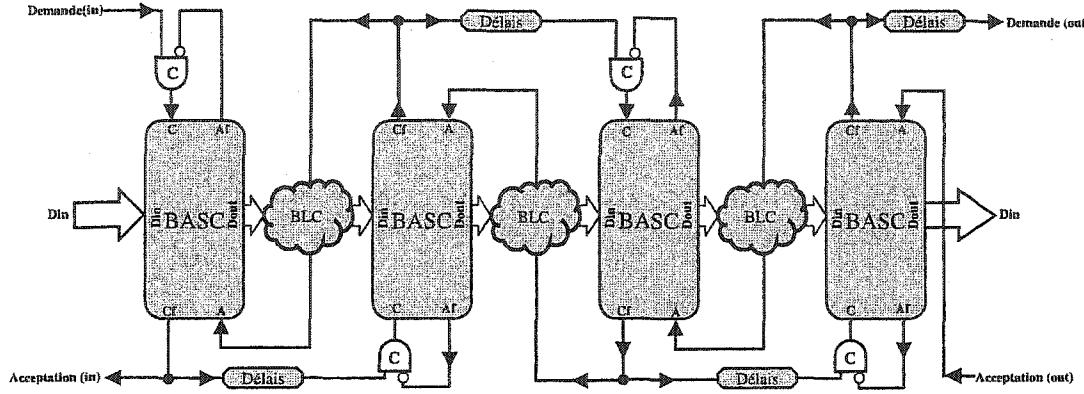

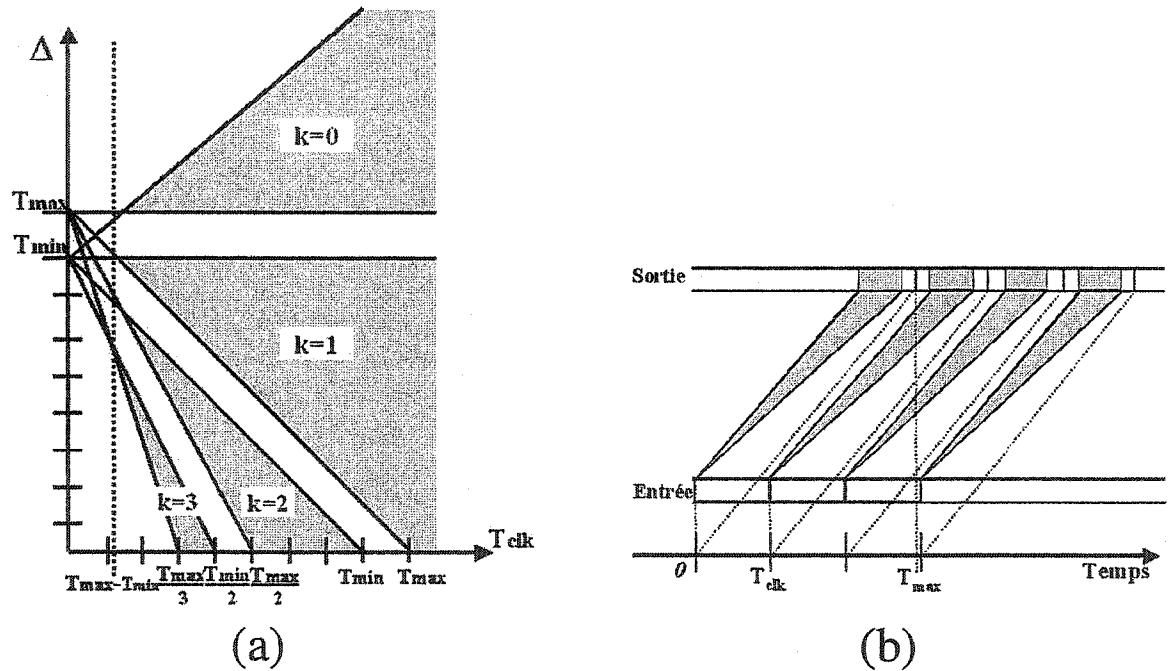

Le pipeline par vagues, a comme principe d'introduire à l'intérieur du CLB, un nombre de vagues de données supérieur au délai de propagation à travers la logique combinatoire ceci en diminuant la période de l'horloge mère entre les deux registres principaux sans nécessairement utiliser de registre interne. Ainsi, une diminution concrète de surface d'intégration et une augmentation du débit liée aux nombres de vagues sont introduites. Cependant, cette méthode d'implantation demeure toutefois complexe et demande d'aller aux limites de la technologie d'intégration. Plus spécifiquement, au niveau des délais des transistors lors d'ajustements de précision (dimension des transistors) et lors des ajustements grossiers (longueurs des chemins). La figure 1.1 représente grossièrement les différences principales entre une logique combinatoire RTL conventionnelles vis-à-vis aux logiques combinatoires RTL pipeline conventionnel et pipeline par vagues.

Figure 1.1) Concept du pipeline par vagues

En bref, les deux types (conventionnel et micro) cherchent à diminuer le trajet de la donnée la plus longue du bloc de logique combinatoire, ce qui pourrait être considéré comme un affinement grossier (*corse tuning*) dans le jargon. Alors que les types de pipelines, Domino et « par vagues », ont un ajustement de précision (*fine tuning*) en plus d'un affinement grossier, ce qui pousse vers une diminution du délai dynamique des transistors, qu'on appelle généralement ajustement de précision. Les deux derniers types de pipeline (Domino et par vagues) permettent d'utiliser l'intégration de portes logiques axées sur une conception niveau transistor. Nous discuterons en profondeur de l'optimisation utilisant l'affinement grossier et l'affinement de précision au Chapitre 4.

L'implication d'une nouvelle technique emmène nécessairement des questions encore non répondues. L'une d'elle est l'utilisation d'outils CAO. Très rare, ils constituent

toujours un obstacle puisque leurs maniements sont encore très peu utilisés. Comme exemple, l'utilisation d'un logiciel pouvant introduire de façon automatique des temporiseurs (*buffer*) aux chemins les plus courts pour équilibrer les chemins n'est pas encore disponible sur le marché. Il faut dès lors, concevoir manuellement les pipelines par vagues en utilisant principalement des outils schématiques. En plus, l'utilisation de langages de haut niveau comme le VHDL ne peut simplement pas être utilisé seul pour l'implantation d'un pipeline par vagues. Le VHDL est utilisé souvent pour développer des architectures de type conventionnel ou pipeline conventionnel puisqu'il existe déjà plusieurs librairies CMOS offrant plusieurs combinaisons de logique booléenne. Cette recherche emmènera des réponses partielles ou complètes aux questions suivantes :

- Quelles sont les techniques récentes appliquées à la résolution d'une augmentation de débit?

- Quels sont les problèmes techniques qui devront être affrontés, comme par exemple le transport d'une horloge rapide et l'implantation d'une technologie d'intégration à très grande échelle (ITGE).

- Quels sont les paramètres externes qui peuvent influencer le débit d'une architecture lors de l'utilisation du pipeline par vagues?

## 1.2 Objectifs

L'objectif principal de cette recherche est d'apporter une contribution à l'avancement d'une récente technique peu connue et d'emmener le développement d'une nouvelle architecture dédiée à l'égalisation de canaux utilisant la méthode du pipeline par vagues comme élément principal. L'apprentissage des différentes méthodes d'augmentation du débit en comparant l'avantage principal d'utiliser le pipeline par vagues comme méthode pour permettre une plus grande transmission est notre premier objectif. Ceci dit, pour permettre à un algorithme comme le réseau de neurones d'être utilisé à son plein potentiel, nous devons absolument l'implanter en utilisant une méthode d'intégration avancée en VLSI (*very low scale of integration*) ou en français ITGE (intégration à très grande échelle).

Ainsi l'étude portera plus particulièrement sur les techniques d'implantation pipeline par vagues. La particularité de ce projet sera l'implantation d'une cellule nommée NPCPL qui permettra de réaliser des fonctions logiques de base avec la particularité d'avoir des délais de propagation équilibrés et d'obtenir de meilleurs débits architecturaux. Le développement et la réalisation de cette cellule sont la base de ce travail de recherche. Cette méthode de pipeline a été proposée à un algorithme de reconstitution de signaux basé sur le filtre de Kalman [B. Elouafay, mémoire de maîtrise, UQTR], [MAS98] et le présent projet est une suite allant vers la réalisation des cellules de base en vue d'une fabrication.

Enfin, il ne faut pas oublier que la création et le développement de dessin de masque d'unités arithmétiques emmèneront une certaine expérience positive à l'école d'Ingénierie

de Trois-Rivières.

### 1.3 Méthodologie

La première étape est une recherche bibliographique permettant de sélectionner les différents algorithmes appliqués à l'égalisation de canaux, ainsi que des références pertinentes sur la méthode d'implantation du pipeline par vagues en ITGE. Ensuite, vient l'étude des architectures dédiées à l'algorithme retenu, où l'implantation de la technique du pipeline par vagues est possible. Une des solutions retenues pour traiter le problème engendré par la transmission de la logique est d'utiliser une cellule NPCPL (Normal Process Complementary Pass Transistor Logic). La cellule NPCPL permet en effet d'équilibrer les délais accordés aux portes logique tel qu'expliqué dans [GOS95]. Finalement, la proposition d'un processeur spécialisé utilisant le pipeline par vagues dédié à l'égalisation de canaux permettra une contribution à la recherche dans le développement d'architectures à très haut débit pour la communication. Il conviendra de concevoir les principaux blocs à partir de la cellule NPCPL à la base du processeur spécifique développé. Par ailleurs, l'étude d'une implantation de la distribution d'horloges à très haute vitesse en utilisant un PLL (Phase Locked Loop) sera conçue en vue d'une utilisation comme multiplicateur de fréquence et verrouilleur de phase. Le tout sera conçu puis simulé à l'aide de plusieurs outils CAO (Matlab, Mentor Graphics, Synopsys et Cadence).

En bref, la réalisation de ce projet est justifiée par le cheminement des étapes qui suivent:

- Une recherche approfondie des nouvelles techniques d'augmentation du débit.

- Une étude reliée au pipeline par vagues.

- Un apprentissage des algorithmes dédié à l'égalisation de canaux

- Un apprentissage d'outils et méthodes pour la conception assistée par ordinateur (CAD) des circuits ITGE.

- Un apprentissage de la conception d'unités arithmétiques sur dessin de masque.

- Un développement de l'architecture dédié à l'égalisation de canaux

## 1.4 Organisation de ce mémoire

En premier lieu, une étude axée sur les techniques de base des algorithmes d'égalisation de canaux sera présentée au Chapitre 2. Plus spécifiquement, nous discuterons des principes à la section 2.1, des différences entre hors-ligne et en-ligne à la section 2.2, des algorithmes adaptatifs d'égalisation de canaux linéaires à la section 2.3, basés sur la logique floue à la section 2.4, basés sur les réseaux de neurones à la section 2.5 et enfin, du choix de l'égaliseur à être implanté à la section 2.6.

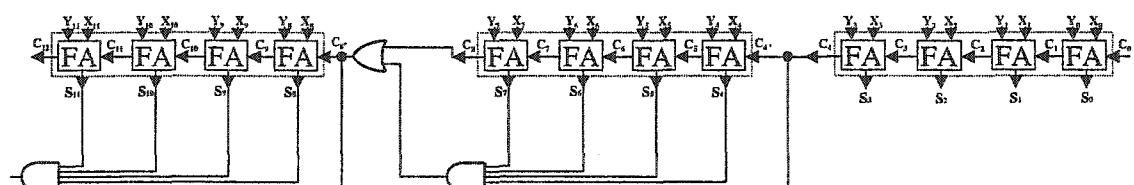

Ensuite, les unités arithmétiques entières seront abordées au chapitre 3 en commençant par la représentation binaire comme fondement de base à la section 3.1. Puis, nous présenterons les additionneurs binaires connus à la section 3.2. En passant à travers les additionneurs partiels (section 3.2.1), entiers (section 3.2.2), à retenue propagée (section 3.2.3), à retenue anticipée (section 3.2.4), à conservation de la retenue (section 3.2.5), à saut de la retenue (section 3.2.6), additionneurs sériel (section 3.2.7) et autres additionneurs (section 3.2.8). Après avoir discuté des additionneurs, nous présenterons les multiplicateurs connus à la section 3.3 pour passer ensuite au choix des unités arithmétique choisies à la

---

section 3.4.

Le chapitre 4 porte sur les principales techniques pipeline. Tout d'abord, il est question du pipeline conventionnel à la section 4.1, du pipeline asynchrone à la section 4.2 pour ensuite approfondir plus en détail sur le pipeline par vagues à la section 4.3. En passant d'abord à travers les équations de base (section 4.3.1), de l'optimisation des délais de propagation (section 4.3.2), des types de cellules disponibles en vue d'une implantation du pipeline par vagues (section 4.3.3), de la cellule choisie nommée NPCPL (section 4.3.4), ainsi que la structure ITGE qui utilisera le pipeline par vagues comme méthode d'optimisation de débit (section 4.3.5). Et finalement, le choix de la technique la plus approprié à l'égalisation sera présenté à la section 4.4.

Le chapitre 5 porte sur la réalisation des unités qui seront utilisées pour notre implantation pipeline par vagues. En premier lieu, l'intégration en technologie CMOS de 0.5  $\mu$ m de notre cellule NPCPL sera présentée à la section 5.1. Ensuite nous présenterons les résultats individuels obtenus sur l'additionneur et le multiplicateur pipeline par vagues à la section 5.3. Par la suite, le multiplicateur-accumulateur complet sera présenté à la section 5.3. Pour enfin évaluer les performances et les comparaisons finales proposées sur le multiplicateur-accumulateur choisi, à la section 5.4.

Le chapitre 6 porte sur l'architecture axée sur l'égalisation de canaux hors-ligne à base d'un réseau de neurone. En passant par les contraintes et critères architecturaux ITGE. Pour ensuite présenter le choix et la description de l'architecture à la section 6.2. Une estimation de la surface que notre architecture sera finalement présentée à la section 6.3

---

## **2 Algorithmes d'égalisation de canaux de communication**

L'utilisation toujours croissante de communication analogique ou numérique prend une grande part d'importance dans le domaine du génie électrique car plusieurs branches se rejoignent. En effet, les domaines reliés à celui de la communication sont entre autres; le traitement du signal, la conception de circuit analogique et numérique, l'asservissement, et bien entendu l'intégration à très grande échelle (ITGE). Ceci dit, l'idée principale derrière une communication est de transmettre et de recevoir une information avec une certaine célérité et une fiabilité accrue. Puisque le sujet est vaste, nous limiterons ce chapitre à l'importance de l'égalisation de canaux.

De nos jours, le numérique a un grand avantage sur la transmission analogique. Il est beaucoup moins sensible aux paramètres externes et permet d'être régénéré périodiquement lorsqu'il est transmis sur une longue distance, éliminant ainsi les effets néfastes reliés au bruit [PRO94]. En effet, durant une transmission analogue, le bruit additionné au signal sera négativement amplifié lors de sa régénération périodique aux endroits spécifiques. De plus, le numérique peut éliminer la redondance appliquée au signal avant la démodulation et ainsi conserver la largeur de bande du canal de transmission. Finalement, la transmission

numérique coûte souvent moins chère comparativement à la communication analogique au niveau matériel [LEE94].

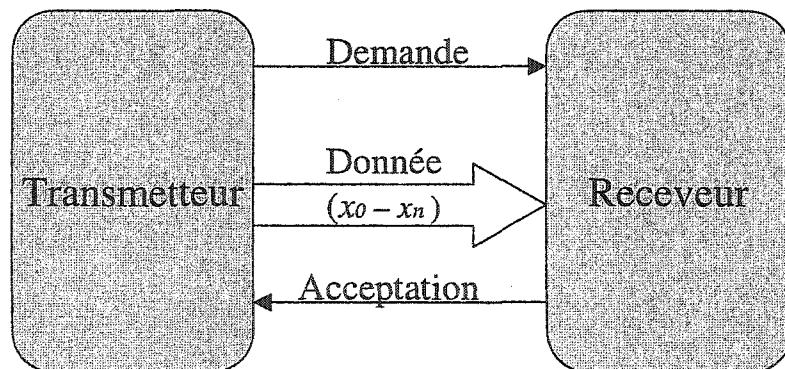

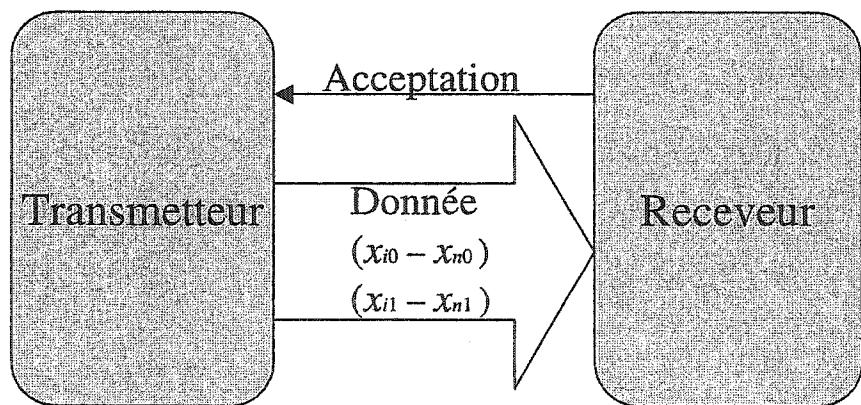

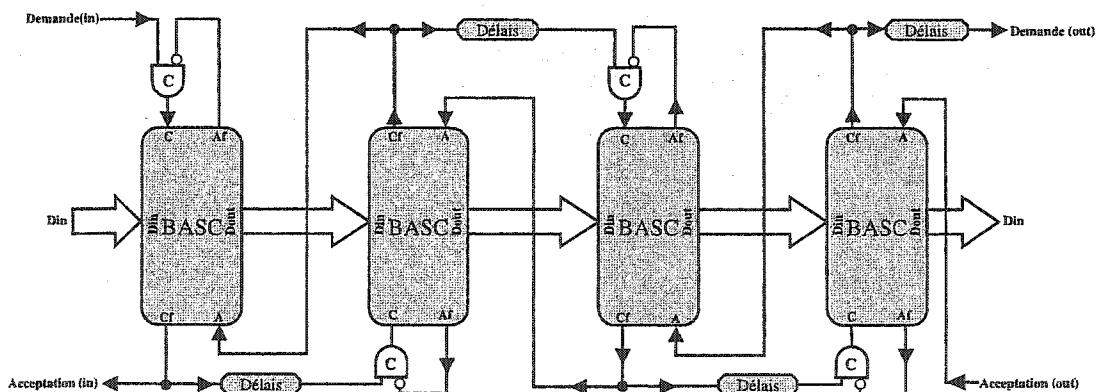

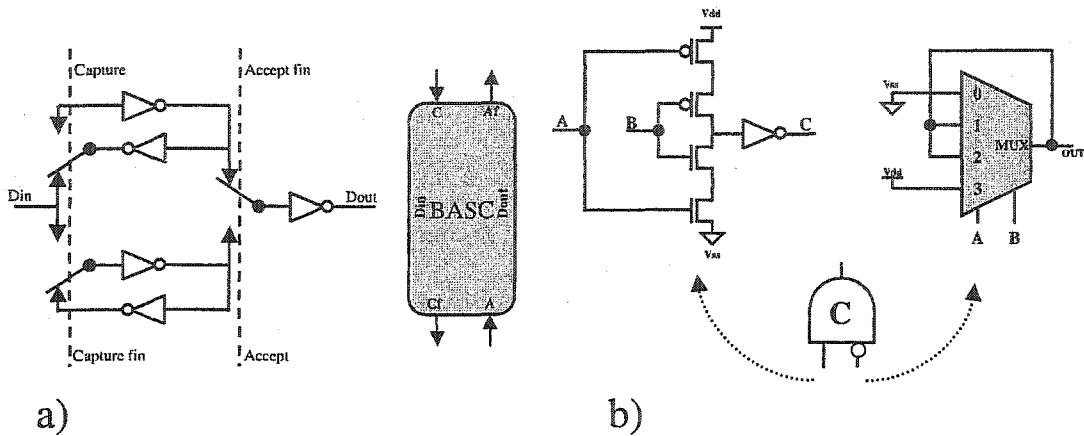

**Figure 2.1) Communication numérique élémentaire**

Le canal de transmission est d'abord et avant tout, le médian dans l'échange de données. Il sert de lien entre le transmetteur et le receveur. Il existe plusieurs milieux physiques classiques reliés au canal, comme:

- Une paire de fils de cuivre conduit par un courant électrique.

- Une fibre optique qui transmet un flux lumineux modulé.

- Une transmission sonore acoustique sous l'eau.

- Un Champ électromagnétique radié par une antenne électrique.

D'autres milieux peuvent aussi être considérés, comme la transmission magnétique ou optique de données emmagasinées par un lecteur de disque rigide d'un ordinateur

personnel.

Ceci dit, le milieu force le canal en limitant sa bande de transmission et caractérise sa fonction de transfert ou réponse impulsionnelle. Les problèmes rencontrés lors de transmissions sont souvent caractérisés par un bruit additif blanc de type Gaussienne créé en général par le bruit thermique. L'agitation des électrons à l'intérieur des résistances et autres circuits plus spécifiques au domaine des semi-conducteurs est une source de bruit. D'autres types de bruits et interférences externes peuvent être rencontrés. Une façon de résoudre ces problèmes est d'augmenter la puissance du signal transmis, par contre le type de canal peut limiter ce facteur. Le canal peut avoir d'autre dégradation du signal produit par l'atténuation, l'amplitude, la distorsion de phase et l'empilement entre symbole communément appelé *intersymbol interference (ISI)* d'une même source emmène une distorsion de l'information [PRO95]. Le canal peut être décrit mathématiquement par une simple équation, où

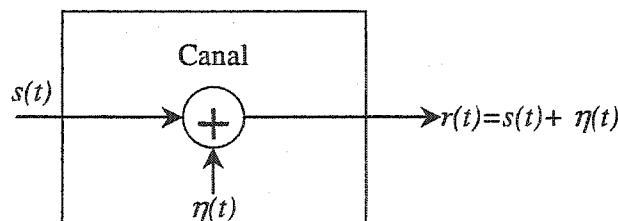

Figure 2.2) Canal avec bruit additif

$$r(t) = s(t) + n(t) \quad \text{Où } n \text{ représente le facteur d'atténuation} \quad (2.1)$$

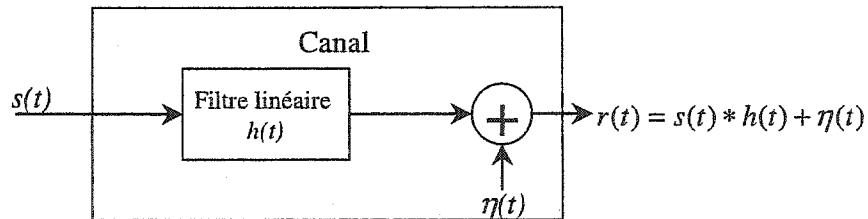

Cependant, il existe quatre types de canaux généralement rencontrés, le premier le plus simple et le moins fréquent représenté par la figure 2.2, est un canal avec bruit blanc additif de type Gaussienne. En second, nous avons un canal avec filtre linéaire invariant, limité par sa largeur de bande, ce type de canal atténue l'énergie spectrale du signal pour permettre de ne pas empiéter sur d'autre données transmises (figure 2.2), souvent rencontré par les communications par les paires de fils de cuivre utilisés en téléphonie. Le modèle mathématique (2.2) de ce signal est une convolution entre la réponse impulsionnelle  $h(t)$  et les données transmises  $s(t)$ .

$$r(t) = s(t) * h(t) + n(t) = \int_{-\infty}^{+\infty} h(\tau)s(t - \tau)d\tau + n(t) \quad (2.2)$$

Figure 2.3) Canal linéaire invariant avec bruit additif

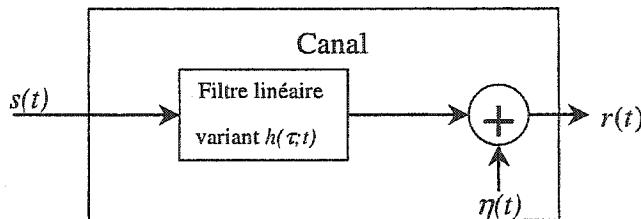

Comme troisième type de canal, nous avons le canal linéaire variant. Ce type de canal peut la plupart du temps être rencontré lors de transmission acoustique et lors de transmission de signaux à travers la couche ionosphérique, comme les transmissions satellites et cellulaires, où l'environnement change avec le temps. La réponse impulsionnelle du canal est  $h(\tau;t)$ , où  $h(\tau;t)$  représente la réponse du canal à un temps  $t$

causé par une impulsion au temps  $t-\tau$ , alors que  $\tau$  représente le délai entre les deux événements. La figure 2.4 est donc un exemple d'un canal linéaire variant. Ce canal sert souvent aux communication multiplex, c'est-à-dire lorsque plusieurs données sont transmises par le même canal de communication [LEE94].

Figure 2.4) Canal linéaire variant avec bruit additif

Les trois types de canaux que nous venons de voir, représentent d'après [PRO94] une très grande majorité de canaux auxquels nous devrons faire face. Cependant, il existe d'autres types de canaux, l'un d'eux est un canal non-linéaire. Le canal non-linéaire peut en majorité être estimé par sa linéarisation lorsque sa réponse est faiblement divergente. Cependant, les distorsions non-linéaires sur un canal de communication augmentent de plus en plus avec l'augmentation de la vitesse de transmission des données [WAN93]. Le modèle mathématique généralement rencontré d'un canal non-linéaire discret est :

$$\{r(t)\} = \mathfrak{I}[\{s(t)\}, \Theta] + n(t) \quad (2.3)$$

Où  $\Theta$  est un vecteur de paramètres de l'opérateur  $\mathfrak{I}$ . La reconstitution consiste à régulariser l'inversion de l'opérateur  $\mathfrak{I}$ , c'est-à-dire l'opérateur  $\mathfrak{R}$  [VID99].

$$\{s(t)\} = \Re[r\{(t)\}, \Theta] \quad (2.4)$$

Un paramètre fréquemment utilisé pour mesurer la qualité de transmission est la quantité de bloc d'information (bit) corrigé sur le nombre de donnée transmis c'est-à-dire le nombre de bit sans erreur reçu communément nommée le BER (*bit error rate*). Plusieurs méthodes existent pour corriger les erreurs générées par les bruits créés sur le canal. Les méthodes proposées sur ce projet permettent un excellent BER. Ainsi l'égalisation de canaux, plus particulièrement les algorithmes : linéaires, adaptatifs et de boucle de retour (DFE), permettent de corriger le canal de transmission en utilisant le modèle inverse du canal. L'avantage d'utiliser l'égalisation de canaux c'est qu'elle est axée principalement sur la diminution du nombre de bit erroné lors de transmission (BER). Permettant ainsi d'obtenir des vitesses supérieures aux vitesses normalement atteintes lorsque nous nous limitons aux vitesses régies par le théorème de Nyquist [LEE94]. En plus, l'utilisation d'égalisation de canaux permet non seulement de filtrer le bruit blanc causé principalement par le récepteur, mais surtout de diminuer les ISI (l'empiètement entre symbole d'un même signal).

Figure 2.5) Exemple d'un égalisateur de canaux

Il existe trois grandes catégories d'égalisation de canaux [PRO95]. La première doit

prendre l'entrée et la sortie du canal avant le traitement pour identifier le canal et son inverse. Ces types de filtres, peu pratique, se nomment égalisateur linéaire. Ils utilisent des filtres sous optimum où on doit faire un apprentissage hors-ligne des poids (gains) utilisés. Les filtres adaptatifs doivent eux utiliser constamment l'erreur entre l'entrée et la sortie pour estimer le modèle de la fonction de transfert peu importe l'apprentissage (en-ligne ou hors-ligne). Il existe aussi des égalisateurs optimaux, où l'inverse du canal est estimé sans connaître son entrée, nommé auto-égalisateur (*Blind Equalisation*). Dès lors, il existe plusieurs approches à un problème et l'égalisation n'est pas une exception. Nous verrons plus loin différents types d'égalisateur de type optimum et sous optimum.

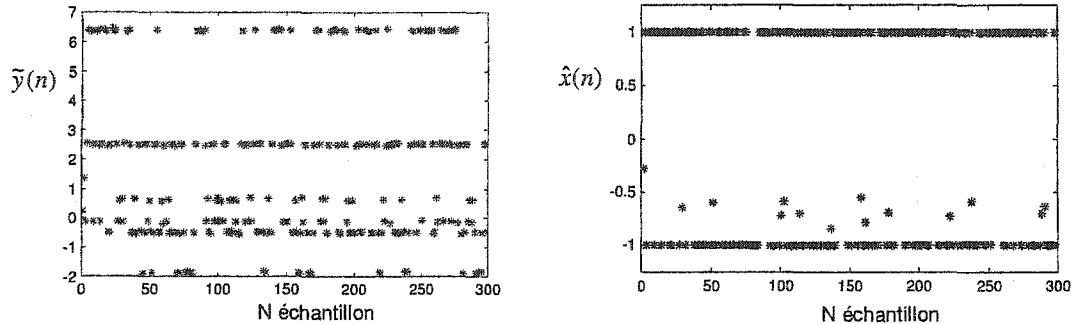

En bref, la transmission de données numériques est constituée principalement de données comprises entre -1 et 1. Ce qui facilite en quelque sorte la probabilité lors de l'adaptation des poids durant l'apprentissage. Un exemple de transmission de données additionnées d'un bruit blanc est représenté par figure 2.6.a. Alors que, la figure 2.6.b représente la sortie de l'égalisateur [VID99].

Figure 2.6) Exemple d'une transmission avant l'égalisateur (a), et après (b)

Les sous-sections suivantes serviront d'introduction au problème d'égalisation de canaux et des algorithmes proposés.

## 2.1 Principe de l'égalisation de canaux

Pour ce mémoire, nous allons plus particulièrement nous concentrer sur les algorithmes adaptatifs pour l'égalisation puisqu'ils ont souvent prouvé leur efficacité et leur robustesse au bruit. Ainsi, puisqu'ils sont polymorphes, ils varient automatiquement selon l'erreur fournie lors de sa validation. L'égalisation adaptative est un excellent candidat pour le choix de notre algorithme, puisqu'il est quasi impossible d'obtenir un canal qui ne varie pas avec le temps. Un exemple simple serait le transfert de données par modem téléphonique. Le canal varie uniquement lors de la connexion initiale, pour ensuite être stable tout au long de l'appel. Ceci peut facilement être considéré non variant, cependant le filtre devra être flexible initialement [PRO95].

Figure 2.7) Exemple d'un égalisateur adaptatif

Ceci dit, l'égalisation adaptatif pour les communications numériques a été initialement développé par R.W. Lucky (1965, 1966). Aidé par les recherches de filtre adaptatif par B. Windrow et M.E. Hoff, Jr en 1960. Son algorithme a été initialement développé pour le critère de distorsion maximum (*peak distortion criterion*), ce qui l'emmèna à développer l'algorithme *zero-forcing*. Ces études furent révolutionnaires et emmenèrent par la suite au développement de modem à haute vitesse, où il a été publié sur le sujet durant cinq ans. Ces études permirent le développement commercial de modem à très hauts débits de 9600 à 56000 bits/sec sur un canal téléphonique. Parallèlement, l'algorithme de Wiener de moyenne des moindres carrés (LMS) qui a été ensuite modifié par Windrow (1966), et ainsi que son utilisation à l'égalisation adaptative pour des signaux de valeurs complexes a été premièrement mise-à-jour, décrit et étudié par Proakis et Miller (1969). La percée révolutionnaire des travaux par Lucky en 1965, emmena aussi le développement de modulation de code de treillis plus poussé par Ungerboeck et Csajka (1976). Par la suite, d'autres études ont suivi, comme les recherches de Godard (1974), Picinbono (1978),

Morf et al. (1977, 1979), Makhoul (1978), Satorius et Pack (1981), Satorius et Alexander (1979), Ling et Proakis (1982, 1984, 1985), de grand savant. L'algorithme RLS Kalman pour l'égalisation de canaux adaptatif a été premièrement introduit par Falconer et Liung (1978). De plus, les premières recherches sur l'auto-égalisation (*Blind equalisation*) furent introduites par Sato (1975). Pour ensuite, finir sur les communications multiplex par constellation (compression du signal utilisant la phase). [HAY96], [LEE94], [PRO94], [PRO95].

## 2.2 Adaptation hors-ligne et en-ligne

L'objectif principal de l'égalisation adaptatif est d'adapter les coefficients d'un filtre adaptatif quelconque en vue de minimiser le bruit et l'empiètement entre les symboles d'un même signal (*Inter-Symbol Interference*) ISI émis à la sortie, pour ensuite être saturé par la fonction de décision (-1,1). L'adaptation des coefficients est alors fonction de l'erreur du signal. Cette erreur, par la suite, détermine la direction du coefficient en fonction du symbole auquel son erreur tend vers un minimum stable. Avant tout, l'algorithme choisi est défini par ces propres règles initiales. Il faut donc définir en premier des poids qui pourront converger le plus près et le plus rapidement possible au point de stabilité asymptotique de la fonction de transfert du canal régis par le type de minimum choisi. Généralement, le MSE (*Mean Square Error*) ou l'erreur minimum de la moyenne des carrés est choisie. Par la suite, il faut déterminer si une adaptation en-ligne ou hors-ligne est absolument

nécessaire. En effet, le choix de l'adaptation en-ligne ou hors-ligne est principalement déterminé par le type de canal auquel l'égalisation adaptative sera appliquée.

- Adaptation en-ligne:

Les poids de l'algorithme sont constamment modifiés en fonction du canal variant.

- Adaptation hors-ligne:

Les poids sont introduits antérieurement au filtrage, et doivent donc estimer le canal qu'ils seront appliqués.

Ce qui détermine la différence entre une adaptation en-ligne ou hors-ligne est d'abord la charge de calculs. L'évolution toujours constante du filtre lors de l'adaptation en-ligne, permet une convergence plus rapide et une plus grande flexibilité. Donc, une adaptation en-ligne peut se permettre de changer de canal, contrairement à un apprentissage hors-ligne. Cependant, la charge de calcul et l'utilisation d'une plus grande surface d'intégration au niveau ITGE peuvent désavantager ce type d'apprentissage. À l'opposé, l'utilisation d'une adaptation hors-ligne simplifie l'architecture à implanter. Sa convergence est plus lente si les poids ont mal été choisis par rapport au canal appliqué. Donc, un signal beaucoup moins filtré, avec un BER faible [PRO94], [LEE94], [PRO95].

### 2.3 Algorithmes adaptatifs d'égalisation de canaux linéaires

En générale, tout types de canaux physiques seront initialement non-linéaire. Cependant, comme expliqué plutôt, il est souvent possible de linéariser le canal et donc de simplifier le nombre nécessaire de retard sur la mesure et la complexité de calculs. En effet, il existe des algorithmes simples qui peuvent être aussi bon qu'un autre filtre, comme le RLS. Le récepteur employé pour la démodulation du signal est souvent caractérisé par deux types. Soit, les receveurs optimums et sous-optimums. Les receveurs optimums sont en principe basés sur l'estimation de probabilité maximum (*maximum likelihood sequence*) pour détecter la séquence d'information échantillonnée à la sortie du démodulateur. Les receveurs sous-optimums emploient généralement un égalisateur linéaire ou un égalisateur avec retour de décision (DFE). Pour ce qui est d'un égalisateur linéaire, il faut déduire que la réponse impulsionnelle ou la réponse en fréquence est initialement connue à la reception. Dans la plupart des cas, l'égalisation adaptative est utilisée. Ce choix est justifié par la fonction de transfert du canal qui est inconnue au départ, et serait plus souvent du type variant. Pour de tel cas, l'égalisation de canaux adaptatifs permet alors d'être ajusté en fonction du changement du canal puisqu'il existe un asservissement entre l'entrée idéale et la sortie du canal. S'il s'averrait que le canal variant serait du type variant dans le temps, l'égalisateur doit changer avec le canal. Et donc, préférablement utiliser un apprentissage en-ligne. Plus précisément, un canal variant dans le temps n'est pas régit par une gaussienne. Il est donc difficile à faire converger sans un apprentissage en-ligne.

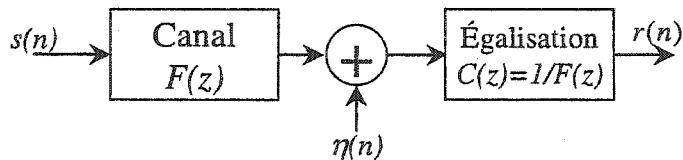

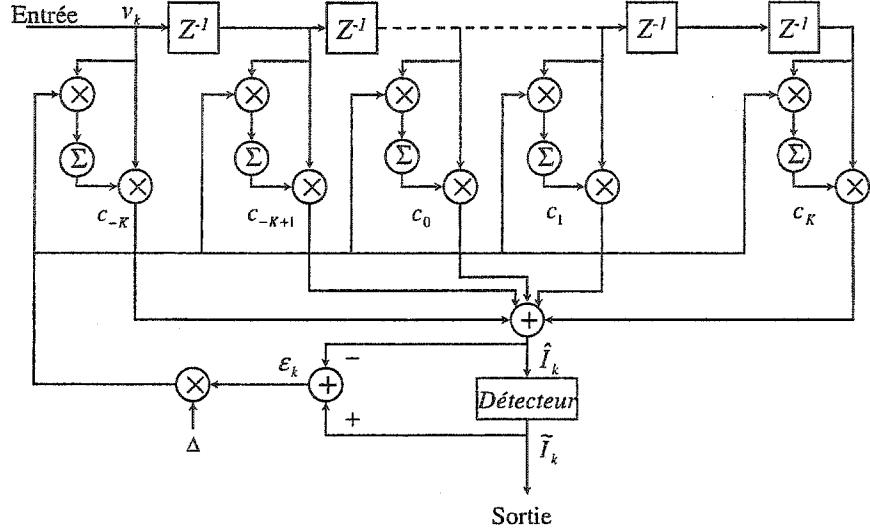

Figure 2.8) Exemple d'une égalisation adaptative zero-forcing

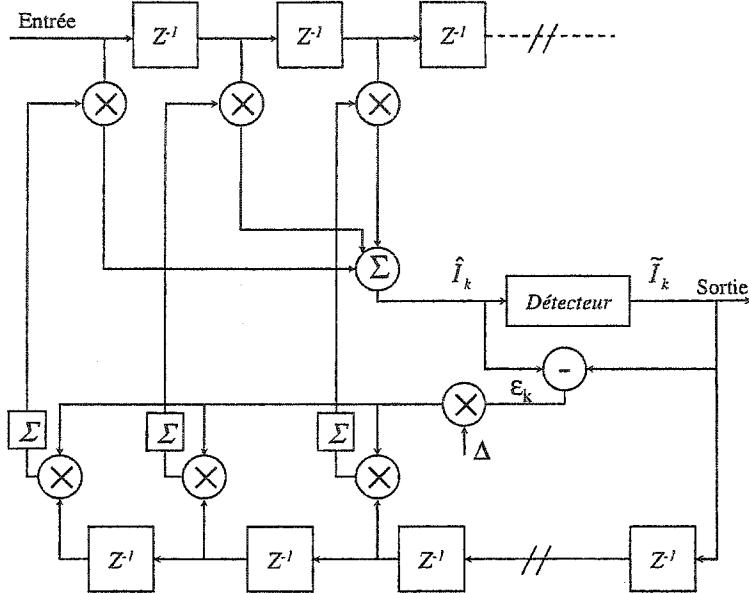

La figure 2.8, représente un type d'algorithme classé dans les algorithmes des égalisateurs de canaux adaptatifs linéaires. Cet algorithme utilise le critère de distorsion maximum  $\rho(c)$  (*peak distortion criterion*) qui déterminera si une saturation est appliquée lorsque  $\rho(c) < 1$ . Ce qui force la réponse de l'égalisateur  $q_n = 0$  pour  $1 \leq |n| \leq K$  et  $q_0 = 1$ . L'algorithme *zero-forcing* impose un ensemble de moyennes d'erreur  $\varepsilon_k = I_k - \hat{I}_k$  et la séquence d'information désirée  $\{I_k\}$  pour qu'elle diverge vers zéro en utilisant des paramètres se situant entre  $0 \leq |n| \leq K$ . Où  $Z^{-1}$  est la valeur échantillonnée discrète alors que  $\Sigma$  représente la sommation des multiplications. Ceci dit, si la réponse du canal est inconnue, l'injection de coefficients utilisés lors de l'entraînement pourrait être utilisé et donc la convergence serait plus rapide [PRO95], [LEE94].

Figure 2.9) Architecture élémentaire de l'algorithme LMS

Un autre filtre connu dans la catégorie égalisateur adaptatif est l'algorithme LMS (*Least Mean Square*) ou la moyenne des moindres carrés de Wiener [HAY96]. Elle peut aussi être appelée algorithme du gradient stochastique. L'équation principale du filtre est

$$\hat{C}_{k+1} = \hat{C}_k + \Delta \varepsilon_k V_k \quad (2.5)$$

Où  $C_k$  représente une série de coefficients de  $k^{ième}$  itération, alors que l'erreur du signal à la  $k^{ième}$  itération  $\varepsilon_k = I_k - \hat{I}_k$ .  $V_k$  représente le vecteur d'entrée du signal bruité qui crée l'estimation  $\hat{I}_k$ , et où  $V_k = [v_{k+K} \dots v_k \dots v_{k-K}]'$ . Ainsi  $\Delta$  est un nombre positif assez faible pour assurer une certaine convergence lors de l'itération. Puisque l'algorithme est basé sur le MSE (*Minimum square error*) ou l'erreur minimum au carré, il cherche à converger vers

le minimum MSE ce qui permet de stabiliser la valeur des poids. Pour aider la convergence des poids, le récepteur doit connaître la covariance du signal à être envoyé et le niveau du bruit additif. Cependant, l'algorithme LMS peut quand même être efficace si nous estimons le vecteur du gradient  $\hat{G}_k$ . Ce qui permettra alors, d'obtenir des poids du coefficient  $\hat{C}_{k+1}$  de meilleure qualité. [PRO95], [MIC92] Où :

$$\hat{C}_{k+1} = \hat{C}_k - \Delta \hat{G}_k \quad (2.6)$$

Alors que l'estimé du gradient ( $\hat{G}_k$ ) est:

$$\hat{G}_k = -\varepsilon_k V_k \quad (2.7)$$

Ceci nous emmène donc à l'équation principale (2.5).

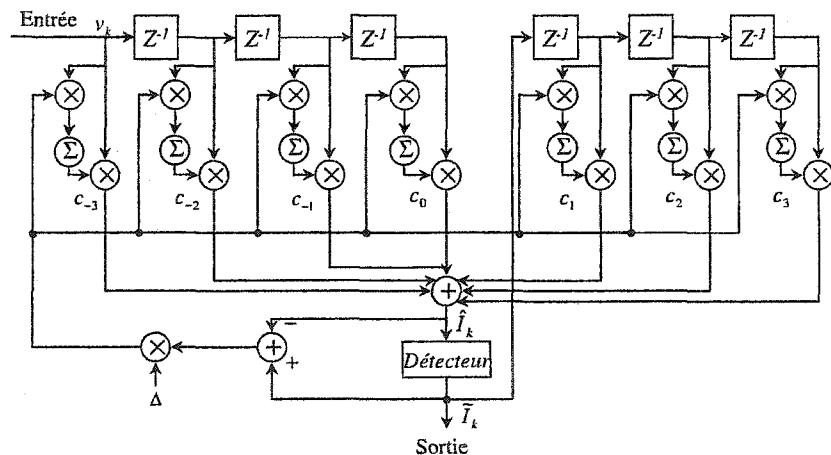

Après avoir vu les égalisateurs adaptatifs linéaires, nous avons une deuxième catégorie bien connue sous le nom d'égalisateur à retour de décision (*Decision Feedback equaliser*) ou DFE. Ce type d'égalisateur effectue non seulement une boucle de retour (*feedback*), comme les filtres adaptatifs linéaires, mais effectue aussi une boucle d'action (*feedforward*). La figure 2.10 représenté ci-dessous est un excellent exemple d'égalisateur à retour de décision. Comme vu précédemment, les filtres linéaires adaptatifs sont très efficaces pour un canal de type téléphonique, où les ISI ne sont pas trop élevés. Ainsi, si la

sévérité d'un taux d'empiètement est assez élevée entre les symboles d'un canal, elle peut donc causer des erreurs. Car, les ISI ne varient pas seulement au niveau temporel mais aussi au niveau de la caractéristique spectral. Selon les dires de J.G Proakis [PRO94], ce type de problème est souvent rencontré lors de communication radio, où le canal se situe spécialement dans la couche ionosphérique à des fréquences inférieures à 30 MHz. Donc, l'égalisateur à retour de décision est un égalisateur de type non-linéaire qui utilise les décisions passées pour ainsi éliminer les ISI.

Figure 2.10) Architecture de l'égaliseur à retour de décision (DFE)

L'égaliseur DFE consiste à utiliser deux filtres. Le premier filtre est appelé « filtre à boucle de retour ». Le filtre généralement utilisé est souvent le RIF (*réponse impulsionale finie*) avec les poids variables. Par ailleurs, dans la boucle de retour, le RIF est aussi utilisé. Donc, nous avons deux algorithmes très simples à implanter qui emmènent un taux de rejet ISI supérieur. Cependant, il est important de mentionner que le

DFE donne de meilleurs résultats que les filtres adaptatifs au niveau des ISI, mais son taux de rejet au bruit ne dépasse pas les filtres adaptatifs. Pour simplifier la compréhension, l'architecture de la figure 2.10 est conçue avec deux filtres utilisant l'algorithme LMS.

Comme troisième catégorie, nous avons les auto-égalisateurs. Contrairement aux égalisateurs adaptatifs linéaires, les auto-égalisateurs reçoivent la correction d'une chaîne de données préalablement définie pour ajuster les poids des coefficients. Les communications réseaux cellulaires sont des canaux qui changent avec l'endroit de la communication. D'où l'importance d'une grande vitesse de transmission est primordiale. Le besoin de transmettre avant une chaîne d'information est excessivement coûteux. Alors, une égalisation qui aurait initialement appris un type de canal sans devoir redemander une chaîne d'information à chaque changement devient extrêmement pratique. Ce type d'égalisation est du type auto-égalisation. Par conséquent, l'erreur entre l'entrée et la sortie du canal n'est plus nécessaire. La figure 2.11 représente ce type d'égalisation.

Figure 2.11) Égalisation aveugle (*Blind equalisation*)

Ceci dit, il existe d'autre type d'algorithmes adaptatifs utilisés comme le RLS (*Recursive Least Square*) communément appelé algorithme des moindres carrés récursifs, nous avons aussi le filtre de Kalman. Nous verrons dans les sections subséquentes des exemples d'égalisation de canaux optimum utilisant la logique floue et les réseaux de neurones.

## 2.4 Algorithmes basés sur la logique floue

L'utilisation de la logique floue comme méthode d'égalisation de canaux est encore tout nouveau. Peu reconnu au début de sa découverte, elle fût grandement appréciée par l'industrie japonaise vers les années 90. Ce boum permis de développer de nouveaux horizons [KOS97]. Des lors, l'arrivée de l'utilisation de la logique floue comme méthode d'égalisation de canaux permis de pousser l'égalisation pour les canaux non-linéaire.

Trois étapes principales régissent le concept de la logique floue:

1. La fuzzification

2. L'optimisation des lois d'inférences

3. La Défuzzification

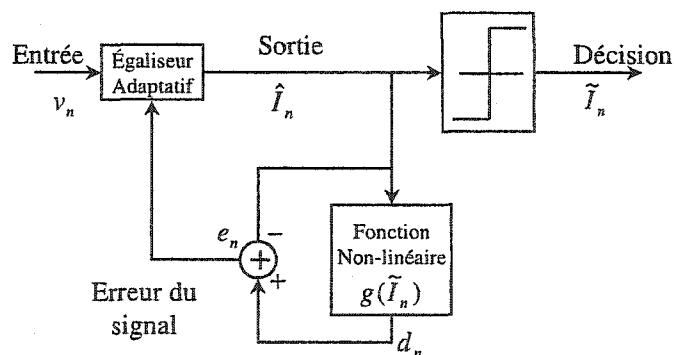

La description proposée ici fait surtout référence aux articles, [WAN93], [MOU99]. L'égalisation de canaux non-linéaires utilisant la logique floue est représenté par la figure 2.12.

Figure 2.12) Modèle de la logique floue dans un égalisateur de canaux

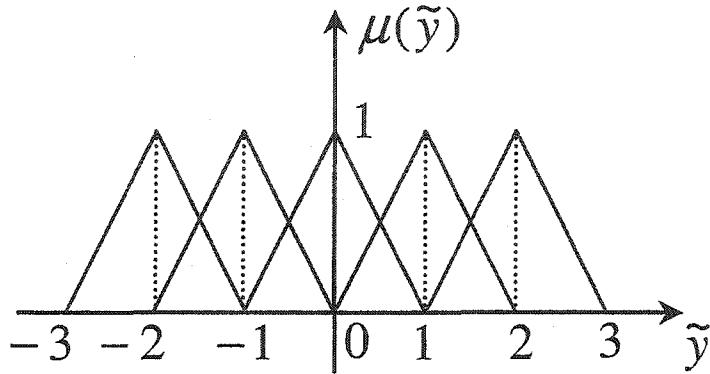

Pour obtenir un filtre optimum basé sur la logique floue, il est important de bien choisir sa fonction d'appartenance et le nombre  $m$  d'appartenances auquelles nous voulons que notre système utilise comme référence. Généralement, la fonction d'appartenance utilisée est de type Gaussienne. Cependant, l'intégration d'une fonction de type Gaussienne n'est pas facilement implantable et lors de la défuzzification des problèmes reliés au calcul du moment d'inertie ou de centre de gravité pourraient avoir lieu. Il est difficile d'approximer la Gaussienne sans une trop grande complexité de calculs. L'utilisation d'une fonction canonique par morceau permet alors de simplifier grandement le nombre nécessaire de calculs, ce qui est directement relié à la surface d'intégration et à la consommation de puissance. La figure 2.13, présente un exemple d'une fonction d'appartenance de type canonique par morceau.

Figure 2.13) Fonction d'appartenance canonique linéaire

Après avoir choisi notre fonction d'appartenance, il faut assigner à l'entrée  $\tilde{y}(n)$  la bonne valeur identifiée par sa fonction d'appartenance. La sortie de l'égalisation est représentée par l'équation 2.8, ci-dessous.

$$\hat{x}_k = p'(\tilde{y}) \cdot \Theta \quad (2.8)$$

Où  $\hat{x}_k$ , représente la sortie de l'égalisateur à logique floue à l'entrée du bloc de décision.

$p'(\tilde{y})$  est le vecteur d'entrée tempisé, alors que  $\Theta$  représente le vecteur des lois d'inférences choisies.

$$p^{l_1, l_2, \dots, l_n}(\tilde{y}) = \frac{\mu(\tilde{y}_n, l_1) \cdot \mu(\tilde{y}_{n-1}, l_2) \cdot \mu(\tilde{y}_{n-m+1}, l_n)}{c_n(\tilde{y})} \quad (2.9)$$

Alors que,  $c_n(\tilde{y})$  est le dénominateur de la somme des possibilités de la fonction

d'inférence. Alors que  $\mu(\tilde{y}_{k-i+1})$  est la réponse de la fuzzification.

$$\mu(\tilde{y}_{k-m+1}) = \exp\left[-\frac{1}{2}\left((\tilde{y}_{k-n+1} - \bar{y}_{k-n+1})/\sigma_n\right)^2\right] \quad (2.10)$$

Ceci dit, on utilise l'erreur entre le signal  $\hat{x}(n)$  et le signal idéal transmis  $s(n)$ . Pour ensuite introduire cette erreur à un algorithme adaptatif (RLS, LMS, etc). Ceci permet donc de développer des lois d'interférences qui sont représentées par le vecteur des paramètres  $\Theta$ . La logique floue permet la transformation du domaine temporel au domaine discret basé sur les lois d'inférences communément appelé la fuzzification. Après avoir filtré, le signal sera re-transformé en utilisant la défuzzification pour revenir au domaine temporel en se servant des lois d'inférences par le biais du moment d'inertie ou le centre de gravité.

Les résultats donnés par cet égalisateur de canaux nécessitent présentement une trop grande charge de calculs. En plus d'effectuer une multitude de multiplication et de divisions, l'égalisateur doit nécessairement utiliser un filtre adaptatif, ce qui alourdit la méthode. D'après une étude effectuée par M. Zakhama [ZAK99], cette technique ne peut pour l'instant égaliser un canal non-linéaire de plus de trois points d'après.

## 2.5 Algorithmes basés sur les réseaux de neurones

Grandement appréciés les réseaux de neurones ont énormément évolué durant les deux dernières décennies [MEH97]. Extrêmement robustes au bruit, et au non-linéarité, à l'origine, ils sont excellents pour l'égalisation de canaux, spécialement lorsque les canaux sont non-linéaires. Leur simplicité d'implantation leur donne un grand avantage comparativement à la méthode vue précédemment utilisant la logique floue.

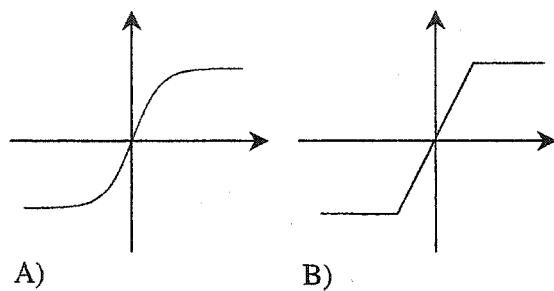

**Figure 2.14) Exemple de fonction d'activation**

a) **Sigmoïde** B) **Canonique linéaire**

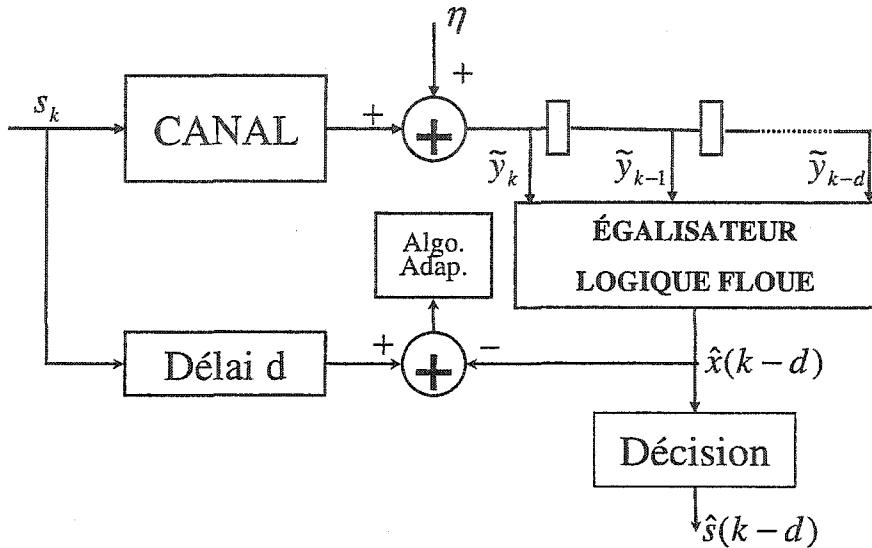

Il existe plusieurs types de réseaux de neurones. Cependant, nous allons spécialement introduire deux types de réseaux qui sont à notre avis plus spécifiquement dédiée à l'égalisation de canaux non-linéaire. Ce sont les réseaux à multicouches récursifs et non récursifs [KEC94], [VID99] et [VID99b]. Les réseaux de neurones sont à l'origine non-linéaire. La cause principale vient de la fonction d'activation introduite à tous les niveaux. C'est-à-dire que chaque neurone en principe effectue une saturation. Cette fonction d'activation est généralement de type sigmoïde. Elle permet ainsi de contrôler le débit à

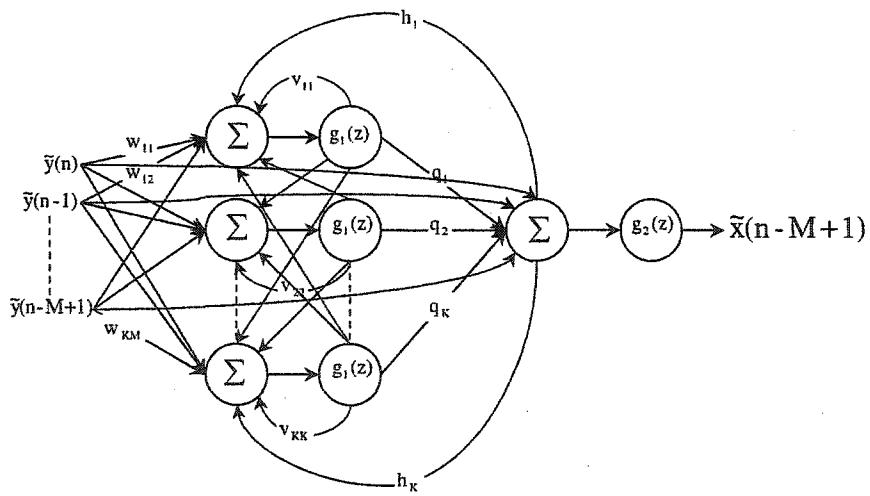

l'intérieur du réseau. La figure 2.14, représente deux types de fonctions d'activation bien connus. L'implantation ITGE numérique de la fonction sigmoïde constitue un problème d'implantation, mais l'utilisation d'une fonction canonique linéaire par morceau pourrait remplacer la sigmoïde [VID99]. Le réseau multicouche récursif ou PL-RNN (*Piecewise linear recursive multilayer neural network*) représenté ci-dessous démontre bien la complexité du réseau [KEC94] puisque chaque donnée est retournée aux neurones précédents. Cet algorithme constitue un excellent égalisateur adaptatif, cependant il nécessite énormément de calculs.

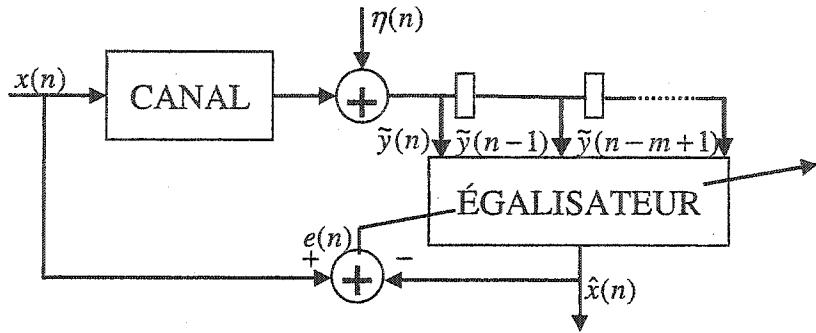

Figure 2.15) Réseau multicouche récursif (PL-RNN)

Par cette figure on peut remarquer qu'il utilise la valeur présente ainsi que les précédentes. Ce nombre dépend de la qualité de recouvrement du signal bruité à recevoir. C'est-à-dire que le nombre M de retard sur le signal reçu soit estimé, ce qui permet d'être représenté par un nombre minimum. Il est primordial cependant que les données reçues

soient sans erreur. En vérifiant son BER (*Bit error rate*), on peut ainsi déterminer le nombre de retard et de couche cachée qui seront nécessaires. Il existe différents autres facteurs qui déterminent la qualité du signal. Nous avons le nombre de neurone nécessaire, le nombre de retard vérifiable, ainsi que la valeur des poids, et bien sûr le type d'architecture. Jusqu'à maintenant, il n'existe pas d'outils permettant de déterminer ces facteurs en évaluant le signal devant être traité. Pour ce qui est de la qualité des signaux égalisés, il ne faut pas oublier qu'il est important lors de l'apprentissage du réseau de fournir des signaux de type qualitatif et quantitatif. Cependant, un nombre trop important de signaux peut emmener un sur-apprentissage du réseau et ainsi détériorer le niveau BER de la sortie. Pour ce qui est de l'apprentissage, généralement on utilise un niveau de bruit supérieur de donnée réelle. Par conséquent, le réseau augmente sa robustesse au bruit blanc. Pour ce qui est du choix de la fonction d'appartenance, M. Vidal [VID99] démontre bien qu'il n'est pas toujours quantifiable d'utiliser une sigmoïde. L'utilisation d'une fonction canonique par morceau s'avère suffisante spécialement lorsque l'implantation ITGE est visée. En plus de démontrer qualitativement les résultats utilisant une fonction d'appartenance simplifiée, M. Vidal [VID99] propose une architecture simple basée sur le réseau récursif multicouche. La topologie de la figure ci-dessous présente une architecture multicouche non récursive, pouvant être utilisée comme égalisateur de canaux non-linéaires (*PL-MNN*).

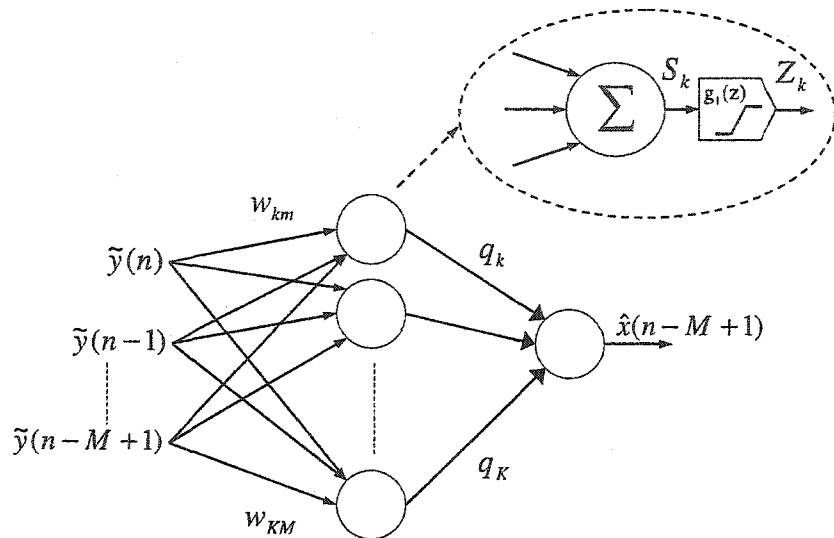

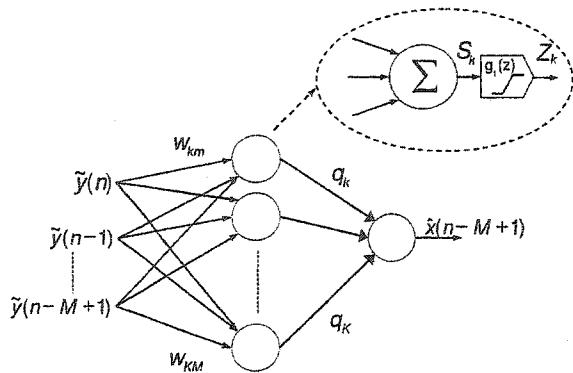

Figure 2.16) Réseau de neurone multicouche non récursif (PL-MNN)

L'algorithme nécessite  $M$  retard déterminé par la réponse impulsionnelle du canal et de la quantité de bruit additif (niveau signal/bruit). Chaque retard est multiplié par un vecteur  $W_{KM}$  identifié lors de l'apprentissage. Où  $K$  est le nombre de neurone dans la couche cachée et  $M$  est le nombre de retard. Après avoir accumulé dans chaque neurone la multiplication des signaux,  $\tilde{y}(n-M+1) \times W_{KM}$ , la fonction d'activation canonique linéaire  $g(s)$  suit. Ensuite, la sortie des neurones de la couche cachée est multipliée par un second poids ( $q_K$ ), pour ensuite être additionnée. Pour ensuite passer à travers la fonction d'activation, ce qui permettra d'obtenir un échantillon du signal transmis,  $\hat{x}(n-M+1)$ . L'équation 2.11 représente le signal estimé du réseau PL-MNN.

$$\hat{x}(n-M+1) = g\left(\sum_{k=1}^L q_k g\left(\sum_{j=1}^M w_{kj} \tilde{y}(n-m+1)\right)\right) \quad (2.11)$$

$$s_k = \sum_{m=1}^M w_{km} \tilde{y}(n-m+1) \quad \text{pour } k=1,2,\dots,K \quad (2.12)$$

$$\hat{x}(n-M+1) = g\left(\sum_{k=1}^L q_k g(s_k)\right) \quad (2.12) + (2.11) = (2.13)$$

Où  $s_k$  est la multiplication des signaux bruités et leurs retards par le poids de la première couche de neurone. L'équation de  $g(s)$  donne:

$$g(s) = \frac{|s+4| - |s-4|}{8} \quad (2.14)$$

Où la dérivée de  $g(s)$  est:

$$g'(s) = \begin{cases} 0.25 & \text{si } -4 < s < 4 \\ 0 & \text{ailleurs} \end{cases} \quad (2.15)$$

Pour ce qui est de la phase d'apprentissage, elle est basée sur la propagation d'une boucle de retour (*backpropagation*). L'erreur  $e(n)$  entre le signal idéal et l'estimé est ensuite introduite pour le calcul des poids de la couche cachée et de la sortie.

$$e(n) = \mu(x(n) - \hat{x}(n)) \quad (2.16)$$

Des lors, équation 2.17 et 2.18 emmènent le calcul des poids  $W_{KM}$  et  $q_K$ :

$$w_{km}(n+1) = w_{km}(n) + e(n)q_k(n)g'(s_k(n))y_m(n) \quad (2.17)$$

$$q_k(n+1) = q_k(n) + e(n)z_k(n), \quad q_k(1) = 0 \quad (2.18)$$

Pour le choix de l'implantation ITGE d'une architecture pour l'égalisation de canaux, notre choix s'arrête sur l'algorithme PL-MNN. Simple, régulier, et nécessitant beaucoup moins d'opérations comparativement aux deux algorithmes précédents. Le réseau de neurone multicouche PL-MNN obtient d'excellents résultats. Puisque l'architecture utilisera comme augmentation de débits la technique du pipeline par vagues, l'utilisation de l'algorithme PL-MNN devra utiliser un apprentissage hors-ligne. Ce qui permettra de stabiliser l'architecture. Comme nous verrons plus loin, il est primordial qu'une architecture utilisant le pipeline par vagues ait le moins possible de variations de débit. En plus, il devient extrêmement difficile d'équilibrer les chemins de l'architecture lorsque l'architecture est récursive. L'ajout d'une phase d'apprentissage crée cette récursivité dans l'architecture. Par conséquent, la fréquence de traitement de l'égalisateur de canaux devra être plus faible qu'une architecture continue. Ainsi en éliminant la phase d'apprentissage nous obtenons une architecture extrêmement linéaire, ce qui contribue à l'augmentation du débit et par le fait même celle de la latence.

## 2.6 Choix de l'Égaliseur

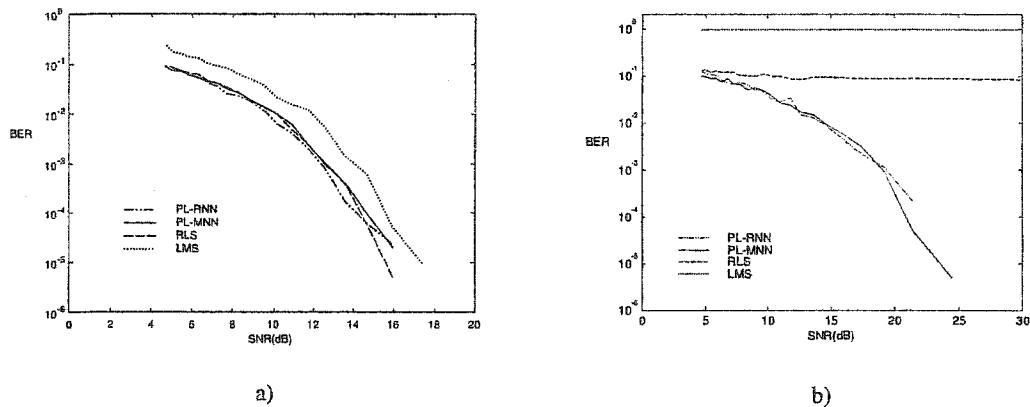

Le choix de l'égaliseur s'arrête sur l'utilisation d'un réseau de neurone, plus particulièrement le PL-MNN (*Piecewise Linear Multilayer Neural Network*), présenté dans [VID99], [VID99b] et [VID99c]. L'avantage d'utiliser un réseau de neurone lors de communication PAM (*Pulse Amplitude Modulation*) est la facilité d'intégration comparativement à d'autres types de réseaux de neurone comme le PL-RNN. La récurrence utilisée par le PL-RNN emmène une plus grande difficulté d'intégration puisque chaque neurone est entièrement connecté avec les autres. Si nous comparons aux algorithmes plus populaires comme le LMS et le RLS décrit par S. Haykin [HAY93], le PL-MNN obtient de bien meilleur résultat. Notre principal objectif lorsque vient le choix de notre algorithme est sa robustesse face aux bruits. Alors, nous utiliserons le BER en fonction SNR (*Signal-Noise Ratio*) comme méthode de sélection de l'algorithme choisi.

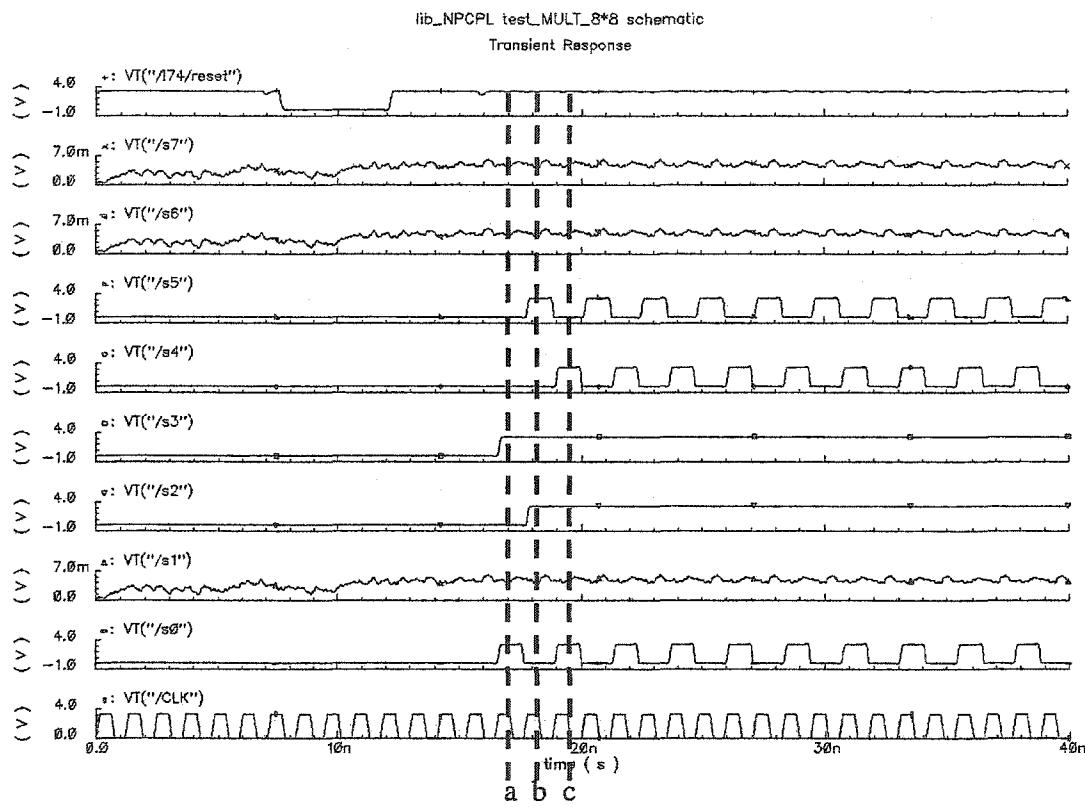

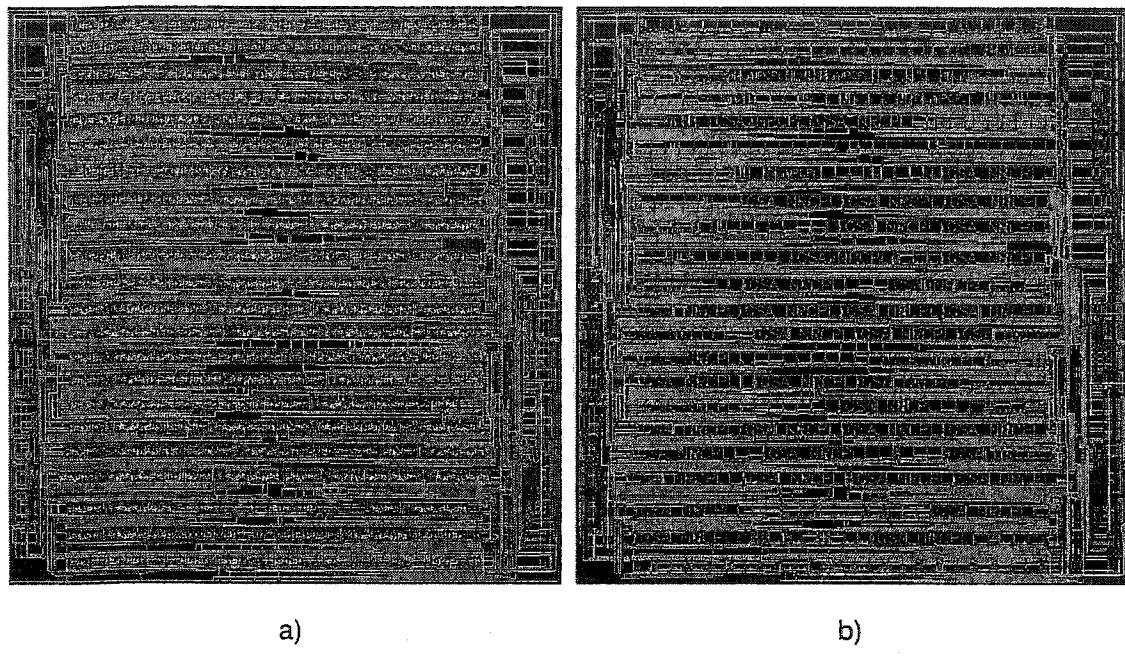

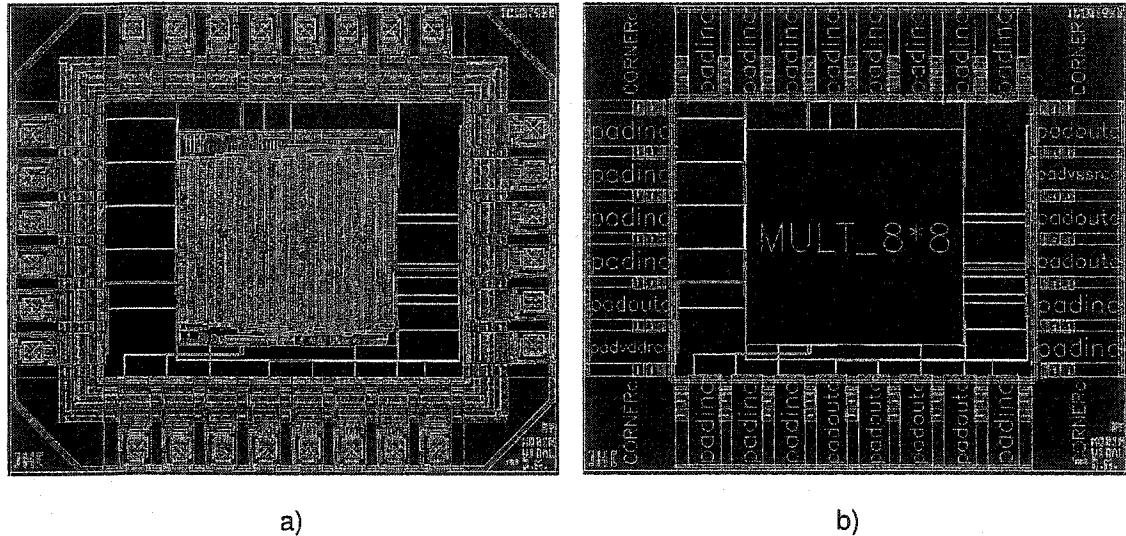

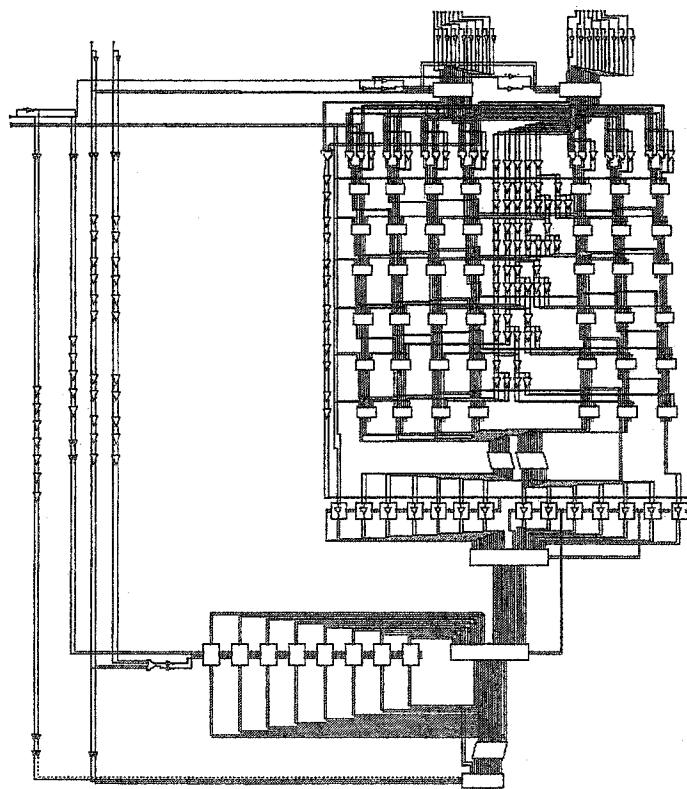

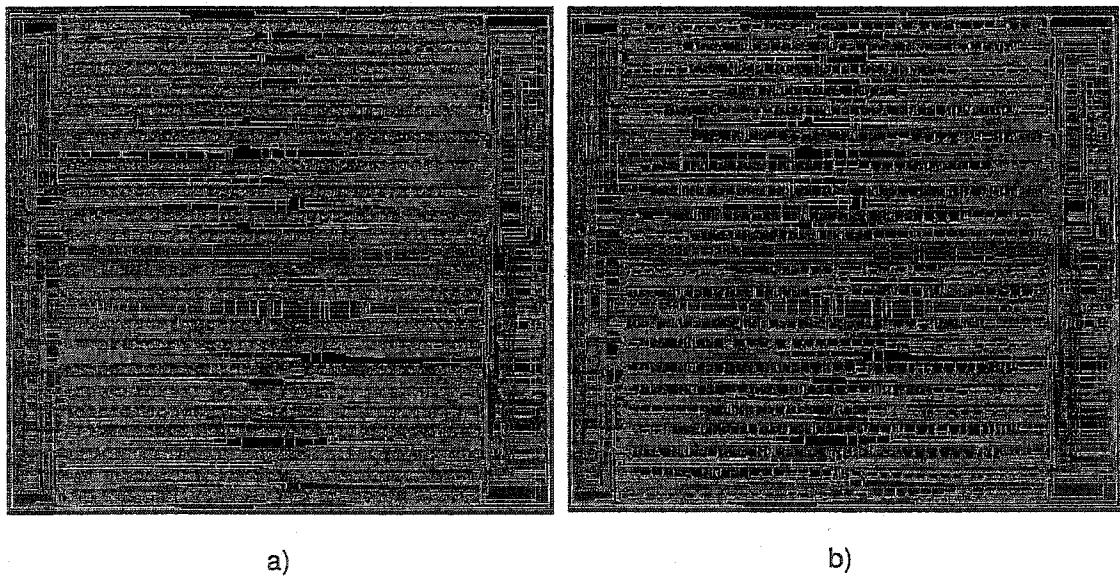

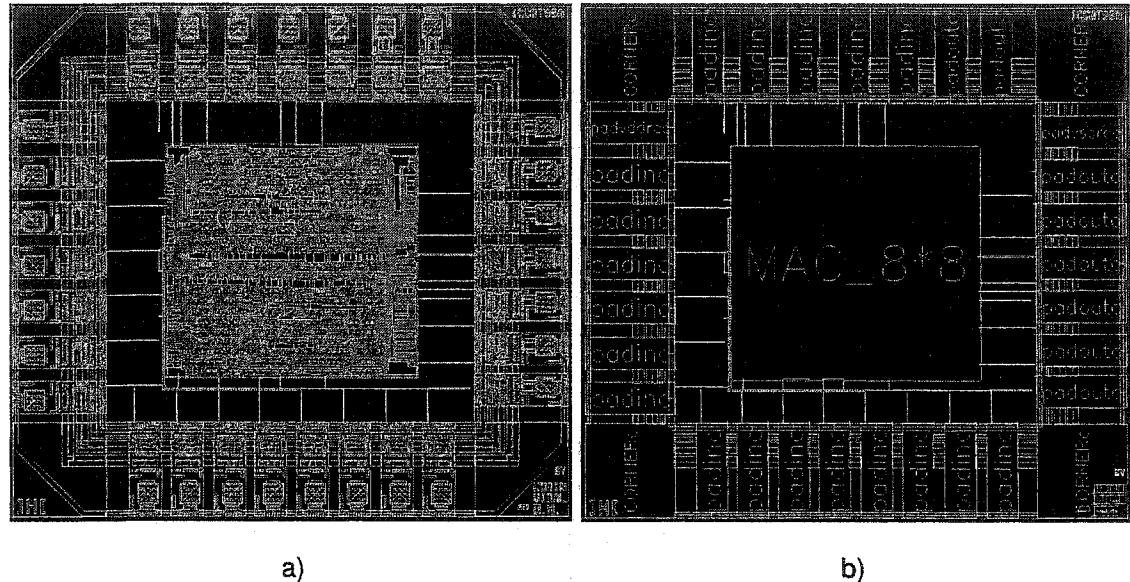

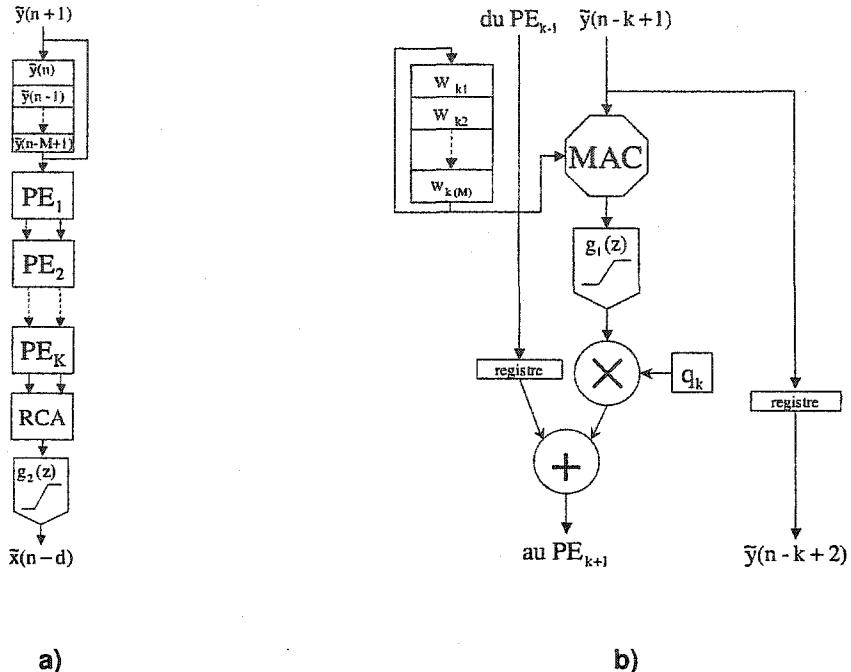

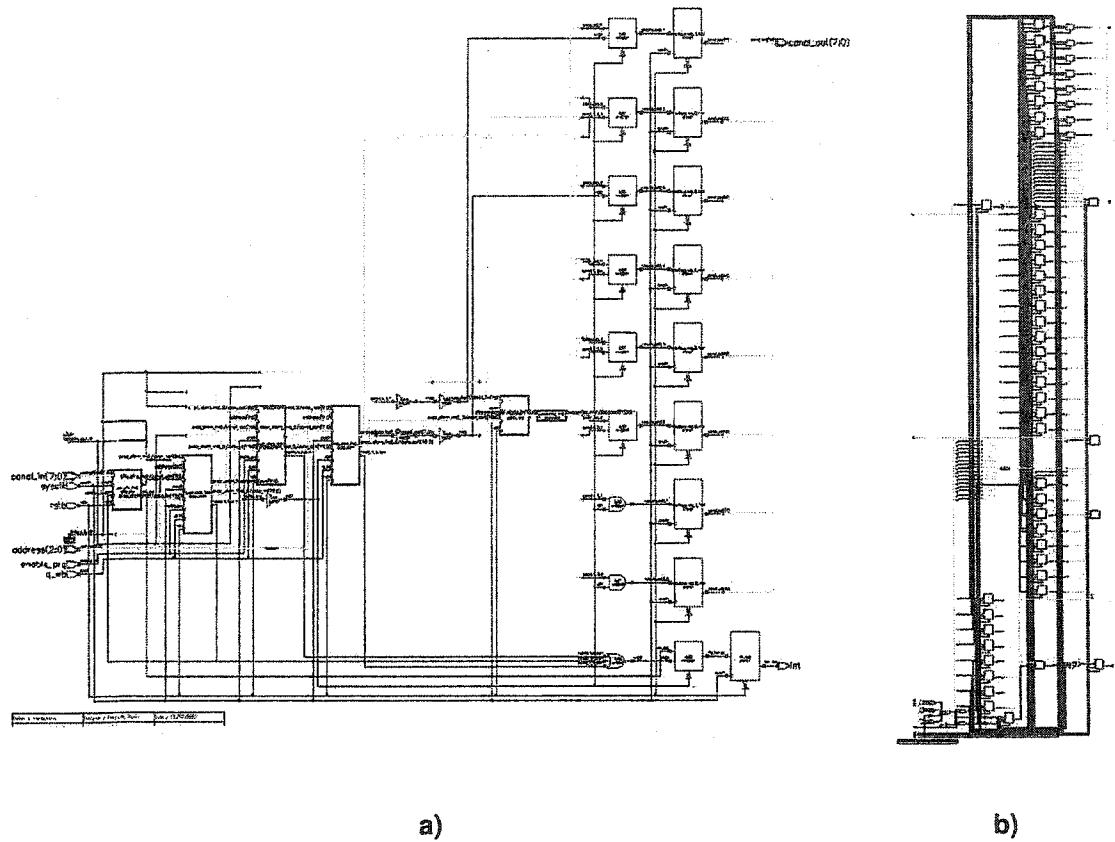

**Figure 2.17) Robustesse au bruit****a) Canal linéaire, b) Canal non-linéaire**