## UNIVERSITÉ DU QUÉBEC

## THÈSE PRÉSENTÉE À L'UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

### COMME EXIGENCE PARTIELLE DU DOCTORAT EN GÉNIE ÉLECTRIQUE

### PAR HUSSAM HUSSEIN ABU AZAB

ALGORITHME INNOVANT POUR LE TRAITEMENT PARALLÈLE BASÉ SUR L'INDÉPENDANCE DES TÂCHES ET LA DÉCOMPOSITION DES DONNÉES

# Université du Québec à Trois-Rivières Service de la bibliothèque

### Avertissement

L'auteur de ce mémoire ou de cette thèse a autorisé l'Université du Québec à Trois-Rivières à diffuser, à des fins non lucratives, une copie de son mémoire ou de sa thèse.

Cette diffusion n'entraîne pas une renonciation de la part de l'auteur à ses droits de propriété intellectuelle, incluant le droit d'auteur, sur ce mémoire ou cette thèse. Notamment, la reproduction ou la publication de la totalité ou d'une partie importante de ce mémoire ou de cette thèse requiert son autorisation.

## UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

DOCTORAT EN GÉNIE ÉLECTRIQUE (PH.D.)

Programme offert par l'Université du Québec à Trois-Rivières

ALGORITHME INNOVANT POUR LE TRAITEMENT PARALLÈLE BASÉ SUR L'INDÉPENDANCE DES TÂCHES ET LA DÉCOMPOSITION DES DONNÉES

### PAR

### HUSSAM HUSSEIN ABU AZAB

| Adel Omar Dahmane, directeur de recherche | Université du Québec à Trois-Rivières |

|-------------------------------------------|---------------------------------------|

| Sousso Kelouwani, président du jury       | Université du Québec à Trois-Rivières |

| Habib Hamam, codirecteur de recherche     | Université de Moncton                 |

| Ahmed Lakhssassi, évaluateur              | Université du Québec en Outaouais     |

| Rachid Beguenane, évaluateur externe      | Collège militaire royal du Canada     |

| Thèse soutenue le 15 décembre 2016        |                                       |

### **Abstract**

In this thesis, a novel framework for parallel processing is introduced. The main aim is to consider the modern processors architecture and to reduce the communication time among the processors of the parallel environment.

Several parallel algorithms have been developed since more than four decades; all of it takes the same mode of data decomposing and parallel processing. These algorithms suffer from the same drawbacks at different levels, which could be summarized that these algorithms consume too much time in communication among processors because of high data dependencies, on the other hand, communication time increases gradually as number of processors increases, also, as number of blocks of the decomposed data increases; sometime, communication time exceeds computation time in case of huge data to be parallel processed, which is the case of parallel matrix multiplication. On the other hand, all previous algorithms do not utilize the advances in the modern processors architecture.

Matrices multiplication has been used as benchmark problem for all parallel algorithms since it is one of the most fundamental numerical problem in science and engineering; starting by daily database transactions, meteorological forecasts, oceanography, astrophysics, fluid mechanics, nuclear engineering, chemical engineering, robotics and artificial intelligence, detection of petroleum and minerals, geological detection, medical research and the military, communication and telecommunication, analyzing DNA material, Simulating earthquakes, data mining and image processing.

In this thesis, new parallel matrix multiplication algorithm has been developed under the novel framework which implies generating independent tasks among processors, to reduce the communication time among processors to zero and to utilize the modern processors architecture in term of the availability of the cache mem. The new algorithm utilized 97% of processing power in place, against maximum of 25% of processing power for previous algorithms.

On the hand, new data decomposition technique has been developed for the problem where generating independent tasks is impossible, like solving Laplace equation, to reduce the communication cost. The new decomposition technique utilized 55% of processing power in place, against maximum of 30% of processing power for 2 Dimensions decomposition technique.

### **Foreword**

I dedicate this work first of all to my parents Hussein and Inaam, who partied the nights on my upbringing.

I dedicate this work to my life partner and so my PhD partner .... Rana

I foreword my work to the scientist of Math, to Al-Khwārizmī, Abū Ja'far Muhammad Ibn Mūsā, Pythagoras (Πυθαγόρας), Isaac Newton, Archimedes, René Descartes, and Alan Mathison Turing, father of computer science.

I foreword this work to my daughter Leen, and my sons Hussein, Yazan, and Muhammad.

I would acknowledge proudly my supervisor Prof. Adel Omar Dahmane, for his unlimited support through my PhD march, and I would thank all who supported me by all means.

# **Table of Contents**

| Abstract       | iii                                    |

|----------------|----------------------------------------|

| Foreword       | v                                      |

| Table of Con   | tentsvi                                |

| List of Tables | xi                                     |

| List of Figure | s xiii                                 |

| List of Symbo  | olsxvii                                |

| Chapter 1 -    | Introduction                           |

| 1.1. Moi       | tivation                               |

| 1.2. Orig      | ginality7                              |

| 1.3. Obj       | ectives                                |

| 1.4. Met       | hodology8                              |

| 1.5. The       | sis Organization9                      |

| Chapter 2 -    | Matrix Multiplication                  |

| 2.1. Intr      | oduction11                             |

| 2.2. Mai       | rix Multiplication Definition          |

| 2.3. Seri      | al Matrix Multiplication Algorithm     |

| 2.3.1.         | Serial Algorithm14                     |

| 2.3.2.         | Strassen's algorithm15                 |

| 2.4. Par       | allel Matrix Multiplication Algorithms |

| 2.4.1.         | Systolic Algorithm                     |

| 2.4.2.         | Cannon Algorithm19                     |

|        | 2.4.3.     | Fox and Otto's algorithm                                                | 21 |

|--------|------------|-------------------------------------------------------------------------|----|

| 2.5.   | Conclus    | sion                                                                    | 23 |

| Chapte | er 3 - ITF | PMMA algorithm for Parallel Matrix Multiplication (STMMA)2              | 24 |

| 3.1.   | Introduc   | ction                                                                   | 24 |

| 3.2.   | ITPMM      | A algorithm for Parallel Matrix Multiplication (STMMA)                  | 25 |

|        | 3.2.1.     | ITPMMA flowchart                                                        | 29 |

| 3.3.   | ITPMM      | A applied to different matrices sizes                                   | 33 |

|        | 3.3.1.     | Square Matrix multiplication, size of the result matrix is multiple of  | f  |

|        | the numb   | er of processors in parallel                                            | 33 |

|        | 3.3.2.     | Square Matrix multiplication, size of the result matrix is not multiple | e  |

|        | of the nun | nber of processors in parallel                                          | 39 |

|        | 3.3.3.     | Non - square Matrix multiplication, size of the result matrix is        |    |

|        | multiple o | of the number of processors in parallel                                 | 41 |

|        | 3.3.4.     | Non - square Matrix multiplication, size of the result matrix is not    |    |

|        | multiple o | of the number of processors in parallel                                 | 43 |

| 3.4.   | ITPMM      | A properties                                                            | 44 |

|        | 3.4.1.     | ITPMMA Complexity                                                       | 45 |

|        | 3.4.2.     | ITPMMA Load Balancing                                                   | 47 |

|        | 3.4.3.     | ITPMMA Communication Cost                                               | 48 |

|        | 3.4.4.     | ITPMMA algorithm (STMMA) Efficiency                                     | 48 |

| 3.5.   | Conclus    | sion                                                                    | 55 |

| Chapte | er 4 - ITP | PMMA Analysis and Results5                                              | 6  |

| 4.1.    | Introduction                                                | 56 |

|---------|-------------------------------------------------------------|----|

| 4.2.    | Simple parallel environment                                 | 57 |

| 4.3.    | Guillimin Cluster at CLUMEQ supercomputer environment       | 61 |

|         | 4.3.1. Speedup calculations                                 | 62 |

|         | 4.3.2. Load balance calculations                            | 65 |

|         | 4.3.3. Efficiency Calculations                              | 72 |

|         | 4.3.4. Performance calculations                             | 73 |

| 4.4.    | Conclusion                                                  | 75 |

| Chapte  | r 5 - The clustered 1 Dimension decomposition technique     |    |

| 5.1.    | Previous work                                               |    |

| 5.2.    | One and two dimensions' data decomposition techniques       | 78 |

| 5.3.    | Clustered one-dimension data decomposition technique        | 81 |

| 5.4.    | Analytical Analysis                                         | 83 |

| 5.5.    | Experimental Results                                        | 84 |

| 5.6.    | Conclusion                                                  | 89 |

| Chapte  | r 6 - Conclusion and Recommendation91                       |    |

| 6.1.    | Future Research Directions                                  | 93 |

| Referen | nces 95                                                     |    |

| Append  | dix A- Basic Linear Algebra Subroutine (BLAS)105            |    |

| Append  | dix B- Parallel Matrix Multiplication Algorithms107         |    |

|         | B.1. PUMMA (Parallel Universal Matrix Multiplication)1      | 07 |

|         | B.2. SUMMA (Scalable Universal Matrix Multiplication)       | 10 |

|         | B.3. DIMMA (Distribution Independent Matrix Multiplication) | 12 |

| scalable shared memory systems (2004)                                                                       | 115         |

|-------------------------------------------------------------------------------------------------------------|-------------|

| B.5. Coppersmith and Winograd (CW) Algorithm                                                                | 116         |

| B.6. Group-theoretic Algorithms for Matrix Multiplication                                                   | 120         |

| B.7. NGUYEN et al Algorithms for Matrix Multiplication                                                      | 120         |

| B.8. Pedram et al Algorithms for Matrix Multiplication                                                      | 121         |

| B.9. James Demmel Algorithms for Matrix Multiplication                                                      | 121         |

| B.10. Cai and Wei Algorithms for Matrix Multiplication                                                      | 121         |

| B.11. Sotiropoulos and Papaefstathiou Algorithms for Matrix Multiple                                        | lication122 |

| B.12. Andrew Stothers 2010                                                                                  | 122         |

| B.13. Breaking the Coppersmith-Winograd barrier 2011                                                        | 122         |

| B.14. Nathalie Revol and Philippe Théveny 2012                                                              | 122         |

| B.15. Jian-Hua Zheng 2013                                                                                   | 122         |

| B.16. Fast matrix multiplication using coherent configurations 2013.                                        | 123         |

| B.17. Square-Corner algorithm 2014                                                                          | 123         |

| B.18. Khalid Hasanov algorithm 2014                                                                         | 123         |

| B.19. Tania Malik et al algorithm 2014                                                                      | 123         |

| Appendix C- ITPMMA execution time vs different Parallel Algorithms  Appendix D- ITPMMA Algorithm pseudocode | 126         |

| Les algorithmes de traitement parallèle précédents                                                          |             |

| Nouveau cadre pour le traitement parallèle                                                                  | 132         |

B.4. SRUMMA a matrix multiplication algorithm suitable for clusters and

| ITPMMA                                                                               | 133 |

|--------------------------------------------------------------------------------------|-----|

| Multiplication de matrice carrée, la taille de la matrice résultante est multiple du |     |

| nombre de processeurs en parallèle                                                   | 137 |

| Propriétés de l'ITPMMA                                                               | 139 |

| Accélération des calculs à l'aide de l'algorithme ITPMMA                             | 139 |

| La technique de décomposition 1D en grappe                                           | 145 |

| Équation de Laplace en utilisant la méthode itérative Gauss-Seidel en grappe 1D      | 146 |

# **List of Tables**

| Table 2-1 The performance of the algorithm being studied by [33]                                                                                                                                | 19 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 2-2 The performance of the algorithm being studied by [56]                                                                                                                                | 2  |

| Table 3-1 Tasks to be performed by each processor                                                                                                                                               | 39 |

| Table 3-2 ITPMMA (STMMA) algorithm's tasks and execution time [59]                                                                                                                              | 50 |

| Table 3-3 Systolic Algorithm [61]                                                                                                                                                               | 51 |

| Table 3-4 Cannon's Algorithm [62]                                                                                                                                                               | 52 |

| Table 3-5 Fox's Algorithm with square decomposition [63]                                                                                                                                        | 52 |

| Table 3-6 Fox's Algorithm with scattered decomposition, [64]                                                                                                                                    | 53 |

| Table 3-7 Algorithms' execution time summary table                                                                                                                                              | 54 |

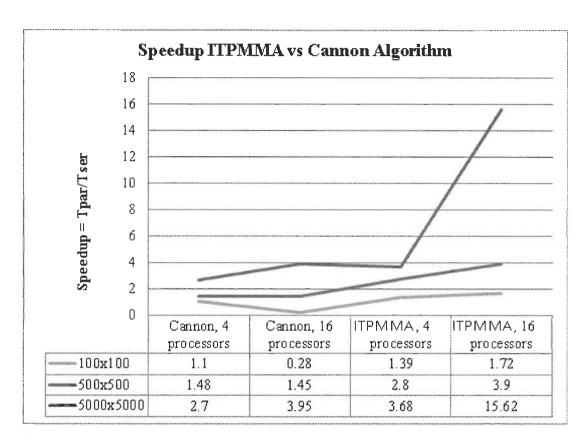

| Table 4-1 Comparison between the performance of ITPMMA (STMMA) and Cannon Algorithms for matrices of 100×100, 500×500, and 5000×5000                                                            | 5′ |

| Table 4-2 Different sizes of matrices with 16 processors in parallel, where the matrices size is multiplicand of the number of processors                                                       | 63 |

| Table 4-3 multiplying different sizes of matrices on 16 processors, where the matrices size is not multiplicand of the number of processors (balanced load will be clear with ITPMMA algorithm) | 60 |

| Table 4-4 comparison between different size matrices multiplication, where the size of the matrices are multiple and non-multiple of the processors.                                            | 68 |

| Table 4-5 Non-square matrices – 750 × 700 – with different number of processors                                                                                                                 | 69 |

| Table 4-6 Fixed size of matrices with different number of processors, where the matrices size is multiple of the number of processors                                                           | 72 |

| Table 5-1 Parallel Laplace's Equation Solution using Gauss-Seidel Iterative method on 2D                                                                                                  | 81  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Table 5-2 Parallel Laplace's Equation Solution using Gauss-Seidel Iterative method on Clustered1D                                                                                         | 84  |

| Table 5-3 Speed up and efficiency of parallel gauss-seidel iterative solution of Laplace's equation in Decomposition 2D, for 128 processers, for very large matrices sizes                | 88  |

| Table 5-4 Speed up and efficiency of parallel gauss-seidel iterative solution of Laplace's equation in Clustered 1D, for 128 processers, for very large matrices sizes                    | 88  |

| Table 5-5 Speed up comparison for clustered 1D vs Decomposition 2D for parallel gauss-seidel iterative solution of Laplace's equation in, for 128 processers, at very large matrices size | 89  |

| Table C-0-1 PUMMA (MBD2), [119]                                                                                                                                                           | 124 |

| Table C-0-2 SUMMA, [120]                                                                                                                                                                  | 124 |

| Table C-0-3 DIMMA, [121]                                                                                                                                                                  | 125 |

# **List of Figures**

| Figure 2-1 Matrix Multiplication problem as benchmark problem for Intel processor performance [39]                                                                                                                        | 12 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2-2 Systolic Algorithm                                                                                                                                                                                             | 18 |

| Figure 2-3 Layout of the A and B matrices in the systolic matrix-matrix multiplication algorithm for A4x4×B4x4 task mesh. The arrows show the direction of data movement during execution of the systolic algorithm. [55] | 19 |

| Figure 2-4 Cannon's algorithm layout for n = 3                                                                                                                                                                            | 20 |

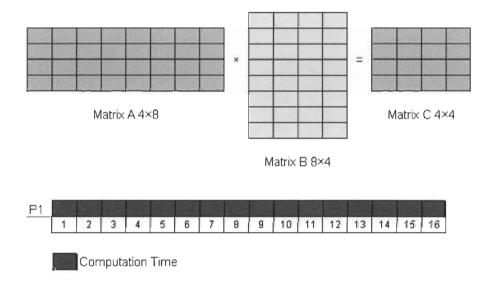

| Figure 3-1, Serial Matrix Multiplication                                                                                                                                                                                  | 27 |

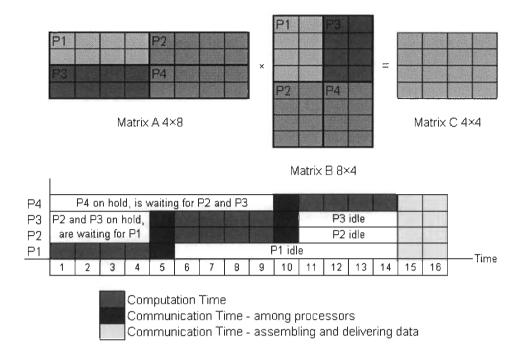

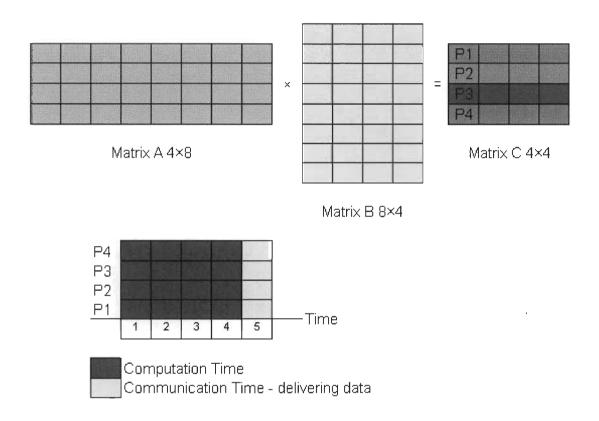

| Figure 3-2 Simulation of pre ITPMMA Algorithms                                                                                                                                                                            | 28 |

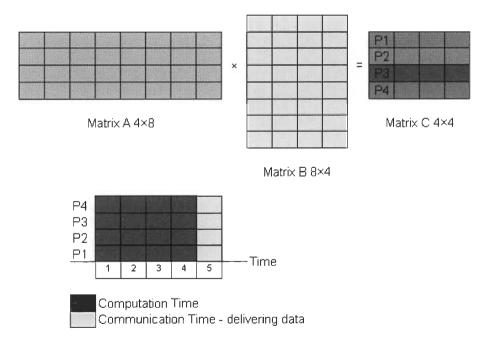

| Figure 3-3 Simulation of ITPMMA Algorithm                                                                                                                                                                                 | 28 |

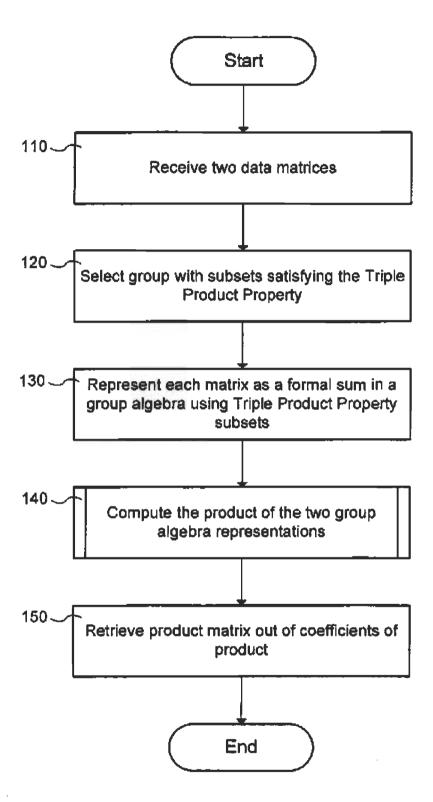

| Figure 3-4 ITPMMA Algorithm flowchart                                                                                                                                                                                     | 30 |

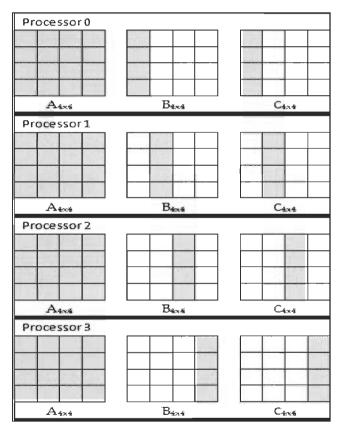

| Figure 3-5 Task distribution of $A_{4x4} \times B_{4x4}$ , where each processor will produce part of the result matrix $C_{4x4}$ .                                                                                        | 33 |

| Figure 3-6: Pseudo code executed by processor P0                                                                                                                                                                          | 34 |

| Figure 3-7: Pseudo code executed by processor P1                                                                                                                                                                          | 34 |

| Figure 3-8: Pseudo code executed by processor P2                                                                                                                                                                          | 34 |

| Figure 3-9: Pseudo code executed by processor P3                                                                                                                                                                          | 35 |

| Figure 3-10 Task distribution of $A_{12x12} \times B_{12x12}$ , where each processor will produce part of the result matrix $C_{12x12}$                                                                                   | 36 |

| Figure 3-11: Pseudo code executed by processor P0, to produce the first and the fifth and the ninth columns of the result matrix C <sub>12x12</sub>                                                                       | 37 |

| Figure 3-12: A <sub>12x12</sub> × B <sub>12x12</sub> using ITPMMA algorithm for parallel matrix multiplication                                                                                                            | 38 |

| Figure 3-13 Tasks to be performed by each processor of the eight processor to produce the matrix $C_{12\times12}$                                                                                   | 40 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

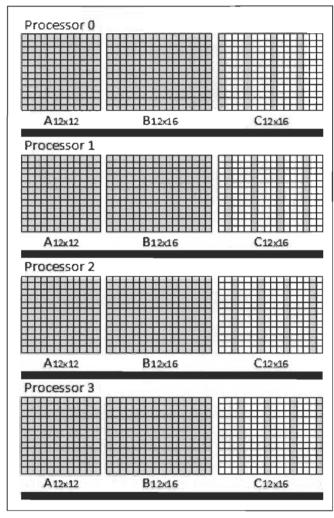

| Figure 3-14 Task distribution of $A_{12x12} \times B_{12x16}$ , where each processor will produce different part of the result matrix $C_{12x16}$                                                   | 42 |

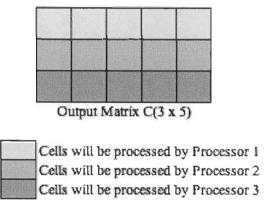

| Figure 3-15 Multiplions of matrices $A(3 \times 3) * B(3 \times 5) = C(3 \times 5)$ using 3 processors                                                                                              | 43 |

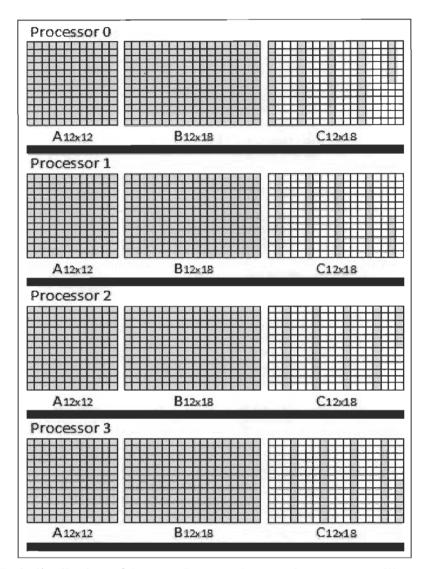

| Figure 3-16 Task distribution of $A_{12x12} \times B_{12x18}$ , where each processor will produce part of the result matrix $C_{12x18}$ .                                                           | 44 |

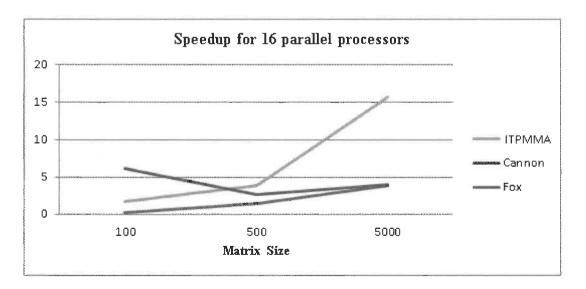

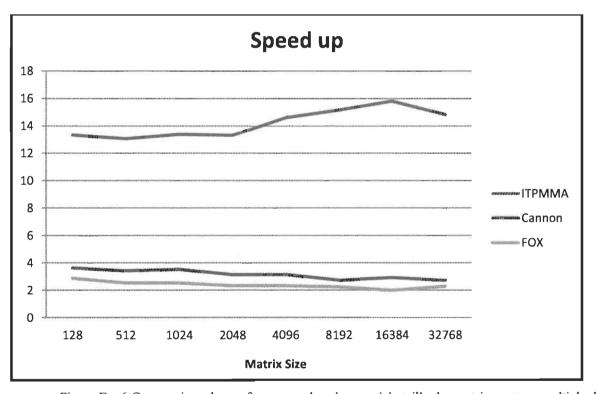

| Figure 4-1 Speed up of ITPMMA compared with Cannon                                                                                                                                                  | 59 |

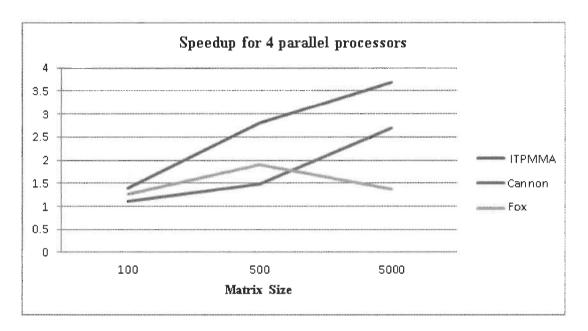

| Figure 4-2: Speed up comparison for 4 processors between ITPMMA Cannon algorithms                                                                                                                   | 60 |

| Figure 4-3: Speed up comparison for 16 processors between ITPMMA Cannon algorithms                                                                                                                  | 60 |

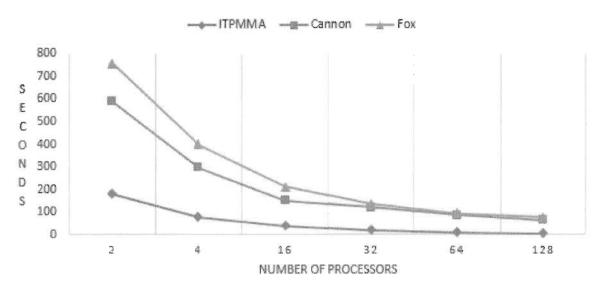

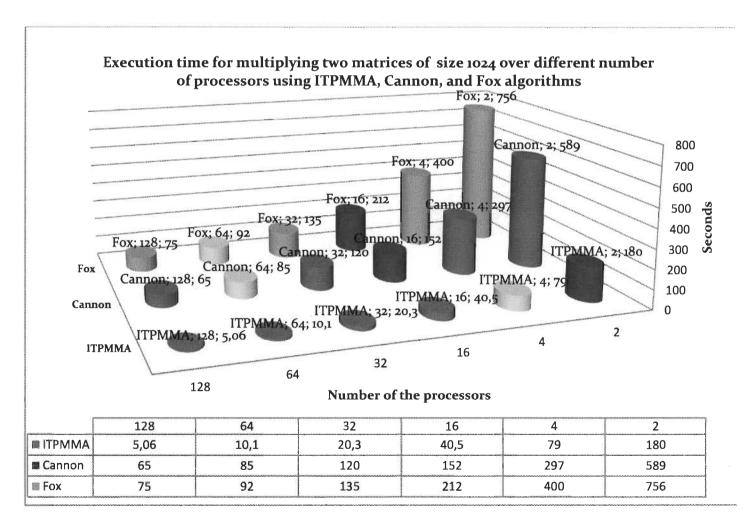

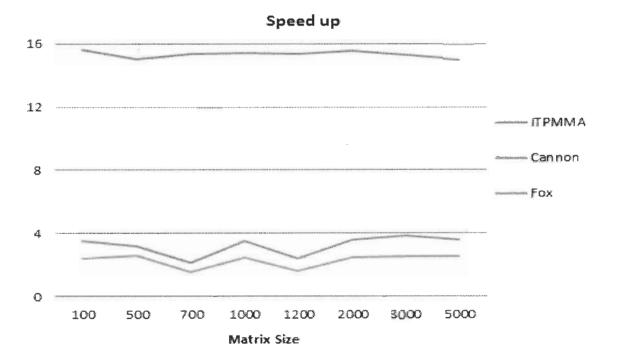

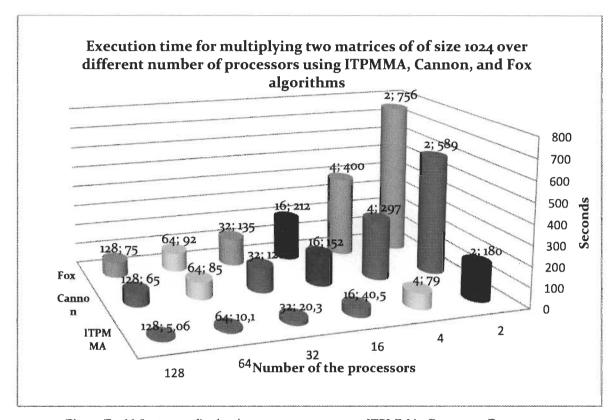

| Figure 4-4 ITPMMA Algorithm Speed up against both Cannon Algorithm, and Fox Algorithm where the matrices size is multiplicand of the number of processors                                           | 63 |

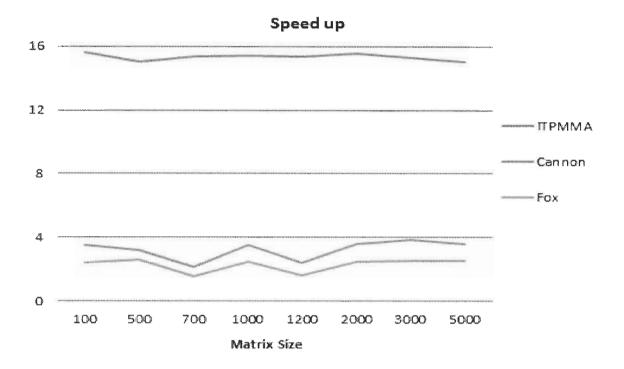

| Figure 4-5 Speed up of ITPMMA algorithm against both Cannon Algorithm, and Fox Algorithm where the matrices size is not multiple of the number of processors                                        | 67 |

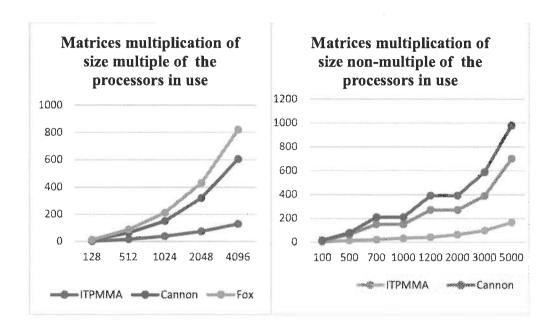

| Figure 4-6 Matrices multiplication of size multiple and non-multiple of the processors in use                                                                                                       | 69 |

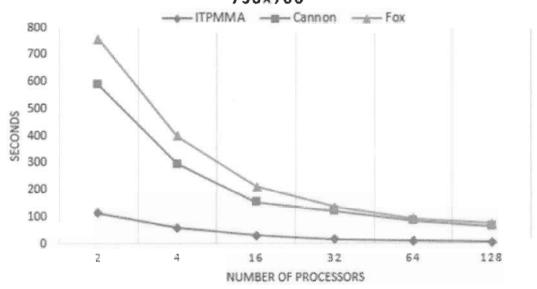

| Figure 4-7 Parallel Processing Time ITPMMA algorithm against both Cannon Algorithm, and Fox Algorithm where the matrices size of 750×700 is not multiple of the number of processors                | 70 |

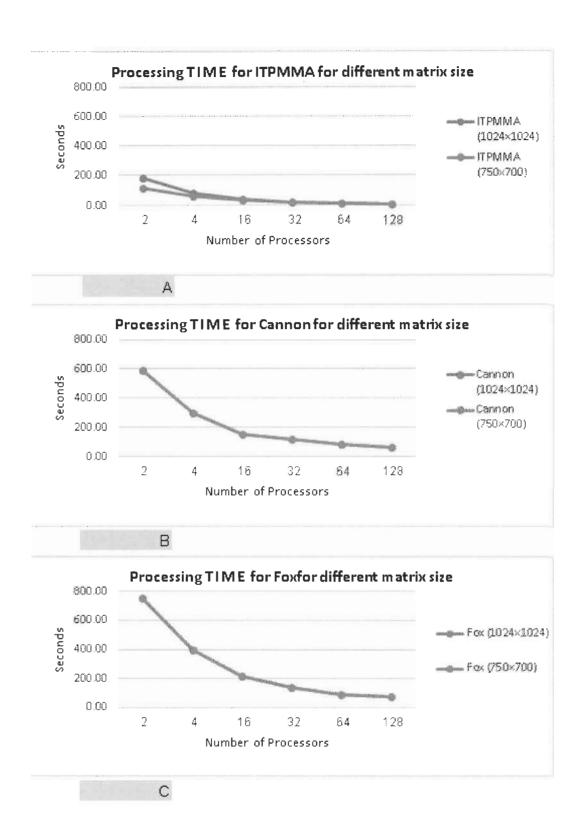

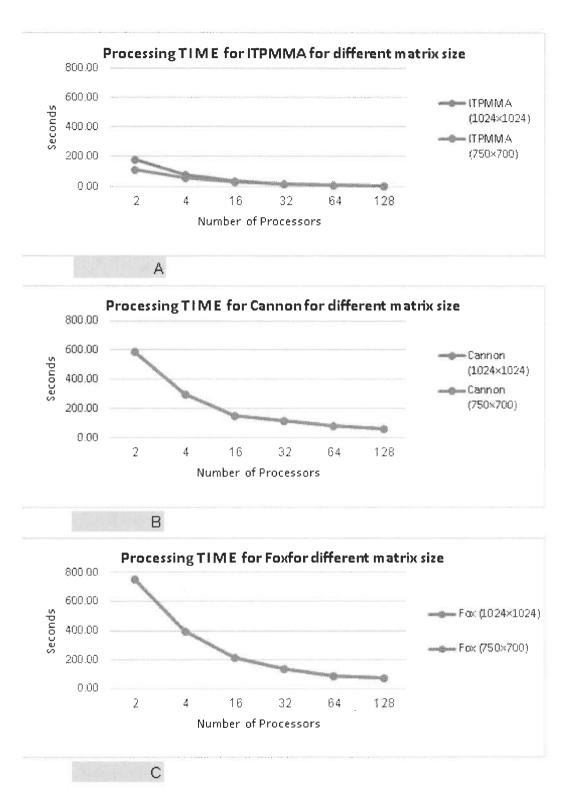

| Figure 4-8 Parallel Processing Time for matrices multiplication of two different sizes 750×700, and 1024×1024. A: ITPMMA algorithm, B: Cannon Algorithm, C: Fox Algorithm                           | 71 |

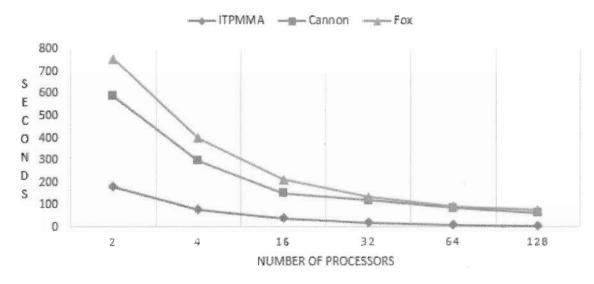

| Figure 4-9 Parallel Processing Time for ITPMMA algorithm against both Cannon Algorithm, and Fox Algorithm where the matrices size is multiple of the number of processors for matrices of 1024×1024 | 73 |

| Figure 4-10 Execution time per processor for ITPMMA, Cannon, and Fox algorithms                                                                                                                     | 74 |

| Figure 5-1 Laplace Equation problem presentation, reds are boundary points while blue are interior points                                                         | . 79 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

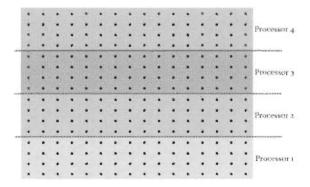

| Figure 5-2 1D Decomposition                                                                                                                                       | . 79 |

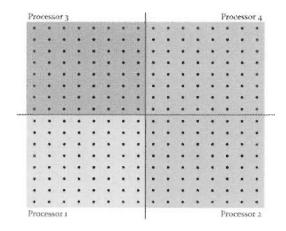

| Figure 5-3 2D Decomposition                                                                                                                                       | . 80 |

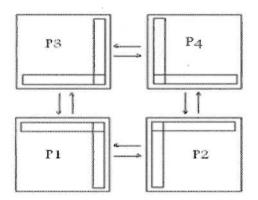

| Figure 5-4 Data dependency of 2D Decomposition                                                                                                                    | . 80 |

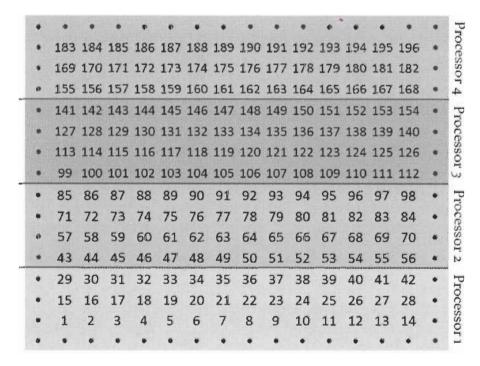

| Figure 5-5 1D decomposition technique, total time units is 196 units                                                                                              | . 81 |

| Figure 5-6 2D decomposition technique, total time units is 147 units                                                                                              | . 82 |

| Figure 5-7 Clustered 1D decomposition technique, total time units is 73 units                                                                                     | . 83 |

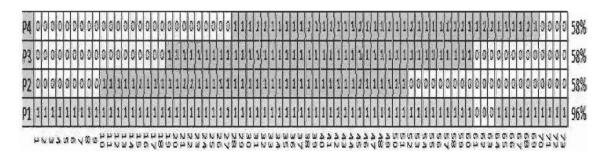

| Figure 5-8 Clustered 1D decomposition processors utilization                                                                                                      | . 83 |

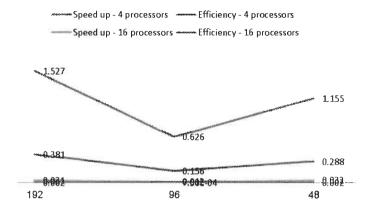

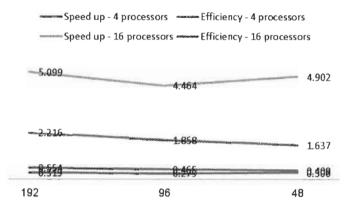

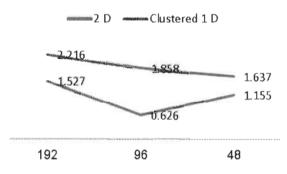

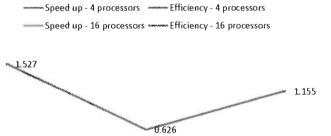

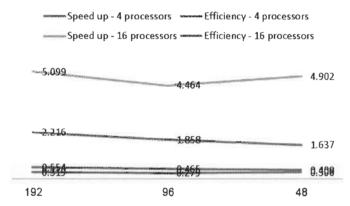

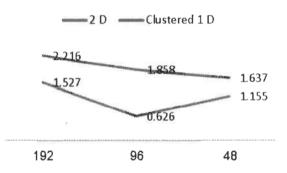

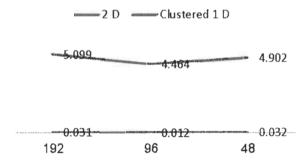

| Figure 5-9 Speed up and efficiency of parallel gauss-seidel iterative solution of Laplace's equation in 2 dimentions                                              | . 85 |

| Figure 5-10 Speed up and efficiency of parallel gauss-seidel iterative solution of Laplace's equation in clustered 1 dimensional decomposition                    | . 86 |

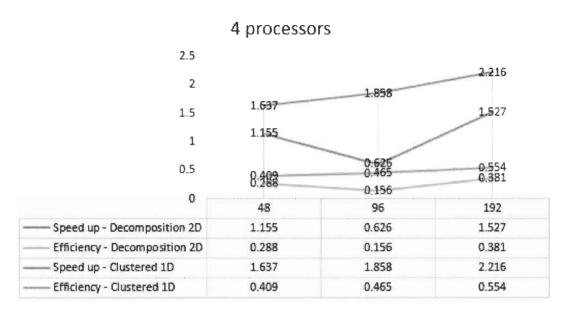

| Figure 5-11 Speed up of parallel gauss-seidel iterative solution of Laplace's equation in both data decomposition techniques at 4 processors                      | . 86 |

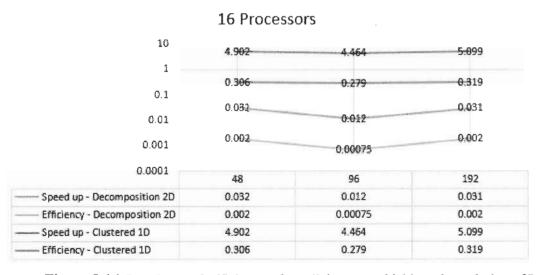

| Figure 5-12 Speed up of parallel gauss-seidel iterative solution of Laplace's equation in both data decomposition techniques at 16 processors                     | . 86 |

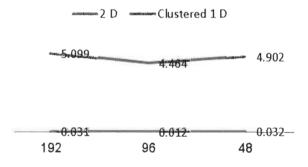

| Figure 5-13 Speed up and efficiency of parallel gauss-seidel iterative solution of Laplace's equation in clustered 1D vs Decomposition 2D, for four processers    | . 87 |

| Figure 5-14 Speed up and efficiency of parallel gauss-seidel iterative solution of Laplace's equation in clustered 1D vs Decomposition 2D, for sixteen processers | . 87 |

| Figure B-0-1 matrix-point of-view and processor point-of-view for PUMMA, SUMMA, and DIMMA                                                                         | 107  |

| Figure B-0-2 PUMMA Single Data Broadcasting                                                                                                                       | 108  |

| Figure B-0-3 PUMMA Multiple Data Broadcasting 1                                                                                                                   | 109  |

| Figure B-0-4 PUMMA Multiple Data Broadcasting 2                                                                                                                   | 110  |

| Figure B-0-5 SUMMA algorithm                                                                                                                                      | 111  |

| Figure B-0-6 SUMMA Algorithm iterations                                                                                                                           | 111  |

| Figure B-0-7 DIMMA Algorithm                           | 114 |

|--------------------------------------------------------|-----|

| Figure B-0-8 Coppersmith and Winograd 2010 (1/2) [13]  | 118 |

| Figure B-0-9 Coppersmith and Winograd 2010 (2/2) [102] | 119 |

# **List of Symbols**

f = number of arithmetic operations units

$t_f$  = time per arithmetic operation <<  $t_c$  (time for communication)

c = number of communication units

q = f / c average number of flops per communication access.

Speedup  $S_p = q (t_f/t_c)$

nproc = number of processors

nblock = number of blocks

## **Chapter 1 - Introduction**

The need for vast computing power in so many fields like forecasting the weather, analyzing DNA material, simulating earthquakes etc. has led for looking for parallel and distributed computing, in the light of the limited speed of the classic computers and processing power due to the physical constraints preventing frequency scaling. On the other hand, the physical limits been achieved at the hardware level in processors industry, which leads for opening the doors to design parallel processors in the mid of 1980's by introducing the parallel processing and networks of computers [1-8]. By the 1990's, the Single Instruction Multiple Data (SIMD) technology show up, and later multi-core platforms in the mainstream industry such as multi-core general purpose architectures (CPUs) and Graphics Processing Units (GPUs) where several cores working in parallel inside the processor chip [4, 9, 10-12]. New processors show vast computing power [4, 6, 13-15]. Multi-core i7 CPU is the most updated parallel CPU produced by Intel at PC level; While latest NVidia Graphics Processing Unit has 1536 core at its VGA card Tesla K10, which has two GPUs, which implies  $1536 \times 2 = 3,072$  processors running in parallel [16], which is needed for applications of seismic, image, signal processing, video analytics. This implies that the future software development must support multi-core processors, which is parallel processing.

Parallel processing has opened an era to have super computing power at the cost of several PCs. So, connecting several PCs into a grid could be utilized as one single supercomputer by the help of certain algorithm to manage the distributing of the load among the active connected PCs. Well, parallel processing did not stop here, but parallel processing extends to include computers and super computers connected over internet, where the load could be distributed over connected super computers to have enormous parallel processing power.

All parallel algorithms until the moment depended in decomposing the data of a problem into blocks and perform the functionality on it, in parallel mode taking in consideration the data and the functional dependency among the data.

Data Decomposition in general having two modes, one dimension (1D), where the data will be set of strips, where each processor will process one single strip at a time; and the other mode is two dimensions decomposing (2D), where the data will be set of blocks, and each processor will process single block at a time.

In addition, existing parallel algorithms did not address and utilize the parallel capabilities of the new processors, like multicore and other enhancement like cache memory and wide address bus of 64 bit. All parallel algorithms have kept looking at the processor on the old architecture design. For example, they are considering the grain applications, where the application will be divided into the most simple functions, so each processor will process these simple functions and getting the next afterword; while all these algorithms are not looking at high capabilities of the new processors, where it can process more than a function at a time, dual core processors processes two functions a time, while Intel Xeon Phi processor has 61 cores, which implies it processes 61 functions at a time. Existing parallel algorithms sends one single function to each processor regardless number of cores

it has. In addition, the new processors architecture has different levels of cache memory which allows for more data upload capacity to reduce the access time of RAM, so cache memory leads to faster processing for complex functions which need huge chunk of data; Existing parallel algorithms do not consider the availability of cache memory and keep send simple math functions to each processor, which is a bad exploitation of modern architecture processors.

In this thesis, new technique for parallel processing will be introduced, which will overcome the drawbacks of the previous algorithms. The technique is called ITPMMA algorithm, it depends on dividing the problem into set of tasks, which implies the data will not be decomposed in ITPMMA algorithm, and instead the problem will be decomposed into independent sets of operations, where each processor will execute independent operations and will upload what data it needs. In addition, ITPMMA algorithm will utilize the capabilities of the parallel and multi-core processors, which is absent in the existing parallel algorithms.

### 1.1. Motivation

Numerical problems consume a lot of processing resources which leads to utilize the parallel processing architecture. Since 1969, parallel algorithms start showing up, [17-21]. Parallel Matrix Multiplication algorithms were one of the earliest parallel processing algorithms that appeared since then. So, since 1969 for homogenous clusters like Systolic algorithm [22], Cannon's algorithm [23], Fox and Otto's algorithm [24], PUMMA (Parallel Universal Matrix Multiplication) [25], SUMMA (Scalable Universal Matrix Multiplication) [26] and DIMMA (Distribution Independent Matrix Multiplication) [27]. All these algorithms had been designed for distributed memory platforms, and most of them use the

popular ScaLAPACK library [28, 29], which includes a highly-tuned, very efficient routine targeted to two-dimensional processor grids.

PUMMA algorithm maximizes the reuse of the data that have been hold in the upper levels of the memory hierarchy (registers, cache, and /or local memory) [16]. PUMMA, which had been developed in 1994, did not address the time consumption by exchanging intermediate results between processors.

SUMMA algorithm, been developed in 1997. It has introduced the pipelining in PUMMA to maximize reuse of data. In addition, SUMMA reformulated the blocking method in terms of matrix-matrix multiplications instead of matrix-vector multiplications, which reduced the communication overhead [26]. In general, SUMMA did not address the time consumption of the communication between processors. In addition, SUMMA did not address the cache memory of the modern processors.

On the same year, 1997, Choi [27] has developed DIMMA algorithm. "The algorithm introduced two new ideas: modified pipelined communication scheme to overlap computation and communication effectively; and to exploit the least common multiple (LCM) block concept to obtain the maximum performance of the sequential BLAS – Basic Linear Algebra Subprograms – routine in each processor" [27]. But still, DIMMA did not address the huge time consumed on communication between processors to exchange the intermediate results.

In 2005, NGUYEN et al. [29] combined the use of Fast Multipole Method (FMM) algorithms and the parallel matrix multiplication algorithms, which gave remarkable results. Nevertheless, the algorithm still suffers data dependency and high communication

cost among the processors. Moreover, the algorithm does not address heterogeneous environments.

In 2006, Pedram et al. [30], have developed high-performance parallel hardware engine for matrix power, matrix multiplication, and matrix inversion, based on distributed memory. They have used Block-Striped Decomposition (BSD) algorithm directly to implement the algorithm. There was obvious drawback related to processors' speed up efficiency. The algorithm reduces memory bandwidth by taking advantage of reuse data, which results in an increase in data dependencies.

On 2008 James Demmel developed a new algorithm to minimize the gap between computation and communication speed, which continues to widen [31]. The performance of sparse iterative solvers was the aim of this algorithm, where it produced speedup of over three times of serial algorithm. In fact, the increasing gap between computation and communication speed, is one of the main points to be addressed by reducing the communication between processors as much as possible. The algorithm still suffers data dependency and communication; especially for large matrices sizes.

In 2008 Cai and Wei [32] developed new matrix mapping scheme to multiply two vectors, a vector and a matrix, and two matrices which can only be applied to optical transpose interconnection system (OTIS-Mesh), not to general OTIS architecture, to reduce communication time. They have achieved some improvements compared to Cannon algorithm, but it was expensive in term of hardware cost. In addition, the algorithm did not add any new value in term of algorithm design.

In 2009, Sotiropoulos and Papaefstathiou implement BSD algorithm using FPGA device [33]. There was no achievement in terms of reducing data dependencies and communication cost.

In 2012, Nathalie Revol and Philippe Théveny developed new algorithm, called "Parallel Implementation of Interval Matrix Multiplication" to address the implementation of the product of two dense matrices on multicore architectures [34]. The algorithm produced accurate results but it fails to utilize the new features of the multicore architectures processors, as it has targeted in advance.

In 2013 Jian-Hua Zheng [35] proposed new technique based in data reuse. It suffers from a lot of data dependency and high communication cost.

In 2014, another decomposition technique called Square-Corner instead of Block Rectangle partition shapes to reduce the communication time has been proposed in [36]. The research was limited to only three heterogeneous processors. For some cases, they have reported less communication time and therefore showed a performance improvement.

Also, in 2014 Khalid Hasanov [37] introduced hierarchy communication scheme to reduce the communication cost to SUMMA algorithm. Although achieved some better performance, pre ITPMMA algorithm drawbacks like data dependency and communication cost are still there. Moreover, this algorithm is for homogenous environment.

Other algorithms have been designed later on to enhance the process of matrix multiplication and to reduce the processing time. In 2014, Tania Malik et al. [38] proposed new network topology to decrease communication time among the processors. The algorithm suffers from more data dependencies between the processors. The major

drawback of all previous parallel algorithms developed until now need homogenous processor architecture, and never addressed heterogeneous processors, except NGUYEN et al. [29], which conclude very negative results, so, by executing these algorithms in a grid of several PCs – heterogeneous environment – would have a lot of incompatible latency factors.

Having homogenous environment, all parallel algorithms, either for parallel matrix multiplication as we will see in this thesis, or for any numerical problem else, all existing algorithms suffer from classic drawbacks, like:

- 1. The optimal size of the block of the decomposed matrices.

- 2. The communication time of the exchanged messages among the processors, which is proportional to number of processors and number of the blocks of the decomposed matrices.

- 3. Data and functional dependency between the processors.

- 4. Poor load balance especially with non-square matrices.

### 1.2. Originality

In this thesis, a new novel framework for parallel processing has been developed to add the following new values:

- 1. Reducing the communication time among the parallel processors to ZERO.

- 2. No processor becomes idle or in hold, waiting other processors output until the parallel operations over.

- 3. Eliminating the need for a certain topology of processors.

### 1.3. Objectives

Thesis objectives to develop a novel framework for parallel processing which implies reconstruct the parallel problem into independent tasks to:

- 1. Reduce the idle time of the processors to increase the efficiency, and this to be achieved by:

- a. Proper load balance among the processors.

- Utilizing the modern processor architecture capabilities in term of multicore and cache memories of different levels.

- 2. Reduce the communication time among the processors, by eliminating the data dependencies by reconstructing the parallel problem into set of independent tasks, to reduce the communication time among processors to zero.

On the other hand, for numerical problems where reconstructing the parallel problem into independent tasks is not within hands, like solving Laplace equation in parallel, a new data decomposing technique is developed, to reduce the communication time among the processors, and reduce idle time of the processors, to increase the efficiency.

#### 1.4. Methodology

To satisfy the objectives of this thesis, I am to follow the procedure below:

- 1. Review literature of parallel matrix multiplication and data decomposition techniques.

- 2. Study in details different parallel algorithms and data decomposition techniques to find out its drawbacks.

- Develop common diagram to setup new framework for parallel processing to address the drawbacks of the previous algorithms.

- 4. Develop new parallel matrix multiplication algorithm and new data decomposition technique within the new framework.

- 5. Test the new framework on small environment of 4 and 16 processors.

- 6. Test the new framework on the advanced supercomputer CLUMEQ.

- 7. Compare the results of the performance of the new framework with benchmark algorithms like Cannon algorithm and Fox algorithm.

### 1.5. Thesis Organization

This thesis is organized into six chapters. Chapter I is an introduction for the thesis to show the motivation, originality, objectives of the research and the methodology.

Chapter II, titled "Matrix Multiplication", I will discuss the common Parallel Matrix Multiplication Algorithms in terms of performance, which includes speed up, time complexity, load balancing, data dependencies.

Chapter III, titled "ITPMMA algorithm for Parallel Matrix Multiplication (STMMA)", presents the proposed algorithm followed by the results and comparisons with parallel matrix multiplication algorithms.

Chapter IV, titled "Analysis and Results", presents the experimental results which showed that the ITPMMA algorithm achieved significant runtime performance on CLUMEQ supercomputer and also a considerable performance compared by other algorithms like Cannon Algorithm and Fox Algorithm. In these experiments I have used up to 128 processors in parallel, and about 40000 matrices size.

Chapter V, titled "The clustered 1 Dimension decomposition technique" presents the new data decomposition technique, developing parallel solution for Laplace equation using Gauss-Seidel iterative method, and test the results and compare it with same of 1 dimension and 2 dimensions data decomposition techniques.

Finally, Chapter VI presents the conclusion and explores the opportunities for the future that build upon the work presented in this dissertation.

## **Chapter 2 - Matrix Multiplication**

#### 2.1.Introduction

In this chapter I will address the matrix multiplication problem in serial and parallel mode. This problem will be used to describe the efficiency of the parallel algorithms; in fact, matrix multiplication has been used as benchmark problem for parallel processing algorithms for several reasons:

- 1. It is easily scaled problem for a wide range of performance; its size grows like N<sup>3</sup> for matrices of order N.

- 2. It has two nested loops plus the outer loop, total of three loops; the most inner loop consists at least a single multiply and add operation. Where the loops can be parallelized or to achieve high performance.

- 3. Computation independency, where the calculation of each element in the result matrix is independent of all the other elements.

- 4. Data independence, where the number and type of operations to be carried out are independent of the data type of the multiplied matrices.

- 5. Different data types like short and long integers and short and long floating-point precision can be used, which promises for different levels of tests. Also it allows for utilizing of the capabilities of the new processors, which has high cache memories, by

- multiplying long type matrices, which needs high size of cache memory for intermediate results.

- 6. Number of floating point operations (flops) easily is calculated.

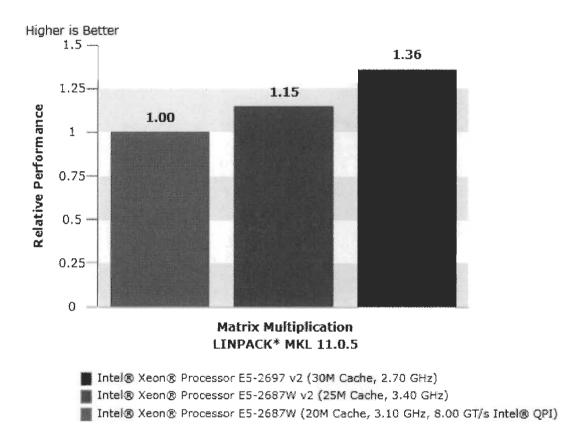

- 7. Matrix multiplication is used as bench mark problem to test the performance of so many processors, like Intel, as shown in the figure 2-1, below.

Figure 2-1 Matrix Multiplication problem as benchmark problem for Intel processor performance [39].

In this chapter, some important aspects of matrix multiplication will be addressed, together with the outstanding characteristics of the already developed parallelization algorithms, like cannon and fox algorithms.

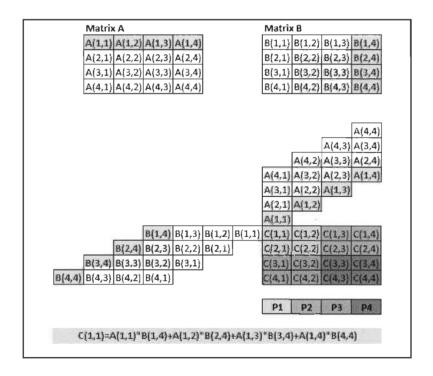

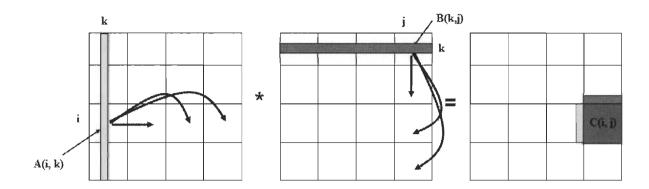

### 2.2. Matrix Multiplication Definition

It is defined between two matrices only if the number of columns of the first matrix is the same as the number of rows of the second matrix. If A is an i-by-k matrix and B is a k-by-j matrix, then their product AB is an i-by-j matrix, is denoted by  $C_{ij}=A_{ik}\times B_{kj}$ , which be given by

$$C_{ij} = \sum_{k=1}^{n} A_{i,k} \times B_{k,j}$$

Eq. 21

And it is calculated like

$$\begin{pmatrix} C_{11} & C_{12} & C_{13} & C_{14} \\ C_{21} & C_{22} & C_{23} & C_{24} \\ C_{31} & C_{32} & C_{33} & C_{34} \\ C_{41} & C_{42} & C_{43} & C_{14} \end{pmatrix} = \begin{pmatrix} A_{11} & A_{12} & A_{13} & A_{14} \\ A_{21} & A_{22} & A_{23} & A_{24} \\ A_{31} & A_{32} & A_{33} & A_{34} \\ A_{41} & A_{42} & A_{41} & A_{44} \end{pmatrix} \times \begin{pmatrix} B_{11} & B_{12} & B_{13} & B_{14} \\ B_{21} & B_{22} & B_{23} & B_{24} \\ B_{31} & B_{32} & B_{33} & B_{34} \\ B_{41} & B_{42} & B_{43} & B_{44} \end{pmatrix}$$

Eq. 2-2

So,

$$C_{11} = A_{11} \times B_{11} + A_{12} \times B_{21} + A_{13} \times B_{31} + A_{14} \times B_{41}$$

Eq. 2-3

Which is different than BA, which is denoted by  $D_{ij} = B_{kj} \times A_{ik}$ , given by

$$D_{ij} = \sum_{k=1}^{n} B_{k,j} \times A_{i,k} \quad \text{Eq. 2-4}$$

So,

$$D_{11} = B_{11} \times A_{11} \times + B_{12} \times A_{21} + B_{13} \times A_{31} + B_{14} \times A_{41}$$

Eq. 2-5

Which implies matrix multiplication is not commutative; that is, AB is not equal to BA. The complexity of matrix multiplication, if carried out naively, is  $O(N^3)$ , where N is the size of

product matrix C. So for the Matrix multiplication of  $4\times4$  size, the complexity is  $O(N^3) = O(4^3) = 64$  operations, or the timing of 64 operations.

In 1969, Volker Strassen has developed Strassen's algorithm, has used mapping of bilinear combinations to reduce complexity to  $O(n^{\log 2(7)})$  (approximately  $O(n^{2.807...})$ ). The algorithm is limited to square matrix multiplication which is considered as a main drawback.

In 1990, another matrix multiplication algorithm developed by Don Coppersmith and S. Winograd. The algorithm has complexity of  $O(n^{2.3755})$ . [40]

In 2010, Andrew Stothers gave an improvement to the algorithm,  $O(n^{2.3736})$  [41]. In 2011, Virginia Williams combined a mathematical short-cut from Stothers' paper with her own insights and automated optimization on computers, improving the bound to  $O(n^{2.3727})$  [42].

### 2.3. Serial Matrix Multiplication Algorithm

### 2.3.1. Serial Algorithm

The serial algorithm for multiplying two matrices is taking the form:

```

for (i = 0; i < n; i++)

for (j = 0; i < n; j++)

c[i][j] = 0;

for (k = 0; k < n; k++)

c[i][j] += a[i][k] * b[k][j]

end for

end for</pre>

```

with the complexity  $O(N^3) = O(4^3) = 64$  operations, or the timing of 64 operations.

#### 2.3.2. Strassen's algorithm

In 1969, Professor V. Strassen [36] developed new algorithm known by his name, Strassen's algorithm, where the complexity of his algorithm is  $O(N^{log7/log2}) = O(N^{log27})$  =  $O(N^{ln7})$ , which will be equal to  $O(4^{log27}) = 14.84$ , which is less than 64, i.e. to multiply two 4×4 matrices using Strassen's algorithm, the algorithm needs the time of 14.84 operations, rather than the time of 64 operations using the standard algorithm.

To simplify Strassen's algorithm, I will implement it on the following matrices multiplications:

$$\begin{pmatrix} C_{11} & C_{12} \\ C_{21} & C_{22} \end{pmatrix} = \begin{pmatrix} A_{11} & A_{12} \\ A_{21} & A_{22} \end{pmatrix} \times \begin{pmatrix} B_{11} & B_{12} \\ B_{21} & B_{22} \end{pmatrix}$$

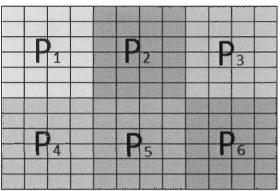

So, we run the below 7 quantities:

$$P_1 = (A_{12} - A_{22}) \times (B_{21} + B_{22})$$

$$P_2 = (A_{11} + A_{22}) \times (B_{11} + B_{22})$$

$$P_3 = (A_{11} - A_{21}) \times (B_{11} + B_{12})$$

$$P_4 = (A_{11} + A_{12}) \times B_{22}$$

$$P_5 = A_{11} \times (B_{12} - B_{22})$$

$$P_6 = A_{22} \times (B_{21} - B_{11})$$

$$P_7 = (A_{21} + A_{22}) \times B_{11}$$

And produce the product matrix C, we run the below summations

$$C_{11} = P_1 + P_2 - P_4 + P_6$$

$$C_{12} = P_4 + P_5$$

$$C_{21} = P_6 + P_7$$

$$C_{22} = P_2 - P_3 + P_5 - P_7$$

The main drawback of Strassen's algorithm is the size product matrix should be product of 2, i.e.  $2^1$ ,  $2^2$ ,  $2^3$ ,  $2^4$ ,  $2^5$ , ..., so for matrices multiplication of size 5, where  $2^2 < 5 < 2^3$ , we need to pad the matrices by zeros, till we have 8×8 matrices and multiply them. Recent studies study the arbitrary size of the multiplied matrices by Strassen algorithm in more details [43] but without getting better performance. So for Strassen's algorithm for matrices multiplication of size 3×3, we have 7 multiplies and 18 adds. The complexity of the algorithm for matrices multiplication of size n×n can be computed as 7\*T(n/2) + 18\*(n/2)2=  $O(N^{Log_27})$ =  $O(8^{Log_27})$ =  $O(2^{3^{log_27}})$ =  $O(2^{log_27})^3$  =  $7^3$ ; while if we use standard matrices multiplication, the complexity is  $O(5^3) = 5^3 = 125$  which is less than  $7^3 = 343$ , which is 2.744 times the complexity of Strassen's algorithm. And the difference become so huge when we have big matrix size, let us say a matrices multiplication of size 127×127, and 127 is not multiplicand of 2, the nearest multiple of 2 is 128, so, 128×128 matrices multiplication, we do have complexity of  $O(128^{Log_27}) = O(2^{log_27}) = O(2^{log_27})^7 = 7^7 = 0$ 823,543; while if we go for the standard matrices multiplication where the complexity is  $O(N^3) = O(127^3) = 2,048,383$ ; which is 2.49 times the complexity of Strassen's algorithm, so Strassen's algorithm has positive effect. While if we consider matrices multiplication of size 70×70, again, we need to pad it with zeros till we reach  $128\times128$  matrices multiplication, where the complexity of standard multiplication is  $O(N^3) = O(70^3) = 343,000$ , so, the complexity of Strassen's algorithm is 2.4 times the complexity of standard multiplication, so Strassen's algorithm has negative effect.

It is clear that the evaluations of intermediate values P<sub>1</sub>, P<sub>2</sub>, P<sub>3</sub>, P<sub>4</sub>, P<sub>5</sub>, P<sub>6</sub>, and P<sub>7</sub> are independent and hence, can be computed in parallel.

Another drawback of Strassen's algorithm is the communication between the processors [44, 45, and 46]. Some other researches [47] focus on optimizing the communication between processors at the execution of Strassen's algorithm, where they could obtain some success at different ranges according to the size of the matrices and number of processors; but they could not eliminate the communication among the processors to zero.

On the other hand, many researches have tried to extract parallelism from Strassen's algorithm, and standard matrices multiplication algorithm [48], and many researches have tried to extract the algorithm on multi-core CPUs [49, 50, and 51] to exploit more performance. In 2007, Paolo D'Alberto, Alexandru Nicolau [52] have tried to exploit Strassen's full potential across different new processors' architectures, and they could achieve some success for some cases, but still, they have to work with homogenous processors. While in 2009, Paolo D'Alberto, Alexandru Nicolau have developed adaptive recursive Strassen-Winograd's matrix multiplication (MM) that uses automatically tuned linear algebra software [53], to achieve up to 22% execution-time reduction for a single core system and up to 19% for a two dual-core processor system.

### 2.4. Parallel Matrix Multiplication Algorithms

Parallel algorithms of matrices multiplication are parallelization of the standard matrices multiplication method.

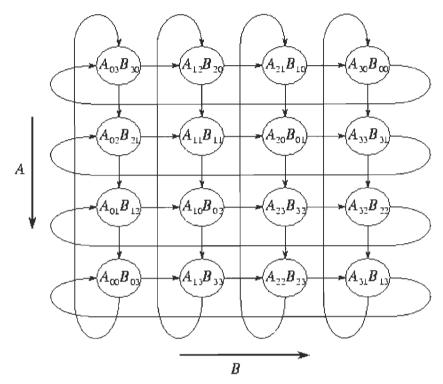

### 2.4.1. Systolic Algorithm

One of the old parallel algorithms returns to 1970, but still active algorithm till moments [54]. It is limited to square matrix multiplication only. In this algorithm, matrices A, B are decomposed into submatrices of size  $\sqrt{P} \times \sqrt{P}$  each, where P is number of processors. The basic idea of this algorithm is the data exchange and communication occurs between the nearest-neighbors.

Figure 2-2 Systolic Algorithm

Figure 2-3 Layout of the A and B matrices in the systolic matrix-matrix multiplication algorithm for A4x4×B4x4 task mesh. The arrows show the direction of data movement during execution of the systolic algorithm. [55]

Table 2-1 The performance of the algorithm being studied by [33]

| Task                                 | Execution time                  |  |

|--------------------------------------|---------------------------------|--|

| Transpose B matrix                   | $2n^2 t_f$                      |  |

| Send A, B matrices to the processors | $2m^2p t_c$                     |  |

| Multiply the elements of A and B     | $m^2 n t_f$                     |  |

| Switch processors' B sub-matrix      | $n^2 t_c$                       |  |

| Generate the resulting matrix        | $n^2 t_f + n^2 t_e$             |  |

| Total execution time                 | $t_f(m^2 n + 3n^2) + t_c(4n^2)$ |  |

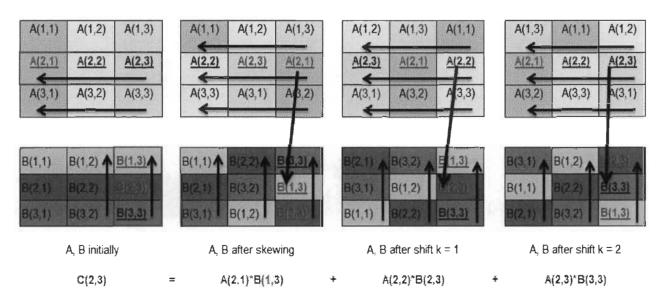

### 2.4.2. Cannon Algorithm

It is a memory efficient if the multiplied matrices are square. The blocks of matrix A to rotate vertically while matrix B blocks to rotate horizontally, this can be handled using circular shifts to generate the product matrix C. In fact, it replaces the traditional loop

$$C_{i,j} = \sum_{k=0}^{\sqrt{p}-1} A_{i,k} \times B_{k,j}$$

With the loop

$$C_{i,j} = \sum_{k=0}^{\sqrt{p}-1} A_{i,(i+j+k)mod\sqrt{p}} \times B_{(i+j+k)mod\sqrt{p},j}$$

or the Cannon Matrix multiplication algorithm

The Pseudo-code for the Cannon Matrix multiplication algorithm

% p number of processors % s size of the matrix For i = 0 to p - 1

A(i, j)=A(i,(i+j) mod p %left-circular-shift row i of A by i shifts (skew of A)

For i = 0 to p - 1

B(i, j)=B((i+j) mod p, j) %up-circular-shift row j of B by j shifts (skew of B)

For (i = 0 to p-1) and (j = 0 to p-1)

$C(i,j) = C(i,j) + \sum_{k=1}^{p} A(i,k) * B(k,j)$

$A(i, j)=A(I,(i-j) \mod p$ % left-circular-shift each row of A by 1

$B(i, j)=B((i-j) \mod p, j)$ % up-circular-shift each column of B by 1

Figure 2-4 Cannon's algorithm layout for n = 3

```

|| Skew A \& N | for i = 0 to s-1 || s = sqrt(p) |

|left-circular-shift row i of A by i || cost = s*(\alpha + n2/p/\beta) |

| for i = 0 to s-1 || cost = s*(\alpha + n2/p/\beta) |

| Multiply and shift | | cost = 0 to s-1 | | | cost = 0 to s-1 | | cost = 0 t

```

- Total Time =  $2*n3/p + 4*s*\alpha + 4*\beta*n2/s$

- Parallel Efficiency = 2\*n3 / (p \* Total Time)=  $1/(1 + \alpha * 2*(s/n)3 + \beta * 2*(s/n))$ = 1/(1 + O(sqrt(p)/n))

- Grows to 1 as n/s = n/sqrt(p) = sqrt(data per processor) grows

- Better than 1D layout, which had Efficiency = 1/(1 + O(p/n))

Table 2-2 The performance of the algorithm being studied by [56]

| Task                                 | Execution time                         |  |

|--------------------------------------|----------------------------------------|--|

| Shift A, B matrices                  | 4n <sup>2</sup> t <sub>f</sub>         |  |

| Send A, B matrices to the processors | $2n^2 t_c$                             |  |

| Multiply the elements of A and B     | n <sup>2</sup> t <sub>r</sub>          |  |

| Shift A, B matrices                  | $2(mn t_c + 2m^2 n t_f)$               |  |

| Generate the resulting matrix        | $n^2 t_f + n^2 t_e$                    |  |

| Total execution time                 | $t_f(5m^2 n + 5n^2) + t_c(2n^2 + 2mn)$ |  |

### 2.4.3. Fox and Otto's algorithm

Fox's algorithm for multiplication organize  $C = A \times B$  into submatrix on a P processors. The algorithm runs P times, in each turn, it broadcasts corresponding submatrix of A on each

row of the processes, run local computation and then shift array B for the next turn computation. The main disadvantages, it is applied only for square matrices.

This algorithm being written in general in HPJava, we still use Adlib.remap to broadcast submatrix, matmul is a subroutine for local matrix multiplication. Adlib.shift is used to shift array B, and Adlib.copy copies data back after shift, it can also be implemented as nested over and for loops.

```

Group p=new Procs2(P,P);

Range x=p.dim(0);

Range y=p.dim(1);

on(p) {

//input a, b here;

float [[#,#, ,]] a = new float [[x,y,B,B]];

float [[\#,\#,\ ,\ ]] b = new float [[x,y,B,B]];

float [[#,#, ,]] c = new float [[x,y,B,B]];

float [[\#,\#,\ ,\ ]] temp = new float [[x,y,B,B]];

for (int k=0; k<p; k++) {

over(Location i=x|:) {

float [[,]] sub = new float [[B,B]];

//Broadcast submatrix in 'a' ...

Adlib.remap(sub, a[[i, (i+k)%P, z, z]]);

over(Location j=y|:) {

//Local matrix multiplication ...

matmul(c[[i, j, z, z]], sub, b[[i, j, z,

z]]);

}

//Cyclic shift 'b' in 'y' dimension ...

Adlib.shift(tmp, b, 1, 0, 0); // dst, src, shift, dim,

mode;

Adlib.copy(b, tmp);

}

```

"Two efforts to implement Fox's algorithm on general 2-D grids have been made: Choi, Dongarra and Walker developed 'PUMMA' [50] for block cyclic data decompositions, and Huss-Lederman, Jacobson, Tsao and Zhang developed 'BiMMeR' for the virtual 2-D torus wrap data layout" [57].

### 2.5. Conclusion

In this chapter I have addressed the use of matrix multiplication as benchmark and the definition of matrix multiplication, serial algorithms and parallel algorithms.

Parallel algorithms for carrying out matrix multiplication in different architecture since 1969 had been studied and analyzed. Parallel algorithms for matrix multiplication have common mode, it is subdividing the matrices into small size matrices and distributing them among the processors to achieve faster running time.

We found out that although so many parallel matrix algorithms have been developed since Cannon Algorithm and Fox algorithm four decades ago, all these algorithms – described in Appendix B – still use the same methodology and framework of Cannon and Fox algorithms in term of data decomposition and communication among the processors. On addition, all these algorithms could not achieve a distinguished performance against both Cannon and Fox algorithms, which keep both algorithms as bench mark algorithms in parallel matrix multiplication.

Finally, Identification of BLAS, and the development till considering multi-core architecture had been shown in Appendix A.

# **Chapter 3 - ITPMMA algorithm for Parallel Matrix Multiplication (STMMA)**

#### 3.1.Introduction

Several parallel matrix multiplication algorithms had been described and analyzed in the previous chapter. All parallel matrix multiplication algorithms based on decomposing the multiplied matrices into smaller size blocks of data, the blocks will be mapped and distributed among the processors, so each processor run matrix multiplication on the assigned blocks; this will reduce the whole time of the matrix multiplication operation to less than the time needed to complete this operation by utilizing one processor. All existing parallel matrix multiplications algorithms suffer from four drawbacks:

- 1. To define the optimal size of the block of the decomposed matrices, so the whole operation can be produced by the minimum time. For example, multiplying matrices of size 64×64 over 4 processors, should the block size be 4×4 or 8×8 or 16×16.

- 2. The number of exchanged messages between the processors are highly time consuming; it is proportional to the number of the processors. On the other hand, the time of forwarding the messages relays partly on the network structure.

- 3. Data dependency between the processors, where some processors will stay idle waiting an intermediate calculation results from other processors. Data dependency increases as number of blocks/processors increases.

- 4. Some algorithms suffer from another drawback, which is the load balance, especially with non-square matrix multiplications.

In this chapter, new parallel matrix multiplication algorithm will be introduced, to overcome the above four drawbacks, which returns in vast difference in the performance in terms of processing time and load balance. For example, for a matrices multiplication of 5000×5000, it consumes 2812 seconds using cannon algorithm, while only 712 seconds needed using the new algorithm, which implies 4 times faster. I have implemented the algorithm initially using Microsoft C++ ver. 6, with MPI Library. I have execute it at Processors Intel(R) Core(TM) i5 CPU 760 @2.80GHz 2.79 GHz, the installed memory (RAM) was 4.00 GB, System type: 64-bit Operating System, Windows 7 Professional. Later I have implemented the algorithm using CLUMEQ supercomputer, where I have used up to 128 processors in parallel.

I will reference to the new algorithm by the name ITPMMA algorithm. The basic concepts of ITPMMA algorithm were published on "Sub Tasks Matrix Multiplication Algorithm (STMMA)", [59].

### 3.2.ITPMMA algorithm for Parallel Matrix Multiplication (STMMA)

Unlike previous algorithms, ITPMMA Algorithm for Parallel Matrix Multiplication does not define new data movement or circulation; instead, it generates independent serial tasks follows the serial matrix multiplications shown below:

```

1: for || I=0 to s-1 {

2: for J=0 to s-1 {

3: for K=0 to s-1 {

4: CIJ = CIJ + AIK ×BKJ }}}

```

ITPMMA Algorithm decomposes the parallel matrix multiplication problem into several independent vector multiplication tasks, keeping the processing details of each independent task to the processors, which are multicore processors, so I am utilizing the modern

architecture processors' capabilites. ITPMMA Algorithm has the advantage to utilize the up-to-date processor architecture features in terms of multicores and cache memories. In fact, ITPMMA Algorithm defines each independent task as set of instructions to produce one element of the result matrix. Each single set is fully independent of production of any other set, or independent task. Each single independent task is being processed by one single processor. Once each processor has completed the independent task been assigned to it, and produced an element of the result matrix, it processes the next independent task, to produce the next element, and so on. ITPMMA Algorithm implies:

- 1. Zero data dependences so better processors' utilization since no processor stays on hold, waits for other processors' output,

- 2. Zero data transfer among the processors of the cluster, so faster processing. Communications in ITPMMA Algorithm is limited to the time needed to send the independent tasks lists by the server node processor to different processors, and to the time needed to receive back alerts and results by the other processors to the server node processor.

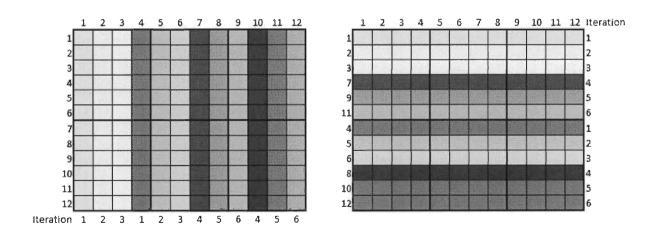

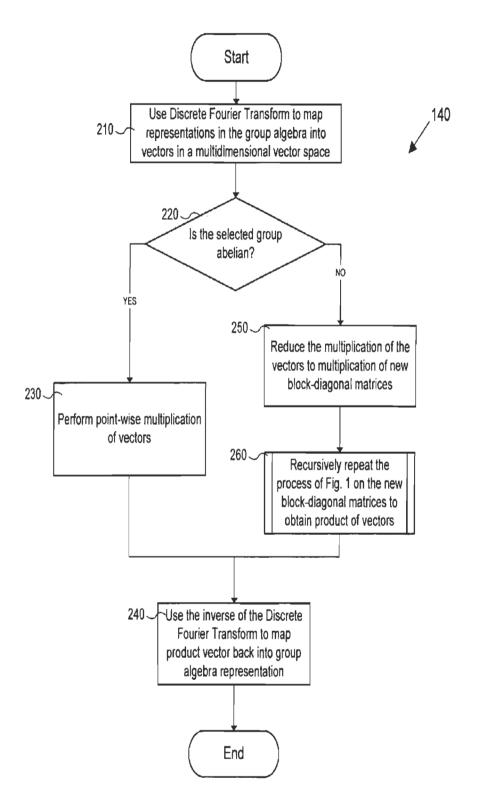

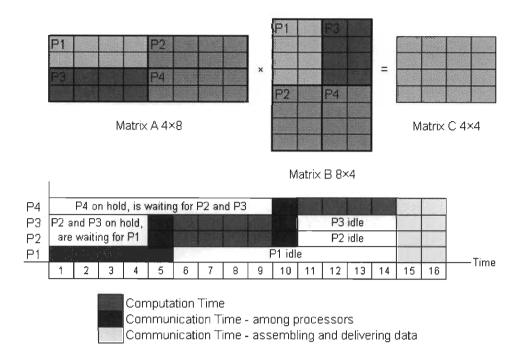

In this context ITPMMA Algorithm has advantages of efficient use of the processors' time. Figure 3-1 simulates the serial matrix multiplication using one single core processor. Figure 3-2 simulates the previous parallel algorithms. It is clear that both processors P2 and P3 are on hold, till processor P1 over and switch to idle status. On addition, processors P4 will not start processing till both P2 and P3 over. The efficiency of using the processors' time is so poor. Each processor computes for 4 units of time and 3 units for communication, and been on hold or idle for 9 units of time. So the computing efficiency of each processor is 4/16 =25%. On the other hand, figure 3-3 simulates parallel multiplication using new algorithm

which is called Independent Tasks Parallel Matrix Multiplication Algorithm (ITPMMA). Instead of decompose the data among the processors; we distribute the independent tasks among the processors. So, processor P1 should produce the first row of Matrix C shown in figure 2, while processor P2 should produce the second row of Matrix C, and processor P3 should produce the third row, finally processor P4 should produce the fourth row of Matrix C. For that, we need only 4 units of time to accomplish the tasks, in addition, no communication among the processors, also, no time for assembling the results, only to deliver it. One of the major advances of ITPMMA algorithm is efficiency of using the processors, no processor gets on hold or idle. The efficiency of each processor is 4/5 = 90%.

Figure 3-1, Serial Matrix Multiplication

Figure 3-2 Simulation of pre ITPMMA Algorithms

Figure 3-3 Simulation of ITPMMA Algorithm

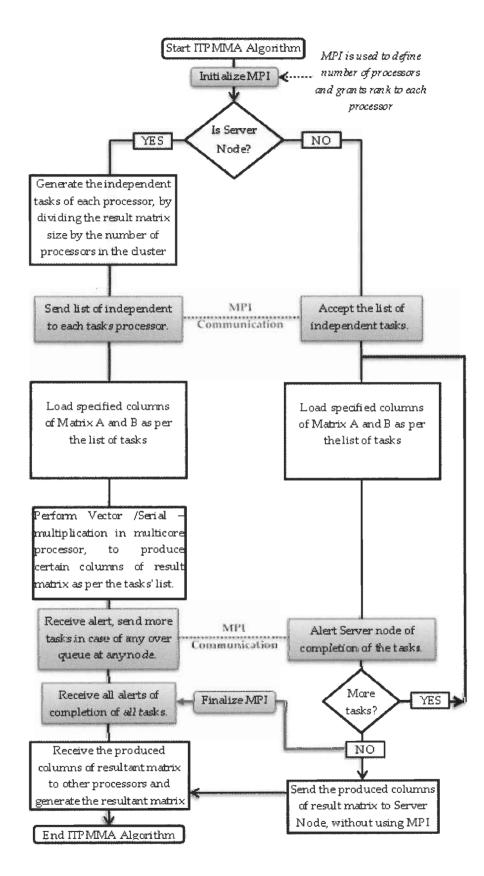

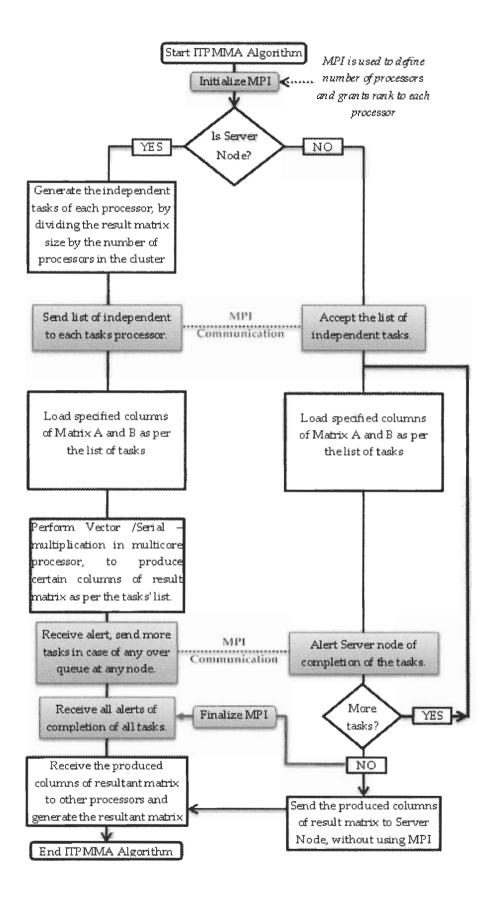

# 3.2.1. ITPMMA flowchart

ITPMMA Algorithm for parallel matrix multiplications, on the contrary of other parallel matrix multiplication algorithms, it depends on reformatting the matrix multiplication process into many independent vector multiplication operations, each vector multiplication operation will be carried out by single processor, to avoid any data dependency and processor-to-processor data transferring time. Figure 3-3 shows ITPMMA Algorithm flowchart.

Figure 3-4 ITPMMA Algorithm flowchart

ITPMMA Algorithm uses MPI library to define the number of active processors on the cluster and rank them. In addition, MPI library is used to transfer the lists of tasks to the processors and to forward task completion alerts from different processers to the node processor. So the server node: received bird sow

- 1. Defines the processors available in the parallel cluster and to rank them.

- Generate the the independent tasks, so produce an element of the result matrix is considered as independent task.

- 3. Divides the last of independent tasks by the number of active processors in the cluster. So for the output matrix of size 7000×7000 and number of processors is 128 active processors, (7000×7000)/128=382812.5, so 64 processors produce 382,812 independent tasks and 64 processors produce 382,813 independent tasks. So the time needed to process 7000×7000 matrix multiplication in parallel of 128 processors is equivalent process 620×620 in one processor.

- 4. Sends for each processor list of independent tasks to be carried out.

- 5. Receives from each processor alert of completion when all assigned tasks have been carried out.

- 6. Redistributes the processor of any faulted processor(s) to other active ones by sending extra tasks for the high computing power processors, once the initial sent list of tasks of these processors had been carried out. Redistribution includes shifting tasks from the over queued low computing power processors to the high computing ones; so this algorithm address the hetregenious environment.

MPI library will not be used to exchange any data at all, as all tasks are independent, so, no processor receives any data from another processor to be able to complete its work, nor any processor communicate with non-server node processor.

I will explain the algorithm using different four examples:

- 1. Square Matrix multiplication, and the size of the result matrix is multiple of the number of processors being used in parallel, like  $A_{4x4} \times B_{4x4} = C_{4x4}$ , for four processors in parallel; well, the size of the result matrix is  $4\times4$ , is multiple of the number of processor in use, which is 4.

- 2. Square Matrix multiplication, and the size of the result matrix is not multiple of the number of processors being used in parallel,  $A_{12x12} \times B_{12x12} = C_{12x12}$ , for eight processors in parallel; it is obvious that 12 is not multiple of 8.

- 3. Non Square Matrix multiplication, and the size of result matrix is multiple of the number of the processors being used in parallel, like  $A_{12x12} \times B_{12x16} = C_{12x16}$ , for four processors in parallel; it is obvious that both 12 and 16 are multiple of 4.

- 4. Non Square Matrix multiplication, and the size result matrix is not multiple of the number of the processors being used in parallel, like  $A_{12x12} \times B_{12x18} = C_{12x18}$ , for four processors in parallel; it is obvious that 18 is not multiple of 4.

The second and the fourth example will help me to show how ITPMMA algorithm will address the problem of load balance to be very obvious. On the other hand all previous algorithms for parallel matrix multiplication are limited to square matrix multiplication only.

### 3.3.ITPMMA applied to different matrices sizes

3.3.1. Square Matrix multiplication, size of the result matrix is multiple of the number of processors in parallel

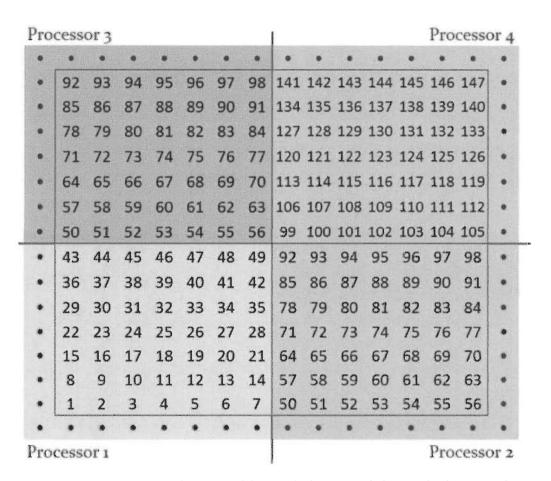

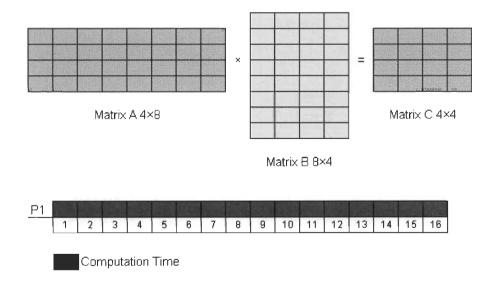

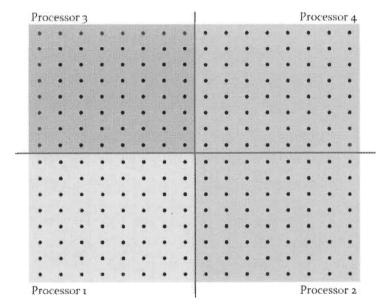

In this example,  $A_{4x4} \times B_{4x4}$  being executed on four processors  $P_0$ ,  $P_1$ ,  $P_2$ , and  $P_3$ , matrix A will be sent to all processors, while one single column of matrix B will be sent to each matrix, so each processor produces part of the matrices multiplication result as shown of Figure. 3-4.

Figure 3-5 Task distribution of  $A_{4x4} \times B_{4x4}$ , where each processor will produce part of the result matrix  $C_{4x4}$

Each processor processes separate independent tasks, so no messages of intermediate results will be exchanged, instead each processor produces what it needs when needed, that is to reduce the time consumed for exchange intermediate results between the processors

and to avoid data dependencie which put the processor on hold waiting results from other processors. So, P<sub>0</sub> will execute the code shown in Figure 3-5:

```

1: for J=0 to 3{

2: for K=0 to 3 {

3: C<sub>J0</sub> = C<sub>J0</sub> + A<sub>3K</sub> ×B<sub>KJ</sub>

4: }

5: }

```

Figure 3-6: Pseudo code executed by processor P0

While P<sub>1</sub> will execute the code shown in Figure 3-6:

```

1: for J=0 to 3 {

2: for K=0 to 3 {

3: C<sub>J1</sub> = C<sub>J1</sub> + A<sub>1K</sub> ×B<sub>KJ</sub>

4: }

5: }

```

Figure 3-7: Pseudo code executed by processor P1

While P2 will execute the code shown in Figure 3-7:

```

1: for J=0 to 3 {

2: for K=0 to 3 {

3: C<sub>J2</sub> = C<sub>J2</sub> + A<sub>2K</sub> ×B<sub>KJ</sub>

4: }

5: }

```

Figure 3-8: Pseudo code executed by processor P2

While P3 will execute the code shown in Figure 3-8:

```

1: for J=0 to 3{

2: for K=0 to 3 {

3: CJ3 = CJ3 + A3K ×BKJ

4: }

5: }

```

Figure 3-9: Pseudo code executed by processor P3

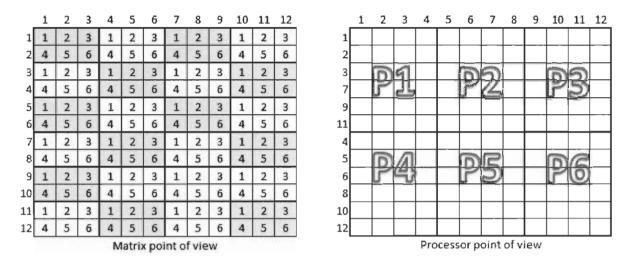

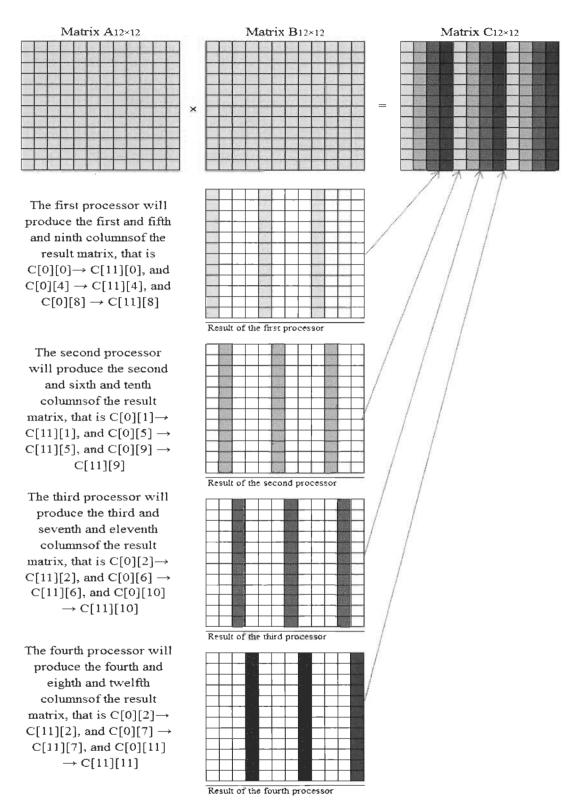

As we can see, no processor waits its entries from another processor(s), and no processor sends some results to other processor, so we could reduce the data dependency and exchanged messages to zero, which has played backward role on the performance of the previous parallel matrix multiplications. To generalize the case mentioned above, for different matrices size, I will use the example of  $A_{12x12} \times B_{12x12} = C_{12x12}$ , for four parallel processors. So, each processor will produce three columns of the matrix C, processor  $P_0$  will produce three columns, these are the first and fifth and ninth columns of the matrix  $C_{12x12}$ , Figure 3-9 shows task distribution of  $A_{12x12} \times B_{12x12} = C_{12x12}$ .

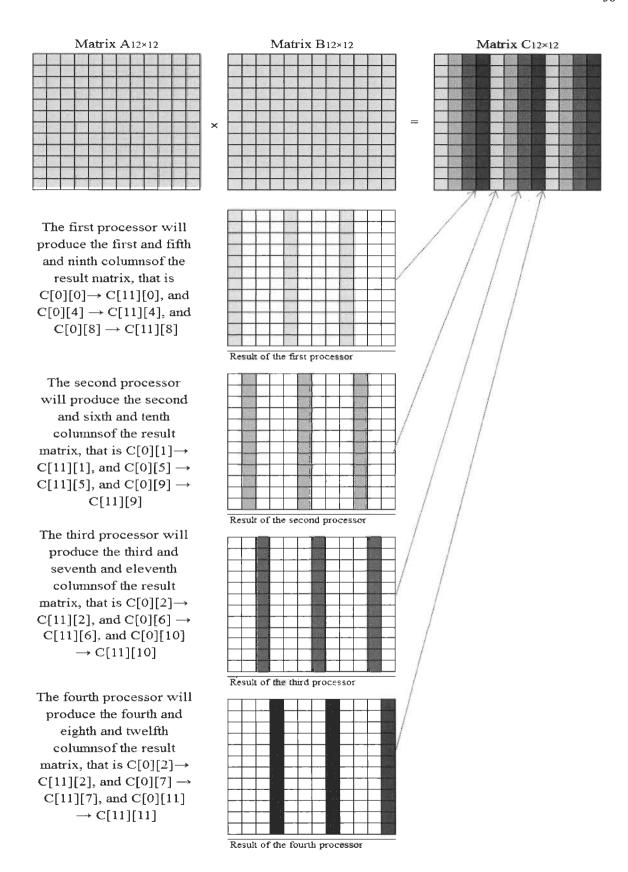

Figure 3-10 Task distribution of  $A_{12x12} \times B_{12x12}$ , where each processor will produce part of the result matrix  $C_{12x12}$

Processor 0 executes the code shown in Figure 3-10, to produce the first and the fifth and the ninth columns of the result matrix  $C_{12x12}$ .

```

1: for J=0 to 11 {

2: for K=0 to 11 {

3:    CJ0 = CJ0 + AOK ×BKJ

4:    }

5: }

1: for J=0 to 11 {

2: for K=0 to 11 {

3:    CJ4 = CJ4 + A4K ×BKJ

4:    }

5: }

1: for J=0 to 11 {

2: for K=0 to 11 {

3:    CJ8 = CJ8 + A8K ×BKJ

4:    }

5: }

```

Figure 3-11: Pseudo code executed by processor P0, to produce the first and the fifth and the ninth columns of the result matrix  $C_{12x12}$

While processor  $P_1$  produces different three columns, these are the second and sixth and tenth columns of the matrix  $C_{12\times12}$ , and so on for the remaining processors. Figure 3-11 shows the details of ITPMMA algorithm for the multiplication of  $A_{12x12} \times B_{12x12}$ , using four processors in parallel.

Figure 3-12:  $A_{12x12} \times B_{12x12}$  using ITPMMA algorithm for parallel matrix multiplication

The tasks are fully independent tasks – so no processor needed to exchange data with other processors – so there was no time being wasted by exchanging messages, and no processor has stayed idle waiting its input from other processors, well, this is the essence of ITPMMA algorithm.

# 3.3.2. Square Matrix multiplication, size of the result matrix is not multiple of the number of processors in parallel

For this case, the size of the multiplied matrices is not multiple of the number of the processor. In this example, we are to multiply  $A_{12x12} \times B_{12x12}$ , while the number of processors is eight, where 12 is not multiple of 8. In this case, we have to overcome this issue, and schedule the independent tasks between the processors equally, so the load is balanced, and no processor will stay idle while other processors still overloaded. So, we can run the schedule shown in Table 3-1, which satisfy the criteria of ITPMMA algorithm.

Table 3-1 Tasks to be performed by each processor

| Processor | Tasks to be performed          |                                  |

|-----------|--------------------------------|----------------------------------|

| P0        | C[0][0]→C[11][0]               | $C[0][8] \rightarrow C[5][8]$    |

| P1        | C[0][1]→C[11][1]               | C[6][8]→C[11][8]                 |

| P2        | $C[0][2] \rightarrow C[11][2]$ | C[0][9]→C[5][9]                  |

| Р3        | C[0][3]→C[11][3]               | $C[6][9] \rightarrow C[11][9]$   |

| P4        | C[0][4]→C[11][4]               | $C[0][10] \rightarrow C[5][10]$  |

| P5        | C[0][5]→C[11][5]               | $C[6][10] \rightarrow C[11][10]$ |

| P6        | C[0][6]→C[11][6]               | $C[0][11] \rightarrow C[5][11]$  |

| P7        | C[0][7]→C[11][7]               | C[6][11]→C[11][11]               |

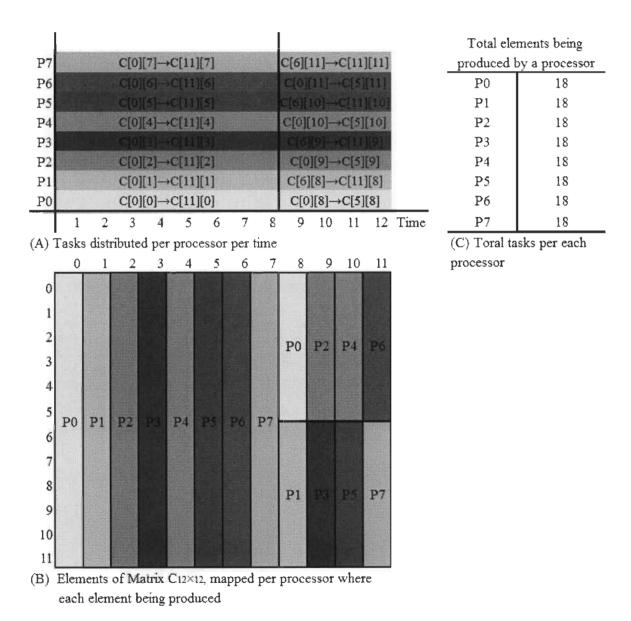

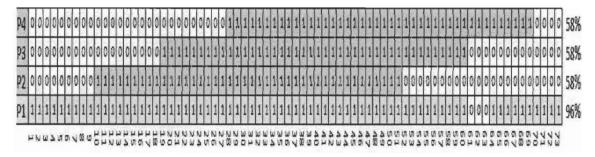

Each processor produce 18 elements of the output matrix C, which satisfies the load balance between the processors, also, each task – and so each processor – is independent from any other tasks, and so, there is no exchanged messages. Figure 3-12 (A) shows the time chart for the eight processors for this example  $A_{12x12} \times B_{12x12} = C_{12x12}$ , it is obvious that all processors working, and no processor is idle, and no processor finishes its tasks before the others, which implies the highest efficiency of using the processors and the