# UNIVERSITÉ DU QUÉBEC

# MÉMOIRE PRÉSENTÉ À L'UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

## COMME EXIGENCE PARTIELLE DE LA MAÎTRISE EN GÉNIE ÉLECTRIQUE

### PAR MOHAMMED BOUGATAYA

ÉTUDE DE LA DYNAMIQUE THERMIQUE DANS UN PROCESSEUR MASSIF À HAUT NIVEAU DE DÉBIT

**DECEMBRE 2002**

À mon père, à ma mère À ma sœur (Fatna) À mes frères(Sghir, Rachid et Radouane) À toute ma grande famille À tous mes amis et amies au Maroc, Algérie, Europe et au Canada À titre de reconnaissance, d'amour et d'affection

# Résumé

Au cours du développement et la conception des circuits intégrés (CI) l'aspect thermique est crucial pour leur bon fonctionnement. La contrainte thermique finale est la température du silicium, qui est désignée généralement sous le nom de la température de jonction, demeure un obstacle majeur devant les performances les plus recherchées des circuits intégrés soit : l'augmentation de la vitesse d'opération et la miniaturisation des composants. Dans les deux cas cela se traduit par une augmentation de la température des composants électroniques causée respectivement par l'accumulation d'un résidu thermique d'un cycle à l'autre et l'augmentation de la densité de puissance dissipée.

En effet, le contrôle de la température et son gradient à partir du premier pas de la conception du circuit intégré est essentiel. Cependant, le placement des composants ne doit pas provoquer de dégradation de performance due aux différences de température. Les composants doivent rester dans les limites des spécifications et sur la même ligne isotherme, de manière à respecter une symétrie axiale par rapport à la source de chaleur. De cette façon nous avons caractérisé la dynamique thermique dans le processeur WSI (Wafer Scale Integaration) pour développer une cartographie thermique représentant le circuit réel en opération.

De ce fait, notre projet de recherche consiste à étudier la dynamique thermique et thermomécanique en régime permanent et transitoire d'un processeur massif à haut niveau de débit dans l'environnement NISA qui utilise la méthode des éléments finis (FEM). Nos investigations thermiques ont servi à prédire le comportement thermique des

sources de chaleur au niveau du *layout* (dessin des masques sur silicium) et le *Data Bus* (Bus de donnée) placées dans la cavité du boîtier. Les mesures de température données par ces sources permettront la modélisation de l'ensemble du boîtier, afin d'établir une cartographie thermique la plus homogène qui va nous permettre à concevoir les systèmes de dégagement effectif de la chaleur au sein de circuit intégrée.

# Remerciements

Ce travail a été effectué au sein du laboratoire de DMCL (*Device Modelisation* and caracterisation laboratory) à l'UQO et au laboratoire des signaux et systèmes intégrés à UQTR en collaboration avec la compagnie Hyperchip.Inc

Je remercie tout d'abord Monsieur le professeur Ahmed LAKHSASI, directeur du Laboratoire DMCL lors de mon arrivée en projet et actuellement directeur de module de génie informatique à UQO, pour m'avoir accueilli au sein de son laboratoire et pour l'honneur qu'il me fait en acceptant l'encadrement de ce projet.

J'exprime toute ma gratitude pour son encadrement efficace, ses précieux conseils et la confiance qu'il m'a témoigné et par la même occasion je rends hommage à sa rigueur scientifique et technique.

Mes remerciements s'adressent ensuite à Monsieur le professeur **Daniel**MASSICOTTE, mon co-directeur de thèse, responsable de laboratoire de signal et de système intégré à UQTR pour ses précieux conseils.

Je remercie très sincèrement les professeurs Adam SKOREK et Marek

ZAREMBA d'avoir accepté d'être les examinateurs de ma thèse.

Je remercie vivement les professeurs **Yvon SAVARIA** de l'École Polytechnique de Montréal et **Claude THIBEAULT** de l'ÉTS pour leurs nombreux conseils, leurs suggestions et leurs critiques qui m'ont beaucoup aidé d'affronter tant de difficultés.

Je remercie la compagnie Hyperchip qui a financé ce travail de recherche dans le cadre du programme pour développer un routeur pour le réseau d'Internet .

J'adresse mes sincères remerciements à toutes les personnes ayant participé à ce programme avec lesquelles j'ai eu d'excellents rapports. Je remercie tout particulièrement Messieurs Karl FECTEAU et David CHAMBERLAIN pour l'aide directe qu'ils m'ont apporté.

À tous ceux et celles qui de près ou de loin m'ont permis de bien mener à terme ces recherches.

# Table des matières

| RÉSUMÉ                                                            | Ш    |

|-------------------------------------------------------------------|------|

| REMERCIEMENTS                                                     | V    |

| LISTE DES FIGURES                                                 | XI   |

| LISTE DES TABLEAUX                                                | XVI  |

| LISTE DES SYMBOLES                                                | XVII |

|                                                                   |      |

| Chapitre I_: Introduction générale                                | 1    |

|                                                                   |      |

| I.1 Problématique                                                 | 1    |

| I.1.1 Contrainte thermique                                        | 2    |

| I.1.2 Choc thermique                                              | 3    |

| I.1.3 Améliorer la prédiction du skew                             | 3    |

| I.2 Objectifs de la recherche                                     | 3    |

| I.3 Méthodologie de la recherche                                  | 4    |

| I.4 Structure du mémoire                                          | 6    |

|                                                                   |      |

| Chapitre II: Introduction à la gestion thermique en électronique: | -    |

| aspects de la mise en boîtier '' Packaging''                      | 7    |

| II.1 Introduction                                                 |      |

| II.2 Pourquoi la conception thermique                             | 9    |

| II.2.1 Effets de la température sur l'opération du circuit        | 9    |

| II.2.2 Effets de température sur la construction physique         | 10   |

| II.3 Analyse thermique                                            | 11   |

| II.3.1 Écoulement du Flux de chaleur                              | 12   |

| II.3.2 Conception thermique                                       | 17   |

| II.3.3 Sélection de la technique de refroidissement thermique     | 19   |

| II .3.4 Choix du radiateur.                                                  |                                                                 | 20                                                                                                         |

|------------------------------------------------------------------------------|-----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| II.4 Approche des éléments fi                                                | nis                                                             | 20                                                                                                         |

| .4.1 Modélisation par éléme                                                  | ents finis                                                      | 21                                                                                                         |

| —— II.5 Choix du packaging                                                   |                                                                 | 26                                                                                                         |

| II.5.1 Propriétés électriques                                                | des protubérances                                               | 28                                                                                                         |

| II.5.2 Performances électric                                                 | lues                                                            | 29                                                                                                         |

| ■ II.5.3 Performances mécan                                                  | iques                                                           | 31                                                                                                         |

| II.5.3.1 Connexions I/O en ré                                                | seau sur toute la surface de la puce                            | 31                                                                                                         |

| II.5.3.2 Densité d'interd                                                    | connexion et efficacité                                         | 32                                                                                                         |

| II.5.4 Aspect thermique                                                      |                                                                 | 33                                                                                                         |

| II.5.4.1 Résistance therm                                                    | nique d'une boule de soudure                                    | 33                                                                                                         |

| II.5.4.2 Résistance them                                                     | mique de l'interconnexion puce-boîtier                          | 34                                                                                                         |

|                                                                              |                                                                 | ~                                                                                                          |

| (II.5.5 Contrainte thermique                                                 |                                                                 | 36                                                                                                         |

| -                                                                            | [                                                               |                                                                                                            |

| II.6 Conclusion du chapitre II                                               |                                                                 | 39                                                                                                         |

| II.6 Conclusion du chapitre II  Chapitre III: Conditions                     | [                                                               | 39<br>40                                                                                                   |

| II.6 Conclusion du chapitre II  Chapitre III: Conditions  III.1 Introduction | s aux limites thermiques                                        | 39<br>40                                                                                                   |

| II.6 Conclusion du chapitre II  Chapitre III: Conditions  III.1 Introduction | s aux limites thermiques                                        | <ul><li>39</li><li>40</li><li>40</li><li>42</li></ul>                                                      |

| II.6 Conclusion du chapitre II  Chapitre III: Conditions  III.1 Introduction | a chaleur                                                       | <ul><li>39</li><li>40</li><li>40</li><li>42</li></ul>                                                      |

| II.6 Conclusion du chapitre II  Chapitre III: Conditions  III.1 Introduction | a chaleur                                                       | <ul><li>39</li><li>40</li><li>40</li><li>42</li><li>42</li></ul>                                           |

| II.6 Conclusion du chapitre II  Chapitre III: Conditions  III.1 Introduction | a chaleur                                                       | <ul><li>39</li><li>40</li><li>40</li><li>42</li><li>42</li><li>44</li></ul>                                |

| II.6 Conclusion du chapitre II  Chapitre III: Conditions  III.1 Introduction | a chaleur e.                                                    | <ul><li>39</li><li>40</li><li>42</li><li>42</li><li>44</li><li>46</li></ul>                                |

| II.6 Conclusion du chapitre II  Chapitre III: Conditions  III.1 Introduction | a chaleur e. ermique.                                           | <ul><li>39</li><li>40</li><li>42</li><li>42</li><li>44</li><li>46</li><li>48</li></ul>                     |

| II.6 Conclusion du chapitre II  Chapitre III: Conditions  III.1 Introduction | a chaleur e.  ermique.  fluide thermique.  cansfert de chaleur. | <ul> <li>40</li> <li>40</li> <li>42</li> <li>42</li> <li>44</li> <li>46</li> <li>48</li> <li>52</li> </ul> |

| Chapitre IV: Étude de La dynamique thermique                               | 61 |

|----------------------------------------------------------------------------|----|

|                                                                            |    |

| IV.1 Introduction.                                                         | 61 |

| IV.2 Optimisation de l'emplacement des sources de chaleur                  | 64 |

| IV.2.1 Condition de la simulation.                                         | 64 |

| IV.2.2 Résultats de la simulation.                                         | 65 |

| V.3 Optimisation de l'emplacement de nombre de Data Bus                    | 69 |

| IV.3.1 Condition de l'investigation thermique                              | 71 |

| IV.3.2 Résultats de l'investigation thermique                              | 72 |

| IV.4 Optimisation de l'emplacement des sources de chaleur sur une Data Bus |    |

| dans un layout                                                             | 73 |

| IV.4.1 Conditions de la simulation                                         | 75 |

| IV.4.2 Résultats des simulations                                           | 76 |

| IV.5 Emplacement final des sources de chaleur                              | 79 |

| IV.5 .1 Influences d'autre sources de chaleur sur l'emplacement finale des |    |

| puces                                                                      | 80 |

| IV.5.1.1 Conditions de la simulation thermique                             | 81 |

| IV.5.1.2 Résultas des simulations thermiques                               | 81 |

| IV.6 Établissement d'une cartographie thermique pour tout le processeur    | 82 |

| IV.6.1 Sélection de radiateur                                              | 84 |

| IV.6.2 Types de refroidissement                                            | 85 |

| IV.6.3 Conditions de la simulation pour le processeur WSI                  | 89 |

| IV.6.4 Résultats de simulation pour le processeur WSI                      | 91 |

| IV.7 Conclusion du chapitre IV                                             | 93 |

| Chapitre V: Contrainte thermomécanique                                 | 95  |

|------------------------------------------------------------------------|-----|

| V.1 Introduction                                                       | 95  |

| V.2 Distorsions dans le processeur WSI                                 | 97  |

| V.3 Étude de la thermomécanique                                        | 99  |

| V.4 Conditions aux limites statiques                                   | 99  |

| V.5 Analyse de la déformation du processeur WSI                        | 101 |

| V.6 Analyse de la déformation au niveau des boules de soudure          | 101 |

| V.7 Contrainte équivalent "Von Mises"                                  | 104 |

| V.8 Conclusion du chapitre V.                                          | 105 |

| Chapitre VI : CONCLUSION GÉNÉRALE                                      | 106 |

| BIBLIOGRAPHIE                                                          | 109 |

| ANNEXE I : NOUVELLE APPROCHE POUR LA DÉTERMINATION DE $h_{eq}^{Fcons}$ | 111 |

| ANNEXE II : PROGRAMME FICHIER NISA PARTIE THERMIQUE                    | 117 |

| ANNEXE III : PROGRAMME FICHIER NISA PARTIE STATIQUE                    | 121 |

| ANNEXE IV : RÉSULTAT DE LA DÉTERMINATION DU RADIATEUR                  | 125 |

36

# Liste des figures

Chapitre I

Figure 2.13

Figure 2.14 Figure 2.15

Figure 2.16

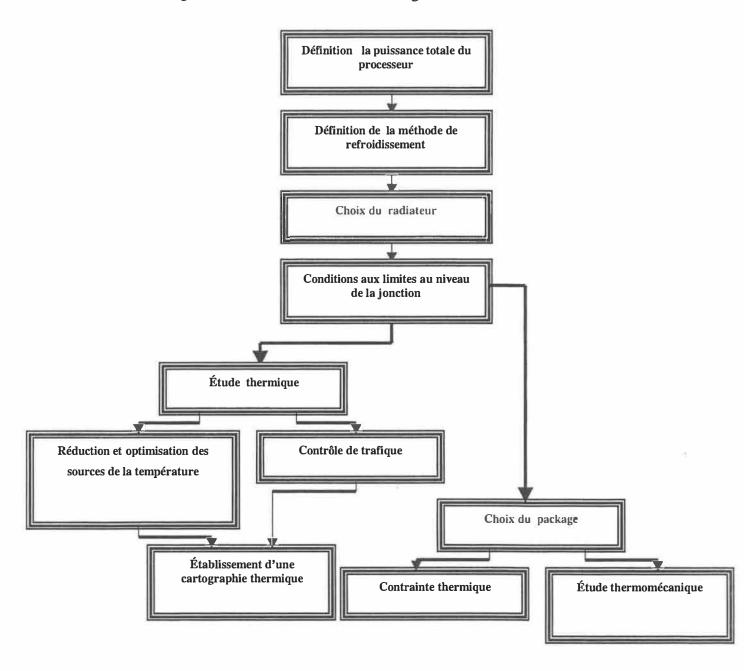

| Figure 1.1  | Organigramme de la Méthodologie de recherche               | 5  |

|-------------|------------------------------------------------------------|----|

|             |                                                            |    |

| Chapitre II |                                                            |    |

| Figure 2.1  | Conditions aux limites thermiques                          | 12 |

| Figure 2.2  | Organigramme pour la conception thermique                  | 18 |

| Figure 2.3  | Modèle d'éléments finis simplifiés en 2D                   | 22 |

| Figure 2.4  | Organigramme pour exécuter une analyse des éléments finis. | 23 |

| Figure 2.5  | Exemple de résultat d'une analyse thermique par les        |    |

| Figure 2.6  | éléments finis.                                            | 25 |

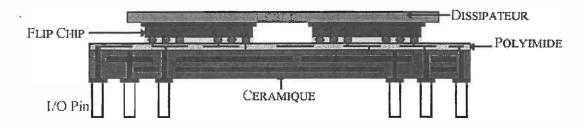

| Figure 2.7  | Flip Chip Packaging (FCP)                                  | 26 |

| Figure 2.8  | Exemple: Flip Chip TBGA                                    | 27 |

| Figure 2.9  | Exemple: Flip Chip sur MCM                                 | 27 |

| Figure 2.10 | Technologie C4: Boules de soudure                          | 28 |

| Figure 2.11 | Montages Flip Chip utilisant des substances adhésives      | 28 |

| Figure 2.12 | Disposition des boules de soudure sur la puce (Grid Array) | 31 |

Modélisation thermique d'une configuration Flip Chip......

Exemple de modélisation thermique d'une puce montée en Flip Chip......

Interconnexion d'une puce sur son support: Flip Chip......... 38

# Chapitre III

| Figure 3.1  | Élément de volume ( $\Delta V$ )                              | 42 |

|-------------|---------------------------------------------------------------|----|

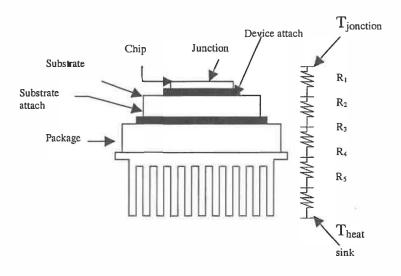

| Figure 3.2  | Model thermique statique 1-D                                  | 46 |

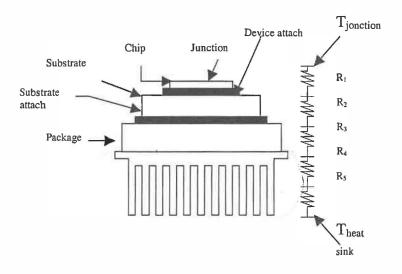

| Figure 3.3  | Analogies électriques entre la jonction et le radiateur       | 47 |

| Figure 3.4  | Conditions aux limites thermiques au niveau de la jonction    | 51 |

| Figure 3.5  | Schémas d'un Radiateur                                        | 52 |

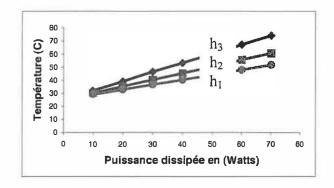

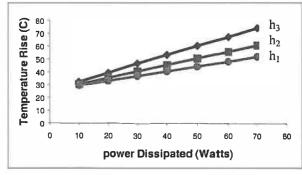

| Figure 3.6  | Évolution de la température de radiateur AAVID_61540 en       |    |

|             | fonction de la puissance dissipée pour une source de          |    |

|             | 16mm×20mm                                                     | 53 |

| Figure 3.7  | Déroulement de l'analyse d'un problème de transfert de        |    |

|             | chaleur                                                       | 56 |

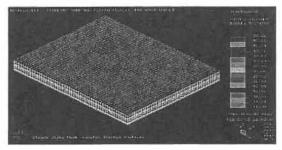

| Figure 3.8  | Modèle en éléments finis et distribution de la température    |    |

|             | pour la source 16mm×20mm                                      | 57 |

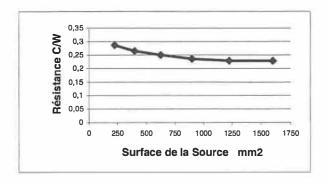

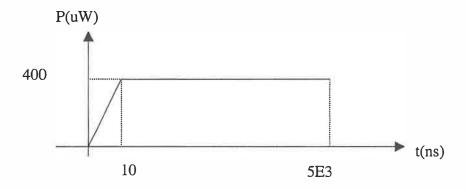

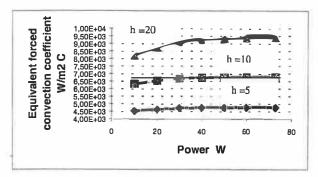

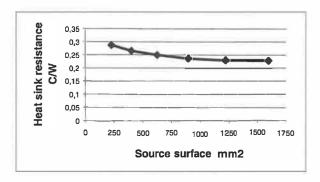

| Figure 3.9  | Évolution du coefficient de convection forcé équivalent       |    |

|             | avec la puissance dissipée pour différents h                  | 57 |

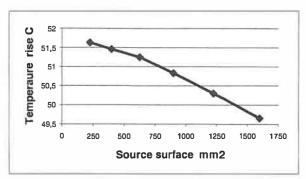

| Figure 3.10 | Évolution de la température avec la surface de la source pour |    |

|             | h =20W/m <sup>2</sup> * °C                                    | 57 |

| Figure 3.11 | Évolution de la résistance équivalente du radiateur avec      |    |

|             | l'évolution de la surface pour $h = 20W/m^2 * {}^{\circ}C$    | 57 |

| Figure 3.12 | Évolution du coefficient de convection forcé équivalent avec  |    |

|             | la surface de la source pour $h = 20W/m^{2*} {}^{\circ}C$     | 57 |

# Chapitre IV

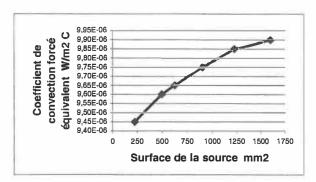

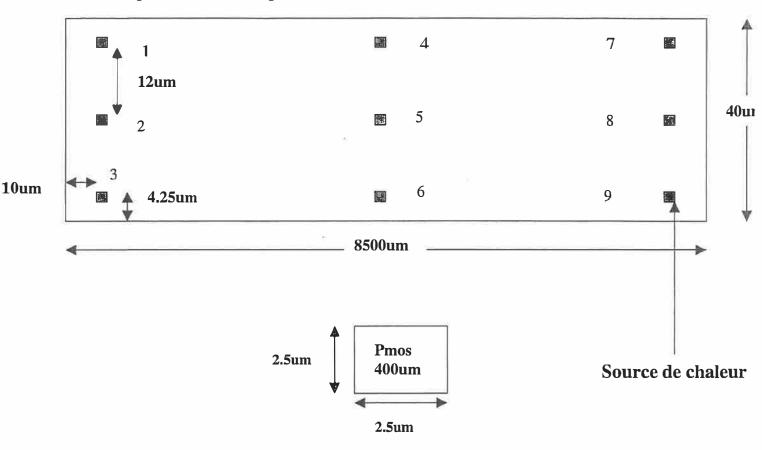

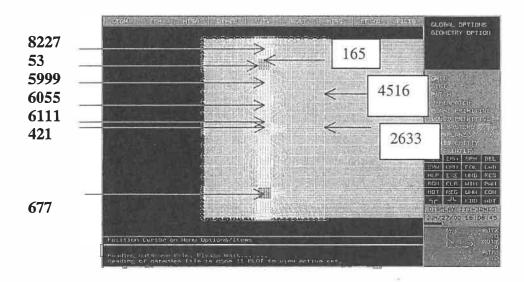

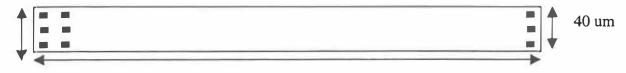

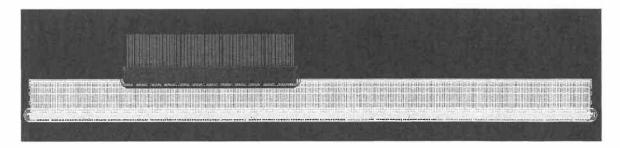

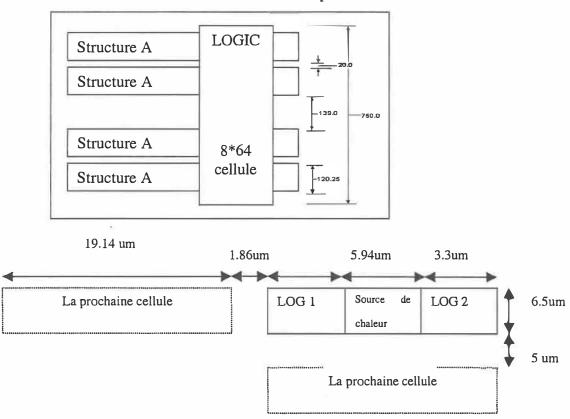

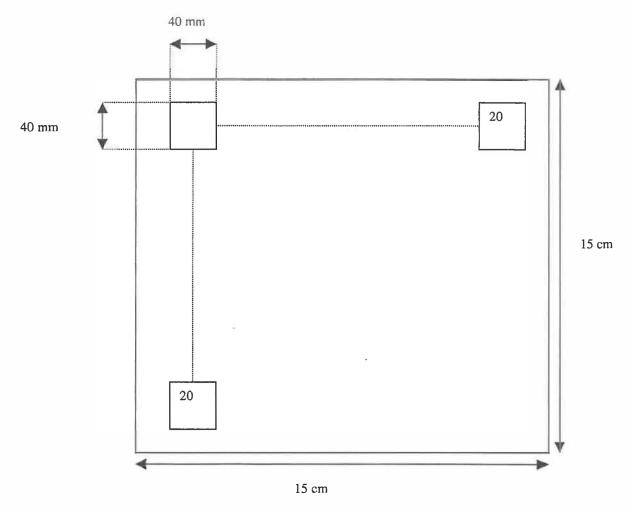

| Figure 4.1  | Dimensions des sources de chaleur dans un bus de donnée        | 64 |

|-------------|----------------------------------------------------------------|----|

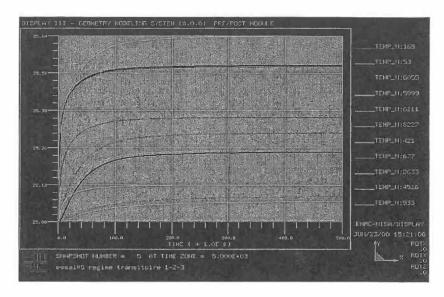

| Figure 4.2  | Fonction TIMEAMP pour le régime transitoire                    | 65 |

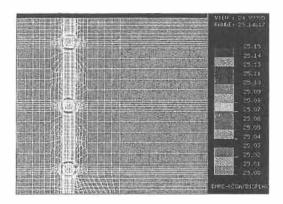

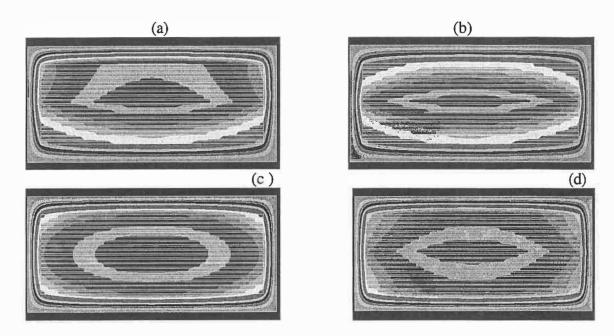

| Figure 4.3  | Résultats obtenus pour les différents temps de simulation      | 66 |

| Figure 4.4  | Emplacements des points a étudier en régime transitoire sur    |    |

|             | la surface de Bus de donnée                                    | 67 |

| Figure 4.5  | Évolution de la température sur la surface du bus de donnée    |    |

|             | à des différents nœuds                                         | 68 |

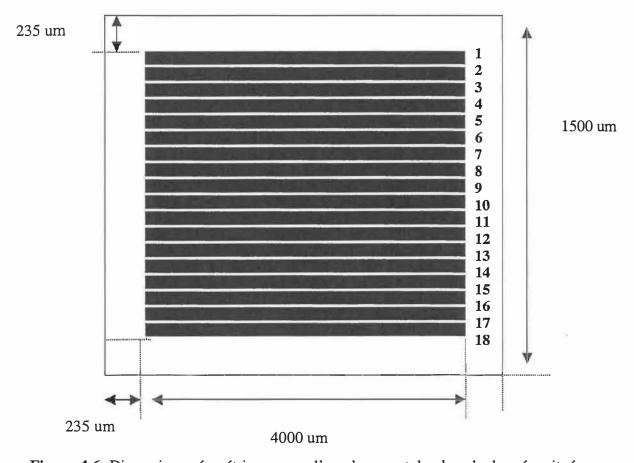

| Figure 4.6  | Dimensions géométriques pour l'emplacement des bus de          | Ü. |

|             | données situées sur le layout du processeur WSI                | 69 |

| Figure 4.7  | Dimensions géométriques pour un bus de donnée                  | 70 |

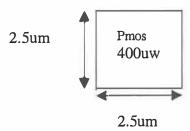

| Figure 4.8  | Dimensions géométriques pour une source de chaleur             | 70 |

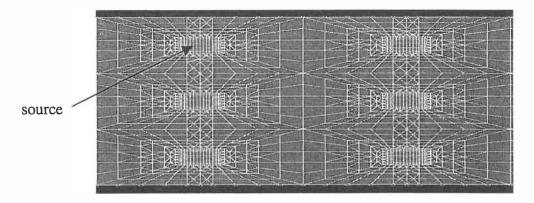

| Figure 4.9  | Maillage des éléments de la chaleur pour les sources et les    |    |

|             | Bus de donnée en 2D                                            | 70 |

| Figure 4.10 | Conditions aux limites appliquées sur layout                   | 70 |

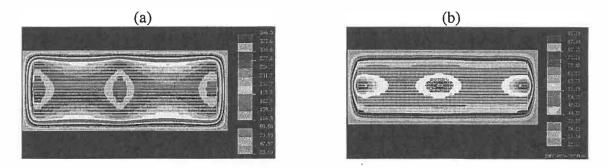

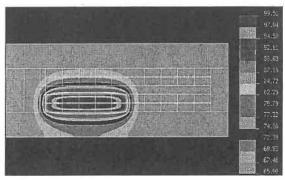

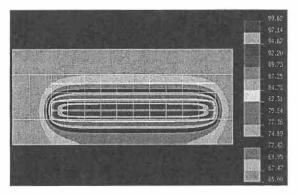

| Figure 4.11 | Lignes isothermes thermiques pour quelques sources de          |    |

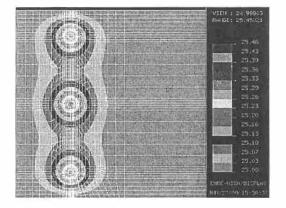

|             | chaleur allumées pour différents Bus de données                | 72 |

| Figure 4.12 | Lignes isothermes thermiques pour 200 sources du chaleur       |    |

|             | allumée pour différents Bus de donnée                          | 73 |

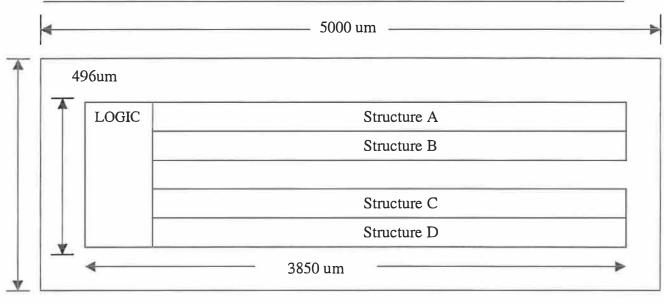

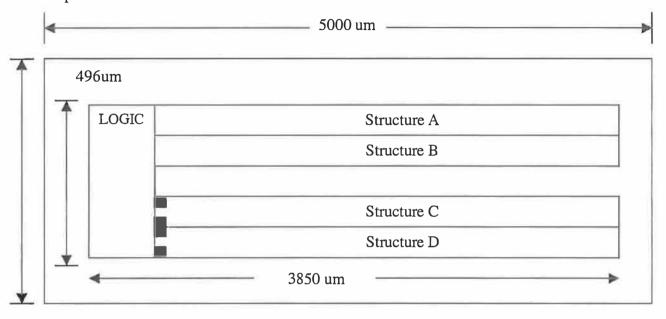

| Figure 4.13 | Dimensions du layout du processeur WSI                         | 74 |

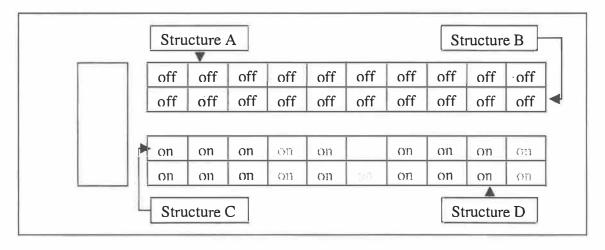

| Figure 4.14 | Schématisation de l'emplacement des sources de chaleur         |    |

| 79          | dans la structure C et D pour la simulation N1                 | 75 |

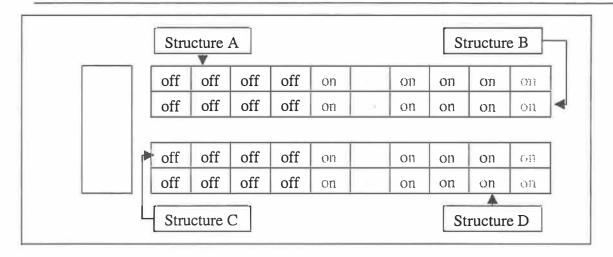

| Figure 4.15 | Schématisation de l'emplacement des sources de chaleur à la    |    |

|             | droite des structures A, B, C et D pour la simulation N2       | 75 |

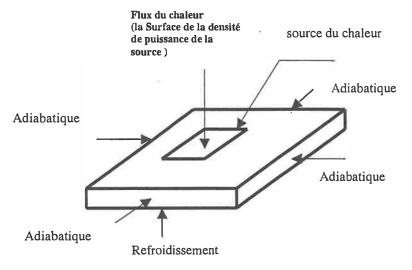

| Figure 4.16 | Conditions aux limites représentées par la densité de          |    |

|             | puissance modélisée par un flux de chaleur et la spécification |    |

|             | de la température en bas de la structure                       | 74 |

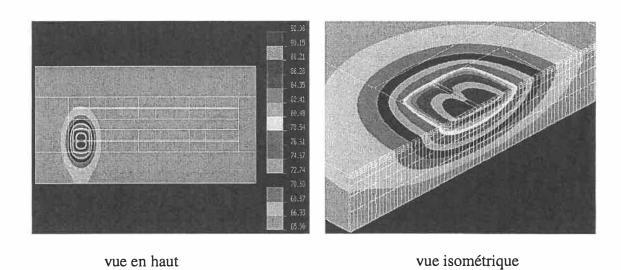

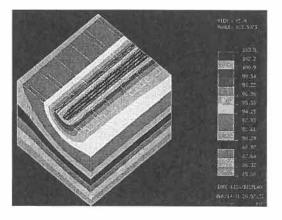

| Figure 4.17 | Lignes isothermes thermiques pour une puissance appliquée      |    |

|             | pour 1/10 de la structure C et D pour une température nodale   |    |

|             | spécifiée à 65 °C                                              | 76 |

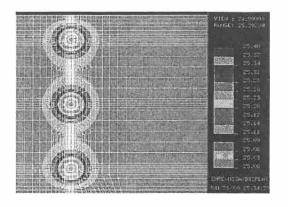

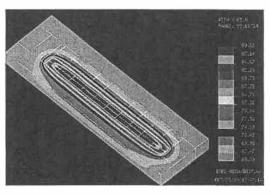

| Figure 4.18 | Lignes isothermes thermiques pour une puissance appliquée    |            |

|-------------|--------------------------------------------------------------|------------|

|             | pour 5/10 de la structure C et D pour une température        |            |

|             | nodale spécifiée à 65 °C(vue en haut)                        | 77         |

| Figure 4.19 | Lignes isothermes thermiques pour une puissance appliquée    |            |

|             | pour 3/10 de la structure C et D pour une température nodale |            |

|             | spécifiée à 65 °C(vue en haut)                               | 77         |

| Figure 4.20 | Lignes isothermes thermiques pour une puissance appliquée    |            |

|             | pour toutes les structures C et D pour une température       |            |

|             | nodale spécifiée à 65 °C(vue en haut)                        | 77         |

| Figure 4.21 | Lignes isothermes thermiques pour une puissance appliquée    |            |

|             | pour toutes les structure C et D pour une température nodale |            |

|             | spécifiée à 65 °C (vue isométrique)                          | 77         |

| Figure 4.22 | Lignes isothermes thermiques pour une puissance appliquée    |            |

|             | à la droite des structures A, B, C et D pour une température |            |

|             | nodale spécifiée à 65 °C                                     | 77         |

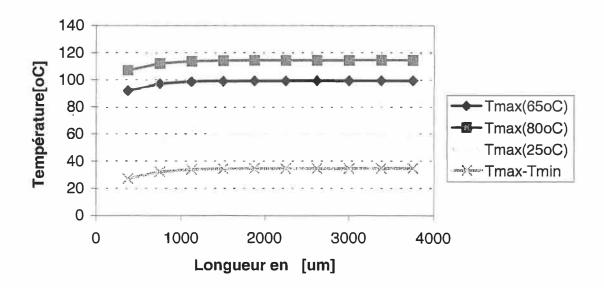

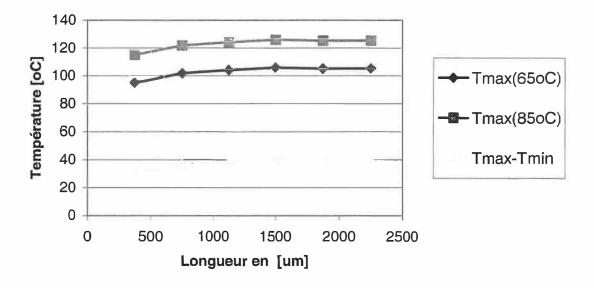

| Figure 4.23 | Évolution de la température maximale pour différents         |            |

|             | placements des sources de chaleur (simulation No 1)          | 78         |

| Figure 4.24 | Évolution de la température maximale pour différents         |            |

|             | placements des sources de chaleur (simulation No 2)          | 78         |

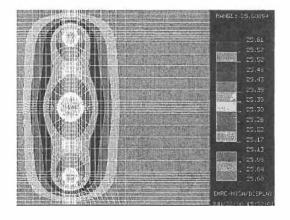

| Figure 5.26 | Dimensions et l'emplacement final des sources de chaleur et  |            |

|             | les Bus de données dans un layout                            | <b>7</b> 9 |

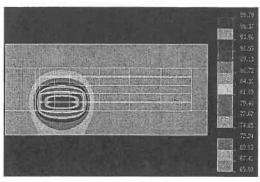

| Figure 5.27 | Lignes isothermes thermiques pour une puissance appliquée    |            |

|             | à la gauche des structures C et D                            | 79         |

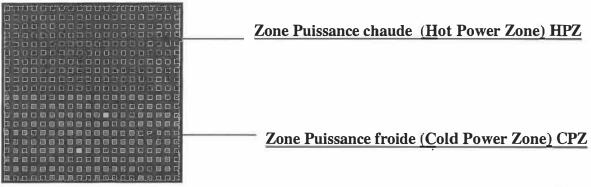

| Figure 5.28 | Dimension des cellules des sources de chaleurs               | 80         |

| Figure 5.29 | Lignes isothermes thermiques pour une puissance appliquée    |            |

|             | sur la LOGIC.                                                | 81         |

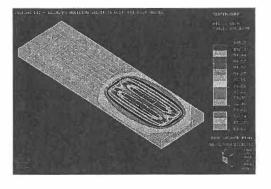

| Figure 5.30 | Emplacement des sources de chaleur pour tout le processeur   |            |

|             | WSI                                                          | 83         |

| Figure 5.31 | Dimension géométrique utilisée pour tout le processeur       | 83         |

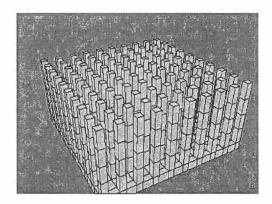

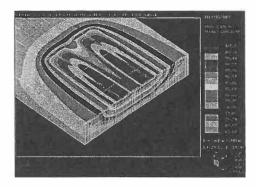

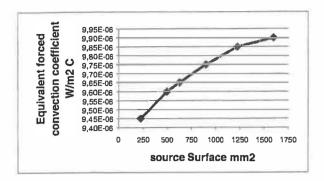

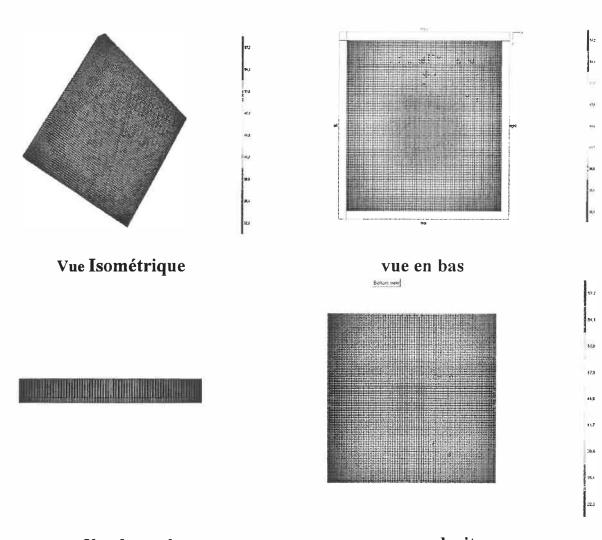

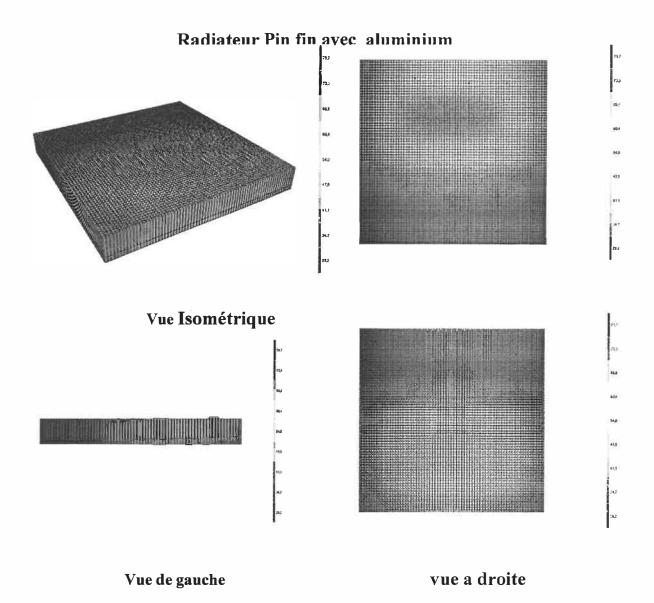

| Figure 5.32 | 3-D Simulation en 3D pour la détermination d'un radiateur    | 87         |

| Figure 5.33 | Analogies électriques entre la jonction et le radiateur                             | 89  |

|-------------|-------------------------------------------------------------------------------------|-----|

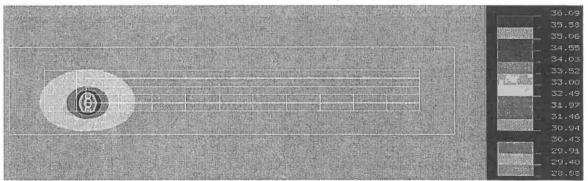

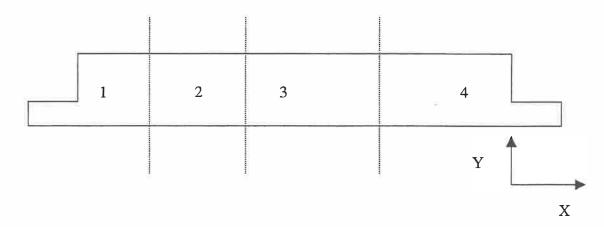

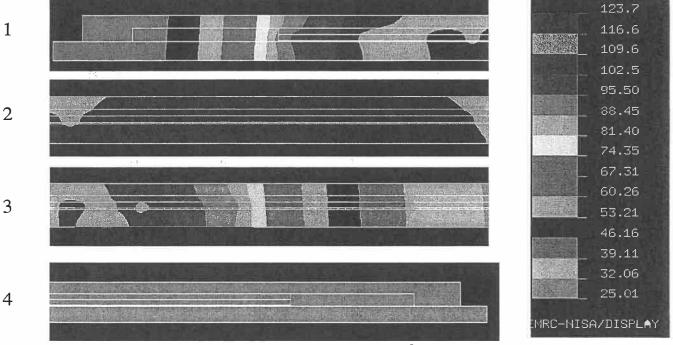

| Figure 5.34 | Coupes XY pour la simulation en 2-D                                                 | 90  |

| Figure 5.35 | 3-D lignes isothermes thermiques pour tout le processeur                            | 91  |

| Figure 5.36 | $2\text{-}\mathrm{D}$ lignes isothermes thermiques pour tout le processeur $\ldots$ | 91  |

|             |                                                                                     |     |

| Chapitre V  |                                                                                     |     |

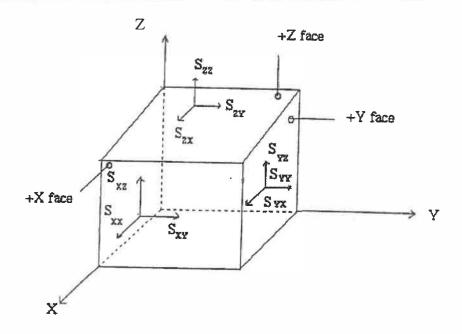

| Figure 5.1  | Signes et conventions pour les composants des contraintes et                        |     |

|             | des distorsions                                                                     | 98  |

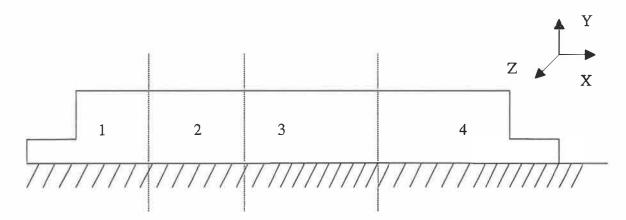

| Figure 5.2  | Conditions aux limites statiques pour le processeur WSI et                          |     |

|             | les Coupes visionné pour la simulation en 2-D                                       | 100 |

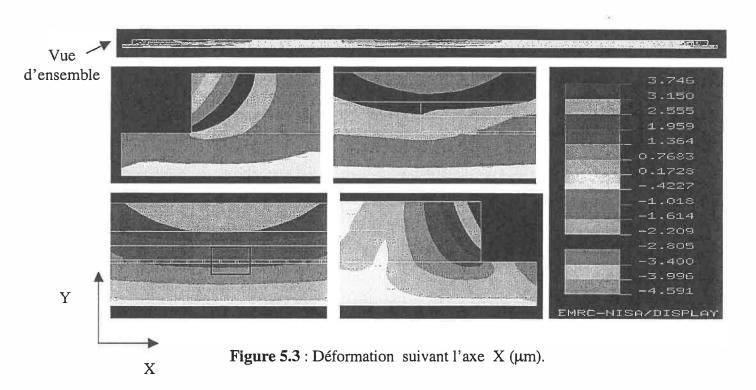

| Figure 5.3  | Déformation suivant l'axe X (µm)                                                    | 101 |

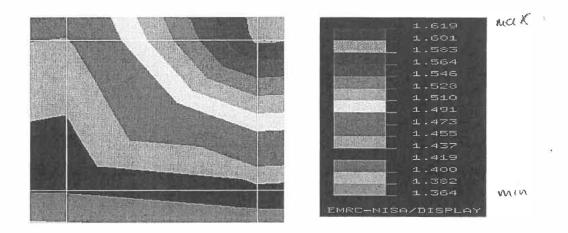

| Figure 5.4  | Déformation maximale au niveau d'une boule de soudure                               |     |

|             | suivant l'axe X.                                                                    | 102 |

| Figure 5.5  | Déformation maximale entre deux boules de soudure                                   |     |

|             | suivant l'axe X                                                                     | 102 |

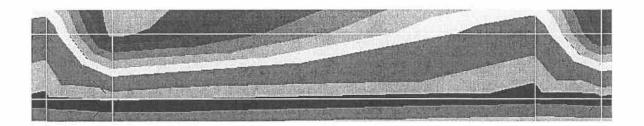

| Figure 5.6  | Déformation suivant l'axe Y (µm)                                                    | 103 |

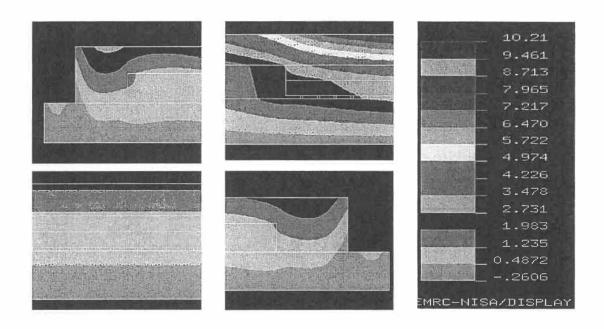

| Figure 5.7  | Déformation maximale au niveau d'une boule de soudure                               |     |

|             | suivant l'axe                                                                       | 103 |

| Figure 5.8  | Contrainte équivalente "Von Mises" (MPa)                                            | 104 |

# Liste des tableaux

| Tableau 2.1 | Ordre de grandeurs d'onde associées à différentes fréquences           | 29 |

|-------------|------------------------------------------------------------------------|----|

| Tableau 2.2 | Ordre de grandeurs sur les performances électriques des                |    |

|             | technologies C4.                                                       | 30 |

| Tableau 3.2 | Comparaison entre les différents paramètres avec l'analyse             |    |

|             | fluide(Qfin) et le transfert de la chaleur (NISA)                      | 57 |

| Tableau 4.1 | Propriétés thermiques des matériaux                                    | 71 |

| Tableau 4.2 | Efficacité de transfert de chaleur pour diverses configurations de     |    |

|             | radiateurs                                                             | 85 |

| Tableau 4.3 | Coefficients de transfert de chaleur typiques pour différents          |    |

|             | types de refroidissement                                               | 86 |

| Tableau 4.4 | Variation de température et résistance thermique en fonction de        |    |

|             | la réduction du coefficient de convection forcée (h) pour $R_{jc}$ =0. |    |

|             | 01 Co/W                                                                | 88 |

# Liste des symboles

```

C

Capacité d'entrée [F]

V

Signal d'oscillation de la tension crête à crête [V]

f

La fréquence [Hz]

Masse volumique |kg/m^3|

ρ

Capacité thermique [J/K]

Cth

Cp

Chaleur massique à pression constante [J/kg.K]

Ε

Module de Young

Coefficient d'échange convectif |W/m^2.K|

h

Courant de la charge [A]

Ιp

k

Conductivité thermique [W/m.K]

Conductivité thermique à 300 K [W/m.K]

ko

Ki

Conductivité thermique de l'isolant [W/m.K]

P

Puissance totale dissipée [W]

Densité volumique des sources internes |W/m^3|

q

Surface d'échange \lfloor m^2 \rfloor

S

T

Température [K]

t

Temps [s]

Ta

Température ambiante [K]

Vo

Tension de seuil [V]

Tension d'alimentation continue [V]

Vcc

Impédance thermique [K/J]

Zth

Conductance thermique W/m^2.K

g

Flux de chaleur [W]

φ

Perte

\alpha

Densité surfacique de flux de chaleur |W/m^2|

φ

Constante de Stéfan-Boltzman W/m^2.K^4

σ

Emmissivité

3

```

Rendement η Résistance thermique entre le boîtier et le radiateur  $|{}^{\circ}C/W|$ Rcs Résistance thermique entre la jonction et boîtier  $|{}^{o}C/W|$ Rjc Résistance thermique entre le radiateur et l'air  $|{}^{\circ}C/W|$ Rsa Impédance de sortie caractéristique  $\mathbf{Z}_0$ délais de propagation [S]  $t_p$ Nombre de I/O  $n_w$ Pas d'interconnexion  $p_L$ W et L Dimension de caractéristique de circuit intégrée [m]  $\delta_w$ Distance inutilisée sur W [m]. Distance inutilisée sur L [m].  $\delta_{\rm L}$ Le nombre de connexions N D La densité d'interconnexion Longueur totale d'interconnexion [m]  $L_{tot}$ Surface totale de puce[m<sup>2</sup>] A Khall Conductivité thermique de la boule de soudure [W/ m.K]. Conductivité thermique d'un pad [W/ m.K]  $K_{pad}$ Conductivité thermique d'un paste [W/m.K] Knaste Conductivité thermique de l'encapsulant [W/m.K] Kencan Coefficient de transfert thermique du fluide interstitiel [W/m².K]  $H_{\text{fluide}}$ Coefficient de transfert thermique du fluide interstitiel [W/m<sup>2</sup>.K] H<sub>fluide</sub> Différence de CTE entre la puce et son support. Δα Contrainte sur la soudure τ Diamètre de la protubérance [m] d Variation de températures à laquelle est soumis le système  $\Delta T$ Résistance thermique de boule  $|{}^{o}C/W|$  $R_{ball}$ Résistance thermique de pad | OC/W |  $R_{pad}$ R<sub>bump</sub> Résistance thermique bump  $[{}^{o}C/W]$ R<sub>soudure</sub> Résistance thermique de soudure  $|{}^{o}C/W|$

# Chapitre I Introduction générale

### I.1. Problématique

Les premières années de ce siècle, sans aucun doute, seront consacrées aux télécommunications, que ce soit pour la téléphonie, l'internet, l'informatique ou les systèmes experts. Les besoins mondiaux en composantes microélectroniques ne cesseront de croître. Les circuits intégrés (CI) sont essentiels aux développements futurs des télécommunications, ils devront être plus complexes, plus rapides et posséder une grande capacité de mémoire[1].

Au cours du développement et la conception des circuits intégrés l'aspect thermique est crucial pour leur bon fonctionnement. Le problème du surchauffe de la jonction demeure un obstacle majeur devant les performances les plus recherchées des systèmes électroniques soit : L'augmentation de la vitesse d'opération et la miniaturisation des composants. Dans les deux cas cela se traduit par une augmentation de la température des composants électroniques causée respectivement par l'accumulation d'un résidu thermique d'un cycle à l'autre et l'augmentation de la densité de puissance dissipée.

La conception d'un processeur fiable et performant nécessite le recours à une étude thermique aux particularités géométriques et structurelles au niveau de la jonction.

En effet l'analyse de transfert de chaleur dans les processeurs repose sur les lois fondamentales de transfert de chaleur. Ces particularités résident essentiellement dans la géométrie et la structure des dispositifs, et dans la répartition spatiale des sources de chaleur. Ainsi, lors de la conception des processeurs, le modèle thermique est considéré essentiel pendant la simulation de la température de la jonction[1].

À mesure que la vitesse de processeur croît et les augmentations des périphériques d'intégration, la puissance de puce augmente. Investigation thermique devient une partie de plus en plus importante de la conception de système qui assure leur bon fonctionnement. La contrainte thermique finale est la température de silicium, qui désignée généralement sous le nom de la température de jonction. Cependant, elle demeure un obstacle majeur devant les performances les plus recherchées des circuits intégrés à très grande échelle d'intégration VLSI (Very Large Scale Integration)

Avant de commencer l'étude sur les aspects thermiques dans un processeur, nous consacrons cette partie à la description sur les problèmes liés à la température, et leur influence sur le circuit intégré. Nous y présentons trois problèmes majeurs, le premier et le deuxième tiennent compte de la structure physique du matériau et le troisième tient compte du fonctionnement du composant.

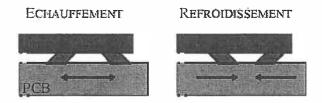

### I.1.1. Contrainte thermique

Dans certaines conditions d'utilisation le CI peut être soumis à des variations plus ou moins brusques de température, ces variations entraînent des variations dimensionnelles du matériau. Par conséquent, lorsque le matériau n'est pas libre de se dilater ou de se contracter, il se trouve soumis à des contraintes thermiques (*Thermal Stress*). Ces contraintes sont dues aux gradients de déformation qui se développent dans sa structure, dont tous les éléments sont incapables de se déformer librement [2].

### I.1.2. Choc thermique

Lorsque le gradient de température n'est pas très élevé, et que sa valeur est stable, les contraintes thermiques peuvent être atténuées par la déformation des éléments du CI [3]. Par contre, lorsque ce gradient de température est transitoire, c'est à dire lorsqu'il varie plus ou moins dans le temps, on a ce qu'on appelle un choc thermique.

### I.1.3. Améliorer la prédiction du Skew

Le *skew* correspond au déphasage maximal entre les arrivées de l'horloge sur les bascules, donc lorsque le gradient spatial de la température est très élevé ou la température est plus élevée, ce déphasage peut être perturbé, automatiquement il provoque une mauvaise transmission des donnés [4].

### I.2. Objectifs de la recherche

L'objectif général de cette recherche consiste à étudier la dynamique thermique en régime permanent et transitoire pour établire les contraintes thermiques et mécaniques

dans un processeur massif à haut niveau de débit (Prototype WSI de Hyperchip.inc).

L'objectif général peut se décomposer en sous objectifs:

- Définir la méthode de refroidissement et choisir le radiateur nécessaire,

- Établissement des conditions aux limites spécifiques au processeur,

- Proposer une cartographie représentant le positionnement des sources de chaleur pour respecter les contraintes imposées par le procédé de fabrication,

- Étude pour trouver l'emplacement idéal des sources de chaleur qui minimise la température et les contraintes thermique dans toute la structure du processeur,

- Étude de la dynamique thermique en régime transitoire et permanent,

- Établire une cartographie thermique du processeur,

- Faire une étude thermomécanique au niveau du package,

- Discussion des résultats obtenus et leurs applications.

### I.3. Méthodologie de la recherche

La méthodologie du travail est basée sur le contrôle de la température et son gradient à partir du premier pas de la conception du processeur WSI.

Les principales étapes de cette méthodologie sont

- Optimisation de l'emplacement des sources de chaleur sur layout.

- Établire une cartographie thermique du processeur

- Étudier la dynamique thermique en régime transitoire

- Déterminer la capacité de dissipation de chaleur du prototype

Caractérisation de la dynamique thermique dans le démonstrateur WSI pour le développement d'une cartographie thermique représentant le circuit réel en opération.

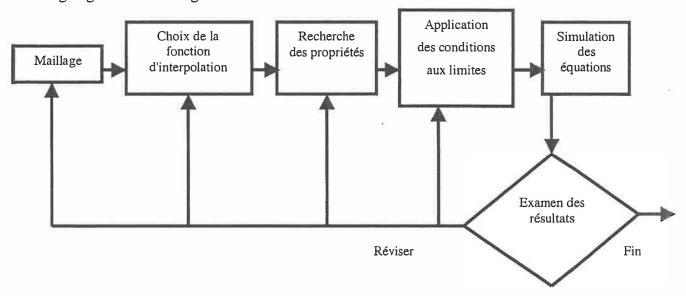

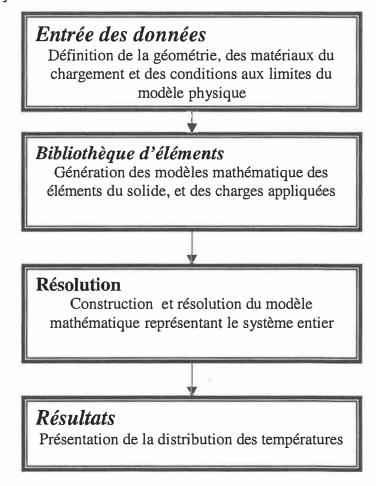

Cette méthodologie de recherche est illustrée à la figure I.1

Figure I-1: Organigramme de la méthodologie de recherche

### I.4. Structure du mémoire.

Ce mémoire est composé de six chapitres : le premier chapitre présente la problématique, les objectifs de recherche et la méthodologie utilisée pour la résoudre.

Le deuxième chapitre présente une introduction à la gestion thermique en électronique de *packaging* qui fournit une description des approches diverses aux questions de la gestion thermique dans les boîtiers électroniques. L'accent sera mis sur les principes de bases et les outils disponibles pour résoudre la majorité des problèmes thermique et mécanique.

Le troisième chapitre est consacré à une nouvelle approche pour la détermination de coefficient de convection équivalent au niveau de la jonction dans le processeur WSI.

Le quatrième et le cinquième chapitre seront consacrés à la modélisation du comportement thermique, thermomécanique et à l'étude détaillée de la dynamique thermique en régime permanent et transitoire afin d'établir une cartographie thermique pour tout le processeur.

Enfin, le sixième chapitre sera consacré à la conclusion générale de cette recherche.

# Chapitre II Introduction à la gestion thermique en électronique : aspects de la mise en boîtier'' Packaging''

### **II.1 Introduction**

La chaleur est une conséquence inévitable de chaque dispositif électronique, elle doit être réduite au minimum. La problématique thermique est généralement mentionnée comme la gestion thermique, elle n'est pas bien comprise par la plupart des ingénieurs, à part le praticien régulier. Ce chapitre, fournit une description des approches diverses aux questions de la gestion thermique dans les boîtiers électroniques. Il est destiné non seulement pour des experts de la gestion thermique, mais aussi pour ceux dans leurs domaines liés à la conception des circuits intégrés qui ont besoin d'un modèle thermique pour l'optimisation de leurs conceptions au niveau silicium. L'accent sera mis sur les principes de base et les outils disponibles pour résoudre la majorité des problèmes thermiques.

La tendance actuelle dans les boîtiers des systèmes électroniques et des soussystèmes réduit les performances thermiques lors d'une augmentation de la densité et de la taille. On peut voir l'évidence de cette tendance dans les niveaux plus hauts d'intégration VLSI dans des semi-conducteurs et l'utilisation accrue d'hybrides et des modules poly cristallins [5]. Le placement de plus de fonctions dans un boîtier électronique plus petit a abouti à la densité de chaleur plus haute, qui met a gestion thermique a une haute priorité dans le processus de conception des circuits intégrés afin de maintenir la performance de système et la fiabilité. L'augmentation de taux d'horloge augmente la puissance dissipée dans les semi-conducteurs et par conséquent, la commutation augmente à un taux linéaire proportionnel à la fréquence :

$$P = CV^2f/2$$

C = Capacité d'entrée en Farads

V= Signal d'oscillation de la tension crête à crête en Volts

f = Commutation de fréquence en Hertz

Si les valeurs de la capacité d'entrée et l'oscillation de tension étaient restées les mêmes tandis que la fréquence d'horloge a augmenté, la quantité de la puissance dissipée aurait grandi dans un taux exponentiel et serait ingérable. Heureusement, le concepteur thermique peut aider à réduire la capacité d'entrée pour chaque nouvelle génération de semi-conducteurs. De plus, les oscillations de tension, qui sont directement liées aux tensions d'alimentation de la logique, ont subi une réduction drastique de 5.0 volts à un volt [5].

### II.2 Pourquoi la conception thermique

### II.2.1 Effets de la température sur l'opération du circuit

L'augmentation de la température d'un dispositif actif change typiquement ses paramètres électriques comme le gain, la fuite et la compensation. Ces variations des paramètres avec la température sont bien documentées et incorporées dans la plupart des

simulateurs de circuit. La plupart des concepteurs de circuit sont conscients que le courant de fuite dans les dispositifs actifs (diode, transistor MOS ''Metal Oxyde Semiconductor'') double approximativement chaque 10 °C. La minimisation de la température réduit ainsi l'effet des courants de fuite. Si la température d'un dispositif actif augmente trop, il excédera les spécifications du fabricant et dérangera le fonctionnement normal du circuit[5]. I

Le changement de la température des dispositifs passifs change typiquement leurs valeurs. Par exemple, les résistances de film ont des coefficients de température qui s'étendent de la gamme de plusieurs parties par million par degré °C jusqu'aux plusieurs centaines. Des condensateurs céramiques, selon le matériel diélectrique, ont la variation de température de 30ppm/°C à 60 % selon les variations de température militaires (-55°C à +125°C) [5]. On ne désire pas typiquement ces changements de paramètres électriques. Si l'augmentation de température est assez haute, le dispositif actif ou passif étant chauffé peut de manière permanente se dégrader ou même se briser totalement.

Donc, une bonne conception thermique doit réduire au minimum n'importe quelles augmentations de température. Entant que concepteur on ne peut pas avoir le contrôle de changements de l'environnement du circuit, mais nous avons le contrôle de l'auto chauffage spatial du dispositif. Dans le cas du WSI, nous pouvons choisir les dispositifs sur le silicium qui produisent la quantité la plus basse de chaleur pour les taux d'horloge exigés dans le projet.

Ainsi, pour réunir la performance tant électrique que thermique d'un circuit, on doit réitérer thermiquement et électriquement la conception de modèle de chaque partie du WSI pour réaliser la performance exigée. De plus, au niveau physique on doit choisir des matériaux alternatifs ou incorporer des arrangements et des mécanismes de refroidissement complémentaires.

### II.2.2 Effets de température sur la construction physique

Avec peu d'exceptions, les métaux s'étendent quand leur température augmente et se contact quand ils sont refroidis. Le coefficient d'expansion thermique (TCE) est un paramètre très important à connaître dans la conception de boîtier électronique. Le tableau (voir annexe IV) montre des valeurs de TCE pour des métaux divers utilisés dans l'assemblage des boîtiers en microélectroniques.

Des contraintes thermiques se produisent quand un matériau prend de l'expansion ou de la contraction. Comme exemple, dans le cas d'un radiateur de cuivre soudé à un substrat de céramique métallisé, la céramique a un TCE de 6.4ppm/°C, tandis que le cuivre a un TCE de 16.8ppm/°C. Ainsi, pendant un cycle de température dans lequel il y a un certain nombre de périodes d'échauffement et de refroidissement, le cuivre s'étend et se contracte à un taux plus haut que la céramique, mais cette contrainte pourrait augmenter, et se multiplier d'un cycle de température à l'autre. De cette façon le joint entre eux se soude, et il provoque une déformation dans la céramique[5].

D'un autre côté réduire ou éliminer les tensions thermiques exige le choix des métaux bien spécifique pour minimiser les changements de la température causés par l'autochauffage.

### **∂** II.3 Analyse thermique

L'analyse thermique est un aspect important lors de la conception des dispositifs électroniques. Quand les matériaux sont chauffés, ils s'étendent et peuvent causer une contrainte qui peut rendre le dispositif inutilisable. De plus si une partie est surchauffée, elle s'approche de la zone de corrosion et d'oxydation des matériaux. Si la partie devient trop surchauffée elle peut perdre ses propriétés mécaniques et électriques. L'analyse thermique est normalement fait comme une étude préalable à une enquête de contrainte où la température est analysée par un modèle d'éléments finis structurel. Dans le cas de notre projet de recherche, l'analyse thermique est nécessaire au bon fonctionnement pour réaliser une compréhension minutieuse des différentes parties du processeur WSI.

L'analyse thermique avec le modèle en éléments finis va inclure les parties suivantes :

- → Analyse de la radiation thermique aux surfaces,

- Analyse de la convection autour des dispositifs,

- Analyse de la conduction à l'intérieur du processeur,

- Analyse thermique en régime permanent,

- Analyse thermique en régime transitoire,

- Analyse mixte thermo-mécanique.

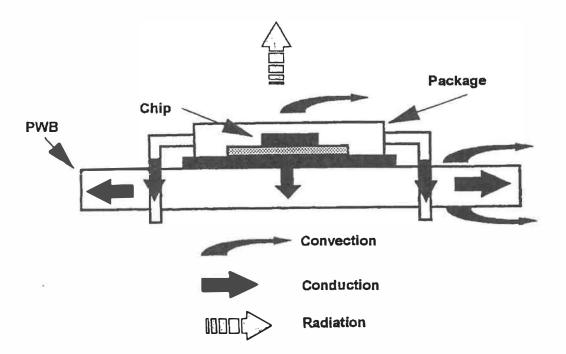

### II.3.1 Écoulement du Flux de chaleur

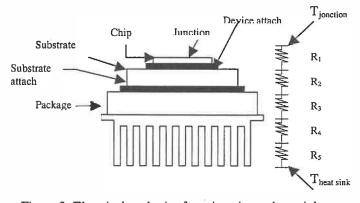

Le deuxième principe de la thermodynamique déclare que la chaleur coule toujours spontanément d'une région plus chaude à une région plus froide. Tous les dispositifs actifs et passifs sont des sources de chaleur. Ces dispositifs sont toujours plus chauds que la température moyenne de leur environnement immédiat. Il y a trois mécanismes pour le transfert de chaleur : conduction, convection et radiation, comme indiqué dans figure 2.1. Dans les sections suivantes, nous allons présenter le mécanisme de la distribution de température de la source de chaleur à l'environnement.

Figure 2.1 Conditions aux limites thermiques

### a) La conduction\_

C'est le transfert de chaleur provoqué par la différence de température entre deux régions d'un milieu matériel ou entre deux milieux matériels en contact physique.

Dans le mode d'échange par convection, la transmission de la chaleur se fait dans les fluides, les liquides ou les gaz en mouvement. Ces cas se rencontrent souvent dans l'échange entre une paroi et un fluide.

La loi fondamentale de la conduction thermique, établie par Fourrier sur la base de certaines expériences, s'exprime mathématiquement par la proportionnalité, en tout point d'un corps isotrope, de la densité de flux au gradient de température par :

$$\varphi = -k. \overrightarrow{grad}(T)$$

.....(2.1)

Cette loi traduit le fait que l'énergie thermique se propage des points les plus chauds vers les plus froids, et que le flux est d'autant plus intense que l'écart de température par unité de longueur est grand.

Le coefficient de proportionnalité K est la conductivité thermique du corps considéré, et s'exprime en W/(mK). Elle peut varier d'un point à l'autre du corps.

La connaissance de la conductivité thermique des matériaux reste un problème majeur.

Cette grandeur dépend d'un certain nombre de paramètres :

- Nature chimique du matériau,

- Nature de la phase considérée (solides, liquides, gazeuses), et de la température.

En d'autre terme, la loi de Fourrier est non linéaire, en appliquant le premier principe de la thermodynamique à un élément de volume indéformable et au repos (la variation d'énergie interne du système est égale à l'énergie thermique entrant dans le volume au travers de la surface limite, ajoutée de la chaleur dégagée par les sources internes).

On obtient finalement l'équation :

$$\rho.c_{p}.\frac{dT}{dt} = div \left[k.grad \left(T\right)\right] + q \qquad (2.2)$$

avec:

$\rho$ : masse volumique du corps  $\left[ kg / m^3 \right]$

$C_P$ : chaleur spécifique du corps [J/(kg.K)]

q : densité volumique des sources internes  $\left[W/m^3\right]$

Dans le cas particulier d'un corps homogène et de conductivité indépendante de la température l'équation devient :

$$\frac{\rho.c_p}{k}.\frac{dT}{dt} = \Delta T + \frac{q}{k} \tag{2.3}$$

La quantité  $k/(\rho.C_p)$ , appelée diffusivité thermique  $\left(\frac{m^2}{s}\right)$  caractérise la vitesse de diffusion de la chaleur dans le matériau.

### b) La convection

C'est le transfert d'énergie par mouvement macroscopique d'un fluide.

On distingue deux types de phénomènes convectifs :

- La convection naturelle ou libre, pour la quelle le mouvement provient de l'action simultanée de différences de température existant au sein du milieu, et d'un champ de force massique.

- La convection forcée, pour laquelle le mouvement est imposé par une action extérieure (pompe, ventilateur,....).

La représentation exacte des processus de transfert par convection pose des problèmes des mécaniques des fluides souvent très difficiles à résoudre directement.

Cependant, comme on ne s'intéresse en général qu'a la quantité de chaleur échangée entre le fluide et une paroi solide, on introduit un coefficient d'échange superficiel h tel que la densité de flux de chaleur  $\phi$ , à travers un élément de surface de la paroi, soit proportionnelle à la différence entre la température T de cet élément et une température moyenne du fluide  $T_a$ :

$$\phi = h.[T-T_a]$$

.....(2.4)

Le coefficient h dépend :

- du type de convection

- du type d'écoulement

- de la géométrie de l'écoulement

- la vitesse de l'écoulement

- de la température

- des propriétés thermo-physiques du fluide (viscosité)

- des conditions adoptées au niveau de la paroi (température constante ou densité de flux constante).

### c) La radiation

Il s'agit d'un rayonnement électromagnétique. La loi fondamentale de ce phénomène, appelée loi de Stefan-Boltzmann, exprime la densité de flux d'énergie émise par une surface idéale, dite noire, en fonction de sa température absolue :

$$\varphi = \sigma . T^4 \qquad (2.5)$$

Ou  $\sigma$  est la constante de Stefan-Boltzmann :  $5.67.10^{-8} \left[ \frac{W}{m^2.K^4} \right]$  .....(2.6)

L'équation d'échange, dans le cas particulier d'un corps noir à la température absolue T, plongé dans une enceinte noire à la température absolue T<sub>a</sub>, s'écrit :

$$\varphi = \sigma \cdot \left(T^4 - T_a^4\right) \dots (2.7)$$

En pratique, on tiendra compte de la géométrie du système par l'introduction d'un facteur de forme F lié à l'angle de vue de la surface rayonnante vers l'ambiante, et des propriétés émissives réelles de la surface, que l'on qualifiera par un coefficient ε appelé émissivité :

$$\varphi = \varepsilon . F . \sigma \left( T^4 - T_a^4 \right) \dots (2.8)$$

### d) Remarque

Dans notre cas, les deux modes d'échanges : convection naturelle et rayonnement thermique sont généralement négligeables, car l'écoulement de la chaleur dans les composants électronique étant essentiellement de type conductif, les deux autres modes interviennent surtout dans les échanges avec l'environnement extérieurs [6]. L'existence d'un radiateur est destinée à l'évacuation de la chaleur .

Le calcul de l'échange est une étape essentielle de la conception thermique des composants électroniques, car la qualité du refroidissement dépend des caractéristiques principales des circuits intégrés.

Il est probable que l'avenir appartienne aux techniques de refroidissement, qui permettent, avec une efficacité accrue, l'évacuation de la chaleur au plus prés des sources de dissipation (jonction).

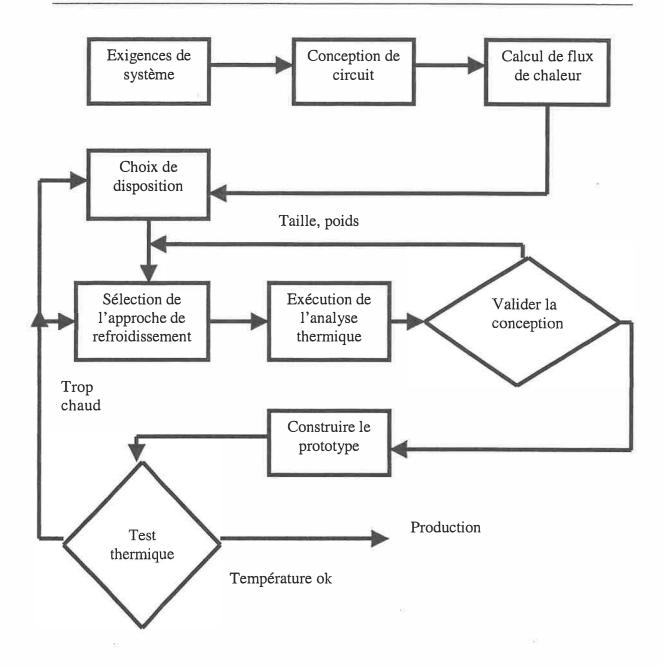

### II.3.2 La conception des systèmes électrothermiques.

Dans l'exécution d'une conception thermique, nous devons d'assurer d'enlever la chaleur résiduelle dans un processeur pour que la température de l'ensemble reste audessous de la température maximale d'opération. Notre approche est guidée selon la figure 2.2.

Pour commencer la conception thermique, nous devons connaître la quantité de puissance qui sera dissipée dans chacun des parties du processeur. Cependant, on doit connaître le cas le plus mauvais ou critique représentant des conditions d'utilisation du processeur, sa taille maximale et son poids et la disponibilité ou non de liquides de refroidissement (tant liquide que l'air).

Figure 2.2: Organigramme général pour la conception d'un système électrothermique

Dans cette étude nous avons proposé une disposition préliminaire des sources de chaleur avec un flux de chaleur pour chaque partie du processeur identifiée. Ainsi, une analyse thermique a été exécutée sur chaque modèle proposé calculant la température à

chaque point dans la structure. Suite à cette étude, nous avons analysé les résultats. D'une manière itérative, les blocs logiques du processeur sont déplacés, des matériaux changés et des chemins de chaleur ajustés pour trouver la conception thermique qui a le moins d'effet sur les paramètres importants du processeur. Nous avons tenu compte d'autres variables lors de l'analyse thermique comme le choix de la technique de refroidissement et l'échangeur thermique futur du processeur[5].

Une fois notre conception thermique complétée, un prototype sera construit et évalué par la compagnie Hyperchip Inc. Ainsi, le fonctionnement tant électrique que thermique du processeur sera évalué en profondeur. Des tests plus poussés seront menés pour évaluer les performances du prototype WSI avant la production du processeur final prévu durant les prochaines années.

# 11.3.3. La sélection de la technique de refroidissement thermique

Basé sur le niveau de puissance dissipée dans le circuit, nous devons choisir une technique de refroidissement la plus appropriée. Pour des niveaux de puissance bas, la conduction et/ou la convection naturelle peut être suffisante, donc un échangeur thermique (radiateur) n'est pas nécessaire.

Dans notre cas le processeur va dissiper 2kW, ainsi nous devons recourir à un échange thermique avec radiateur. La conception et l'application de ce radiateur sont présentés dans la partie qui suit. Cependant, l'addition d'un radiateur augmente la taille

et le poids aussi bien que le coût total du processeur. De plus, à ces niveaux de puissances élevées la convection forcée est inévitable pour arriver à refroidire le processeur.

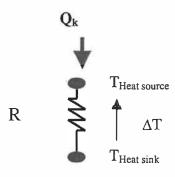

#### II .3.4.Choix du radiateur

De façon générale, pour choisir un radiateur approprié à une application, trois paramètres doivent être adressés[5] :

- R<sub>sa</sub>: la résistance thermique entre le radiateur et le milieu ambiant,

- le Volume de la quantité disponible du courant atmosphérique (ventilateur),

- La température maximale pour la jonction T<sub>imax</sub>.

La température d'exploitation a une température ambiante maximale  $T_{amb}$ .

La hausse maximale de la température de la jonction est définie comme :

$$\Delta T = T_{jmax} - T_{amb}$$

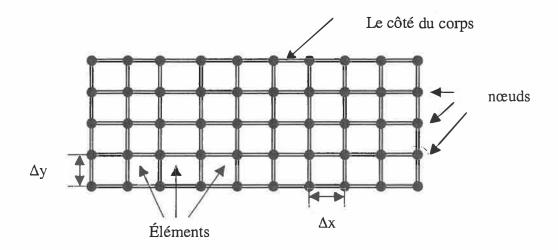

#### II.4 L'approche des éléments finis

La méthode d'éléments finis trace ses origines presque 200 ans en arrière, quand les fonctions d'interpolation ont été utilisées par Gauss. La première personne à utiliser le terme «la méthode des éléments finis » c'étais Clough dans une publication en 1960, quand il a décrit une méthodologie pour la résolution des problèmes d'élasticité[5].

La méthode d'éléments finis a été d'abord utilisée pour l'analyse de transfert de chaleur en 1965, quand Zienkiewicz et Cheung ont appliqué la méthodologie aux problèmes des champs généraux décrits par l'équation de Poisson et de Laplace. Le domaine de solution est réduit et séparé dans des régions plus petites appelées des

éléments. Ces éléments sont alors connectés aux points spécifiques, appelés des nœuds. On montre un modèle d'élément fini simplifié dans la figue 2.3.

Une des forces primaires d'analyse des éléments finis (FEA) est la capacité de représenter la géométrie irrégulière. L'approche des éléments finis est utilisée aujourd'hui pour résoudre les problèmes d'analyse structurelle, écoulement de fluide, des champs électromagnétiques et l'analyse thermique. Dans cette section, seulement l'analyse thermique de FEA sera discutée.

#### - II .4.1 Modélisation par éléments finis

Étudier une structure, donc un domaine continu, par la méthode des éléments finis consiste d'abord à effectuer une discrétisation géométrique. La structure est subdivisée en sous—domaines de forme géométrique simple appelé «élément fini» est défini non pas sur l'ensemble de la structure mais pour chacun de ses éléments. En d'autres termes on ramène le problème du milieu continu à un ensemble de problèmes discrets avec un nombre fini de paramètres inconnus qui sont déterminés par application de critères énergétiques. Dans la méthode matricielle des déplacements, les paramètres inconnus sont les déplacements aux nœuds. Ce déplacement (contraints en certaines nœuds par l'utilisateur )sont reliés aux charges appliquées (également définies par l'utilisateur ) par la matrice de rigidité du système. Le problème consiste donc à calculer cette matrice de rigidité globale du système à partir des matrices de rigidité de chaque élément déterminées en utilisant le théorème des travaux virtuels. Les détails de ces calculs, qui

heureusement sont effectués automatiquement sous forme matricielle par les logiciels spécifiques par exemple NISA [5].

Figure 2.3: Modèle d'éléments finis simplifié en 2D

Les pas d'exécution d'une analyse thermique par les éléments finis est représentés dans l'organigramme de la figue 2.4 et sera décrit ci-dessous.

Figure 2.4 : Organigramme pour exécuter une analyse par éléments finis.

- Le maillage : Consiste à subdiviser le domaine en éléments sur la forme triangulaire ou quadrilatère, ce processus peut être fait manuellement ou automatiquement par le logiciel pour l'analyse thermique. La densité d'élément doit être suffisante pour faire converger facilement la solution. Dans notre cas à peu prés un million d'éléments ont été nécessaires pour représenter fidèlement notre processeur.

- Choix de la fonction d'interpolation: Après que la forme d'élément a été choisie, l'analyste thermique détermine comment la variation du flux de chaleur à travers la structure doit être rapprochée. Typiquement, dans le cas d'une distribution spatiale particulière une fonction d'interpolation de polynôme peut être utilisée. Le nombre des nœuds liés à un élément met l'ordre de la fonction d'interpolation. Dans notre projet, nous avons utilisé et expérimenté plusieurs types de densité de flux de chaleur pour arriver à représenter la dynamique thermique du processeur WSI.

- Propriétés des matériaux : Préciser la conductivité thermique des matériaux comprenant la structure est une étape importante. Pour des systèmes où la conductivité thermique des matériaux est dépendante de la température, une solution itérative est exigée. Dans ce cas on se trouve avec un problème non-linéaire de transfert de chaleur.

- Application des conditions aux limites: Dans la terminologie d'élément fini, un nœud est prescrit si on connaît déjà les valeurs de la variable des champs. Dans une analyse thermique, une température doit être prescrite à un ou plusieurs nœuds dans la partie représentant les conditions aux limites. D'habitude, ces nœuds sont situés sur la limite du maillage de la structure. Les conditions connues sur ces limites internes et externes de la structure doivent être spécifiées, en particulier, la température ambiante et l'apport de flux de chaleur avec le milieu ambiant.

- Simulation du système d'équation : Des techniques numériques standard sont utilisées pour résoudre les champs de température inconnus à chaque nœud de la structure.

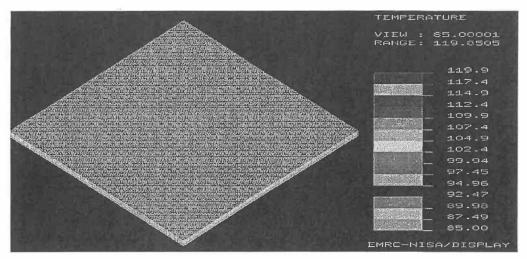

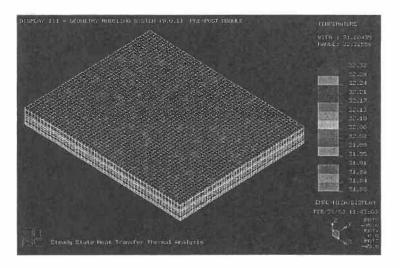

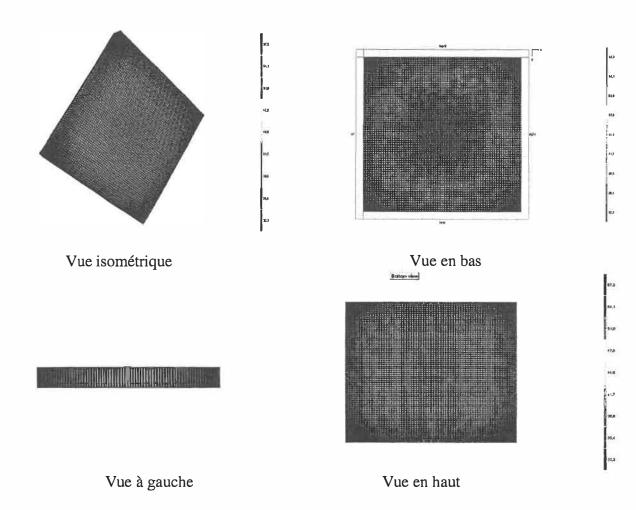

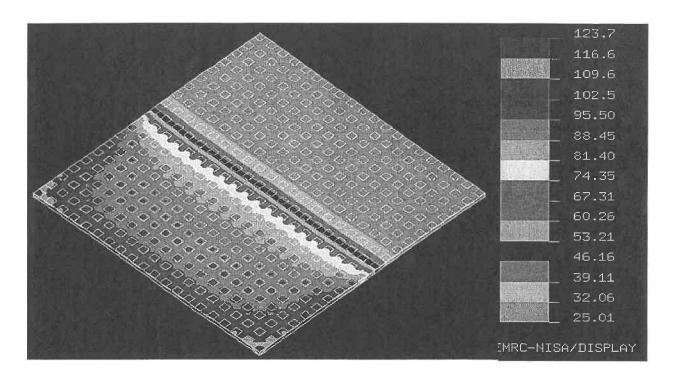

Après l'examen et l'analyse des résultats obtenus, nous pouvons déterminer si la solution est précise. À ce stade d'analyste on peut ajuster la forme et le nombre des éléments ou selon les ré. Itats changer les conditions aux limites pour mieux représenter la dynamique. De plus, selon le cas on peut ajuster la conductivité thermique des divers matériaux si les conductivités varient avec la température. Cependant, on peut aussi ajuster les dimensions pour optimiser la conception du processeur. La figure 2.5 expose les résultats d'une analyse thermique par les éléments finis exécutée sur un boîtier de type BGA (*Ball Grid Array*). Les couleurs diverses sur le côté droit de la figure correspondent à l'échelle de température[5].

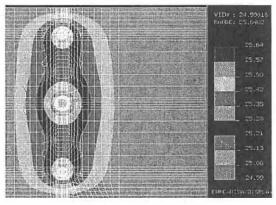

Figure 2.5 : Exemple de résultat d'une analyse thermique par les éléments finis.

#### II .5 Choix du boîtier

Dans le texte qui va suivre nous allons utiliser le mot anglais "packaging" puisqu'il est plus représentatif que la simple mise en boîtier.

Un des niveaux les plus critiques de la conception de nouveau circuit intégré c'est le choix du type de packaging, puisqu'ils sont typiquement sensibles aux influences électriques, mécaniques, physiques et chimiques.

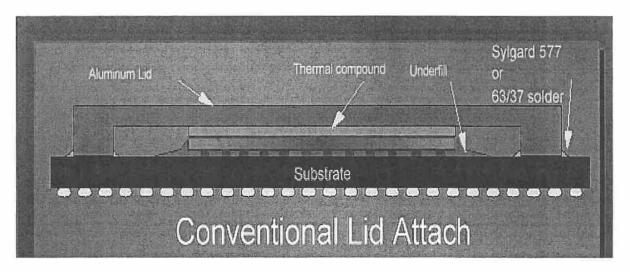

Figure 2.6: Flip Chip Packaging (FCP)

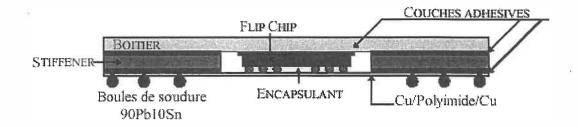

Le packaging choisi à cette étude est une technologie introduite par IBM appelée C4 (Control Collapse Chip Connection) qui consiste en un choix de construction de packaging où les interconnexions sont sous forme matricielle tout au long de la chaîne d'interconnexion. Ainsi, les circuits intégrés reçoivent une préparation spécifique des plots de sortie sous forme de bille d'alliage Plomb-étain (figure 2.9) qui réalisera la liaison électrique et mécanique avec le niveau de packaging suivant. La principale caractéristique de ce mode d'assemblage est qu'il permet un plus grand nombre de connexions, pour une puce de taille donnée, que les sorties périphériques traditionnelles[6].

Néanmoins, cette technique peut devenir critique lorsque l'adaptation des coefficients de dilatation thermique n'est pas très bonne (ou dans le cas de dissipations thermiques importantes) dans le silicium; en effet, des contraintes mécaniques importantes peuvent être générées à l'interface des soudures: fatigue plastique des billes de soudures situées vers l'extérieur de la puce (zones où les contraintes sont les plus élevées) entraînent des problèmes de fiabilité lors des cycles thermiques. Pour restreindre ce type de problème, des résines sont souvent injectées entre la puce et son support[7].

Figure 2.7: Exemple: Flip Chip TBGA (Tape Ball Grid Array).

Figure 2.8: Exemple: Flip Chip sur MCM (Multi Chip Module).

#### II.5.1 Propriétés électriques des protubérances

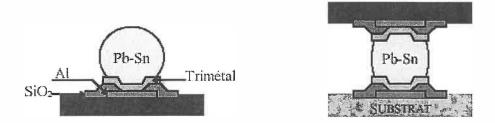

L'assemblage d'un circuit intégré sur son support, dans la configuration Flip Chip, peut s'effectuer par soudure ou par collage. Dans le premier cas, des protubérances de soudure (boules ou colonnes) sont disposées sur la puce, et permettent de créer un lien mécanique et électrique avec le support (figure 2.9). Dans le second cas, c'est une substance adhésive qui provoque la jonction des deux corps (figure 2.10); trois types d'adhésif sont à distinguer: Conducteur, isolant et isotrope (c'est à dire que la conduction électrique s'effectue uniquement selon une direction précise)[8].

Figure 2.9: Technologie C4: Boules de soudure.

Figure 2.10: Montages Flip Chip utilisant des substances adhésives.

Un certain nombre d'inconvénients sont toutefois relatif à ce procédé (flip chip):

- La puce est fixée face en bas, ce qui rend impossible le contrôle,

- Le contrôle des protubérances après report n'est pas non plus possible,

- Les protubérances sont soumises à toutes les dilatations différentielles (Substrat /Puce),

- La transmission thermique est limitée par la résistance thermique des boules,

- Un excellent alignement des protubérances est nécessaire,

- Le pré-test de la pastille n'est pas réalisable,

- Généralement, un design spécifique des aires d'accueil de la puce est nécessaire.

Malgré ces inconvénients, ce type d'assemblage possède un avenir prometteur, car il favorise la miniaturisation des packages. Cela est un avantage primordial pour le processeur en développement chez Hyperchip.

#### II.5.2. Performances électriques

La hauteur des protubérances pour l'interconnexion puce-boîtier s'étend (approximativement) de  $50\mu m$  à  $200\mu m$ . Celles utilisées en BGA (interconnexion du

boîtier) possèdent une hauteur de 0.5 mm ou plus. Le tableau suivant donne quelques ordres de grandeurs des longueurs d'onde associées à différentes fréquences:

| FREQUENCE                                 | 100 MHz | 1 GHz         | 10 GHz | 100 GHz |

|-------------------------------------------|---------|---------------|--------|---------|

| λ <sub>0</sub> (vide) (mm)                | 3000    | 300           | 30     | 3       |

| $\lambda (\varepsilon_r \approx 10) (mm)$ | ≈1000   | ≈ 10 <b>0</b> | ≈10    | ≈l      |

| deriffique (mm)                           | ≈100    | ≈10           | ≈]     | ≈0.1    |

Tableau 2.1 : Ordre de grandeurs d'onde associées à différentes fréquences

Les dimensions des connexions restent très faibles devant la longueur critique  $\mathbf{d_{critique}}$  (grandeur pour laquelle il est nécessaire d'utiliser la théorie des lignes de transmission pour caractériser électriquement les interconnexions). En effet, comme le montre le tableau précédent, même pour des fréquences très élevées, la longueur d'onde des signaux reste nettement supérieure à la hauteur des protubérances. C'est pourquoi, ces interconnexions peuvent être considérées comme « idéales », du point de vue électrique, c'est à dire:

$\mathbb{Z}_0 \ll 1\Omega$ . (impédance de sortie caractéristique)

**t**<sub>p</sub> << 1s. (délais de propagation)

$\alpha \ll 1.$ (pertes)

Pour des technologies BGA, il est nécessaire de prendre des précautions. Les hauteurs des protubérances sont plus importantes. Pour des fréquences élevées, il est possible que les approximations précédentes ne soient plus valables (Il faut assimiler les interconnexions à des lignes de transmission): Un retard de propagation et une impédance caractéristique non nuls, sont alors envisageables[9].

Voici quelques ordres de grandeurs sur les performances électriques des technologies C4 et fil utilisé pour le routage "wire".

|      | RESISTANCE (m $\Omega$ ) | INDUCTANCE (nH) | CAPACITANCE (pF) |

|------|--------------------------|-----------------|------------------|

| WIRE | 90                       | 2.58            | 0.02             |

| C4   | 30                       | 0.06            | 0.17             |

Tableau 2.2 : Ordre de grandeurs sur les performances électriques des technologies C4

La technologie C4 réduit l'inductance des interconnexions (par rapport au câblage). Ceci est un avantage important, car le bruit de commutation est alors fortement affaibli.

#### II.5.3 Performances mécaniques

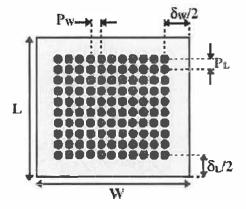

# II.5.3.1 connexions E/S (I/O) : Entrée Sortie (Input Output) en réseau sur toute la surface de la puce

Figure 2.11: Disposition des boules de soudure sur la puce (Grid Array).

Soient W et L, les dimensions caractéristiques du circuit intégré[7]:

$$W = (n_w - 1).p_w + \delta_w$$

$$L = (n_L - 1).p_L + \delta_L$$

avec:

n<sub>w</sub>: Nombre de I/O dans le sens de la largeur W.

$n_L$ : Nombre de I/O dans le sens de la longueur L.

pw: Pas d'interconnexion sur W.

$p_L$ : Pas d'interconnexion sur L.

$\delta_w$ : distance inutilisée sur W.

$\delta_L$ : distance inutilisée sur L.

Le nombre N de connexions I/O vérifie:

$$N = n_w \cdot n_L$$

Dans le cas où le circuit intégré est symétrique, c'est à dire  $L=W,\,n_L$  et  $n_w$  peuvent s'exprimer de la façon suivante:

$$n_{L} = \frac{(p_{L-p_{w}} + \delta_{wL} - \delta_{L})}{2.p_{L}} + \frac{1}{2} \sqrt{(\frac{p_{L} - p_{w} + \delta_{w} - \delta_{L}}{p_{L}})^{2} + 4N\frac{p_{w}}{p_{L}}}$$

$$n_{w} = N/n_{L}$$

**Remarque :** Dans le cas où en plus,  $p_L = p_w = p$  et  $\delta_L = \delta_w = \delta$  alors:

$$N_{yy} = n_y = \sqrt{N}$$

#### II.5.3.2 Densité d'interconnexion et efficacité

La densité d'interconnexion D se définit comme étant le rapport entre la longueur totale d'interconnexion  $L_{tot}$  et la surface totale A occupée par celle-ci (c'est à dire dans notre situation, la surface de la puce)[9]:

$$D = L_{tot}/A = N. h/(L.W)$$

avec:

h: hauteur des soudures.

Étant donné que h est très petite, la densité d'interconnexion précédente est bien meilleure que celle rencontrée dans le ''bonding wire'' et la technologie TAB (Tape Array Ball).

L'efficacité relative à ce type de connexion peut être considérée comme égale à 1: en effet, les protubérances (boules de soudure, colonnes...) n'engendrent pas une surface d'interconnexion supplémentaire à celle de la puce.

#### II.5.4 Aspect thermique

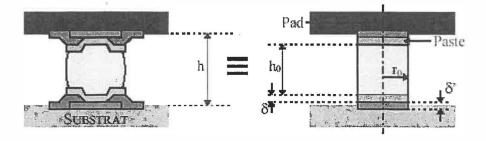

#### II.5.4.1 Résistance thermique d'une boule de soudure

# a) 1<sup>ERE</sup> METHODE

L'interconnexion présente entre la puce et son support est considérée comme uniforme.

L'expression de sa résistance thermique s'écrit:

$$R_{ball} = \frac{h}{K_{ball}.\pi.r_0^2}$$

**K**<sub>ball</sub>: Conductivité thermique de la boule de soudure.

# b) 2<sup>EME</sup> METHODE

Cette fois, les *pads* et les couches métalliques *pastes* présentes aux deux extrémités des protubérances sont pris en compte dans le calcul de la résistance thermique de l'interconnexion:

$$R_{ball} = 2R_{pad} + 2R_{paste} + R_{bump}$$

Avec:

$$R_{bump} = \frac{h_0}{K_{ball}.\pi.r_0^2}$$

$\mathbf{K}_{pad}$ : Conductivité thermique d'un *pad*.

$\mathbf{K}_{\text{paste}}$ : Conductivité thermique d'un *paste*.

#### c) 3<sup>EME</sup> METHODE

La méthode la plus précise, mais également la plus complexe à mettre en œuvre, correspond à la simulation numérique. En discrétisant la protubérance et en utilisant le principe des éléments finis, il est possible d'obtenir une approximation de la résistance thermique très proche de la réalité[6].

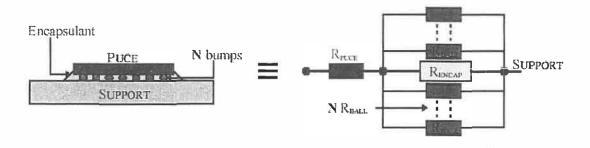

#### II.5.4.2 Résistance thermique de l'interconnexion puce-boîtier.

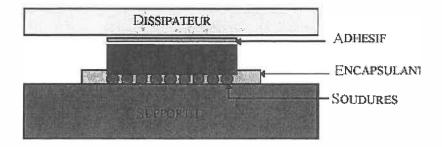

Quand à cette modélisation thermique elle porte sur la totalité des interconnexions, présentes entre la puce et son support.

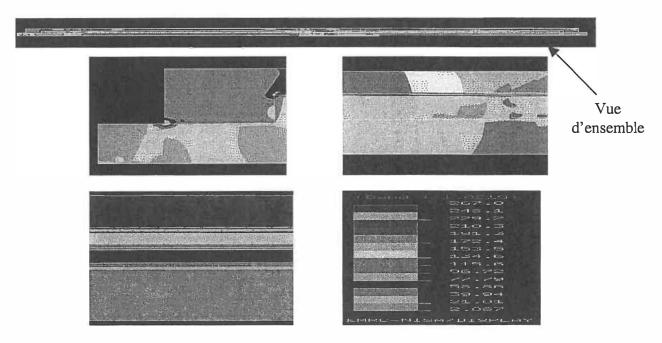

Figure 2.12: Modélisation thermique d'une configuration FLIP CHIP.

La résistance thermique  $\mathbf{R}_{Soudure}$ , modélisant la totalité des interconnexions (soudures), entre la puce et le support, s'écrit (dans le cas où le transfert thermique est considéré comme unidimensionnelle):

$$R_{\text{soudure}} = R_{\text{ball}} / N$$

Il est nécessaire de tenir compte du comportement thermique du milieu existant entre la puce et son support (encapsulant ou air ambiant). La résistance thermique d'un tel milieu est à ajouter à  $\mathbf{R}_{soudure}$ , en parallèle.

• Dans le cas d'un encapsulant:

$$R_{encap} = \frac{h}{K_{encap}[S-N.\pi.r_0^2]}$$

avec:

K<sub>encap</sub>: Conductivité thermique de l'encapsulant.

S: Surface occupée par la puce.

N: Nombre de soudures présentes sur la puce.

• Dans le cas d'un fluide (air ambiant):

$$R_{fluide} = \frac{1}{K_{fluide} \left[ S - N.\pi r_0^2 \right]}$$

avec

$\mathbf{H}_{\text{fluide}}$ : Coefficient de transfert thermique du fluide interstitiel (air, gaz particuliers...).

Enfin, la résistance thermique équivalente existant entre la puce et son support, s'exprime de la façon suivante:

$$R_{EQ} = \left(\frac{1}{R_{soudre}} + \frac{1}{R_{encap}}\right)^{-1}$$

Il apparaît alors que plus le nombre de soudures N est élevé, plus la résistance thermique  $R_{soudure}$  diminue, à l'inverse de  $R_{encap}$  (la surface de soudure augmente):  $R_{EQ} \cong R$   $R_{soudre}$

Figure 2.13: Exemple de modélisation thermique d'une puce montée en Flip Chip.

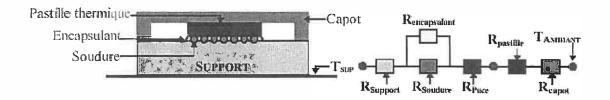

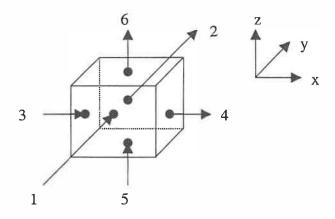

#### **II.5.5** Contrainte thermique (Thermal Stress)

Figure 2.14: Contrainte thermique sur les soudures.

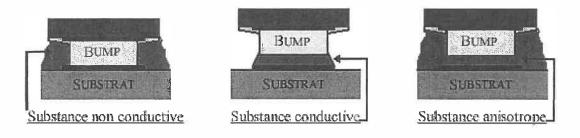

L'un des inconvénients le plus sensible de l'assemblage Flip Chip est sans doute le problème de fatigue dû aux sollicitations thermomécaniques pendant les variations de température (figure 2.14). Pour pallier à cet inconvénient, il est possible d'agir sur plusieurs paramètres. Tout d'abord, on essaiera d'appairer au mieux les matériaux constituant le circuit intégré (silicium) et le substrat (c'est à dire choisir des matériaux dont les coefficients d'élasticité linéaire CTE sont voisins)[6]. On voit tout de suite que cette technique d'assemblage est optimum pour la filière MCM-S, mais également pour les filières MCM-D utilisant le silicium comme substrat. Mais il est également possible de jouer sur la forme, la hauteur et les matériaux de la protubérance. Plusieurs procédés plus ou moins sophistiqués de protubérances hautes existent: Ils débouchent en général sur un empilage de protubérances, élaborées en parallèle, sur la puce et le substrat, puis reliées entre elles (figure 2.15).

L'utilisation d'encapsulant (choisi judicieusement) permet également de limiter les déformations plastiques au niveau des soudures: avec un CTE compris entre celui de la puce et celui du substrat, l'encapsulant joue le rôle d'un « amortisseur » contre les phénomènes de cisaillement.

Figure 2.15: Empilage de protubérances.

Définissons quelques grandeurs caractéristiques:

L: Distance entre la soudure et le centre de la puce.

h: Hauteur de la protubérance (distance entre la puce et son support).

d: Diamètre de la protubérance.

τ: Contrainte sur la soudure.

Δα: Différence de CTE entre la puce et son support.

E: Module d'élasticité de la protubérance. (Module de Young (E))

ΔT: Variation de températures à laquelle est soumis le système.

Lors d'une variation de température, une soudure est soumise à une contrainte dont

l'expression

s'écrit:

$$\tau = \frac{E.d.\Delta\alpha.\Delta T.L}{h_2}$$

L'assemblage des circuits intégrés, selon la méthode FLIP CHIP, utilise des boules de soudure afin de lier mécaniquement et électriquement la puce avec son support. Ce type d'interconnexion procure les meilleures performances mécaniques (surface d'interconnexion équivalente à celle de la puce), thermique (le flux de chaleur passe directement de la puce au support, via les boules de soudure) et électrique (la longueur d'interconnexion procurée par les boules de soudure, sont très courtes et permettent donc de monter en fréquence sans la perturbation des signaux). Cependant, cette technique d'assemblage ne permet pas de tester directement la puce une fois soudée. De même le contrainte thermique peut provoquer des ruptures au niveau des connexions. Ainsi, cet aspect est crucial pour le futur processeur qui sera développé par Hyperchip.Inc.

Figure 2.16: Interconnexion d'une puce sur son support: Flip Chip.

#### Modélisation électrique:

- Impédance caractéristique  $Z_0 \ll 1\Omega$ .

- Temps de propagation  $t_P \ll 1s$ .

- Pertes  $\alpha_r$  et  $\alpha_d \ll 1$ .

#### Modélisation thermique:

- Résistance thermique R<sub>th</sub>.

- Contrainte thermique.

- Configuration extérieure.

#### Modélisation mécanique:

- Type de disposition des pads sur le C.I (Circuit Intégré).

- Densité d'interconnexion D.

- Efficacité η ≅1.

#### II.6 Conclusion du chapitre II

L'étude thermique classique d'un système électronique consiste donc à analyser la capacité de celui-ci à évacuer les Joules issues des différentes sources de chaleur que sont les composants.

Pour atteindre cet objectif, tous les éléments du système sont modélisés en groupes de résistances thermiques en régime permanent. Cependant, lorsque la densité de puissance dissipée augmente, la contrainte thermique en régime transitoire devient cruciale pour le bon fonctionnement du CI de grand taille (WSI)

# Chapitre III Conditions aux limites thermiques

#### III.1 Introduction

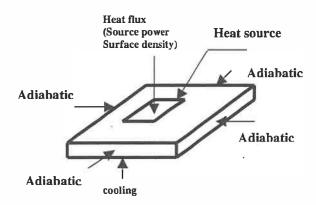

L'augmentation de la capacité d'intégration des puces actuelles entraîne un échauffement conséquent. Lors du développement du processeur WSI il est devenu indispensable de prévoir plus précisément les effets de la température sur différentes parties et surtout de trouver des moyens fiables et pratiques pour quantifier les dégagements de chaleur.

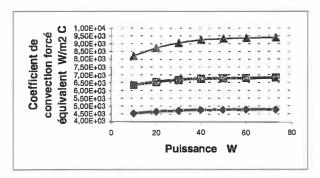

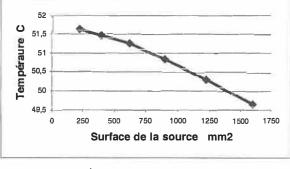

L'un des problèmes majeurs que nous avons rencontré pour faire une étude thermique au niveau du boîtier du processeur est de déterminer les conditions aux limites. Ainsi, à cet effet une nouvelle approche a été établie pour la détermination d'un coefficient de convection équivalent h<sub>équi</sub> au niveau de la jonction ; afin d'éviter la spécification de la température au-dessous de boîtier. Cette spécification introduit un court-circuit thermique entre la surface et la jonction. Pour palier à ce problème, il faut mailler toute la structure jusqu'au radiateur. Cela nécessite l'utilisation d'un modèle qui peut atteindre des dizaines de millions d'éléments rendant l'analyse impossible.

Les performances recherchées sont : l'augmentation de la vitesse d'opération et la miniaturisation des composants. Ainsi, dans les deux cas cela se traduit par une

augmentation de la température causée respectivement par l'accumulation d'un résidu thermique d'un cycle à l'autre et l'augmentation de la densité de puissance dissipée.