# UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

TRAITEMENT ÉCO-ÉNERGÉTIQUE POUR DES SYSTÈMES MIMO MASSIFS:

UNE APPROCHE DE CALCUL APPROXIMATIF

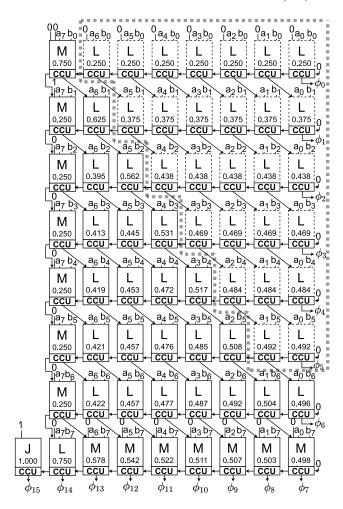

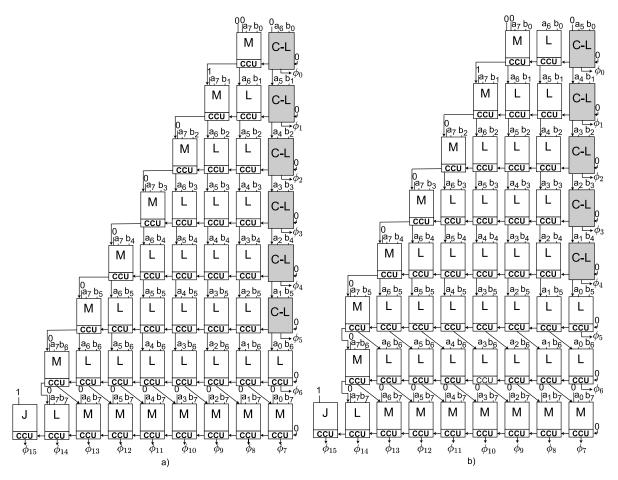

ENERGY EFFICIENT MASSIVE MIMO PROCESSING FOR NEXT GENERATION

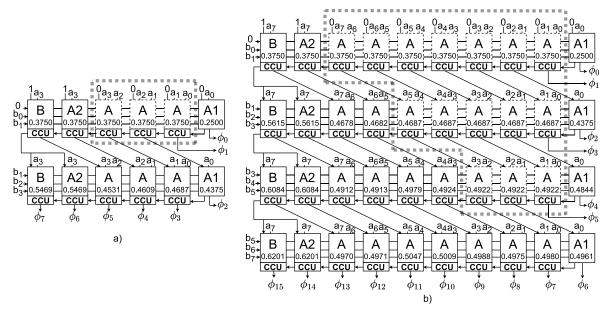

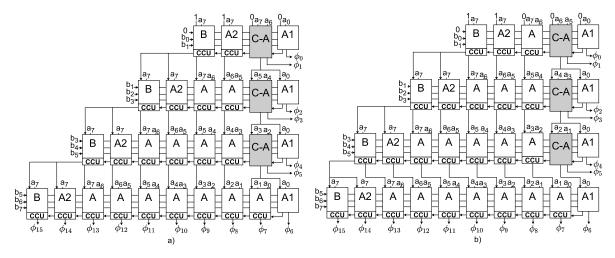

WIRELESS COMMUNICATION SYSTEMS: AN APPROXIMATE COMPUTING

APPROACH.

THÈSE PRÉSENTÉ(E)

COMME EXIGENCE PARTIELLE DU

DOCTORAT EN GÉNIE ÉLECTRIQUE

PAR ABHINAV KULKARNI

# Université du Québec à Trois-Rivières Service de la bibliothèque

# **Avertissement**

L'auteur de ce mémoire ou de cette thèse a autorisé l'Université du Québec à Trois-Rivières à diffuser, à des fins non lucratives, une copie de son mémoire ou de sa thèse.

Cette diffusion n'entraîne pas une renonciation de la part de l'auteur à ses droits de propriété intellectuelle, incluant le droit d'auteur, sur ce mémoire ou cette thèse. Notamment, la reproduction ou la publication de la totalité ou d'une partie importante de ce mémoire ou de cette thèse requiert son autorisation.

# UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

# Doctorat en génie électrique (3739)

# Direction de recherche: Messaoud AHMED OUAMEUR Daniel MASSICOTTE Co-directeur Jury d'évaluation François Nougarou Président Sébastien Roy Externe Michel Lemaire Interne UQTR

Thèse soutenue le 22 11 2024

### Résumé

Avec l'avancée des technologies, les limitations de la norme 5G en matière de débit, connectivité et faible latence exigent le développement de normes pour au-delà de la 5G (B5G - Beyonf 5G). L'émergence de la 6G sous B5G pose des défis concernant l'efficacité énergétique (EE) du traitement des stations de bases (EE - Energy Efficiency). La technologie Multiple Input Multiple Output extrêmement large (XL-MIMO - Extremely Large MIMO), qui améliore l'efficacité spectrale en utilisant des antennes multiples à grande échelle, est essentielle pour la 6G. Toutefois, les systèmes MIMO traditionnels rencontrent des difficultés, notamment une bande passante d'interconnexion élevée et une complexité computationnelle accrue, entraînant des hausses de latence et de consommation d'énergie. La technologie MIMO décentralisée (D-MIMO - Decentralized MIMO) résout ces problèmes en décentralisant les tâches de traitement, réduisant ainsi la bande passante et la complexité, et diminuant la latence et la consommation d'énergie. Le calcul approximatif peut encore améliorer l'Energy Efficiency (EE) en exploitant la résilience aux erreurs du système.

L'objectif principal de cette recherche est d'améliorer l'EE dans la détection des signaux sans fil au sein de Multiple Input Multiple Output (MIMO) grâce à une approche en deux niveaux : la décentralisation de l'algorithme et l'intégration du calcul approximatif dans la détection des signaux. La décentralisation de l'algorithme consiste à développer un nouvel algorithme de détection Decentralized MIMO (D-MIMO), en caractérisant différentes topologies matérielles pour l'accumulation et le traitement des gradients nécessaires. Une méthode heuristique pour les circuits de multiplication signée approximative basés sur Field Programmable Gate Array (FPGA) est également proposée, offrant des compromis entre précision et performance matérielle. L'impact des niveaux d'approximation sur la qualité de service (Quality of Service (QOS)) de la détection

des signaux est étudié avec le modèle Bruit de multiplication approximatif (Approximate Multiplication Noise (AMN)), qui capture les irrégularités causées par la multiplication approximative.

Un algorithme de détection D-MIMO, Newton décentralisé (Decentralized Newton (DN)), utilisant l'optimisation de Newton pour le matériel FPGA, est proposé et évalué pour la bande passante d'interconnexion, la complexité computationnelle et d'autres indicateurs de performance clés (Key Performance Indicator (KPI)) de Beyond 5G (B5G). Les circuits de multiplication signée approximative pour FPGA, développés avec la méthodologie clonage logique (Logic Cloning (LC)), sont optimisés pour la précision, la consommation de ressources et l'énergie. La performance des multiplications approximatives est évaluée pour la détection des signaux forçage zéro (Zero Forcing (ZF)) MIMO. Une analyse de l'impact de l'approximation sur le QoS est réalisée en calculant une expression analytique pour le taux d'erreur de symbole (Symbol Error Rate (SER)) à l'aide du modèle AMN. Les analyses de fidélité du signal et de résilience fournissent des informations sur les configurations fiables de multiplication approximative et les seuils de dégradation de la fiabilité du système.

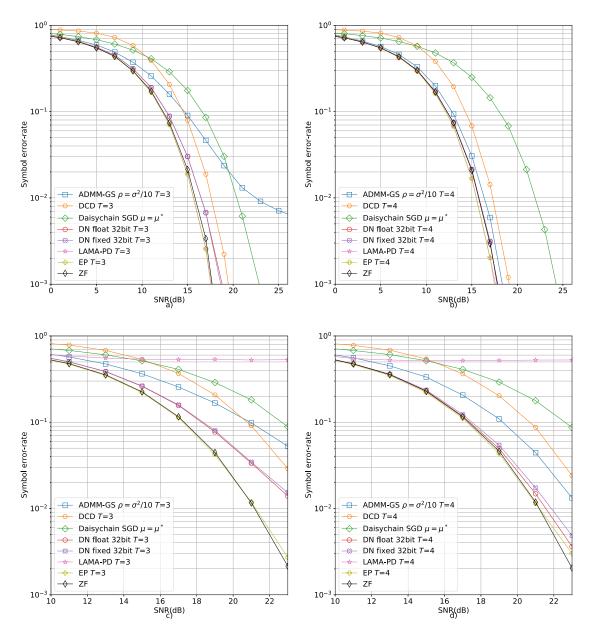

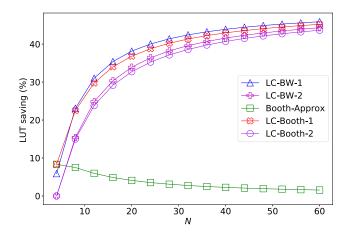

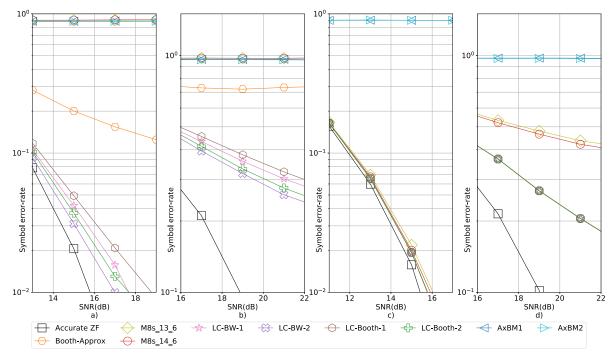

En termes de SER, l'algorithme DN est comparable à la détection ZF en bruit Gaussien blanc additif (Additive White Gaussian Noise (AWGN)), maintenant une complexité linéaire constante à travers les clusters d'antennes Base Station (BS). La configuration en étoile de DN utilise moins de ressources, consommant environ 78,4× et 169× moins d'énergie que les méthodes GPU. Pour des opérandes de 16 bits, la méthode LC réduit la consommation des tables de correspondances (Look-Up Table (LUT)) de 31,05% pour Booth et de 36,85% pour Baugh Wooley (BW), tout en réduisant le Power Delay Product (PDP). L'analyse de l'impact de l'approximation sur le QoS dans Single Input Single

Output (SISO) montre que des niveaux d'approximation plus élevés améliorent l'EE dans des conditions de faible rapport signal sur bruit (Signal-to-Noise Ratio (SNR)), tandis que des niveaux plus faibles sont plus efficaces dans des conditions de SNR élevé. Cette recherche jette les bases pour l'amélioration de l'EE de la détection MIMO en utilisant la décentralisation algorithmique et le calcul approximatif.

# Summary

As technology advances, the limitations of the 5G standard in meeting demands for throughput, connectivity, and low latency necessitate the development of B5G communication standards. With 6G emerging as a key development under B5G, a major concern is the EE of BS processing. Extremely Large MIMO (XL-MIMO) technology, which enhances spectral efficiency through multiple antennas at a extremely large scale, is an infrastructure enabler for 6G. However, traditional MIMO systems face challenges such as high interconnect bandwidth and computational complexity when scaled to a large scale, leading to increased latency and energy consumption. D-MIMO addresses these issues by decentralizing processing tasks to reduce interconnection bandwidth and computational complexity, thereby lowering latency and energy consumption. Approximate computing has potential for further enhancing EE by utilizing error-resiliency of the system.

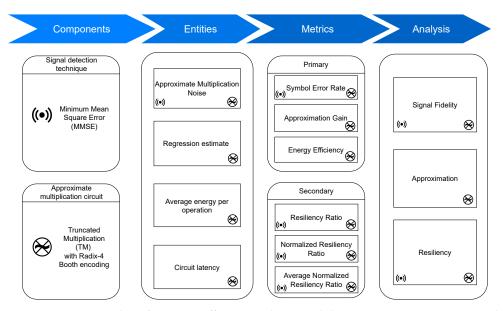

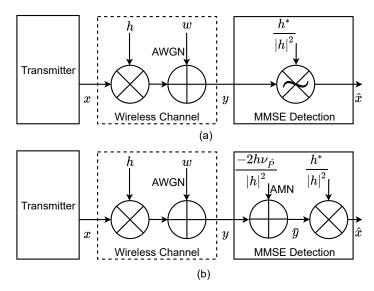

The primary objective of this research is to improve EE in wireless signal detection within MIMO through a two-level approach: algorithm decentralization and incorporating approximate computing techniques in signal detection. Algorithm decentralization involves developing a novel D-MIMO detection algorithm characterizing different hardware topologies for accumulation and processing of gradients required for the algorithm. A novel heuristic methodology for FPGA based approximate signed multiplication circuits is also introduced, which provides controlled trade-offs between multiplication accuracy and hardware implementation performance. In systematic analysis of the impact of approximation levels on the QoS of signal detection, novel AMN model is evaluated to capture the irregularities caused due to approximate multiplication used for wireless signal detection.

A novel D-MIMO detection algorithm, DN, using Newton optimization for FPGA hardware, is proposed and assessed for interconnect bandwidth, computational complexity, and other B5G KPIs. Approximate signed multiplication circuits for FPGA, developed using LC methodology, are optimized for accuracy, resource consumption and power consumption. The performance of approximate multiplications is evaluated for ZF MIMO signal detection. A systematic analysis of the impact of approximation on QoS is conducted by computing an analytical expression for SER using the AMN model. Signal fidelity, approximation, and resiliency analyses provide insights into reliable approximate multiplication configurations and the thresholds at which system reliability degrades.

In terms of SER, the DN algorithm performs comparably to ZF detection in AWGN, maintaining consistent linear complexity across BS antenna clusters. The DN star configuration uses approximately 1.05× DSP48E, 0.84× FF, and 0.71× LUT compared to the DN ring, with both configurations being more power efficient, consuming about 78.4× and 169× less power than GPU based methods. For 16-bit operands, LC method effectively reduces LUT resource consumption by 31.05% for Booth and 36.85% for BW, and lower the PDP by 34% for Booth and 35% for BW. The systematic analysis of the impact of approximation level of multiplication on QoS of signal detection in SISO indicates that higher approximation levels improve EE across all bit-width values, proving advantageous in low SNR conditions, while lower approximation levels are more effective under high SNR conditions. A guideline to extend the systematic analysis of SISO to MIMO enables to gain insights on approximate multiplication configuration. The research work builds foundations using algorithmic decentralization and approximate computing for strategically approaching the research problem of improving EE for MIMO detection.

# Acknowledgment

I am grateful to my supervisor, Prof. Messaoud, for his mentorship and guidance. His expertise in research, along with his innovative approach with research methodology, has been instrumental in shaping my research journey. I would also like to extend my sincere thanks to my co-supervisor, Prof. Daniel, whose expert eye, mentorship and valuable feedback have been crucial to refining my research.

I would also like to acknowledge my colleagues, Michel and Rabiul, for their support and guidance. Their assistance has been a source of strength throughout my academic journey. My deepest gratitude goes to my parents and brother, whose affection and encouragement has helped me navigate the challenges of this academic pursuit.

I believe that knowledge can be advanced through mindfulness and commitment. I also thank all the researchers whose foundational work has allowed me to develop my own research and present this thesis work. Finally, I would like to express my thanks to UQTR for providing me with the opportunity and conducive environment to develop my skills and develop as a researcher.

# **Table of contents**

| Résumé    |                                                      | iii  |

|-----------|------------------------------------------------------|------|

| Summa     | ry                                                   | vi   |

| Acknow    | eledgment                                            | viii |

| Table of  | contents                                             | ix   |

| List of f | igures                                               | xiii |

| List of t | ables                                                | xiv  |

| List of a | acronymsx                                            | viii |

| Chapter   | 1 - Introduction                                     | 1    |

| 1.1       | Background                                           | 1    |

| 1.2       | Rationale                                            | 8    |

| 1.3       | Research Problem                                     | 10   |

| 1.4       | Objectives                                           | 11   |

| 1.5       | Contributions                                        | 11   |

| 1.6       | Research Methodology                                 | 13   |

| 1.7       | Research Infrastructure                              | 15   |

| 1.8       | Thesis Outline                                       | 16   |

| Chapter   | 2 - Literature Review                                | 18   |

| 2.1       | Algorithm decentralization for MIMO unlink detection | 18   |

| 2.2     | Heuris  | stic   | methodology      | for     | FPGA      | based                                   | signed                                  | approximate                             |            |

|---------|---------|--------|------------------|---------|-----------|-----------------------------------------|-----------------------------------------|-----------------------------------------|------------|

|         | multip  | licat  | ion circuits     |         |           |                                         |                                         |                                         | 24         |

| 2.3     | Systen  | natic  | analysis of im   | pact o  | f approxi | mate mu                                 | ltiplicatio                             | on on wireless                          |            |

|         | signal  | dete   | ction            |         |           | • • • • • • • • •                       |                                         |                                         | 27         |

| Chapter | 3 - Alg | orith  | ım decentralizat | ion fo  | r MIMO    | uplink de                               | etection                                |                                         | 31         |

| 3.1     | Résum   | né Lo  | ong              |         |           |                                         |                                         |                                         | 31         |

|         | 3.1.1   | Co     | ntexte de Reche  | erche . |           |                                         |                                         |                                         | 31         |

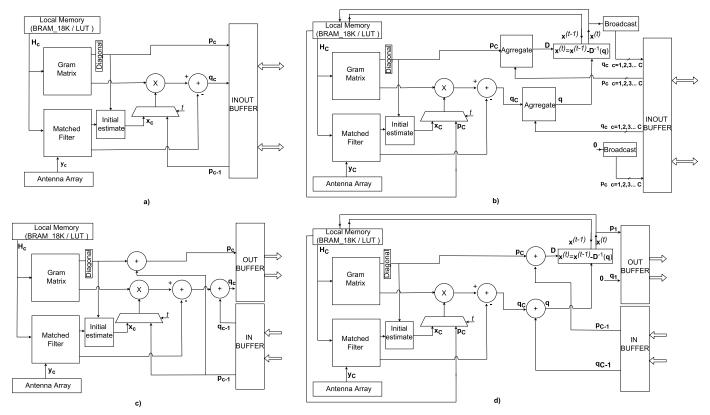

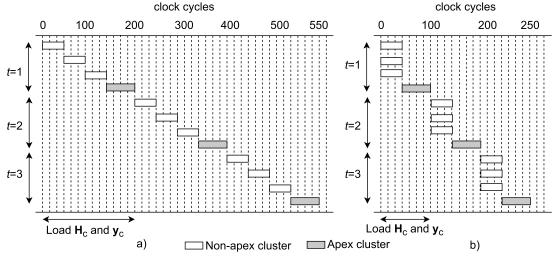

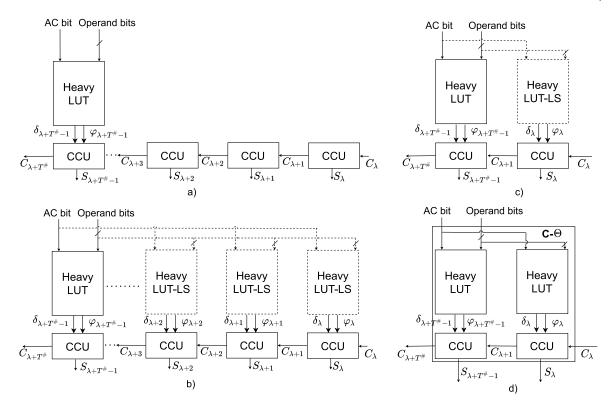

|         | 3.1.2   | Mé     | thodologie       |         |           |                                         |                                         |                                         | 32         |

|         | 3.1.3   | Syı    | nthèse Complèt   | e       |           |                                         |                                         |                                         | 32         |

|         | 3.1.4   | Dre    | oits d'Auteur .  |         |           |                                         |                                         |                                         | 35         |

| 3.2     | Long a  | abstr  | act              |         |           |                                         |                                         |                                         | 35         |

|         | 3.2.1   | Re     | search Context   |         |           |                                         |                                         |                                         | 35         |

|         | 3.2.2   | Me     | ethodology       |         |           |                                         |                                         |                                         | 35         |

|         | 3.2.3   | Co     | mprehensive Sy   | nthesi  | s         |                                         |                                         |                                         | 36         |

|         | 3.2.4   | Co     | pyright          |         |           |                                         |                                         |                                         | 38         |

| 3.3     | Article |        |                  |         |           |                                         |                                         |                                         | 39         |

| CI.     | 4 11    | ٠,.    | 4 11             | C       | EDC A     | 1 1                                     |                                         | . ,                                     |            |

| Cnapter |         |        | c methodolog     | -       |           |                                         | C                                       | 11                                      | <b>5</b> 0 |

|         | mul     | ltıplı | cation circuits. |         |           | • • • • • • • • • • • • • • • • • • • • | • • • • • • • • •                       |                                         |            |

| 4.1     | Résun   | né Lo  | ong              |         |           | • • • • • • • • • • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • • | • • • • • • • • • • • • • • • • • • • • | 53         |

|         | 4.1.1   | Co     | ntexte de la Rec | herch   | e         | • • • • • • • • • •                     |                                         | • • • • • • • • • • • • • • • • • • • • | 53         |

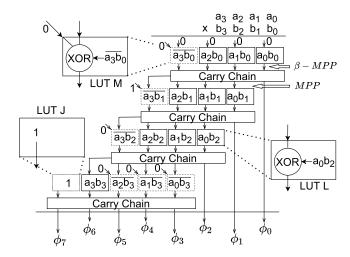

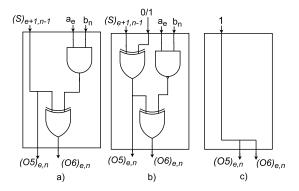

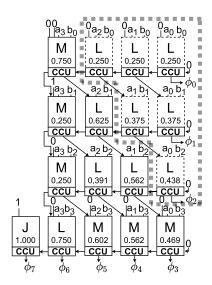

|         | 4.1.2   | Mé     | ethodologie      |         |           |                                         |                                         |                                         | 54         |

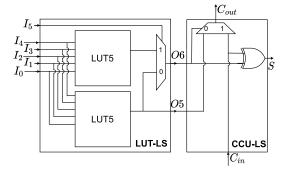

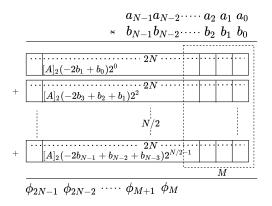

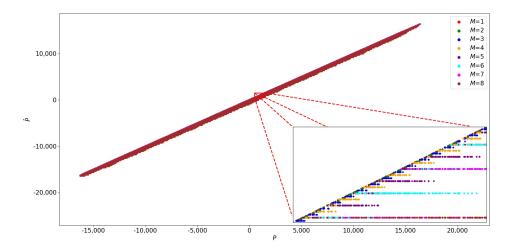

|         | 4.1.3   | Sy     | nthèse Complète  | e       |           |                                         |                                         |                                         | 55         |

|         | 4.1.4   | Dre    | oits d'Auteur .  |         |           |                                         |                                         |                                         | 58         |

| 12      | Long    | ahetr  | act              |         |           |                                         |                                         |                                         | 58         |

|         | 4.2.1       | Research Context                                                     | . 58  |

|---------|-------------|----------------------------------------------------------------------|-------|

|         | 4.2.2       | Methodology                                                          | . 58  |

|         | 4.2.3       | Comprehensive Synthesis                                              | . 59  |

|         | 4.2.4       | Copyright                                                            | . 63  |

| 4.3     | Article     |                                                                      | . 63  |

| Chapter | : 5 - Sysi  | tematic analysis of impact of approximate multiplication on wireless |       |

|         | sign        | al detection.                                                        | . 76  |

| 5.1     | Résum       | né Long                                                              | . 76  |

|         | 5.1.1       | Contexte de la Recherche                                             | . 76  |

|         | 5.1.2       | Méthodologie                                                         | . 77  |

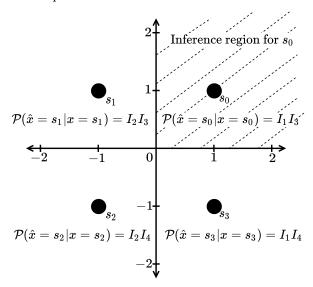

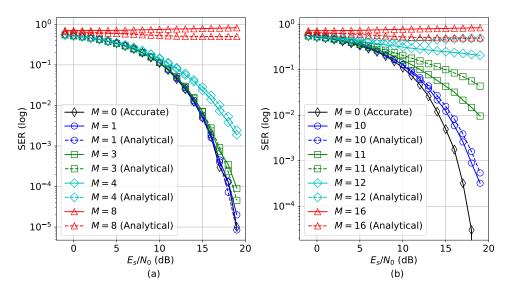

|         | 5.1.3       | Synthèse Complète                                                    | . 77  |

|         | 5.1.4       | Droits d'Auteur                                                      | . 79  |

| 5.2     | Long A      | Abstract                                                             | . 79  |

|         | 5.2.1       | Research Context                                                     | . 79  |

|         | 5.2.2       | Methodology                                                          | . 80  |

|         | 5.2.3       | Comprehensive Synthesis                                              | . 81  |

|         | 5.2.4       | Copyright                                                            | . 82  |

| 5.3     | Article     |                                                                      | . 82  |

| Chapter | : 6 - Con   | cluding Remarks                                                      | . 103 |

| 6.1     | Genera      | al Discussion                                                        | . 103 |

| 6.2     | Conclu      | usion                                                                | . 104 |

| 6.3     | Future      | Work                                                                 | . 105 |

| Chapter | · A - Titro | e de l'annexe A                                                      | 114   |

| Chapter B - Titre de l'annexe B | <br>118 |

|---------------------------------|---------|

# List of figures

| Figure 1.1 | Major KPI improvement projected with 6G in comparison with 5G |    |

|------------|---------------------------------------------------------------|----|

|            | [1]                                                           | 2  |

| Figure 1.2 | MIMO uplink signal detection with BS and User Equipment (UE)s |    |

|            | with single antenna and channel matrix <b>H</b> .             | 3  |

| Figure 1.3 | Research Methodology                                          | 15 |

# List of tables

| Table 1-1 | 6G enabling technologies.                                   | 3  |

|-----------|-------------------------------------------------------------|----|

| Table 2-1 | D-MIMO detection techniques.                                | 22 |

| Table 2-2 | FPGA based techniques for approximate signed multiplication | 26 |

| Table 2-3 | Approximate Computing Techniques for B5G                    | 29 |

| Table 3-1 | Comparaison des topologies en Anneau et en Étoile DN        | 34 |

| Table 3-2 | Comparison of DN Ring and DN Star.                          | 38 |

| Table 4-1 | Performances des circuits de multiplication LC              | 57 |

| Table 4-2 | Performance of LC multiplication circuits                   | 62 |

| Table 5-1 | Analyse Systématique.                                       | 79 |

| Table 5-2 | Systematic Analysis.                                        | 82 |

# List of acronyms

**3GPP** 3rd Generation Partnership Project. 32, 33, 36

**ADMM** Alternating Direction Method of Multipliers. 18, 22

ADMM-GS ADMM with Gauss-Seidel iteration. 18

AMN Approximate Multiplication Noise. iv, vi, vii, 13, 103, 105, 114, 116

ANRR Average Normalized Resiliency Ratio. 78, 79, 81, 82

**ASIC** Application Specific Integrated Circuit. 53, 58, 103

**AWGN** Additive White Gaussian Noise. iv, vii, 22, 32, 36

**B5G** Beyond 5G. iv, vi, vii

**BER** Bit Error Rate. 28, 30, 76, 79, 114

**BS** Base Station. iv, vi, vii, xiii, 3, 6–9, 12, 19–22, 28, 31, 32, 35, 36, 103

**BW** Baugh Wooley. iv, vii, 12, 54–56, 59, 60, 105

CC Carry Chain. 24–26

CCU Carry Chain Unit. 24, 26

**CDMA** Code Divison Multiple Access. 1

**CPD** Critical Path Delay. 55, 60

**CSI** Channel State Information. 31, 35, 105

**D-MIMO** Decentralized MIMO. iii, iv, vi, vii, 9, 20, 21, 105

**DCD** Decentralized Coordinate Descent. 18, 33, 34, 36–38

DCG Decentralized Conjugate Gradient. 19, 22

**DN** Decentralized Newton. iv, vii, xiv, 12, 22, 32–38, 103, 105

**EE** Energy Efficiency. iii, v-vii, 2, 6–11, 13, 22, 25, 27, 29, 32, 36, 53, 58, 76, 78, 79,

81, 104, 106

**EP** Expectation Propagation. 19, 21–23, 28, 30, 32, 33, 36

**FEC** Forward Error Correction. 27, 29

FER Frame Error Rate. 76, 79, 114

**FF** Flip Flop. 33, 36

**FFT** Fast Fourier Transform. 27–29

**FIR** Finite Impulse Response. 28, 30

**FPGA** Field Programmable Gate Array. iii, iv, vi, vii, x, xiv, 10, 12–16, 18, 22, 24–26, 32, 33, 36, 37, 53, 54, 58, 103–105

**GPRS** General Packet Radio Service. 1

**GPU** Graphics Processing Unit. 33, 34, 36–38

**GSM** Global System for Mobile. 1

**IRS** Intelligent Reflecting Surfaces. 106

**KPI** Key Performance Indicator. iv, vii, xiii, 2, 11, 13, 27, 34, 37, 38, 57, 62, 104

LAMA Large-MIMO Approximate Message Passing. 19, 22, 33, 36, 37

LC Logic Cloning. iv, vii, xiv, 12, 26, 54–60, 62, 103, 105

LLR Log Likelihood Ratio. 22, 28, 32, 36

**LSSI** Laboratory of Signal and System Integration. 15, 16

**LUT** Look-Up Table. iv, vii, 12, 24–26, 33, 36, 54–56, 59, 60

MAC Multiply And Accumulate. 25, 26

**MAP** Maximum A Posteriori. 19, 103

**MED** Mean Error Distance. 55, 59, 60

MF Matched Filter. 115

**MIMO** Multiple Input Multiple Output. iii–vii, ix, x, xiii, xiv, 3, 6, 8–15, 18–24, 28, 31, 32, 35, 36, 54, 56, 59–61, 103–106, 114

ML Machine Learning. 4, 20, 25, 27, 106

MMSE Minimum Mean Square Error. 13, 18, 19, 31, 35, 77, 80, 105

MRED Mean Relative Error Distance. 55, 59, 60

MSE Mean Square Error. 114, 117

NMED Normalized Mean Error Distance. 55, 59, 60

NRR Normalized Resiliency Ratio. 78, 79, 81, 82

**OTFS** Orthogonal Time Frequency Space. 20, 23

PDP Power Delay Product. iv, vii, 54, 55, 59, 60

**PP** Partial Product. 24–26

QAM Quadrature Amplitude Modulation. 28–30, 32, 36, 56, 61

**QoS** Quality of Service. iii, iv, vi, vii, 8–11, 14, 29, 76, 79, 82, 104, 114

**QPSK** Quadrature Phase Shift Keying. 13, 77, 80, 105

**RRC** Root Raised Cosine. 28, 30

SC Successive Cancellation. 27, 29

**SCMA** Sparse Code Multiple Access. 28, 30

**SER** Symbol Error Rate. iv, vii, 12, 19, 27, 32, 34, 36, 37, 56, 60, 76–82, 103, 114

SGD Stochastic Gradient Descent. 19, 22

**SISO** Single Input Single Output. iv, vii, 14, 15, 28, 104, 114

**SNR** Signal-to-Noise Ratio. v, vii, 12, 19, 22, 28, 30, 77–79, 81, 82

**TM** Truncated Multiplication. 13, 77, 80, 105, 117

TP Truth Probability. 54, 59, 103

**UE** User Equipment. xiii, 3, 6, 18, 19, 21, 22, 28, 31, 32, 35, 36

**UQTR** Université du Québec à Trois-Rivières. 16

VAR Virtual and Augmented Reality. 1, 2

XL-MIMO Extremely Large MIMO. vi, 6, 10, 15, 18

**ZF** Zero Forcing. iv, vii, 12, 14, 31, 32, 34–37, 54, 56, 59–61, 105

# **Chapter 1 - Introduction**

## 1.1 Background

Wireless communication systems have undergone revolutionary advancements since inception, driven primarily by the escalating demands for higher data rates in evolving applications. Consequently, various wireless standards have evolved to meet the required data rates of these diverse application needs [1,2]. Initially, 1G and 2G were characterized by Global System for Mobile (GSM), which facilitated communication at speeds of up to 30-35 Kbps. This was later enhanced with General Packet Radio Service (GPRS), achieving data rates of up to 110 Kbps. The advent of 3G significantly increased speeds up to 2 Mbps, enabling smartphones to handle faster communication, transfer enormous data, reduced latency, and incorporate enhanced security features. Code Divison Multiple Access (CDMA) technology in 3G facilitated communication across multiple channels simultaneously, thereby enhancing network speed and connectivity. Subsequently, 4G was introduced to elevate data rates up to 100 Mbps. It entailed a complete overhaul and simplification of the 3G architecture, resulting in substantial reductions in transfer latency, and enhancing overall network efficiency and speed. The 5G standard has evolved to provide peak speeds of up to 10 Gbps, latency as nearing 1 millisecond, improved security, extensive coverage, and increased user handling capacity.

As societal communication data needs continue to grow, communication capabilities must be able to keep pace with them. Future communication standards need to support applications such as extended Virtual and Augmented Reality (VAR), multi-sensory holographic teleportation, real-time remote healthcare, autonomous cyber-physical systems, industrial automation, and precision agriculture. Some of these applications cannot be adequately supported by the 5G standard. For instance, next-generation

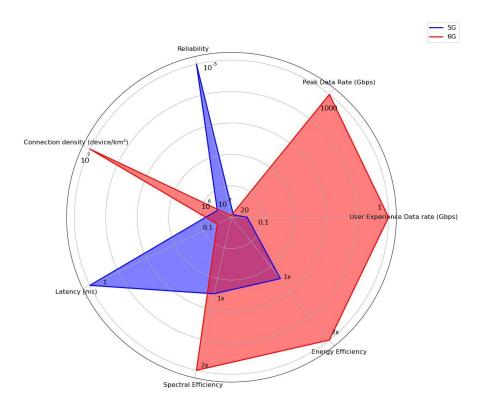

Figure 1.1 Major KPI improvement projected with 6G in comparison with 5G [1].

applications like extended VAR and holographic teleportation require data rates in Tbps range and latency below microsecond level, capabilities that exceed those specified in the frequency bands being utilized for 5G. Increasing industrial automation and the transition towards Industry 4.0 will significantly raise connectivity density, surpassing the servicing capability of 1 million devices per km² that 5G was designed to handle. Heightened connection density will drive demands for improved EE, an aspect that 5G was not specifically designed to address. This has led to the emergence of a new set of requirements and KPIs for evolving B5G communication standards as shown in Figure. 1.1. Spectral and energy efficiency is doubled for 6G, while user data rate and peak data rate is increased by  $10\times$  and  $50\times$  respectively. Latency is reduced by  $10\times$ , while connection density is increased by  $10\times$ . Reliability is increased by about  $100\times$ .

For B5G, the development of 6G standard encompasses advancements in three key areas: spectrum, protocol, and infrastructure [1–3] as shown in Table. 1.1. At the spectrum level, incorporation of higher frequency bands is being researched to expand available bandwidth. Protocol level enhancements aim to optimize data packet organization and transmission methodologies. At the infrastructure level, efficient hardware implementation techniques are crucial for realizing B5G networks. A particular focus is placed on reducing energy consumption to improve the overall scalability and environmental sustainability [4].

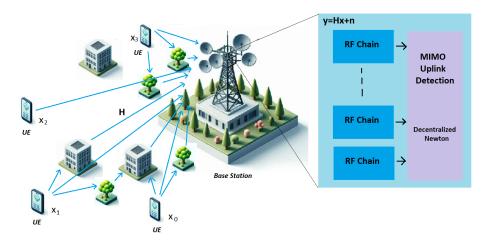

Figure 1.2 MIMO uplink signal detection with BS and UEs with single antenna and channel matrix **H**.

Table 1-1 6G enabling technologies.

| Technology     | Features                      | Benefits                      |  |  |  |  |

|----------------|-------------------------------|-------------------------------|--|--|--|--|

|                | Spectrum Level Enablers       |                               |  |  |  |  |

| Terahertz      | Uses frequencies above 100    | Enables ultra high speed data |  |  |  |  |

| Communications | GHz in THz range for wider    | transmission suitable for     |  |  |  |  |

|                | bandwidths and higher data    | future applications like      |  |  |  |  |

|                | rates.                        | virtual reality and high      |  |  |  |  |

|                |                               | definition streaming.         |  |  |  |  |

| Visible Light  | Uses visible light spectrum   | Offers high speed and energy  |  |  |  |  |

| Communication  | for data transmission,        | efficient communication with  |  |  |  |  |

|                | integrating with illumination | minimal interference, ideal   |  |  |  |  |

|                | systems.                      | for indoor applications.      |  |  |  |  |

| Technology        | Features                       | Benefits                        |

|-------------------|--------------------------------|---------------------------------|

| Dynamic Spectrum  | Allows flexible allocation of  | Optimizes spectrum usage        |

| Sharing           | spectrum resources among       | and increases network           |

|                   | different operators and        | capacity.                       |

|                   | services.                      |                                 |

| Cognitive Radio   | Utilizes spectrum sensing      | Enhances spectrum               |

|                   | and interference management    | efficiency by dynamically       |

|                   | techniques.                    | sharing resources.              |

| Free Space Optics | Uses light propagation in free | Offers high data rates, low     |

|                   | space for high capacity,       | latency, and immunity to        |

|                   | point-to-point                 | electromagnetic interference.   |

|                   | communication links.           |                                 |

|                   | Protocol Level Enablers        |                                 |

| Machine Learning  | Application of Machine         | Improves network                |

|                   | Learning (ML) algorithms       | performance, reduces            |

|                   | for intelligent and adaptive   | latency, and supports           |

|                   | communication                  | dynamic network                 |

|                   | configuration.                 | management.                     |

| Orbital Angular   | Utilizes helical phase         | Increases channel capacity      |

| Momentum          | wavefronts for wireless        | and spectrum efficiency.        |

|                   | modulation, enabling           |                                 |

|                   | multiplexing with              |                                 |

|                   | perpendicular orbital angular  |                                 |

|                   | momentum modes.                |                                 |

| Full Duplex       | Enables simultaneous signal    | Increases spectral efficiency,  |

| Communication     | transmission and reception.    | bolsters network capacity,      |

|                   |                                | and supports real time          |

|                   |                                | bidirectional communication.    |

| Non Orthogonal    | Allows multiple users to       | Improves user connectivity      |

| Multiple Access   | share the same resources       | and spectral efficiency.        |

|                   | through power and code         |                                 |

|                   | domain assignments.            |                                 |

| Network Slicing   | Provides customized virtual    | Optimizes resource              |

|                   | networks on a shared           | allocation, and supports        |

|                   | physical infrastructure.       | diverse application             |

|                   |                                | requirements.                   |

| Blockchain        | Implements decentralized       | Enhances network resilience,    |

|                   | security mechanisms for        | protects against cyber threats, |

|                   | authentication and data        | and ensures trustworthiness     |

|                   | integrity.                     | in communication.               |

| Technology                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Features                      | Benefits                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------------------|

| Proactive Caching                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Caching of frequent utilized  | Reduces latency by reduced     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | content.                      | access delay and efficient     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               | traffic offloading.            |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Infrastructure Level Enabl    | ers                            |

| Edge Intelligence                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Integrates ML algorithms at   | Reduces latency and power      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | the network edge for real     | consumption. Supports          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | time data analytics and       | autonomous applications in     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | decision making.              | distributed environments.      |

| Holographic Radio                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Creates a continuous          | Enables ultra-high density     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | electromagnetic aperture      | and resolution spatial         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | using electromagnetic wave    | multiplexing, facilitating     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | interference, akin to optical | accurate electromagnetic       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | holography.                   | field reconstruction.          |

| Wireless Energy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Enables wireless charging     | Enhances device autonomy,      |

| Transfer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | and power delivery to IoT     | reduces maintenance costs,     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | devices and sensors.          | and supports sustainable       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                               | network operations.            |

| Satellite Networks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Integrates satellite          | Extends network reach,         |

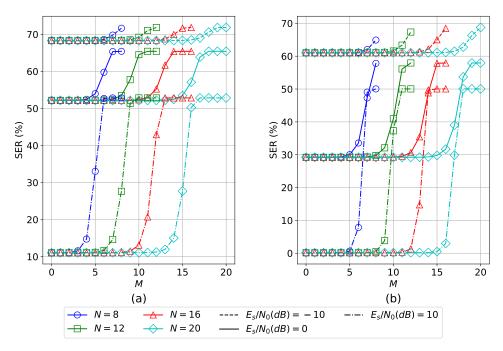

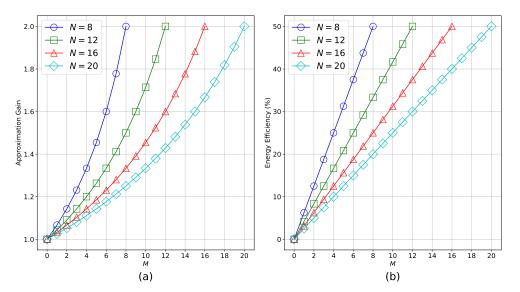

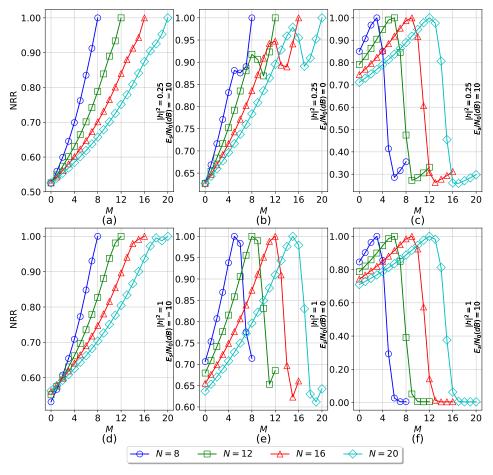

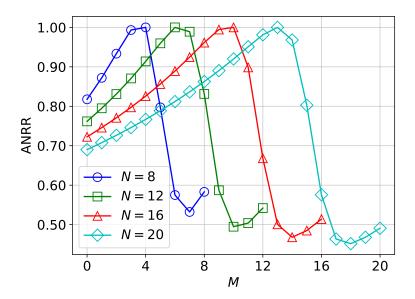

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | communication systems for     | supports remote and rural      |