UNIVERSITÉ DU QUÉBEC

MÉMOIRE PRÉSENTÉ À

L'UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

COMME EXIGENCE PARTIELLE

DE LA MAÎTRISE EN GÉNIE ÉLECTRIQUE

PAR

KHALED ATOUB

OPTIMISATION DE LA FFT À VIRGULE FIXE BASÉE SUR LES ALGORITHMES

GÉNÉTIQUES

NOVEMBRE 2013

Université du Québec à Trois-Rivières

Service de la bibliothèque

Avertissement

L'auteur de ce mémoire ou de cette thèse a autorisé l'Université du Québec à Trois-Rivières à diffuser, à des fins non lucratives, une copie de son mémoire ou de sa thèse.

Cette diffusion n'entraîne pas une renonciation de la part de l'auteur à ses droits de propriété intellectuelle, incluant le droit d'auteur, sur ce mémoire ou cette thèse. Notamment, la reproduction ou la publication de la totalité ou d'une partie importante de ce mémoire ou de cette thèse requiert son autorisation.

## RÉSUMÉ

---

---

## RÉSUMÉ

---

Aujourd’hui l’arrivée de la 4<sup>ème</sup> génération représentée, entre autres, par les réseaux LTE à améliorer le monde de la télécommunication mobile grâce à l’incorporation des techniques OFDM et le MIMO-OFDM. La modulation multiporteuse OFDM consiste à répartir les informations à transmettre sur un grand nombre de porteuses orthogonales, individuellement modulées à débit réduit. L’implémentation de cette modulation est basée sur le principe d’orthogonalité assurée par la transformée rapide de Fourier (FFT – *Fast Fourier Transform*) pour la génération des sous-porteuses. L’exécution en arithmétique à virgule fixe des IFFT/FFT se traduit par la présence de sources de bruits. Ces derniers se propagent au sein du système et provoquent une dégradation de la précision mathématique en sortie du système. Ainsi, il est nécessaire de maîtriser la dégradation de la précision afin de garantir l’intégrité de l’algorithme et les performances du système.

Ce mémoire, présente l’étude de quantification en virgule fixe de l’IFFT/FFT en se basant sur une architecture matérielle de type pipeline radix-4 MDC (*Multi-path Delay Commutator*). Nous présentons une méthode d’optimisation en virgule fixe, basée sur les

## RÉSUMÉ

---

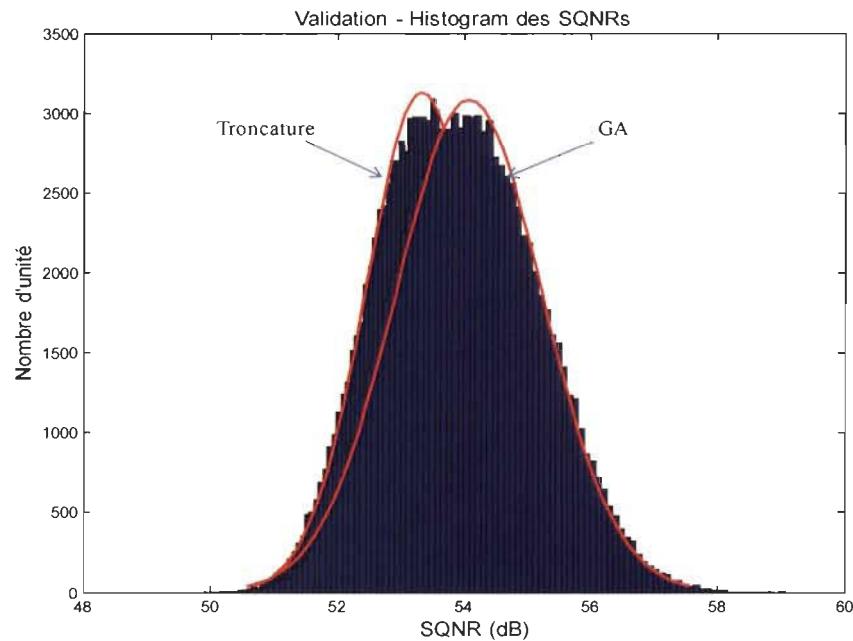

algorithmes génétiques (AG), afin de calculer les coefficients FFT tout en minimisant les erreurs de quantifications. La précision de l'implémentation est évaluée en déterminant l'expression du Rapport Signal à Bruit de Quantification (SQNR : *Signal-to-Quantisation-Noise Ratio*). Une étude de comparaison a été faite entre la méthode qui consiste à simplement tronquer les coefficients de Fourier et celle basée sur les AG. Les résultats obtenus montrent que pour une même largeur binaire des coefficients de Fourier, notre méthode d'optimisation à base des algorithmes génétiques présente un gain en moyenne de 1.5 dB comparativement à la troncature des coefficients de Fourier et cela sans aucun coût matériel supplémentaire.

Nous présentons dans ce travail aussi l'évaluation de la FFT radix-4 MDC sur FPGA afin de montrer le gain en SQNR obtenu ainsi que la consommation en puissance et ressources matérielles utilisées.

---

## REMERCIEMENT

---

Je tiens à exprimer mes plus vifs remerciements à Dieu le tout puissant pour la volonté, la santé, et la patience qu'il m'a donné toutes ces longues années d'études, que nous puissions arriver là.

Je tiens à exprimer ma profonde reconnaissance et ma gratitude à mon professeur, M Daniel Massicotte pour m'avoir encadré, son orientation et ses précieux conseils durant l'élaboration de ce travail, aussi aux membres de jury pour avoir accepté de juger mon travail.

A mes deux êtres les plus chers au monde Ma chère mère et mon cher père

A toute mes sœurs et mes frères pour leurs sincère aide morale

A toute ma famille sans exception

A tous mes collègues et amis. A tous ceux qui avec de chaleur et d'amour se sont dévoués pour ma réussite et mon bonheur, je dédie ce travail.

## TABLE DES MATIÈRES

---

---

## TABLE DES MATIÈRES

---

|                              |       |

|------------------------------|-------|

| RÉSUMÉ .....                 | II    |

| REMERCIEMENT .....           | IV    |

| TABLE DES MATIÈRES.....      | V     |

| LISTES DES FIGURES .....     | XI    |

| LISTE DES TABLEAUX .....     | XVI   |

| LISTE DES ABRÉVIATIONS ..... | XVIII |

| CHAPITRE I.....              | 1     |

| INTRODUCTION .....           | 1     |

---

## TABLE DES MATIÈRES

---

|                                                                            |           |

|----------------------------------------------------------------------------|-----------|

| <b>I.1. Problématique liée au sujet de recherche .....</b>                 | <b>5</b>  |

| <b>I.2. Objectifs du sujet de recherche .....</b>                          | <b>7</b>  |

| <b>I.3. Méthodologie du sujet de recherche.....</b>                        | <b>8</b>  |

| <b>I.4. Organisation de mémoire.....</b>                                   | <b>9</b>  |

| <b>CHAPITRE II .....</b>                                                   | <b>11</b> |

| <b>FFT QUANTIFIÉES AU RÉCEPTEUR AU OFDM.....</b>                           | <b>11</b> |

| <b>II.1. Les systèmes multi-porteurs OFDM.....</b>                         | <b>12</b> |

| II.1.1. Historique – Principe .....                                        | 12        |

| II.1.2. Modélisation des systèmes OFDM.....                                | 14        |

| II.1.2.1. Modulations OFDM.....                                            | 15        |

| II.1.2.2. Orthogonalités.....                                              | 17        |

| II.1.3. La FFT dans les communications OFDM .....                          | 19        |

| II.1.3.1 Implémentation numérique de la Modulation/Démodulation OFDM ..... | 19        |

| II.1.3.2. Quelques standards OFDM à base FFT .....                         | 21        |

| II.1.2. Avantages et inconvénients de l'OFDM .....                         | 22        |

| <b>II.2. Algorithme FFT et l'effet de quantification.....</b>              | <b>24</b> |

| II.2.1 La Transformée de Fourier Discrète.....                             | 24        |

---

## TABLE DES MATIÈRES

---

|                                                                                                         |           |

|---------------------------------------------------------------------------------------------------------|-----------|

| II.2.2. La Transformée Rapide de Fourier.....                                                           | 28        |

| II.2.3. Approche diviser-pour-régner .....                                                              | 29        |

| <b>II.3. Architecture pipeline pour le calcul de la FFT .....</b>                                       | <b>32</b> |

| II.3.1. Classification des algorithmes FFT .....                                                        | 33        |

| II.3.2. Papillon radix-r FFT .....                                                                      | 34        |

| II.3.3. Architecture pipeline radix-r FFT .....                                                         | 35        |

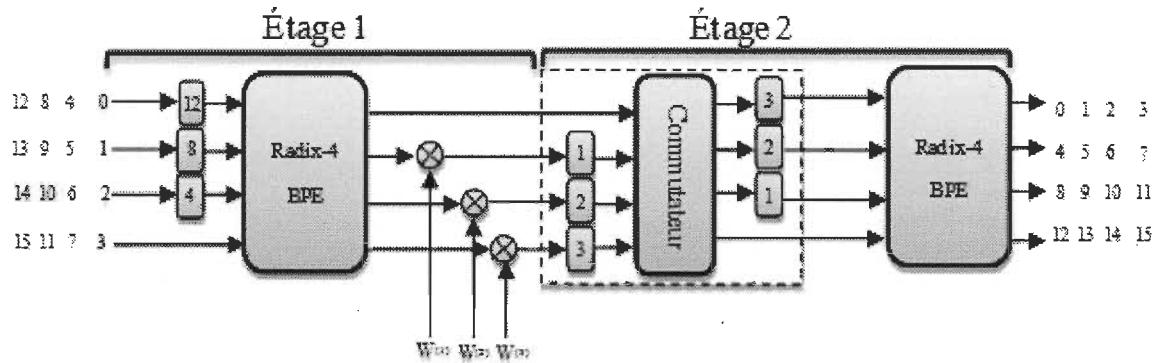

| II.3.4. Algorithme FFT radix-4 MDC .....                                                                | 38        |

| II.3.4.1. Algorithme radix-4 DIT .....                                                                  | 38        |

| II.3.4.2. Algorithme radix-4 DIF .....                                                                  | 41        |

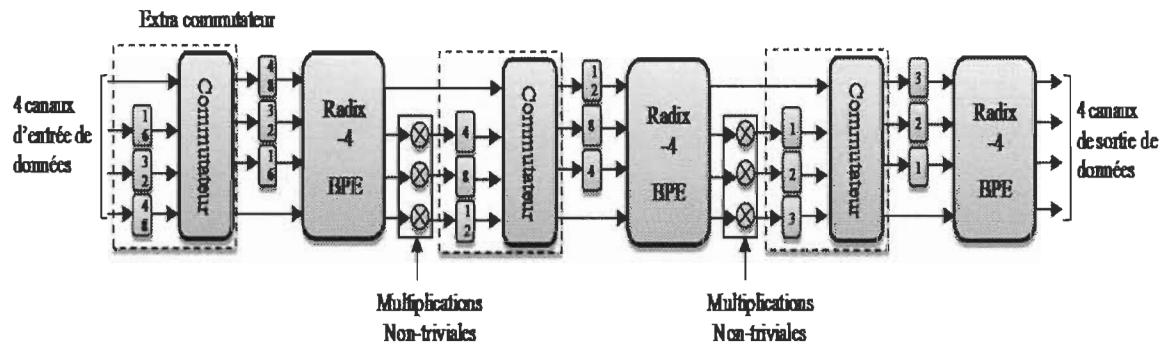

| II.3.4.2. Architecture pipeline radix-4MDC .....                                                        | 44        |

| <b>II.4. Effet de quantification.....</b>                                                               | <b>45</b> |

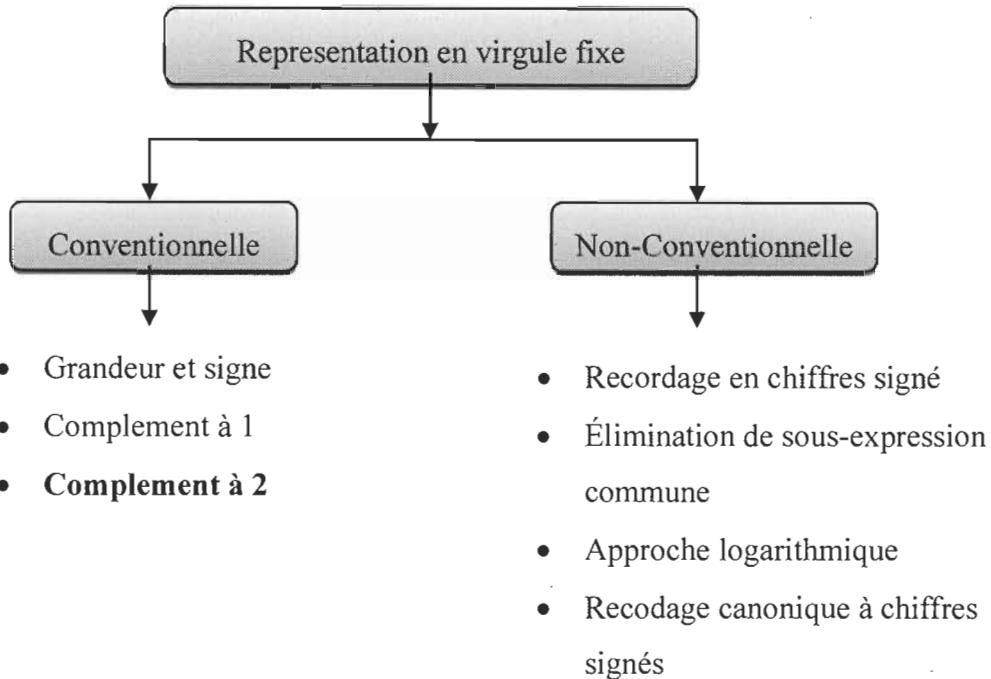

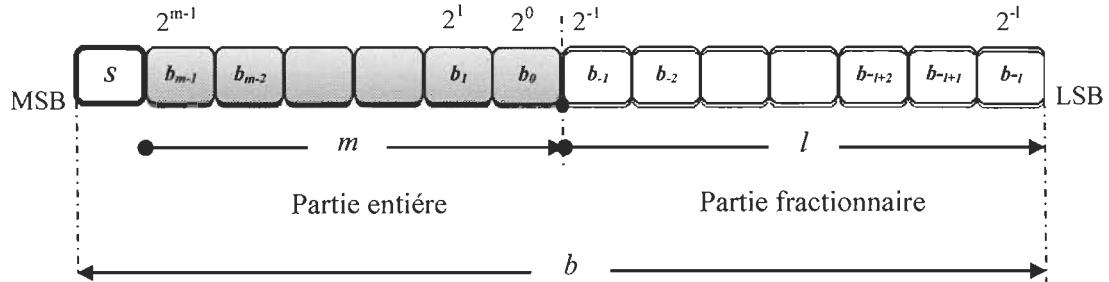

| II.4.1. Arithmétique en virgule fixe conventionnelle .....                                              | 47        |

| II.4.1.1. Représentation des nombres .....                                                              | 47        |

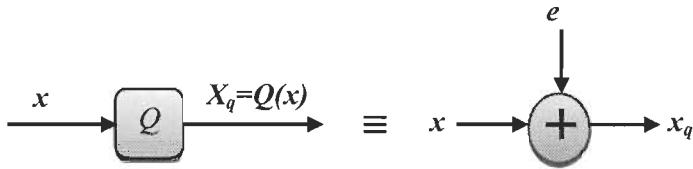

| II.4.1.2. Erreur de quantification .....                                                                | 49        |

| <b>CHAPITRE III .....</b>                                                                               | <b>52</b> |

| <b>ALGORITHME GÉNÉTIQUE POUR L'OPTIMISATION DE LA FFT .....</b>                                         | <b>52</b> |

| <b>III.1. Algorithme génétique pour l'optimisation en virgule fixe des coefficients de la FFT .....</b> | <b>53</b> |

---

## TABLE DES MATIÈRES

---

|                                                                                         |           |

|-----------------------------------------------------------------------------------------|-----------|

| <b>III.2. Algorithme génétique et stratégie d'évolution .....</b>                       | <b>54</b> |

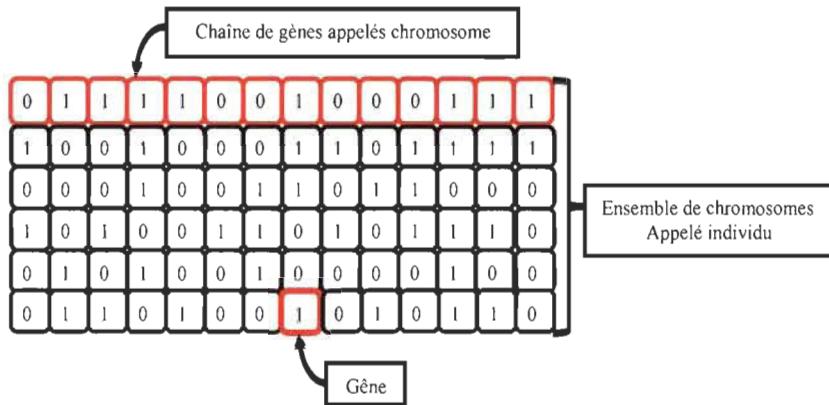

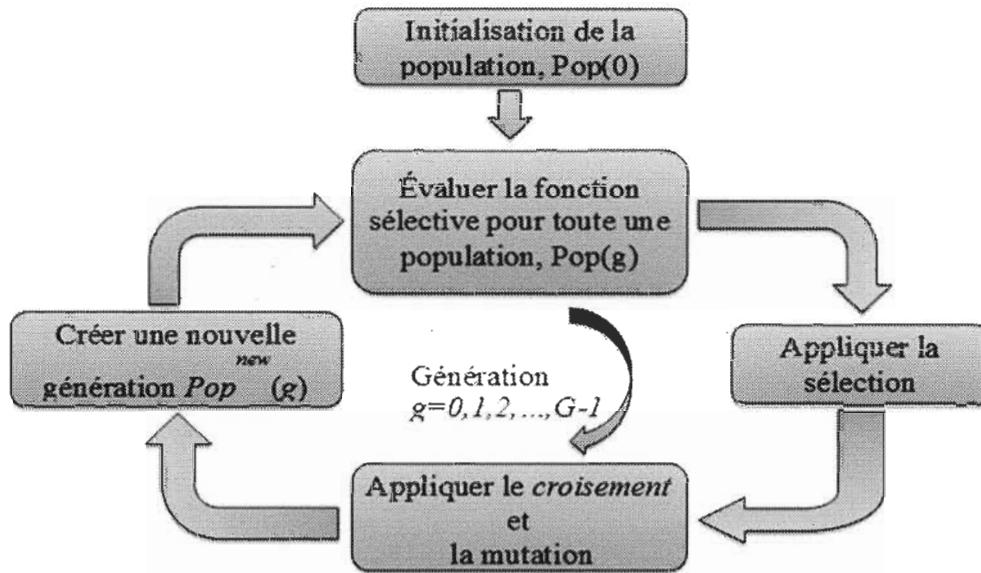

| III.2.1. Présentation des algorithmes génétiques.....                                   | 54        |

| III.2.2. Principe de base des AG .....                                                  | 56        |

| <b>III.3. Algorithme génétique pour l'optimisation des coefficients de la FFT .....</b> | <b>58</b> |

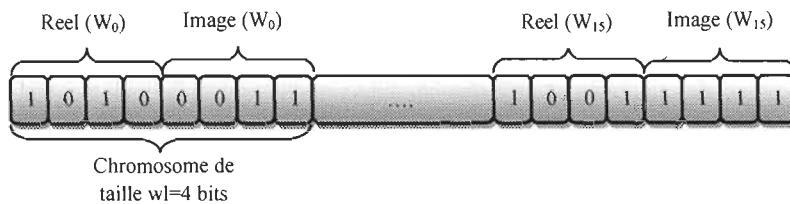

| III.3.1. Génération de la population initiale .....                                     | 58        |

| III.3.2. La phase d'évaluation .....                                                    | 60        |

| III.3.3. La reproduction .....                                                          | 61        |

| III.3.4. Sélection.....                                                                 | 61        |

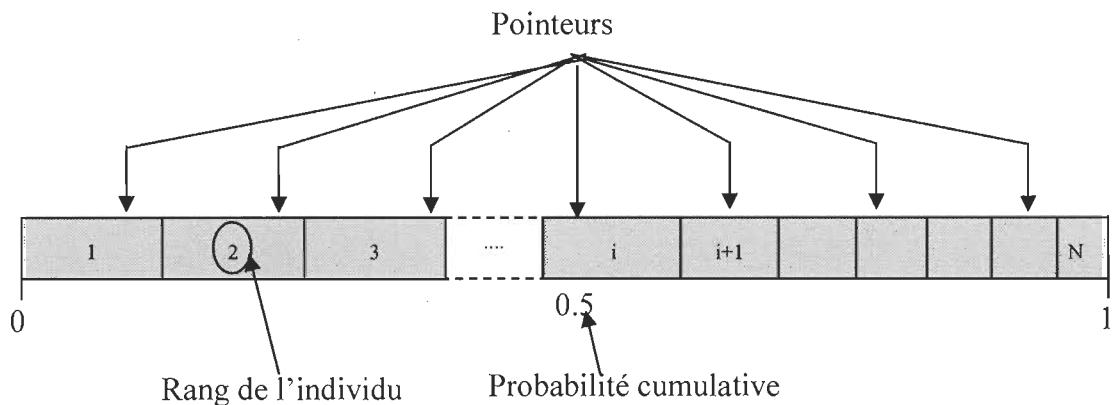

| III.3.4.1. Sélection par échantillonnage stochastique universel .....                   | 62        |

| III.3.4.2. Variante linéaire .....                                                      | 64        |

| III.3.4.2. Variante non linéaire .....                                                  | 64        |

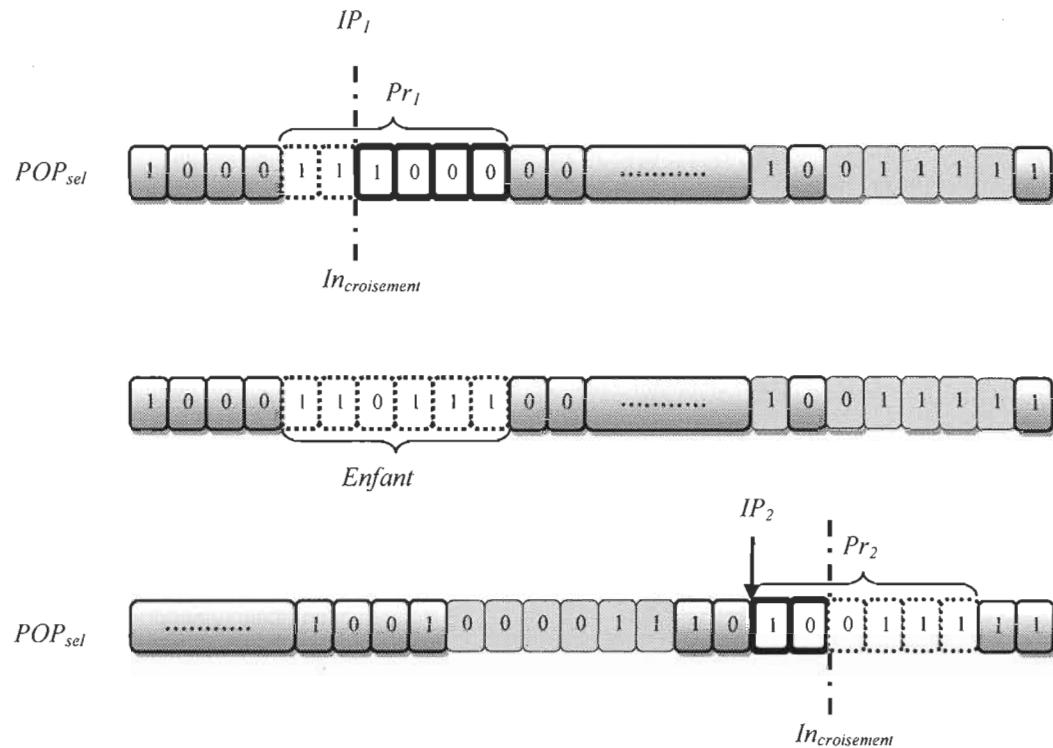

| III.3.5. Croisements (Recombinaison) .....                                              | 65        |

| III.3.6. Mutation .....                                                                 | 67        |

| III.3.7. Critère d'arrêt.....                                                           | 68        |

| III.3.8 Réglage des paramètres des AG.....                                              | 68        |

| <b>III.4. résultats des coefficients de Fourier optimisés en virgule fixe.....</b>      | <b>69</b> |

| III.4.1. Métrique pour évaluer la qualité d'optimisation.....                           | 69        |

| III.4.2. Initialisation des paramètres et conditions de simulation .....                | 71        |

| III.4.3. Optimisation des coefficients FFT .....                                        | 72        |

---

---

## TABLE DES MATIÈRES

---

|                                                                                    |            |

|------------------------------------------------------------------------------------|------------|

| III.4.4. Étude de comparaison de SQNR.....                                         | 78         |

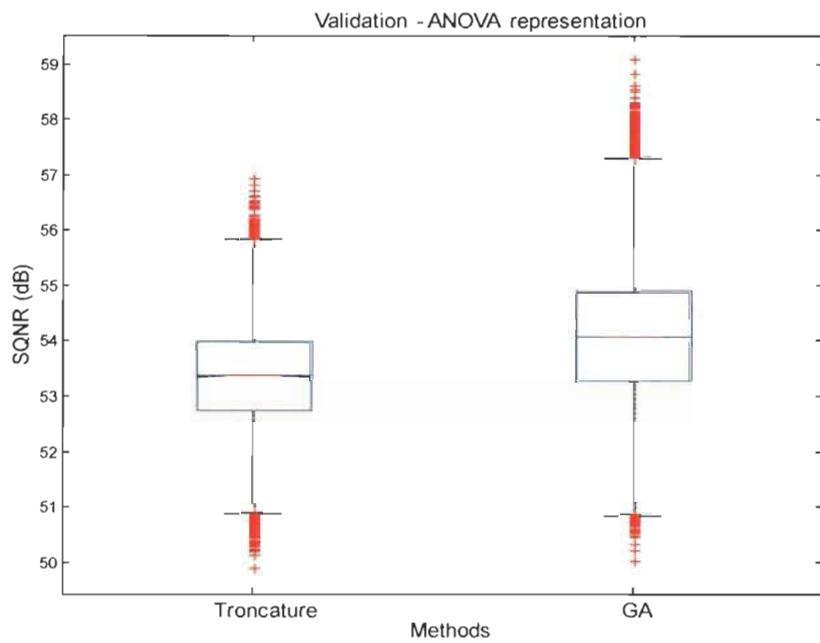

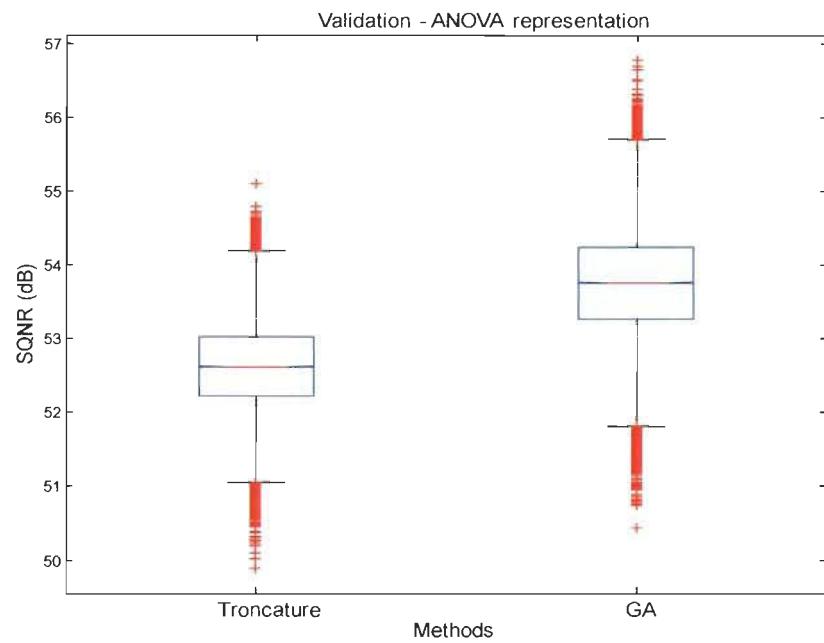

| <b>III.5. Analyse de variance des SQNR.....</b>                                    | <b>82</b>  |

| <b>III.6. Algorithme génétique à objectif multiple .....</b>                       | <b>87</b>  |

| <b>3.7. Conclusion.....</b>                                                        | <b>88</b>  |

| <b>CHAPITRE IV .....</b>                                                           | <b>89</b>  |

| <b>IMPLEMENTATION D'UNE FFT RADIX-4 MDC À 16 POINTS .....</b>                      | <b>89</b>  |

| <b>IV.1. La consommation en puissance dans les circuits FPGA.....</b>              | <b>90</b>  |

| <b>IV.2. Processus d'estimation de puissance de la FFT radix-4 .....</b>           | <b>91</b>  |

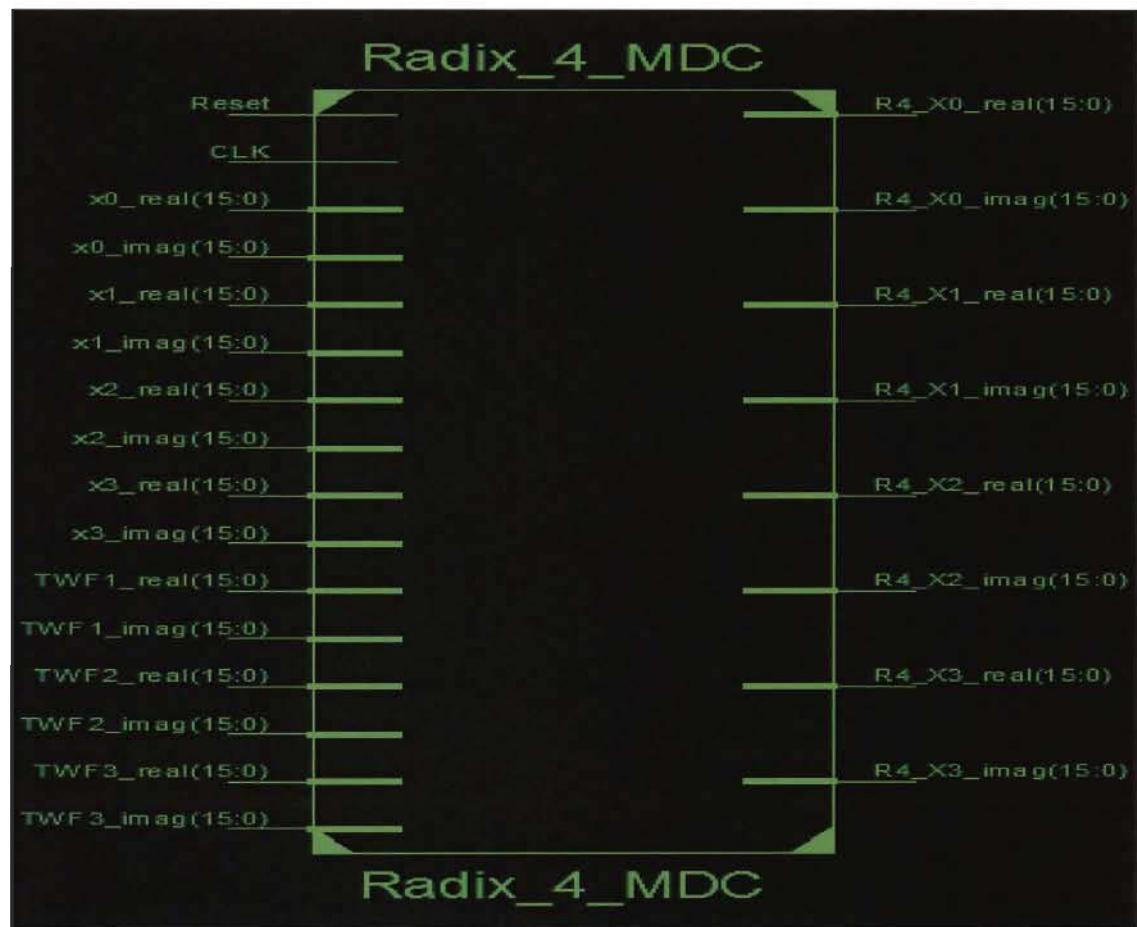

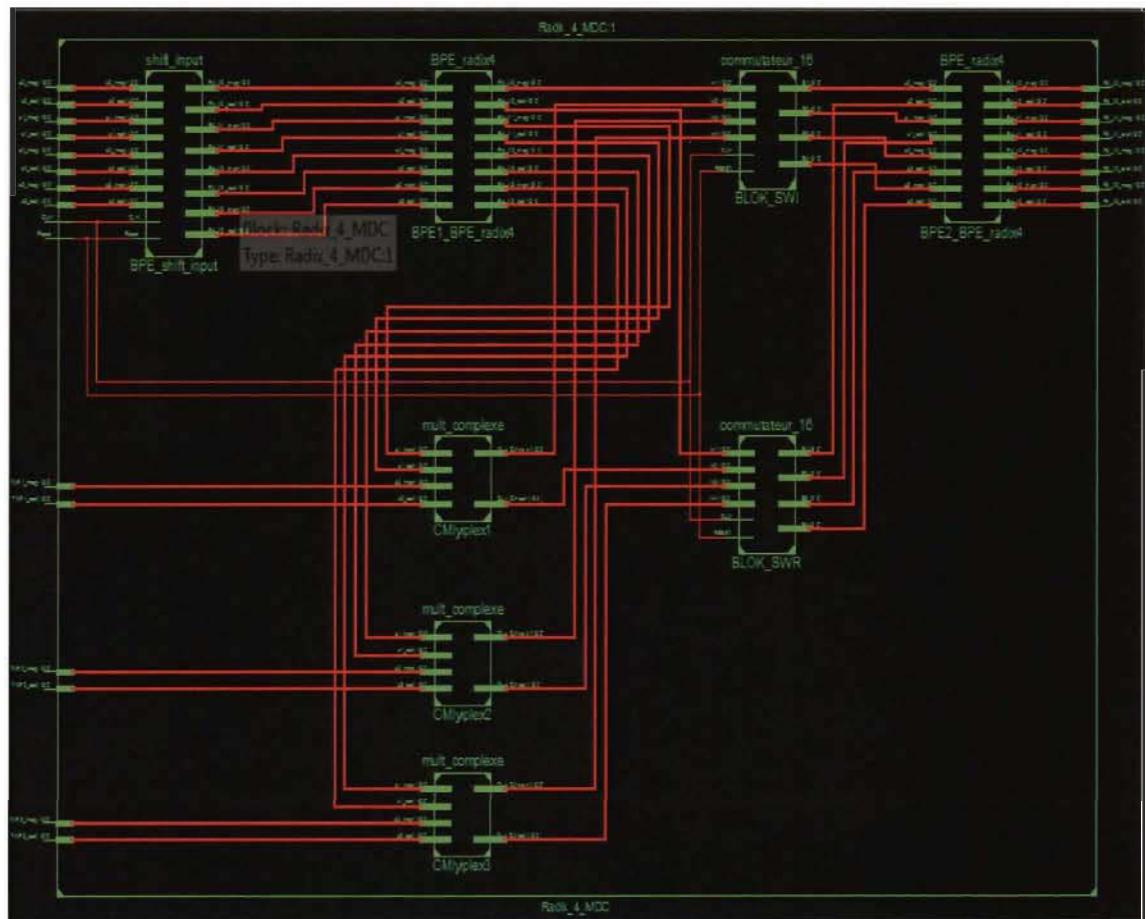

| <b>IV.3. Conception et architecture pipeline radix-4 FFT.....</b>                  | <b>95</b>  |

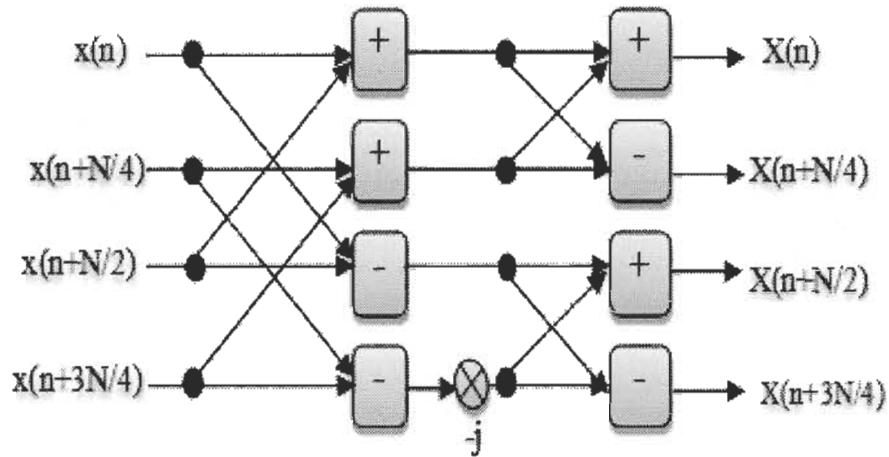

| IV.3.1. BPE radix-4 FFT.....                                                       | 98         |

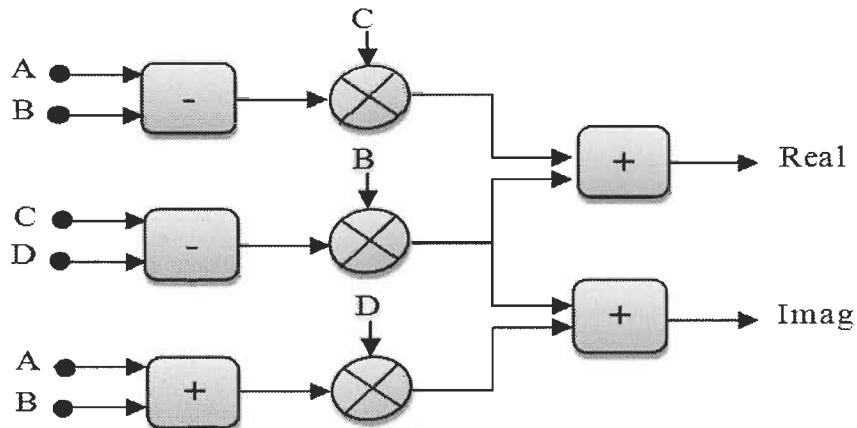

| IV.3.2. Multiplication complexes.....                                              | 99         |

| IV.3.3. Le commutateur .....                                                       | 100        |

| IV.3.4 Evaluation de SQNR de l'architecture pipeline radix-4 MDC à 16 points ..... | 101        |

| <b>IV.4 Implémentation FPGA et analyse des résultats .....</b>                     | <b>103</b> |

| IV.4.1 Résultats de synthèses de radix-4 FFT à 16 points.....                      | 103        |

## TABLE DES MATIÈRES

---

|                                                                                   |     |

|-----------------------------------------------------------------------------------|-----|

| IV.4.2 Représentation schématique au niveau RTL de Processeur FFT R4MDC           | 106 |

| IV.5. Analyse de résultats de consommation en puissance de radix-4 MDC à 16 point | 109 |

| CHAPITRE V                                                                        | 111 |

| CONCLUSION                                                                        | 111 |

| BIBLIOGRAPHIES                                                                    | 114 |

## LISTE DES FIGURES

---

## LISTES DES FIGURES

---

|                                                                                                           |    |

|-----------------------------------------------------------------------------------------------------------|----|

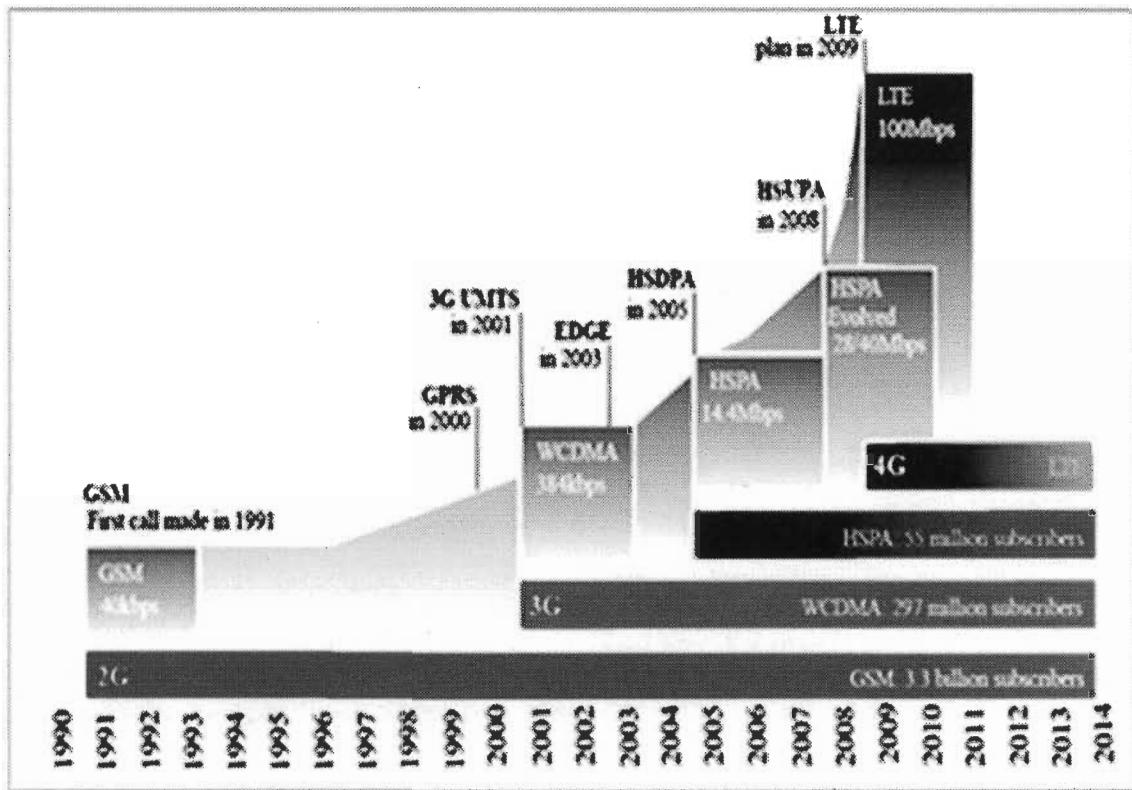

| FIGURE 1.1: ÉVOLUTION DU MONDE DES TECHNOLOGIES SANS FIL [LER09] .....                                    | 3  |

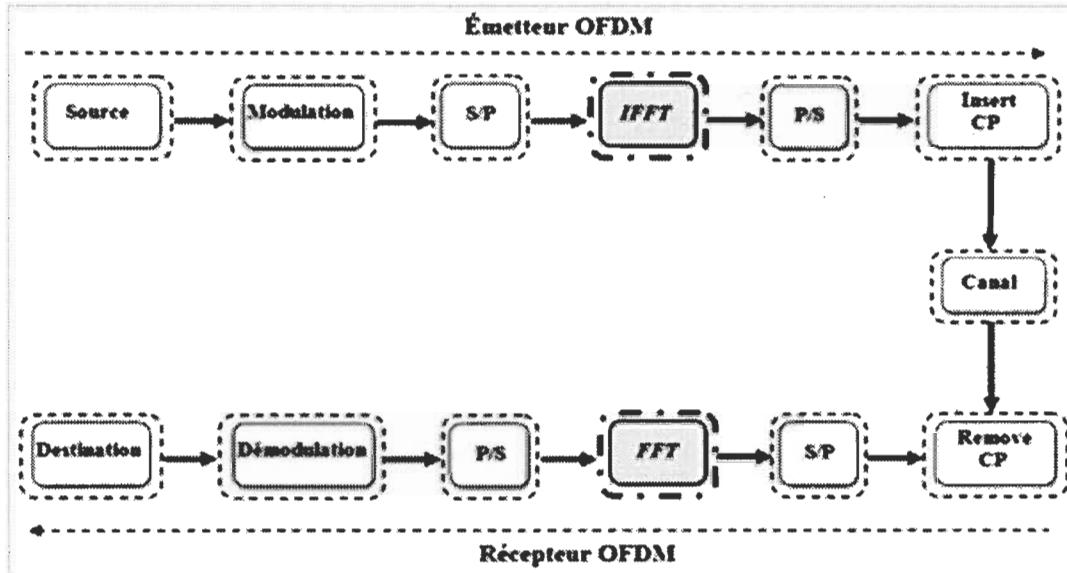

| FIGURE 1.2: ARCHITECTURE D'UN SYSTEME OFDM .....                                                          | 5  |

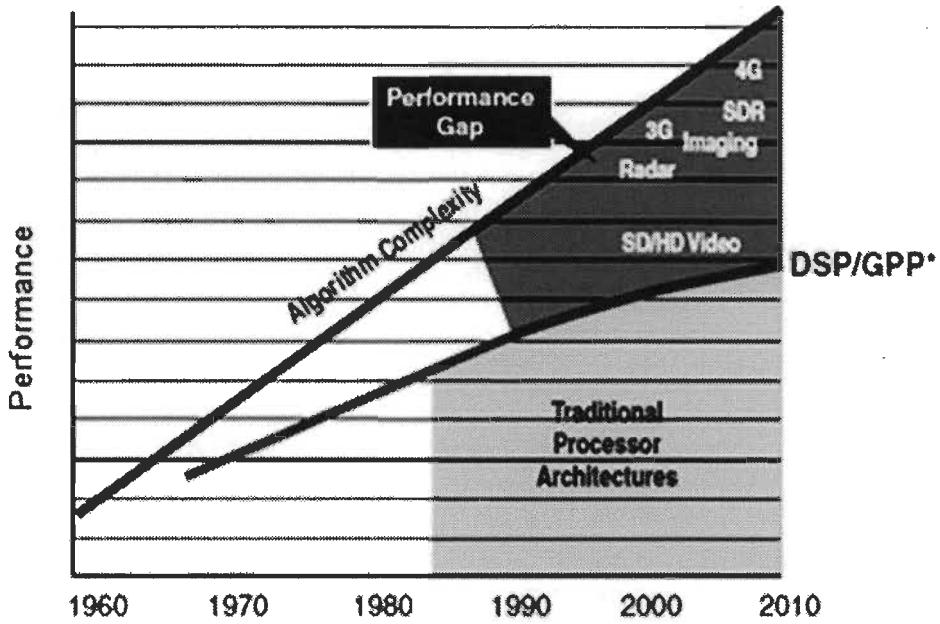

| FIGURE 1.3: PRÉVISION DE LA COMPLEXITÉ ALGORITHMIQUE ET DES PERFORMANCES DES<br>PROCESSEURS [DSP05] ..... | 6  |

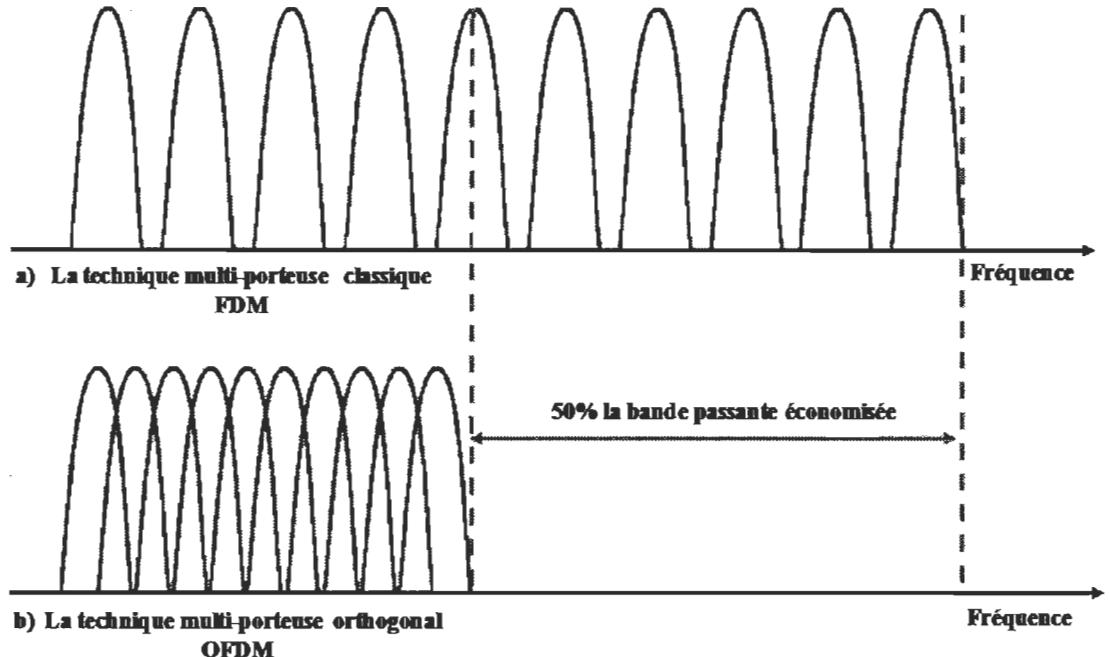

| FIGURE 2.1: MULTIPLEXAGE DE FRÉQUENCE A) CLASSIQUE FDM B) ORTHOGONALE OFDM<br>.....                       | 13 |

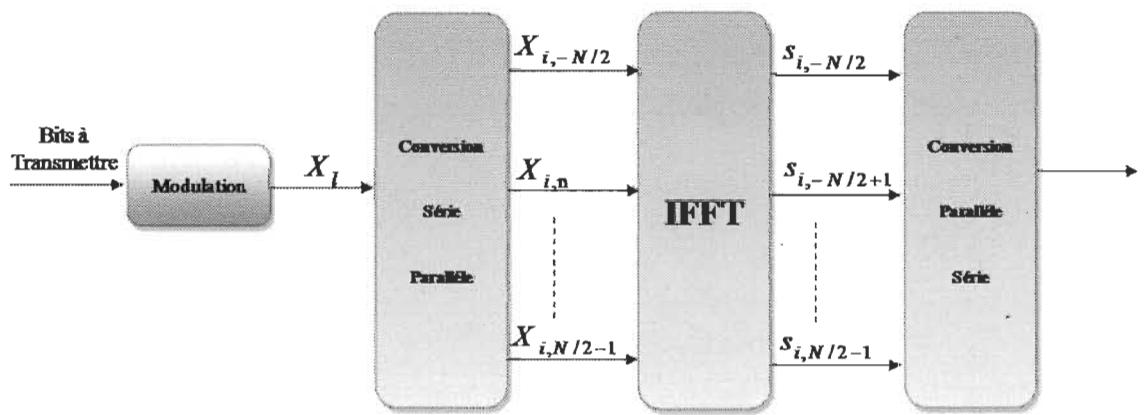

| FIGURE 2.2: SCHÉMA DE PRINCIPE D'UN MODULATEUR OFDM. ....                                                 | 15 |

| FIGURE 2.3: SCHÉMA DE PRINCIPE D'UN DÉMODULATEUR OFDM. ....                                               | 16 |

## LISTE DES FIGURES

---

|                                                                                                                        |    |

|------------------------------------------------------------------------------------------------------------------------|----|

| FIGURE 2.4: (A) LA FORME DES IMPULSIONS PER-SOUS-PORTEUSE. (B) SPECTRE POUR LA<br>TRANSMISSION OFDM BASIC [DAH11]..... | 18 |

| FIGURE 2.5: SPECTRE DU SIGNAL EN SORTIE DU MODULATEUR OFDM, DÉCOMPOSÉ SUR<br>CHAQUE PORTEUSE. [DAH11].....             | 19 |

| FIGURE 2.6: SCHÉMA DE PRINCIPE DU MODULATEUR OFDM NUMÉRIQUE .....                                                      | 20 |

| FIGURE 2.7: SCHÉMA DE PRINCIPE D'UN DÉMODULATEUR OFDM NUMÉRIQUE .....                                                  | 21 |

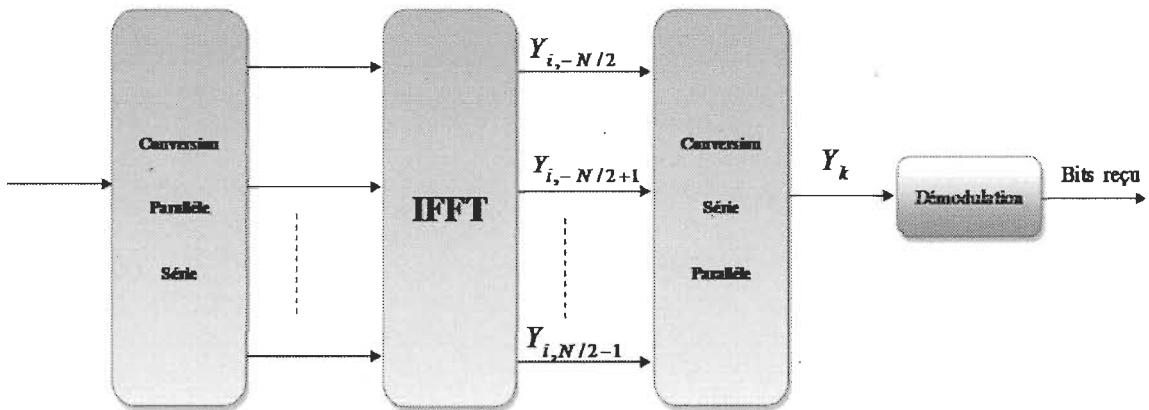

| FIGURE 2.8: LES COEFFICIENTS DE LA DFT POUR N=8.....                                                                   | 26 |

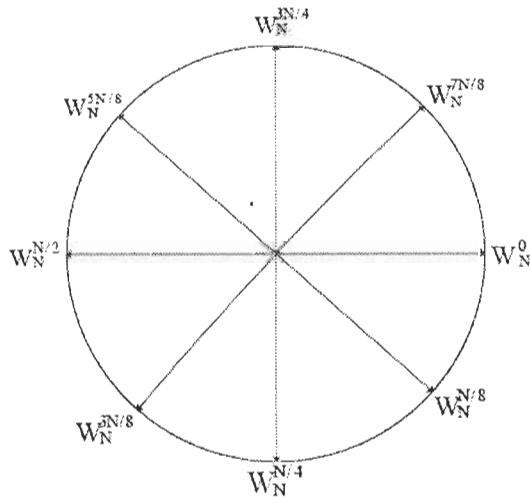

| FIGURE 2.9: DÉCOMPOSITION DE 15 POINTS FFT EN 3 POINTS ET 5 POINTS TFD [PRO96] ..                                      | 32 |

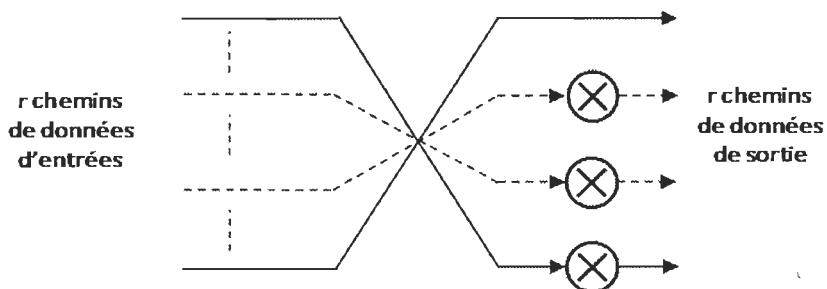

| FIGURE 2.10: PAPILLON (BPE) RADIX- $R$ .....                                                                           | 34 |

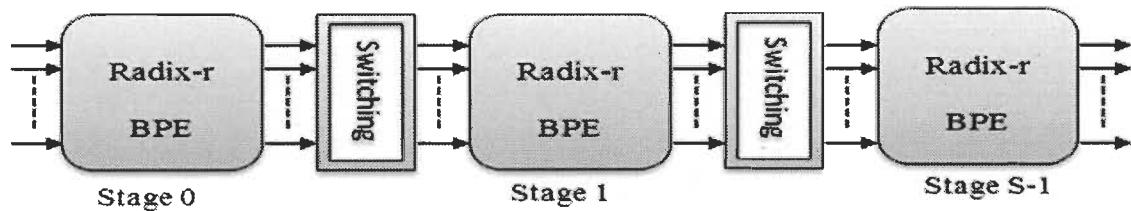

| FIGURE 2.11: ARCHITECTURE PIPELINE DE $S$ STAGES RADIX- $R$ FFT [JAB09] .....                                          | 35 |

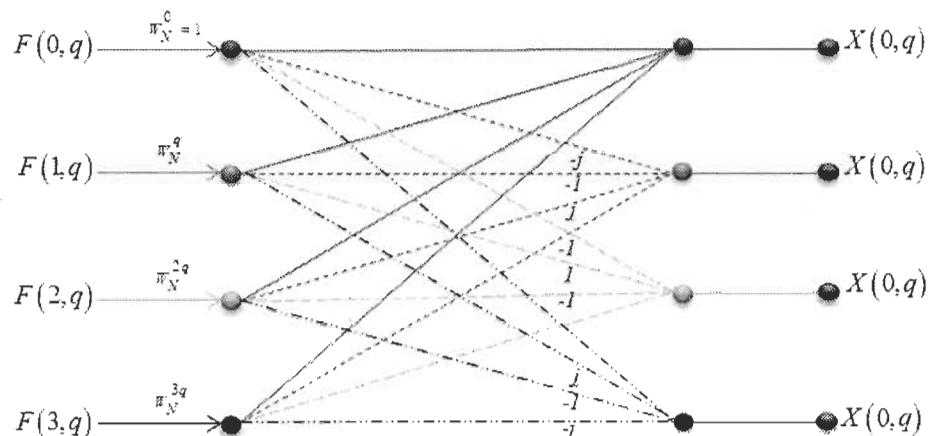

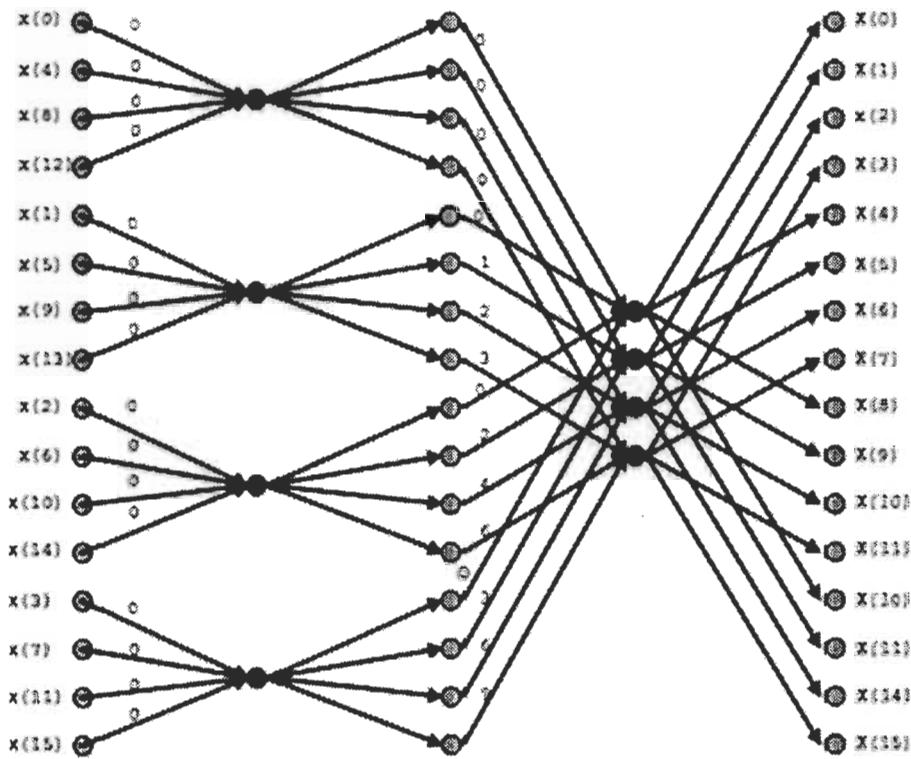

| FIGURE 2.12: DIAGRAMME TYPIQUE DE PAPILLON RADIX-4 DIT .....                                                           | 40 |

| FIGURE 2.13: LA FORME SIMPLIFIÉE DE PAPILLON RADIX-4 DIT .....                                                         | 40 |

| FIGURE 2.14: DIAGRAMME DE LA FFT À BASE DE BUTTERFLY RADIX4 DE TYPE DIT N=16.                                          | 41 |

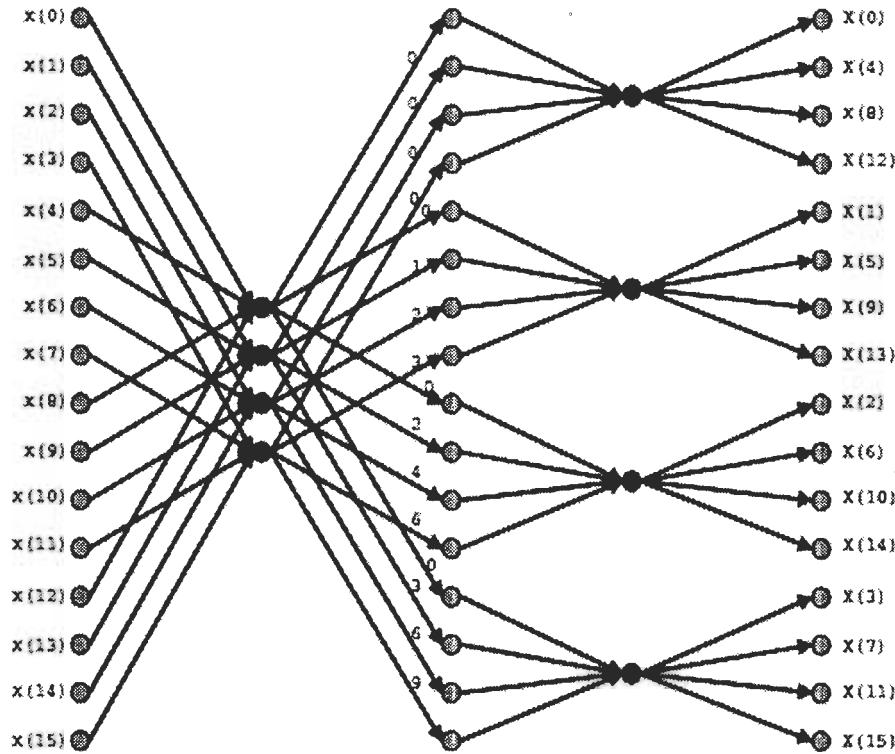

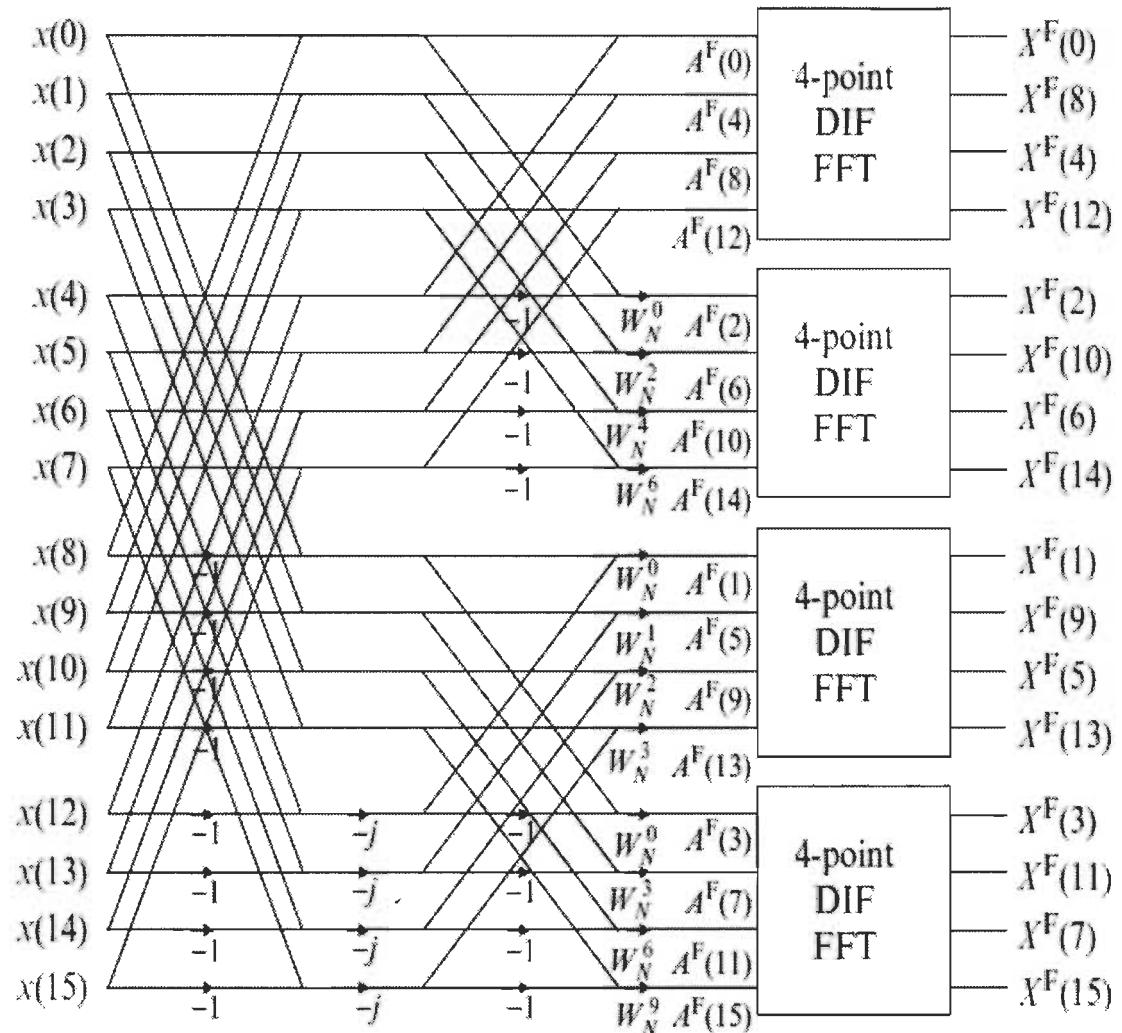

| FIGURE 2.15: DIAGRAMME DE LA FFT À BASE DE BUTTERFLY RADIX4 DE TYPE DIF N=16.                                          | 44 |

| FIGURE 2.16: ARCHITECTURE R4MDC ( $N=64$ POINTS).....                                                                  | 45 |

| FIGURE 2.17: QUELQUES MÉTHODES DE REPRÉSENTATIONS EN VIRGULE FIXE .....                                                | 46 |

| FIGURE 2.18: REPRÉSENTATION DES DONNÉES EN VIRGULE FIXE .....                                                          | 47 |

| FIGURE 2.19: MODÉLISATION DU PROCESSUS DE QUANTIFICATION DU SIGNAL $X$ .....                                           | 50 |

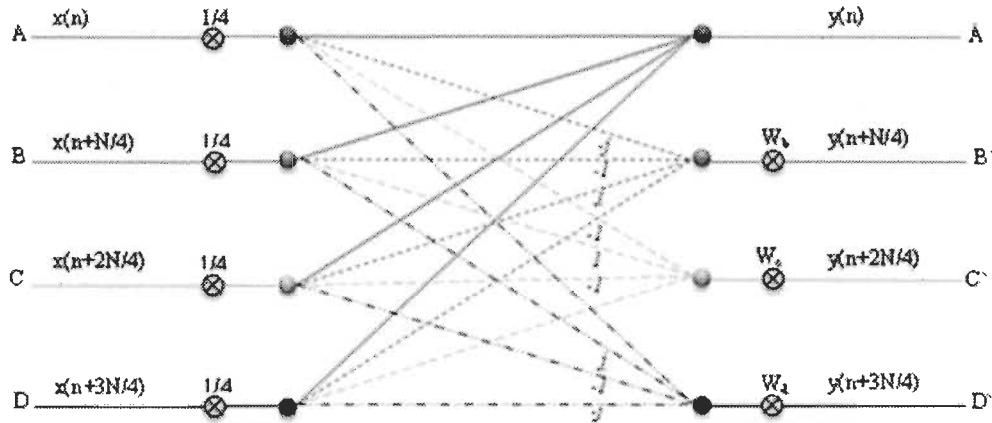

| FIGURE 2.20: BPE RADIX-4 FFT AVEC MISE À L'ÉCHELLE DE 1/4 .....                                                        | 51 |

| FIGURE 3.1: REPRÉSENTATION BINAIRE D'UN INDIVIDU DE DIMENSIONS 6. ....                                                 | 56 |

| FIGURE 3.2: PRINCIPES DE FONCTIONNEMENT D'UN ALGORITHME GÉNÉTIQUE .....                                                | 57 |

---

## LISTE DES FIGURES

---

|                                                                                                             |    |

|-------------------------------------------------------------------------------------------------------------|----|

| FIGURE 3.3: DÉCLARATION DES DÉFINITIONS À VIRGULE FIXE SANS MATLAB .....                                    | 59 |

| FIGURE 3.4: ENCODAGES DES CHROMOSOMES D'UNE FFT DE 16 POINTS .....                                          | 59 |

| FIGURE 3.5: PRINCIPES DE LA TECHNIQUE DE SÉLECTION SUS.....                                                 | 63 |

| FIGURE 3.6: OPÉRATION DE CROISEMENT.....                                                                    | 66 |

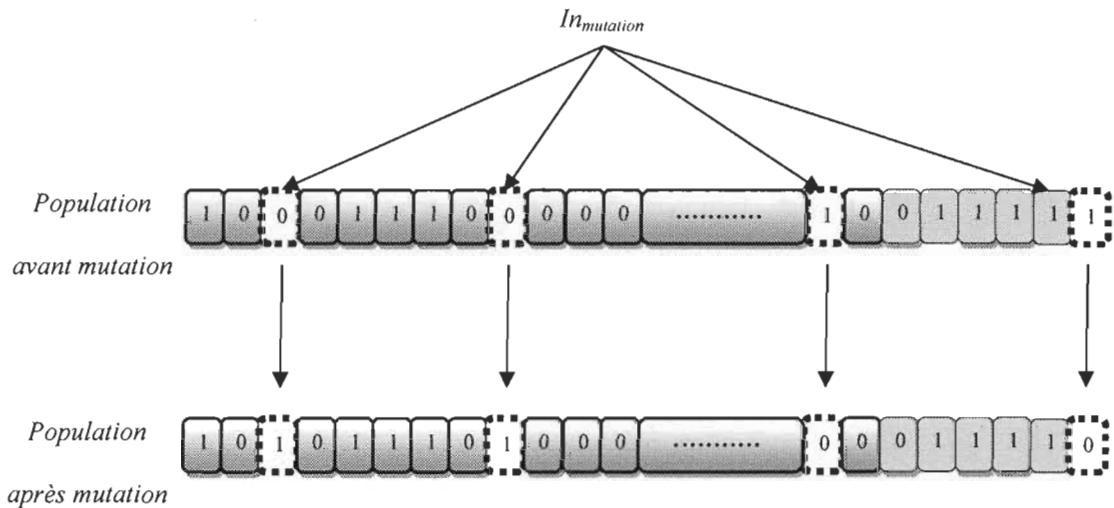

| FIGURE 3.7: OPÉRATION DE MUTATION.....                                                                      | 68 |

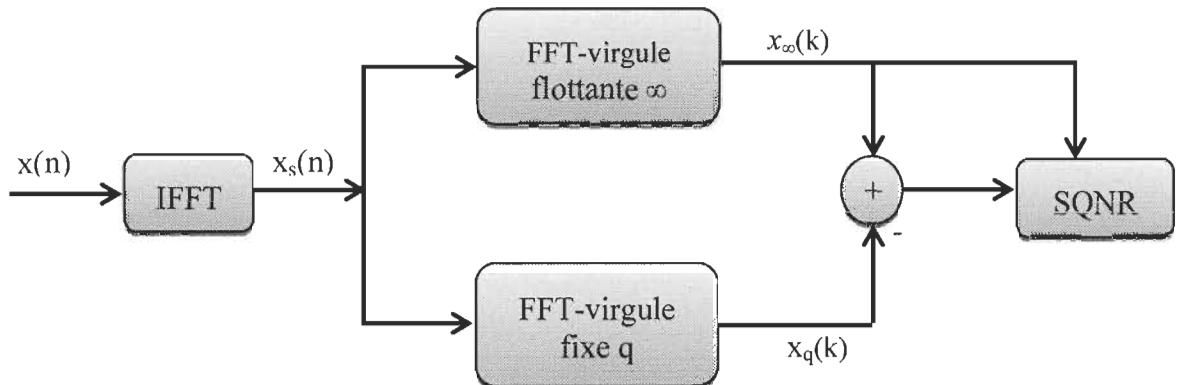

| FIGURE 3.8: MÉTHODOLOGIES D'ÉVALUATION DU SQNR .....                                                        | 70 |

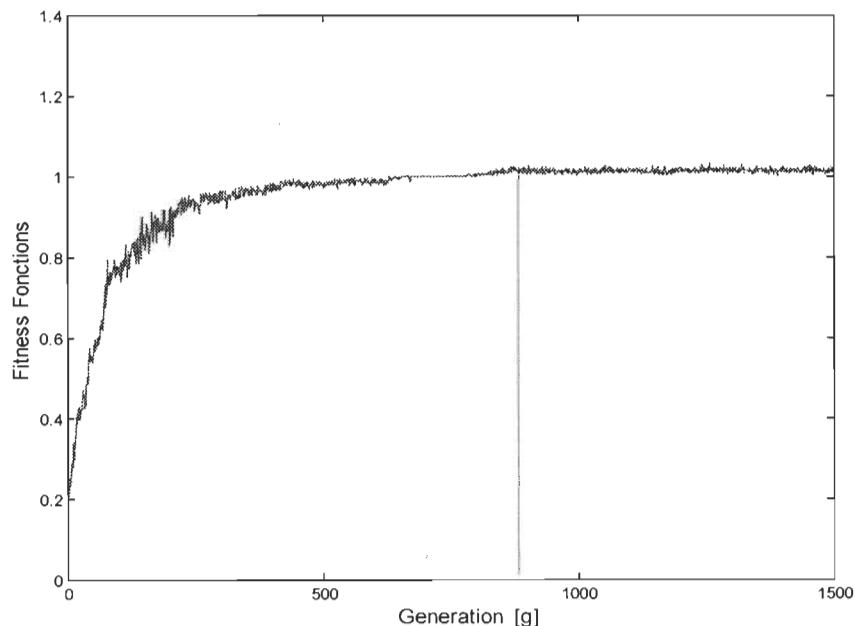

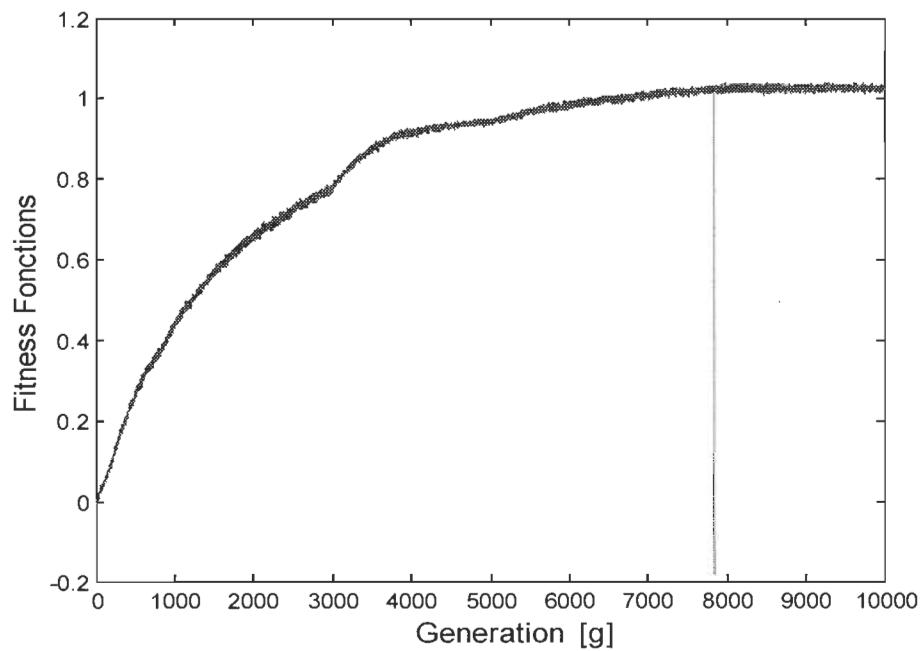

| FIGURE 3.9: ÉVOLUTION DE FONCTION OBJECTIVE DANS LE CAS OÙ N=16, WL_X =10,<br>WL_W=10 .....                 | 72 |

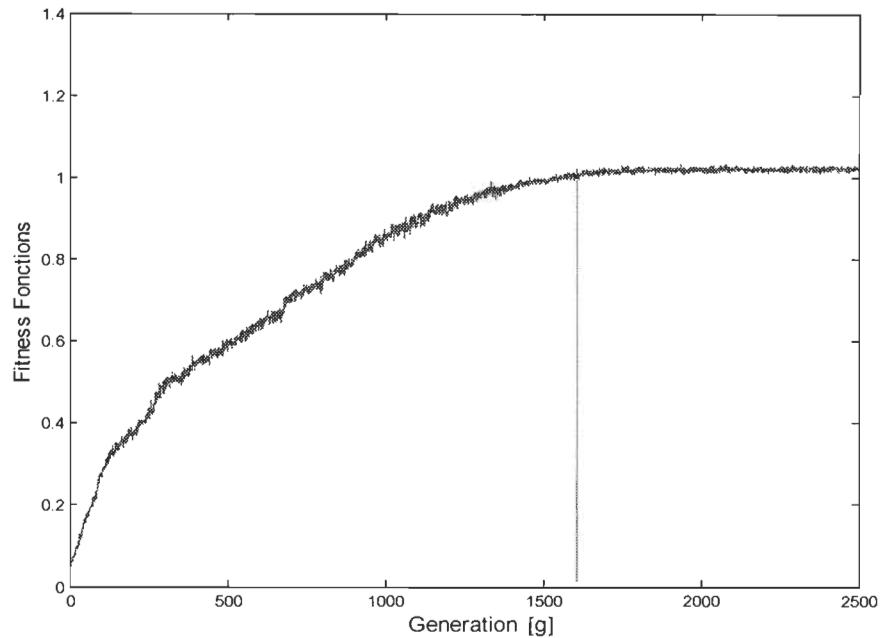

| FIGURE 3.10: ÉVOLUTION DE FONCTION OBJECTIVE DANS LE CAS OÙ N=64, WL_X =10,<br>WL_W=10 .....                | 73 |

| FIGURE 3.11: ÉVOLUTION DE FONCTION OBJECTIVE DANS LE CAS OÙ N=256 WL_X =10,<br>WL_W=10 .....                | 73 |

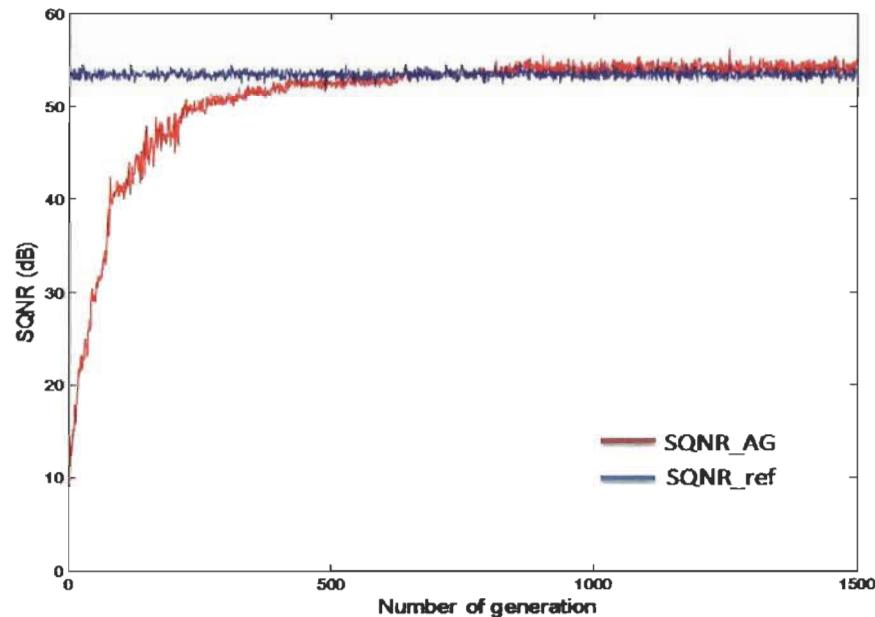

| FIGURE 3.12: CONVERGENCE DE SQNR EN FONCTION DE NOMBRE DE GÉNÉRATION<br>(N=16,WL_X=V.FLOTTANT,WL_W=10)..... | 78 |

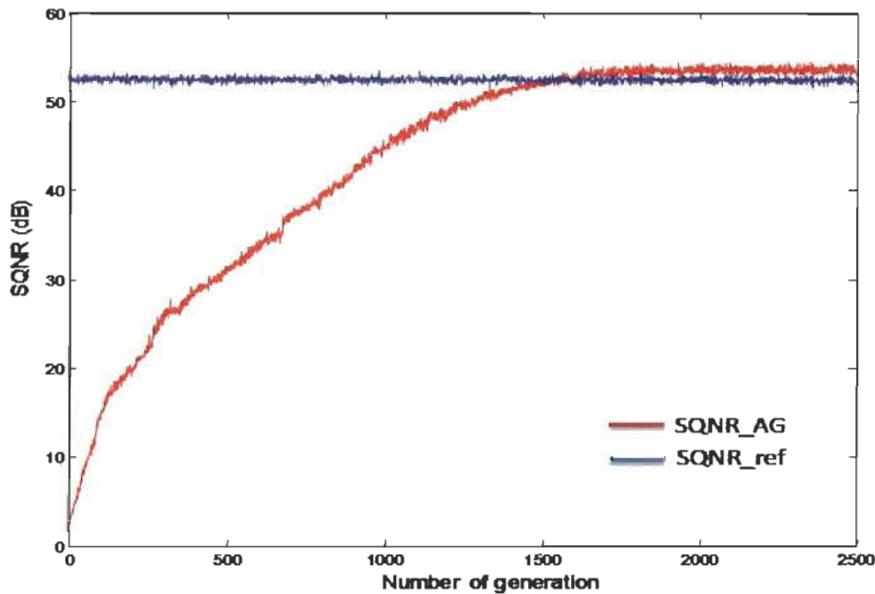

| FIGURE 3.13: CONVERGENCE DE SQNR EN FONCTION DE NOMBRE DE GÉNÉRATION<br>(N=64,WL_X=V.FLOTTANT,WL_W=10)..... | 79 |

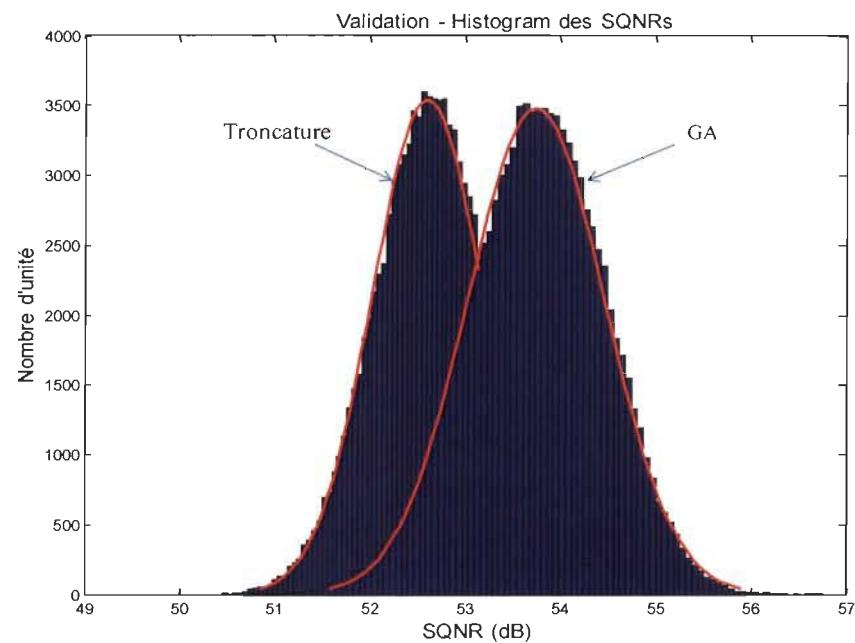

| FIGURE 3.14: HISTOGRAMMES DE LA DYNAMIQUE DE SQNR (N=16, WL_X=V.F, WL_W=10)80                               |    |

## LISTE DES FIGURES

---

|                                                                                                            |    |

|------------------------------------------------------------------------------------------------------------|----|

| FIGURE 3.15: HISTOGRAMMES DE LA DYNAMIQUE DE SQNR (N=64, WL_X=V.F, WL_W=10)                                | 81 |

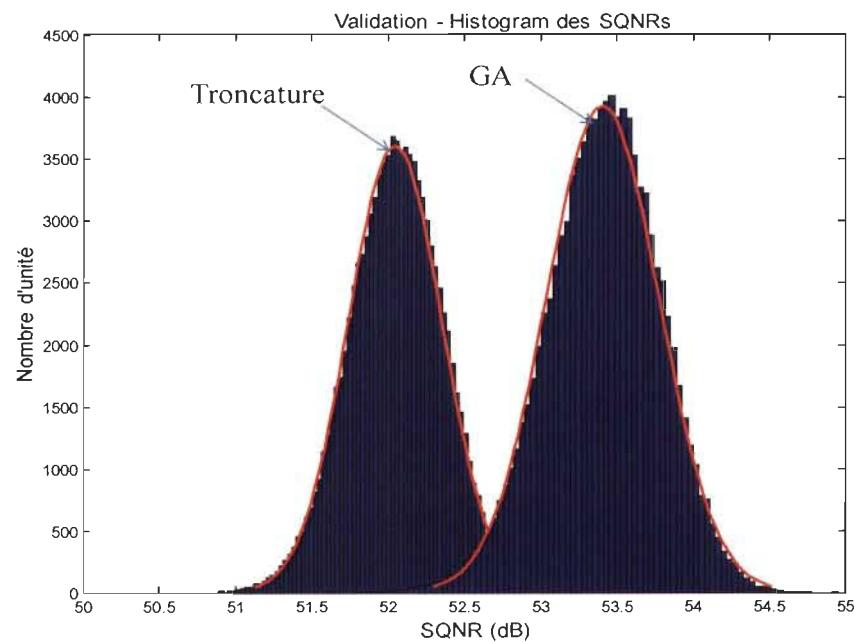

| FIGURE 3.16: HISTOGRAMMES DE LA DYNAMIQUE DE SQNR (N=256, WL_X =V.F, WL_W=10) .....                        | 81 |

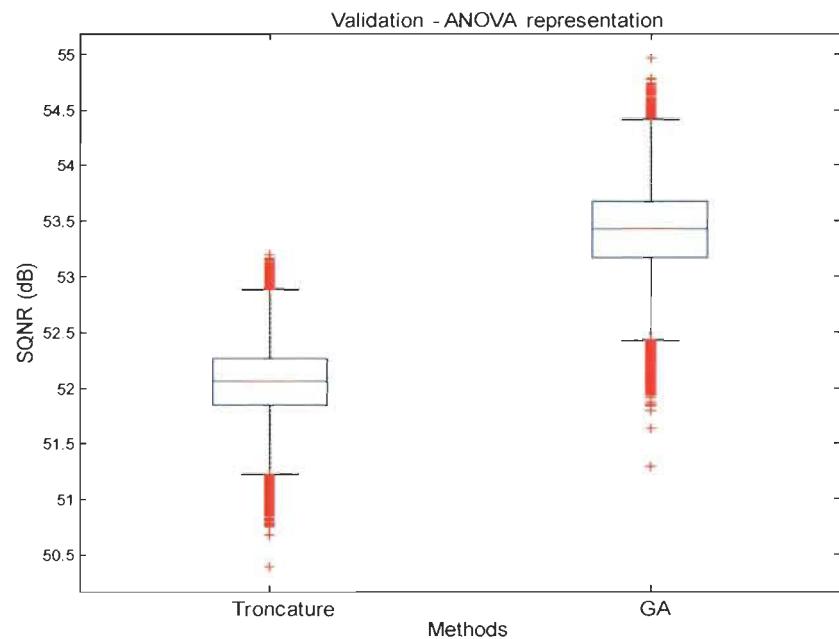

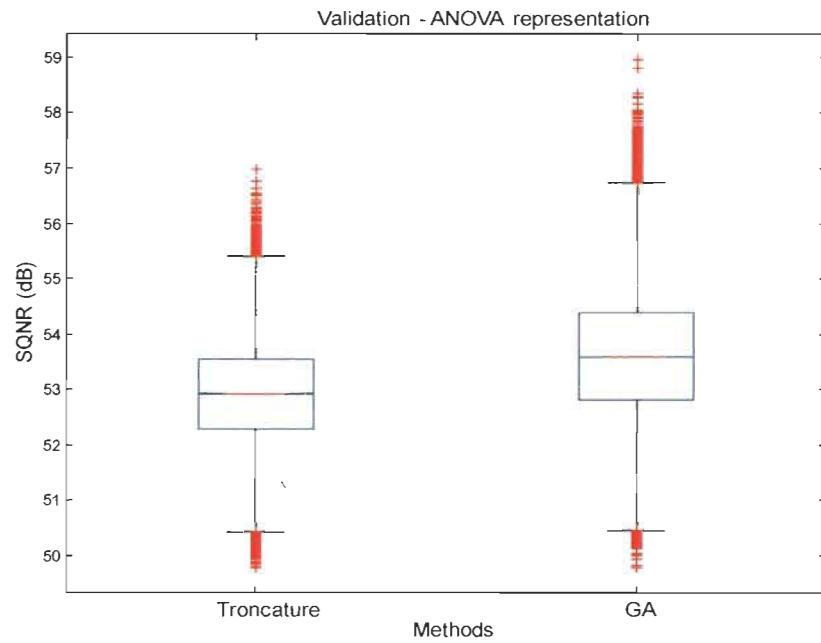

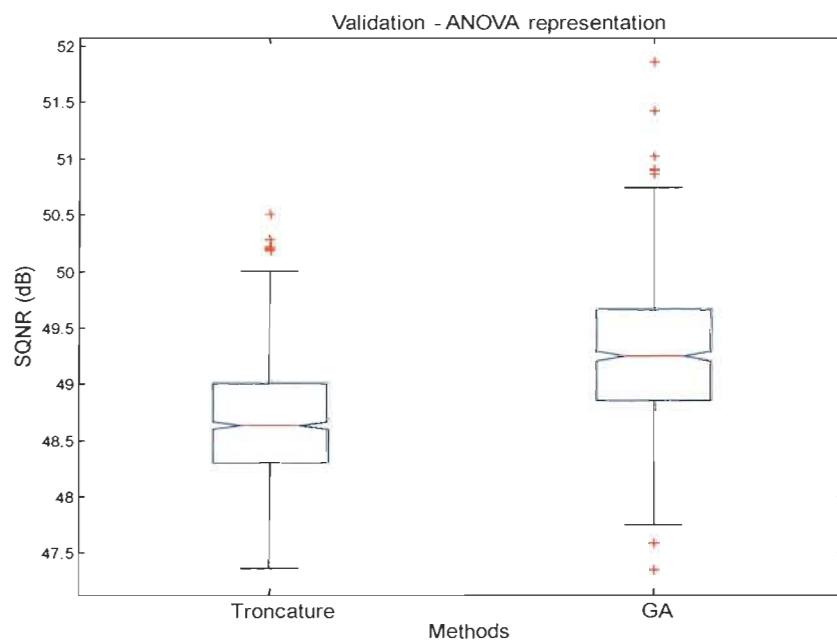

| FIGURE 3.17: ANOVA DES DISTRIBUTIONS STATISTIQUES DES SQNR (N=16, WL_X=V.F, WL_W=10).....                  | 83 |

| FIGURE 3.18: ANOVA DES DISTRIBUTIONS STATISTIQUES DES SQNR (N=64, WL_X=V.F, WL_W=10).....                  | 84 |

| FIGURE 3.19: ANOVA DES DISTRIBUTIONS STATISTIQUES DES SQNR (N=256,WL_X=V.F,WL_W=10).....                   | 84 |

| FIGURE 3.20: ANOVA DE DISTRIBUTIONS STATISTIQUES DES SQNR (N=16, WL_X=V.F,WL_W=10) .....                   | 86 |

| FIGURE 3.21: ANOVA DE DISTRIBUTIONS STATISTIQUES DES SQNR (N=64, WL_X=V.F,WL_W=10) .....                   | 86 |

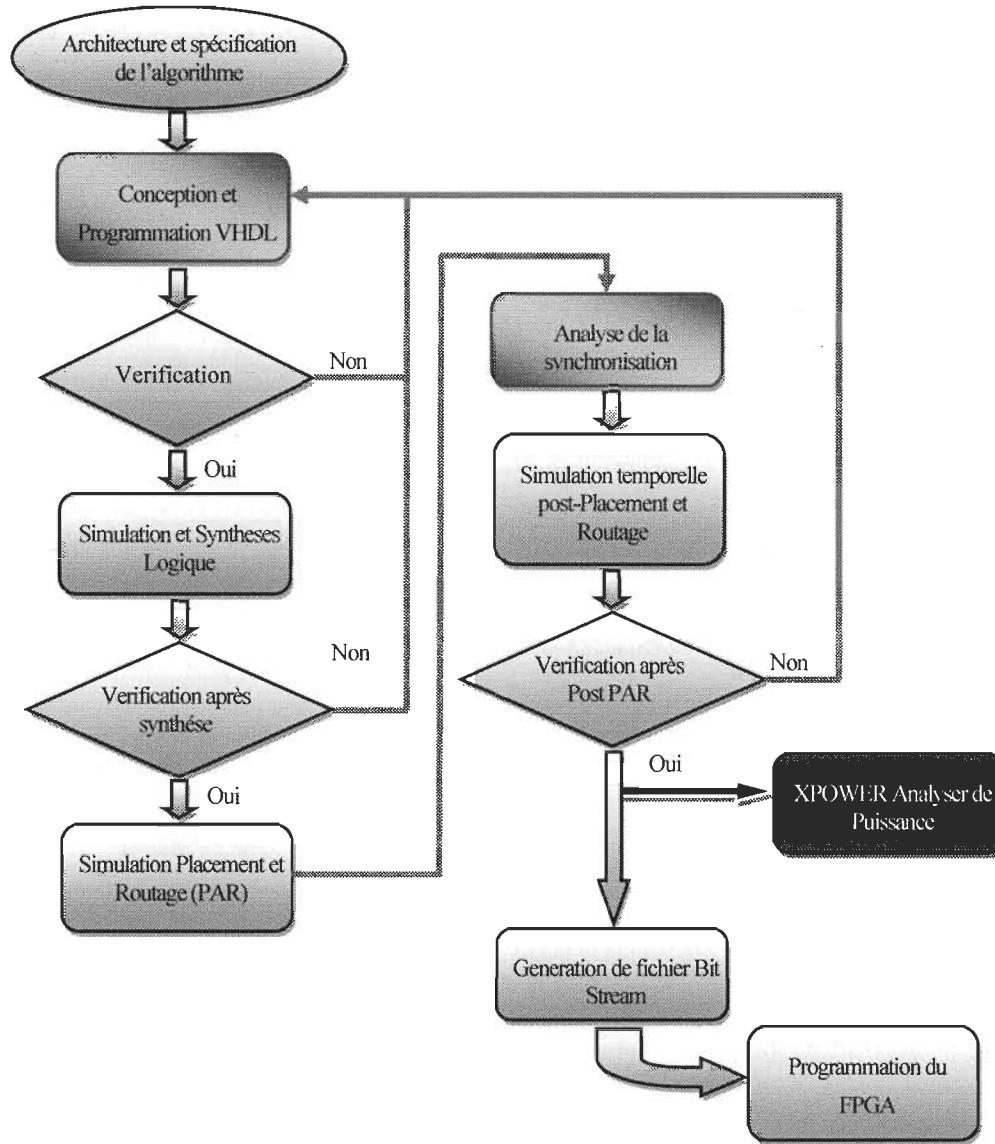

| FIGURE 4.1: ORGANIGRAMME DE CYCLE D'IMPLÉMENTATION ET L'ESTIMATION DE PUISSANCE .....                      | 92 |

| FIGURE 4.2: GRAPHE DE FLUENCE DES ENTRÉES/SORTIES DE LA FFT RADIX-4 MDC DE TYPE DIF POUR N=16 [RAO10]..... | 96 |

| FIGURE 4.3: ARCHITECTURE PIPELINE RADIX-4 MDC DE TYPE DIF À DEUX ÉTAGES .....                              | 97 |

## LISTE DES FIGURES

---

|                                                                                  |     |

|----------------------------------------------------------------------------------|-----|

| FIGURE 4.4: STRUCTURE INTERNE DU BPE RADIX-4 FFT À BASE D'OPÉRATEURS RÉELS. .... | 98  |

| FIGURE 4.5: STRUCTURE INTERNE DE MULTIPLICATEUR COMPLEXE .....                   | 99  |

| FIGURE 4.6: STRUCTURE INTERNE DE COMMUTATEUR .....                               | 100 |

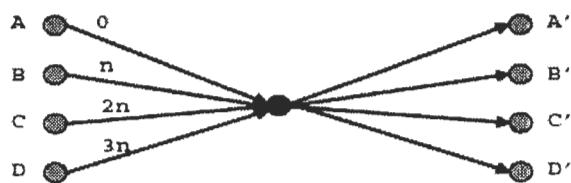

| FIGURE 4.7: LES TRANSFORMATIONS DE COMMUTATEUR.....                              | 101 |

| FIGURE 4.8: BLOC TECHNOLOGIQUE RTL COMPLET DU R4MDC À 16 POINTS.....             | 107 |

| FIGURE 4.9: SCHÉMA TECHNOLOGIQUE COMPLET DU R4MDC À 16 POINTS .....              | 108 |

| FIGURE 4.10: SCHÉMA DE DESIGN INTERNE DE PROCESSEUR FFT R4MDC SUR FPGA.....      | 109 |

---

## LISTE DES TABLEAUX

---

---

## LISTE DES TABLEAUX

---

|                                                                                                                                                                    |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| TABLEAU 2.1: PARAMÈTRE FFT DANS DIFFÉRENTES NORMES OFDM [TSA11] .....                                                                                              | 22 |

| TABLEAU 2.2: COMPARAISON ENTRE LES ARCHITECTURES DES PROCESSEURS FFT .....                                                                                         | 33 |

| TABLEAU 3.1: COMPARAISON EN VIRGULE FIXE EN NOMBRE SIGNÉS ENTRE LES COEFFICIENTS<br>TRONQUÉS ET LES COEFFICIENTS GÉNÉTIQUES POUR UNE FFT À 16 POINTS .....         | 74 |

| TABLEAU 3.2: COMPARAISON EN VIRGULE FLOTTANTE EN NOMBRE SIGNÉS ENTRE LES<br>COEFFICIENTS TRONQUÉS ET LES COEFFICIENTS GÉNÉTIQUES POUR UNE FFT À 16 POINTS<br>..... | 74 |

## LISTE DES TABLEAUX

---

|                                                                                                                                                             |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| TABLEAU 3.3: COMPARAISON EN VIRGULE FIXE EN NOMBRE SIGNÉS ENTRE LES COEFFICIENTS TRONQUÉS ET LES COEFFICIENTS GÉNÉTIQUES POUR UNE FFT À 64 POINTS .....     | 75  |

| TABLEAU 3.4 COMPARAISON EN VIRGULE FLOTTANTE EN NOMBRE SIGNÉS ENTRE LES COEFFICIENTS TRONQUÉS ET LES COEFFICIENTS GÉNÉTIQUES POUR UNE FFT À 64 POINTS ..... | 76  |

| TABLEAU 4.1 : ÉVALUATION DE SQNR EN UTILISANT LES $W_{TRONC}$ .....                                                                                         | 102 |

| TABLEAU 4.2: ÉVALUATION DE SQNR EN UTILISANT LES $W_{AG}$ .....                                                                                             | 102 |

| TABLEAU 4.3: ÉVALUATION DES RESSOURCES MATÉRIELLES ( $N=16$ , $WL\_X=16$ , $WL\_W=16$ ) .....                                                               | 104 |

| TABLEAU 4.4: ÉVALUATION DES RESSOURCES MATÉRIELLES ( $N=16$ , $WL\_X=10$ , $WL\_W=10$ ) .....                                                               | 105 |

| TABLEAU 4.5: ÉVALUATION DES RESSOURCES MATÉRIELLES ( $N=16$ , $WL\_X=16$ , $WL\_W=10$ ) .....                                                               | 105 |

| TABLEAU 4.6 :ÉVALUATION DE LA CONSOMMATION EN PUISSANCE OBTENUS AVEC LES COEFFICIENTS TRONQUÉS .....                                                        | 110 |

## LISTE DES ABRÉVIATIONS

---

---

## LISTE DES ABRÉVIATIONS

---

|          |   |                                                                    |

|----------|---|--------------------------------------------------------------------|

| 2G       | : | Deuxième Génération des systèmes cellulaire                        |

| 3G       | : | Troisième Génération des systèmes cellulaire                       |

| 4G       | : | Quatrième Génération des systèmes cellulaire                       |

| 3GPP     | : | 3 <sup>rd</sup> Generation Partnership Program                     |

| 3GPP-LTE | : | 3 <sup>rd</sup> Generation Partnership Program-Long Term Evolution |

## LISTE DES ABRÉVIATIONS

---

|       |   |                                         |

|-------|---|-----------------------------------------|

| AG    | : | Algorithmes Génétiques                  |

| ANOVA | : | ANalysis Of Variance                    |

| BPE   | : | Butterfly Processing Element            |

| CDMA  | : | Code Division Multiple Access           |

| DVB   | : | Digital Video Broadcasting              |

| DSP   | : | Digital Signal Processing               |

| DIT   | : | Decimation- In-Time                     |

| DIF   | : | Decimation- In-Frequency                |

| DFT   | : | Discrete Fourier Transform              |

| DMT   | : | Discrete Multi Tone                     |

| FFT   | : | Fast Fourier Transform                  |

| FDMA  | : | Frequency Division Multiplexing Access  |

| FPGA  | : | Field Programmable Gate Array           |

| GSM   | : | Global System for Mobile communications |

| HSPA  | : | High Speed Packet Access                |

| HDTV  | : | High Definition Television              |

| ISI   | : | Inter Symbol Interference               |

## LISTE DES ABRÉVIATIONS

---

|             |   |                                                  |

|-------------|---|--------------------------------------------------|

| ICI         | : | Inter-carrier-Interference                       |

| IFFT        | : | Invers Fast Fourier Transform                    |

| IDFT        | : | Invers Discrete Fourier Transform                |

| IMT         | : | International Mobile Télécommunications          |

| IMT-2000    | : | International Mobile Télécommunications-2000     |

| LTE         | : | Long Term Evolution                              |

| LTE avancés | : | Long Term Evolution Advanced                     |

| LSSI        | : | Laboratoire de Signaux et Systèmes Intégrés      |

| MIMO        | : | Multi-input-multi-output                         |

| MDC         | : | Multi-path Delay Commutator                      |

| MC-FDMA     | : | Multi-Carrier Frequency Division Multiple Access |

| MC-TDMA     | : | Multi-Carrier Time Division Multiple Access      |

| MC-CDMA     | : | Multi-Carrier Code Division Multiple Access      |

| NCD         | : | Native Circuit Description                       |

| OFDM        | : | Orthogonal Frequency Division Multiple           |

| PAPR        | : | Peak to Average Powerratio                       |

| PCF         | : | Physical Constraints File                        |

## LISTE DES ABRÉVIATIONS

---

|       |   |                                                    |

|-------|---|----------------------------------------------------|

| PAR   | : | Place-and-Route                                    |

| R2MDC | : | Radix2 Multipath Delay Commutator                  |

| R4MDC | : | Radix4 Multipath Delay Commutator                  |

| RTL   | : | register transfer level                            |

| SDF   | : | Single-path Delay Feedback                         |

| SDC   | : | Single-path Delay Commutator                       |

| SUS   | : | Stochastic Universal Sampling                      |

| SQNR  | : | Signal Quantization Noise Ratio                    |

| TDMA  | : | Time Division Multiple Access                      |

| UMTS  | : | Universal Mobile Telecommunications System         |

| UIT   | : | Union internationale des télécommunications mobile |

| UWA   | : | Underwater Acoustics                               |

| VLSI  | : | Very Large Scale Integration                       |

| VCD   | : | Value Change Dump                                  |

| WiMAX | : | Worldwide Interoperability for Microwave Access    |

| WIFI  | : | Wireless Fidelity                                  |

| XML   | : | Extensible Markup Language                         |

## LISTE DES ABRÉVIATIONS

---

XPA : Xpower Analyzer de la compagnie Xilinx

# CHAPITRE I

---

## INTRODUCTION

---

L'évolution progressive du monde des télécommunications mobile est en train d'envahir la quasi-totalité des domaines d'activité, et la demande pour les systèmes de transmission assurant de très hauts débits avec une qualité de services importants est en croissance exponentielle. Ceci a motivé les chercheurs d'apercevoir des modèles de transmission capable de supporter des communications à large bande. Le développement des réseaux mobiles a traditionnellement été considéré d'une part comme une séquence de générations successives de réseaux de télécommunications [YAY11], essentiellement consacrés à la téléphonie (2<sup>ème</sup>G, *GSM : Global System for Mobile Communications*) basée sur les systèmes mobiles numériques. L'orientation vers la transmission multimédia complète des données ainsi que les communications vocales étaient le fruit des

## CHAPITRE I – INTRODUCTION

---

recherches pour les 3<sup>ème</sup> génération de système de communication mobile nommé UMTS (*Universal Mobile Telecommunication System*) et IMT-2000 (*International Mobile Telecommunication-2000*).

Comparés aux réseaux GSM, les systèmes UMTS sont les premiers systèmes mobiles de traitement des données à haut débit, typiquement dans la gamme de 64 à 384 kbit/s, tandis que le taux maximum de données pour une faible mobilité ou des applications intérieures est de 2 Mbit/s. Avec l'extension du HSPA (*High Speed Packet Access*), les débits des données allant jusqu'à 10 Mbit/s sont disponibles dans la liaison descendante. Le rythme actuel, qui peut être observé dans le marché des communications mobiles, montre déjà que les systèmes 3G ne seront pas les systèmes à solution ultime. Dans un futur proche, selon les critères de l'Union internationale des télécommunications (UIT), qui établirent les normes pour les réseaux cellulaires, les systèmes de communication devront proposer un accès à l'internet avec des débits allant jusqu'à 1 Gbits/s dans une zone locale de couverture (environnement quasi statique) et offrant des débits de données jusqu'à 100 Mbits/s en environnement mobile ; c'est la quatrième génération (4<sup>ème</sup>G) de réseaux cellulaires (voir la figure 1.1). Les technologies préconisées qui devraient satisfaire à ces critères sont les réseaux mobiles WiMAX (*Worldwide Interoperability for Microwave Access*), et les réseaux LTE avancés (*Long Term Evolution Advanced*). Ce type de réseau de haute gamme est voué à remplacer les réseaux de 3<sup>ème</sup> génération basée sur le CDMA (Code Division Multiple Access) qui commence à atteindre leurs limites. De plus, ces normes ont été conçues pour durées longtemps, car le déploiement d'un nouveau réseau est très couteux pour les opérateurs.

## CHAPITRE I – INTRODUCTION

Figure 1.1: Évolution du monde des technologies sans fil [LER09]

Grâce à ces qualités remarquables, en particulier des débits élevés entre la station de base et les terminaux, et afin d'accroître les débits de données et l'efficacité du spectre, l'industrie a développé le nouveau système de radiocommunication mobile LTE (*Long Term Evolution*) qui est une évolution des techniques IMT (International Mobile Telecommunications : UMTS, HSPA, HSPA+). Le LTE vise une efficacité spectrale environ 3 à 4 fois supérieures à l'UMTS HSPA, pour un coût de réseau relativement bas (c'est-à-dire un faible coût par bit transféré). En outre, la réduction de l'intervalle de transmission des données (latence) devrait améliorer considérablement la réactivité du réseau. Enfin, la consommation d'énergie des réseaux LTE doit être minimale que l'UMTS, notamment au niveau du terminal.

## CHAPITRE I – INTRODUCTION

---

Par rapport à la norme UMTS actuelle, la principale innovation de la technologie LTE se base sur l'introduction du procédé de codage par répartition en fréquences orthogonales sous forme de multiples sous-porteuses OFDM (*Orthogonal Frequency Division Multiple*) [MOL11]. En raison de sa flexibilité et son adaptabilité, l'OFDM a été choisi comme une interface pour la liaison descendante dans le cadre des standards LTE.

La spécificité de l'OFDM vient du recouvrement mutuel des différentes sous-porteuses, d'une manière dite orthogonale. Cette orthogonalité permet une utilisation optimale des ressources spectrales et facilite l'implantation numérique. Basant sur la figure 1.2 l'aspect nouveau et moderne de la technique de transmission OFDM est que les signaux sous-porteurs différents sont générés numériquement et conjointement par une transformée de Fourier rapide inverse (*en anglais : Inverse Fast Fourier Transform; IFFT*<sup>1</sup>) dans l'émetteur et par une transformée de Fourier directe (*en anglais : Fast Fourier Transform ; FFT*<sup>2</sup>) dans le récepteur [ROL03]. En conséquence, la génération du signal d'émission est simplifiée et l'efficacité de la bande passante du système est considérablement améliorée.

---

<sup>1</sup> *L'acronyme IFFT, plus largement utilisé comme terme technique, sera utilisé dans le mémoire*

<sup>2</sup> *L'acronyme FFT, plus largement utilisé comme terme technique, sera utilisé dans le mémoire*

Figure 1.2: Architecture d'un système OFDM

## I.1. PROBLÉMATIQUE LIÉE AU SUJET DE RECHERCHE

En se basant sur la figure 1.3, le monde des télécommunications a connu des avancées spectaculaires ces dernières décennies. La complexité algorithmique est un facteur fondamental qui ne cesse d'augmenter chaque fois avec l'évolution des systèmes télécommunications. Les futurs systèmes de communication sans fil sont amenés à proposer une qualité de service très importante en termes de débit d'information élevé, fiabilité, ainsi qu'une faible consommation électrique. L'apparition des réseaux d'accès sans fil large bande tels que le WIFI (*Wireless Fidelity*) ou le WiMAX, la HDTV (*High Definition Television*), ainsi les systèmes de communication 4G, a accru l'intérêt pour de nouvelles techniques de transmission afin de relever un tel défi.

Une des techniques de modulation les plus utilisées dans les systèmes de communication sans fil est l'OFDM, aussi appelée DMT (*Discrete Multi Tone*) dans le cas des

communications filaires. Cette technique de transmission possède une grande efficacité spectrale et semble être la plus adaptée à la demande en termes de débit.

Figure 1.3: Prévision de la complexité algorithmique et des performances des processeurs [DSP05]

La synthèse du signal OFDM est typiquement réalisée en utilisant la transformée de Fourier Rapide inverse (IFFT) à la transmission et directe à la réception permettant de simplifier l'égalisation et par conséquent réduire la complexité du récepteur. Généralement, les modules de FFT/IFFT exigent beaucoup de ressources matérielles, à savoir les registres, les additionneurs/soustracteurs et les multiplieurs le tout en arithmétique à valeur complexe. De plus, dans la technologie VLSI (*Very Large Scale Integration*), l'augmentation du nombre d'opérations arithmétiques entraînera l'augmentation de la consommation d'énergie ce qui rend l'implémentation des modules FFT/IFFT très coûteuse. Par ailleurs, chaque opération arithmétique est réalisée en virgule fixe et engendre une erreur due à la

troncature, appelée erreur au bruit de quantification. Ce dernier est mesuré par le rapport signal sur bruit de quantification (*SQNR: Signal Quantization Noise Ratio*). Respectant les contraintes d'implémentation en technologie VLSI, telles que la faible consommation en puissance et en surface d'implémentation, l'exécution en arithmétique à virgule fixe des transmetteurs-récepteurs s'avère essentielle. Ainsi, une solution efficace de l'implémentation de la FFT consiste à optimiser la largeur binaire des coefficients de Fourier. Pour ce faire, dans un premier temps, une solution est présentée en utilisant les algorithmes génétiques afin de représenter les coefficients de Fourier en tenant compte des contraintes d'implémentation. Dans un second temps, nous comptons implémenter la FFT radix-4 conventionnelle de type MDC (*Multi-path Delay Commutator*) sur FPGA (*Field Programmable Gate Array*). Par la suite, nous estimerons la consommation de la puissance consommée en utilisant le Xpower analyzer de Xilinx (XPA).

### I.2. OBJECTIFS DU SUJET DE RECHERCHE

L'objectif principal de ce projet consiste à proposer une méthode d'optimisation en virgule fixe d'un processeur IFFT/FFT basé sur les algorithmes génétique pour avoir de bonnes performances en termes de probabilité d'erreur avec une faible complexité du traitement, ainsi qu'une faible consommation d'énergie. Pour ce faire, quatre sous-objectifs peuvent être envisagés :

1. Études de l'effet de quantification de l'algorithme Radix-4 FFT de type MDC.

2. Développement des algorithmes d'optimisation de la largeur binaire pour les coefficients de la FFT. A cet effet l'utilisation des algorithmes génétique pour

l’optimisation de la qualité de signal vs compromis de complexité d’implémentation est appliquée dans notre étude.

3. Synthèse et implémentation de la FFT pipeline radix-4 mdc à 2 étages sur FPGA suivie par l’étude d’estimation de la consommation en puissance.

### I.3. MÉTHODOLOGIE DU SUJET DE RECHERCHE

L’ensemble des travaux de ce mémoire a été réalisé au laboratoire LSSI (Laboratoire de Signaux et Systèmes Intégrés) de l’Université du Québec à Trois-Rivières.

Afin d’atteindre nos objectifs, notre méthodologie de travail consiste dans un premier temps, de faire une étude approfondie de la littérature des algorithmes et les différentes architectures pipelines pour le calcul de la FFT. Cette étude nous a fourni un paquet d’informations qui caractérisent chaque algorithme FFT (complexité, quantité de mémoire...). Basé sur cette étude, nous allons choisir l’algorithme radix-4 et son architecture pipeline du type MDC pour le calcul de la FFT. Cependant, son étude est nécessaire pour bien saisir son bon fonctionnement. Ensuite, nous programmons la FFT radix-4 MDC conventionnelle sur Matlab® et nous comparons les résultats en virgule flottante et celle en virgule fixe obtenue en utilisant la fonction *f2*<sup>3</sup> de Matlab®.

Le module IFFT/FFT est une composante non négociable en complexité dans les systèmes de télécommunication mobiles. Ces performances en termes de puissance, la surface et la vitesse d’exécution sont affectées par la largeur binaire des données et des coefficients de FFT [SUL04].

---

<sup>3</sup> Une fonction Matlab permettant la conversion virgule flottante en virgule fixe

## CHAPITRE I – INTRODUCTION

---

Nous étudions les algorithmes génétiques comme outil d’optimisation des coefficients de la FFT. Les bons choix des paramètres qui commandent ces méthodes telles que, le choix de codage des chromosomes, des opérateurs génétiques (sélection, croisement, et la mutation), le critère d’arrêt et la fonction sélective sont les opérations principales pour avoir des résultats optimaux de cet algorithme. La mise œuvre des algorithmes génétiques appliqués pour concevoir un nouveau processeur FFT, permettra également de programmer cette méthode sur Matlab® et de l’appliquer pour l’optimisation des coefficients de la FFT en tenant compte des contraintes d’implémentation VLSI telle que, la complexité de calcul, et la surface d’implémentation. L’étape suivante représente l’implémentation matérielle pour l’estimation en puissance. Dans un premier temps, nous implémentons les blocs de la FFT pipeline de type radix-4 MDC en VHDL. L’outil d’implémentation et de simulation est Modelsim PE Student® de Mentor Graphics®. Secondelement, une fois le code VHDL est vérifié, nous passons à la synthèse de bloc FFT sur FPGA en utilisant le logiciel Xilinx ISE. Ces outils de simulation fournissent la puissance consommée en utilisant le XPower Analyzer.

### I.4. ORGANISATION DE MÉMOIRE

Le reste de mémoire est structuré comme suite :

Le chapitre II met en évidence l’intérêt de la modulation OFDM et examine la DFT comme l’élément de base de la chaîne OFDM. Ce chapitre introduit une revue sur le concept de la DFT et son développement mathématique. Ainsi le modèle mathématique de la FFT radix-4 MDC et son architecture pipeline seront examinés. Le chapitre III discutera

## CHAPITRE I – INTRODUCTION

---

les étapes des algorithmes génétiques appliqués pour l’optimisation de la FFT. Ce chapitre expose également quelques résultats obtenus pour l’optimisation des coefficients de la FFT. Dans le chapitre VI nous discuterons l’implémentation de la FFT radix-4 MDC sur FPGA (Simulation VHDL, Synthèse FPGA). Enfin, le chapitre V présentera la conclusion générale du projet.

## CHAPITRE II

---

### FFT QUANTIFIÉES AU RÉCEPTEUR AU OFDM

---

Nous commençons ce chapitre par la présentation de la technique OFDM comme technique robuste pour les systèmes de communication à haut débit. Son principe de fonctionnement et les éléments constituants de la chaîne OFDM sont présentés aussi. Ensuite, un point est fait sur la fiabilité de ces composants, en particulier sur les éléments sensibles comme la FFT et IFFT. Après, nous exposerons l'historique de la FFT, et une étude approfondie sur l'algorithme FFT adopté dans ce travail. Nous conclurons cette partie par la représentation des nombres en virgule fixe et l'effet de quantification

### II.1. LES SYSTÈMES MULTI-PORTEURS OFDM

L'OFDM est une technique de transmission multi-porteuse consiste à répartir l'information à transmettre à haut débit sur plusieurs sous-porteuses, modulées à bas débit. L'intérêt de cette modulation est l'exploitation optimale du spectre, grâce à la propriété d'orthogonalité des porteuses, ce qui augmente l'efficacité spectrale du système.

#### II.1.1. Historique – Principe

L'idée de l'OFDM est de diviser une bande fréquentielle du signal transmise en un groupe de bandes adjacentes, cette idée a pu être dépistée à la fin des années 50 avec la société Collins Radio Co. Kineplex system [DOE57]. Dans le multiplexage fréquentiel classique (FDM), la bande totale est divisée en  $N$  sous canaux qui ne se chevauchent pas, alors que dans l'OFDM la bande est divisée en un certain nombre de sous canaux superposés avec des fréquences orthogonales.

La figure 2.1 illustre l'efficacité de la largeur de bande requise pour un signal OFDM par rapport à un signal FDM. En utilisant la modulation OFDM, nous économisons près de 50% de la bande passante. Pour réaliser la technique de modulation à porteuses multiples avec chevauchement, il est toutefois nécessaire de réduire l'interférence entre les sous porteurs. Ceci est réalisé par l'orthogonalité fréquentielle des sous porteuses [PRA04].

Figure 2.1: Multiplexage de fréquence a) Classique FDM b) Orthogonale OFDM [PRA04]

L'ensemble des sous-porteuses forme un symbole OFDM. Grâce à l'orthogonalité de l'OFDM, les différentes sous-porteuses se chevauchent dans le domaine fréquentiel, mais sans causer d'interférence entre sous-porteuses ICI (Inter-carrier-Interference). Cette propriété rend ce système robuste contre le problème des multi-trajets.

L'utilisation des porteuses dont le spectre est un sinus cardinal a permis une orthogonalité entre elles pour éviter l'interférence entre canaux [CHA66]. Peu après, B. Salktzberg a expérimenté la performance d'un tel système [SAL67]. En 1971, S. B. Weinstein et P. M. Ebert [WEI71] introduisent l'idée d'utiliser une DFT pour la mise en œuvre de la génération et la réception des signaux OFDM. Après avoir été certifiée, la technique OFDM a été longtemps mise à l'écart des applications commerciales en raison de la complexité que

revêt son implantation. Plus particulièrement, le fait de réaliser la transformée de Fourier en temps réel. Cette opportunité présente une implémentation facile de l'OFDM, spécialement avec l'utilisation de la transformée de Fourier rapide (FFT), qui est une implémentation de la DFT. Pour la première fois, les applications de cette technique ont été proposées en 1985 pour la radiophonie mobile [CIM85], et plus tard implémentaient pour la diffusion numérique [ALA87].

En 1989, cette technique a pris le nom « Modulation à Répartition en Fréquences Orthogonales » (OFDM) [ZER89]. Dans le contexte de la téléphonie mobile, l'OFDM peut être utilisée en combinaison avec d'autres formes d'accès multiple comme le FDMA, le TDMA et le CDMA pour donner lieu, respectivement, aux systèmes FDMA multi-porteuse (MCFDMA), TDMA multi-porteuse (MC-TDMA), et CDMA multi-porteuse (MC-CDMA). Les premières idées pour utiliser l'OFDM en combinaison avec le CDMA ont été présentées dans [YEE93] et [FAZE93].

### II.1.2. Modélisation des systèmes OFDM

L'OFDM peut-être modélisé de plusieurs manières, et la représentation de ce type de système a évolué au cours du temps avec les innovations technologiques. Nous présenterons donc en premier lieu la représentation continue du système OFDM de laquelle nous ferons surgir la modélisation discrète en bande de bases, ainsi qu'une modélisation bidimensionnelle dans le plan temps-fréquence.

### II.1.2.1. Modulations OFDM

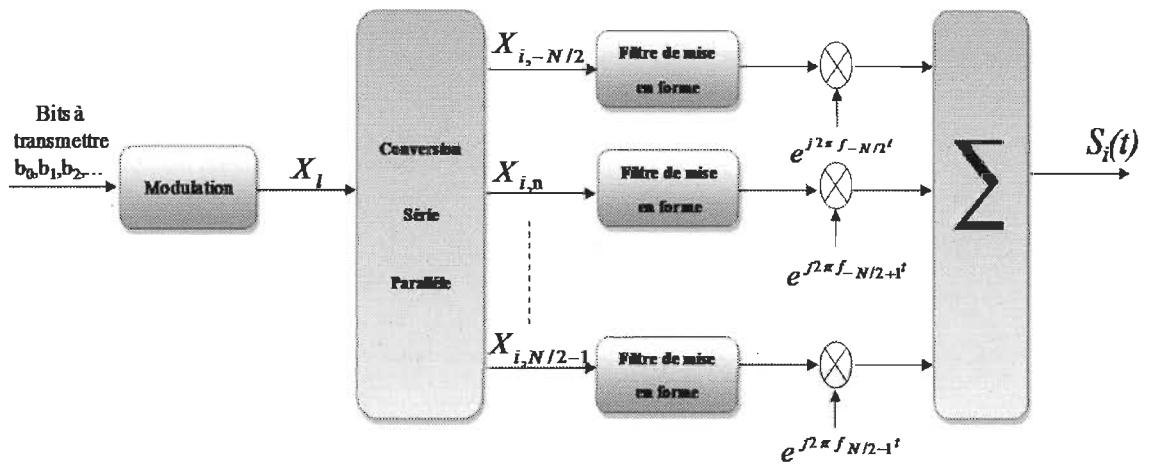

Le principe de la modulation multi-porteuse de types OFDM consiste à transmettre les données de manière simultanée sur  $N$  porteuses. Elle peut être modélisée de plusieurs manières. La figure 2.2 décrit le schéma de principe d'un modulateur OFDM en bande de base.

Figure 2.2: Schéma de principe d'un modulateur OFDM.

Considérons des données binaires ( $b_0, b_1, b_2\dots$ ) de période  $T_b$ . Ces données seront transformées en symboles complexes  $\{X_i\}$  en utilisant des modulations numériques, telles que M-QAM de durée  $T_i = \log_2 M T_b$ , où M est la taille de la constellation. Le convertisseur série-parallèle dispose les symboles complexes  $\{X_i\}$  en groupe de  $N$  symboles, qui sont mis en forme sur une durée de symbole  $T=N.T_b$ , puis envoyés sur les  $N$  porteuses  $\{f_n\}$  afin de former le signal de sortie [TAI09].

Durant l'intervalle du temps  $[iT, (i+1)T]$ , le signal OFDM généré s'écrit [MOL11] :

$$S_i(t) = \sum_{n=-\frac{N}{2}}^{\frac{N}{2}-1} X_{i,n} \underbrace{g(t-iT) e^{j2\pi f_n t}}_{\psi_{i,n}(t)} \quad (2.1)$$

où  $g(t)$  est la forme d'onde de la modulation.  $S_i(t)$  représente le  $i^{\text{ème}}$  symbole OFDM, tandis que les  $\{X_{i,n}\}$  représentent les symboles complexes transmis sur le  $n^{\text{ème}}$  porteuse et le  $i^{\text{ème}}$  symbole OFDM de durée  $T$ . La fréquence inter porteuse  $f_n$  est ici égale à  $1/T$ . L'équation (2.2) décrit le signal reçu pour le cas d'un canal de transmission sans bruit additif [MOL11].

$$y(t) = \sum_{i=-\infty}^{\infty} S_i(t) = \sum_{i=-\infty}^{\infty} \sum_{n=-\frac{N}{2}}^{\frac{N}{2}-1} X_{i,n} \psi_{i,n}(t) \quad (2.2)$$

où  $\{\psi_{i,n}(t)\}_{i,n}$  est la base orthonormale de l'espace des signaux.

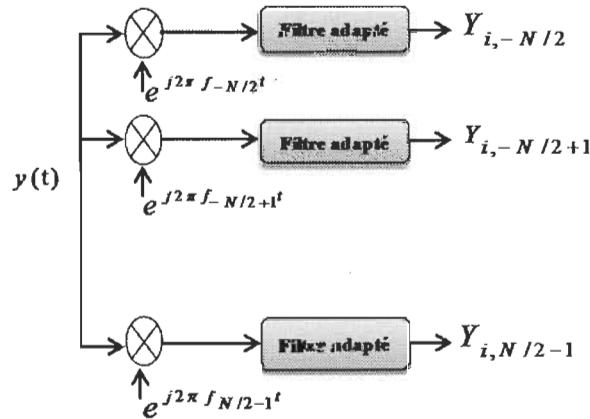

Les symboles transmis peuvent être retrouvés en réception à l'aide d'un filtre adapté suivi d'un échantillonneur. La figure 2.3 illustre le schéma de principe d'un récepteur OFDM.

Figure 2.3: Schéma de principe d'un démodulateur OFDM.

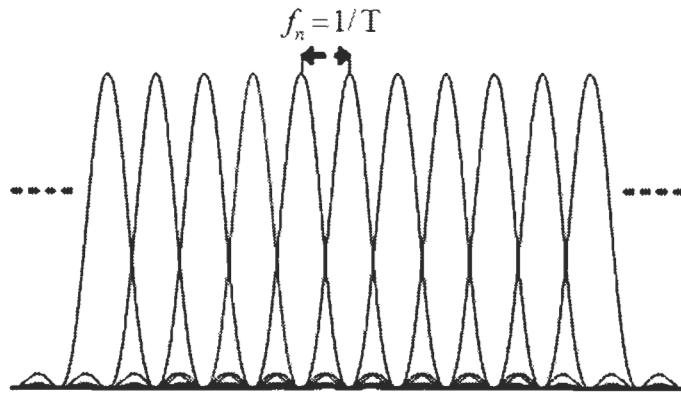

### II.1.2.2. Orthogonalités

La propriété d'orthogonalité est fondamentale en OFDM. Pour que le signal modulé autorise un fort recouvrement spectral entre les sous-porteuses, il faut que les fréquences des porteuses soient les plus proches possible, tout en garantissant que le récepteur soit capable de les séparer et retrouver le symbole numérique émis sur chacune d'entre elles. Ceci est vérifié si le spectre d'une porteuse est nul aux fréquences des autres porteuses (voir la figure 2.1 (b), et la figure 2.5).

En considérons le signal OFDM donnée par l'équation 2.1.  $\psi_{i,n}(t)$ ,  $\psi_{i',n'}(t)$  sont des porteuses orthogonales si :

$$\int_{t_0}^{t_0+T} \psi_{i,n}(t) \overline{\psi_{i',n'}(t)} dt = \begin{cases} 0, & n \neq n' \\ T, & n = n' \end{cases} \quad (2.3)$$

L'équation 2.3 démontre que l'ensemble des  $N$  sous-porteuses d'une trame OFDM sont orthogonales. L'orthogonalité temporelle de la fonction  $\psi_{i,n}(t)$  doit être vérifiée dans la mise en œuvre d'un signal OFDM.

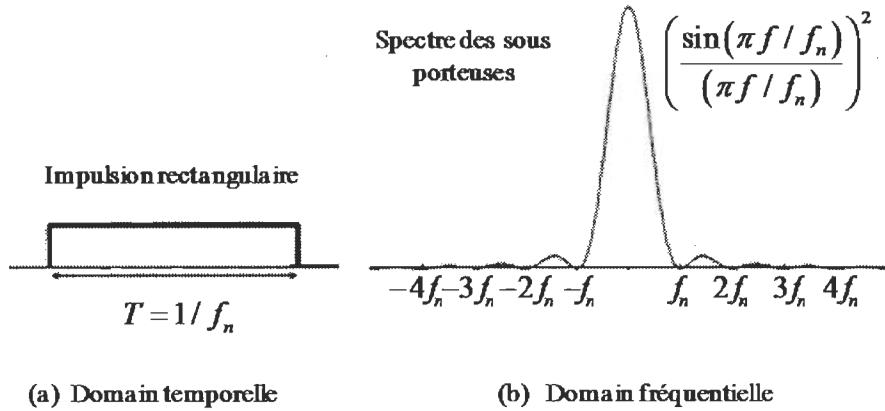

Lors des travaux de Chang [CHA66] ont permis de démontrer que l'orthogonalité de la fonction  $\psi_{i,n}(t)$  se traduit par des conditions sur le module et la phase de  $g(t)$ . Parmi les fonctions disponibles, celle qui est la plus utilisée est la fonction porte  $g(t) = \text{Rect}[0, T]$ . Une simple impulsion rectangulaire élaborée est représentée dans la figure 2.4 (a). Cela

correspond à une Sinc-carrée formée par sous-porteuse du spectre, comme indiqué dans la figure 2.4 (b) [DAH11].

Figure 2.4: (a) la forme des impulsions par sous-porteuse. (b) Spectre pour la transmission OFDM basic [DAH11]

Supposons que les symboles émis sont de moyenne nulle et de variance  $\sigma^2$ , le spectre du signal modulé sur la porteuse  $n$  s'écrit de la façon suivante:

$$S_n(f) = \frac{\sigma^2}{T} \text{sinc}^2[\pi(f - f_n)] \quad (2.4)$$

Ce spectre s'annule aux fréquences  $f = \{f_n + k/T\}$  pour tout entier  $k$  avec  $f_n$  est la fréquence inter porteuse.  $1/T$  est donc l'espacement inter porteuse minimal qui garantit à la fois l'orthogonalité entre les porteuses et une efficacité spectrale optimale. Les spectres des différentes porteuses sont présentés sur la figure 2.5 [TAI09] [DAH11]. Le spectre d'un signal OFDM est la somme de tous ces spectres. Notons que lorsque la mise en forme est une fonction rectangulaire de longueur  $T$ , les filtres adaptés en réception sont des intégrateurs sur la durée  $T$ .

Figure 2.5: Spectre du signal en sortie du modulateur OFDM, décomposé sur chaque porteuse. [DAH11]

### II.1.3. La FFT dans les communications OFDM

D'un point de vue de l'implémentation pratique de l'orthogonalité, la modulation OFDM se fait avec une IDFT/DFT. Ceci est très intéressant puisque les opérations de la IDFT et DFT peuvent s'implanter de façon efficace en utilisant les algorithmes de transformée de Fourier rapide IFFT et FFT. Ces algorithmes permettent de passer d'un nombre de multiplications à  $(N^2)$  vers un nombre de multiplications à  $O(N \log_2(N))$ , ce qui est très intéressant d'un point de vu matériel.

#### II.1.3.1 Implémentation numérique de la Modulation/Démodulation OFDM

La réalisation analogique d'un modulateur OFDM est très complexe car il faut utiliser un banc de modulateurs/démodulateurs synchronisés et un banc de filtres de mise en forme/filtres adaptés avec un grand nombre de voies. En effet, lorsque les porteuses sont orthogonales et que :  $f_n = \frac{n}{T}$  pour  $n = -\frac{N}{2} \dots \frac{N}{2} - 1$ , le signal généré en bande de base dans

l'intervalle de temps  $[iT, (i+1)T]$  peut s'écrire de la façon suivante l'équation (2.5) [TAI09].

$$S_i(t) = \sum_{n=-\frac{N}{2}}^{\frac{N}{2}-1} X_{i,n} e^{j2\pi \frac{nt}{T}} \quad (2.5)$$

Nous discrétons ce signal, nous obtenons :

$$S_i(k) = \sum_{n=-\frac{N}{2}}^{\frac{N}{2}-1} X_{i,n} e^{j2\pi \frac{nk}{N}} \quad (2.6)$$

$\{S_i(k)\}$ , où  $k = -\frac{N}{2} \dots \frac{N}{2}-1$  Correspond aux  $N$  échantillons du  $i^{\text{ème}}$  symbole OFDM. Nous les noterons  $\{S_{i,k}\}$ . Ils peuvent être obtenus grâce à une transformée de Fourier discrète inverse des symboles  $\{X_{i,n}\}$  à transmettre. La figure 2.6 représente un modulateur OFDM.

Figure 2.6: Schéma de principe du modulateur OFDM numérique

A la réception, la procédure inverse est appliquée. La démodulation consiste à effectuer une transformée de Fourier discrète directe des symboles reçus. Ceci peut être réalisé à l'aide de l'algorithme de la FFT. La figure 2.7 décrit le schéma d'un démodulateur OFDM numérique. Nous notons  $\{Y_{i,n}\}$  les symboles reçus après la FFT du récepteur, correspondant aux symboles émis  $\{X_{i,n}\}$  placés avant l'IFFT de l'émetteur.

Figure 2.7: Schéma de principe d'un démodulateur OFDM numérique

#### II.1.3.2. Quelques standards OFDM à base FFT

La technique de modulation OFDM est robuste contre la sélectivité en fréquence et au bruit impulsif du canal de propagation, ce qui permet d'atteindre des débits élevés. La modulation OFDM a émergé comme un signal attrayant pour le modem de communication sans fil large bande telle que les 3GPP LTE, WIMAX, les réseaux locaux sans fil, la télévision numérique (DVB), et a récemment été considéré pour les communications acoustiques sous-marines (UWA: Underwater Acoustics) et les réseaux sans fil de la 4<sup>ème</sup> génération.

Le tableau ci-dessous, résume les paramètres clés de quelques systèmes de communication multi-porteuses.

Tableau 2.1: Paramètre FFT dans différentes normes OFDM [TSA11]

| Technologie                 | Taille de la FFT | Taux d'échantillonnage (MHz) |

|-----------------------------|------------------|------------------------------|

| DVB-T/H                     | 2048-8192        | 9                            |

| 802.11a                     | 64               | 20                           |

| 802.11n                     | 64-128           | 40                           |

| UWB (MB-OFDM)               | 128              | 40                           |

| 802.16 <sup>e</sup> (OFDM)  | 256              | 32.7                         |

| 802.16 <sup>e</sup> (OFDMA) | 128-2048         | 20                           |

| 3GPP-LTE                    | 128-2048         | 30.7                         |

| 802.20                      | 512-2048         | 20                           |

### II.1.2. Avantages et inconvénients de l'OFDM

L'utilisation de la technique OFDM pour les systèmes de communications sans fil conduit à certains avantages et inconvénients. La décision d'utiliser une telle technique est toujours basée sur l'évaluation du rapport coût/performances. Dans certains scénarios tels les communications mobiles intérieures, la réalisation de la technique OFDM s'avère avantageuse sinon la communication n'est pas fiable.

Les principaux avantages de l'OFDM sont les suivants:

- Une haute efficacité spectrale et une grande robustesse à l'évanouissement sélectif en fréquence.

- Une réalisation numérique simple par utilisation d'IFFT/FFT. cela a conduit à son utilisation massive dans plusieurs standards

- Réduction de la complexité des récepteurs évitant les ISI et ICI grâce à l'ajout d'un intervalle de garde.

- L'OFDM permet une égalisation simple grâce à l'ajout du préfixe cyclique, même en présence de canaux multi trajets denses.

Mais le système utilisant la technique d'OFDM n'est pas parfait. L'OFDM possède néanmoins des inconvénients qu'il est important d'appréhender :

- Les signaux multi porteuses ont un coefficient PAPR (*Peak to Average Power ratio*) élevé, ce qui nécessite l'utilisation des amplificateurs à haute linéarité.

- La perte dans l'efficacité spectrale due à l'addition d'un intervalle de garde.

- La sensibilité à l'effet Doppler : quand le récepteur est en mouvement relatif par rapport à la source, la fréquence du signal reçu ne sera pas la même que celle du signal émit. La fréquence du récepteur est supérieure à celle de l'émetteur et diminue au fur et à mesure qu'ils se rapprochent entre eux. Ceci s'appelle « l'effet Doppler ».

- Si le récepteur OFDM est mal synchronisé temporellement, un phénomène d'interférence entre symboles OFDM peut intervenir dégradant considérablement les performances du système global.

### II.2. ALGORITHME FFT ET L'EFFET DE QUANTIFICATION

Dans cette partie, nous commençons par un aperçu de la DFT qui est utilisée pour produire l'analyse de fréquence des signaux périodiques non discrets. Par la suite, nous présentons la FFT comme une autre méthode pour atteindre le même résultat de la DFT tout en apportant moins de complexité de calculs. Enfin, le reste de cette partie se concentre sur la représentation des nombres en virgule fixe et l'effet de quantification.

#### II.2.1 La Transformée de Fourier Discrète

Un signal numérique dans le temps peut être transformé dans le domaine fréquentiel au moyen de la transformée en Z ou de la transformée de Fourier [PRO96]. De manière générale, un signal périodique  $x(t)$  peut se représenter sous la forme d'une somme de signaux sinusoïdaux, selon l'expression (2.7) appelée également transformée de Fourier inverse :

$$x(t) = \int_{-\infty}^{\infty} X(f) e^{j2\pi ft} df \quad (2.7)$$

où :

- $X(f)$  est un nombre complexe définissant l'amplitude et la phase de chaque composante de fréquence. Le terme  $X(f)$  constitue la transformée de Fourier du

signal temporel  $X(t)$  éventuellement complexe, sa définition est donnée par l'équation (2.8) :

$$X(f) = \int_{-\infty}^{\infty} x(t) e^{-j2\pi ft} dt \quad (2.8)$$

L'expression (2.8) correspond à la forme continue de la transformée de Fourier. Le calcul de cette dernière sur une série échantillonnée conduit alors à la définition de la DFT noté  $X[k]$ . Ainsi, pour une série  $x(n)$  constituée d'un nombre  $N$ , de valeurs finies, l'expression de la DFT d'un signal  $x(n)$  est définie dans l'équation (2.9) [PRO96] [RAO10]:

$$X[k] = \sum_{n=0}^{N-1} x(n) e^{-j2\pi k \frac{n}{N}}, \quad 1 \leq k \leq N \quad (2.9)$$

- $n$  et  $k$  représentent respectivement les variables discrètes et normalisées de l'espace original et de l'espace transformé.

- $N$  est une puissance de 2, représente le nombre des valeurs discrètes et successives des variables  $n$  et  $k$ . Et sont inverse associé; IDFT qui effectue l'opération inverse, c'est-à-dire qu'elle convertit le spectre fréquentiel  $X[k]$  dans le domaine du temps échantillonné  $x(n)$ , est donnée par l'équation (2.10) :

$$x(n) = \frac{1}{N} \sum_{n=0}^{N-1} X[k] e^{j2\pi k \frac{n}{N}}, \quad 1 \leq n \leq N \quad (2.10)$$

- $x(n)$  représente le vecteur temporel  $X[k]$  désigne le vecteur fréquentiel,

- $N$  représente la longueur de la DFT/IDFT, et  $1/N$  est un facteur de pondération utilisé dans l'expression de la IDFT afin d'obtenir les mêmes coefficients que dans la décomposition en série de Fourier.

aussi :

$$W_N^{kn} = e^{-j2\pi k \frac{n}{N}} = \cos\left(\frac{2\pi k}{N}\right) + j\sin\left(\frac{2\pi k}{N}\right) \quad (2.11)$$

Est nommé facteur de phase ou coefficient de transformation (en anglais: Twiddle Factor), qui est le coefficient complexe, utilisé pour combiner les résultats d'une étape précédente afin de former l'entrée de l'étape suivante. Ce facteur correspond à une coordonnée sur le cercle unitaire complexe, tel que représenté par la figure 2.8.

Figure 2.8: Les coefficients de la DFT pour  $N=8$

Nous pouvons réécrire l'équation (2.9) sous forme matricielle en faisant ainsi apparaître la complexité de l'algorithme de la DFT.

La matrice de la DFT est composée d'exponentielles complexes, elle est définie comme suite :

$$X[k] = \underbrace{\begin{bmatrix} 1 & 1 & 1 & \dots & w^0 \\ 1 & e^{-j2\pi\frac{1}{N}} & e^{-j2\pi\frac{2}{N}} & \dots & e^{-j2\pi\frac{N-1}{N}} \\ 1 & e^{-j2\pi\frac{2}{N}} & e^{-j2\pi\frac{4}{N}} & \dots & e^{-j2\pi\frac{2(N-1)}{N}} \\ \vdots & \vdots & \vdots & \ddots & \vdots \\ 1 & e^{-j2\pi\frac{N-1}{N}} & e^{-j2\pi\frac{1}{N}} & \dots & e^{-j2\pi\frac{(N-1)}{N}} \end{bmatrix}}_{\text{La matrice DFT}} \begin{bmatrix} x(0) \\ x(1) \\ x(2) \\ \vdots \\ x(N-1) \end{bmatrix} \quad (2.12)$$

Ce qui peut être représenté sous la forme matricielle suivante :

$$X[k] = [B_N][x_N] \quad (2.13)$$

Où :  $[B_N]$  la matrice des coefficients et  $[x_N]$  la matrice d'entrée de la DFT.

Le calcul directe d'une DFT correspond à la sommation d'un produit pour chaque point. Ceci est équivalent à une quantité de calculs considérable. En effet, si  $N$  est élevé, selon les formules données en (2.9) et (2.10), la DFT revient à calculer un produit matrice-vecteur où chaque élément est de type complexe. La complexité de calcul de la DFT est donc de :  $N^2$  multiplications et  $N(N-1)$  additions sur des nombres complexes. Ceci revient à une complexité de  $4N^2$  multiplications réelles et  $N(4N-2)$  additions réelles. Par conséquent, la complexité de l'algorithme est de  $O(N^2)$ , ceci demeure élevé en quantité de ressources

matérielles nécessaire. Donc, en raison de l'implémentation de traitement numérique de signal en temps réel, optimiser ce calcul devient très avantageux [PRO96] [RAO10].

Une autre forme de la DFT est utilisée pour les processus de modulation et de démodulation, appelée la transformée de Fourier rapide (FFT), qui est un algorithme de DFT développé en 1965 [COO65]. Cette transformée rapide réduit considérablement le temps de calcul et la complexité arithmétique.

### II.2.2. La Transformée Rapide de Fourier

De nombreux travaux ont essayé de réduire la complexité de la DFT. En effet, Cooley et Tukey introduisent en 1965 le premier algorithme de la FFT qui permet de réduire considérablement le temps de calcul de la DFT d'une suite dont le nombre d'échantillons  $N$  est décomposable en facteurs typiquement, une puissance de 2, connu sous le nom de Radix-2 [COO65]. Cette publication allait engendrer de nombreuses recherches sur les algorithmes de calculs des transformées. Depuis, et encore de nos jours, les algorithmes de FFT ont révolutionné le traitement numérique de signal (Digital Signal Processing : DSP). Leur efficacité réside dans la réduction du nombre d'opérations nécessaires, en particulier le nombre des multiplications ce qui réduit davantage le temps d'exécution.

Tous ces algorithmes sont basés sur un même principe qui consiste à décomposer le calcul de la DFT en plusieurs sous ensemble de DFT de longueur plus petite. La mise en œuvre de ce principe conduit à différentes méthodes.

En profitant des propriétés de symétrie et de périodicité suivant les équations (2.14) et (2.15) des facteurs de phases  $W_N^k$ .

Symétrie :

$$W_N^{k+\frac{N}{2}} = -W_N^k \quad (2.14)$$

$$(W_N^k)^* = W_N^{-k}$$

Périodicité :

$$W_N^{k+N} = W_N^k \quad (2.15)$$

Où (\*) désigne le complexe conjugué.

Nous pouvons réduire significativement les nombres d'opérations arithmétiques. Cependant, la complexité globale reste  $O(N^2)$  [OPP75].

Les algorithmes de FFT permettent de faire une DFT de manière efficace ainsi que de réduire la charge de calcul en termes de multiplications et additions complexe à l'ordre  $O(N \log_2 N)$ . En effet, il existe de nombreux algorithmes FFT qui découlent tous de l'approche diviser pour régner (en anglais : divide-and-conquer approach). L'idée de cette approche consiste à représenter les vecteurs  $X[k]$  et  $x(n)$  sur deux dimensions (cas du radix-2, radix-4, radix-8, etc ...) ou bien plusieurs dimensions (cas du radix- $2^i$ , radix- $4^i$ ).

### II.2.3. Approche diviser-pour-régner

L'algorithme de la FFT et ses variantes sont détaillées dans de nombreux ouvrage, notamment (Proakis et Manolakis) [PRO96]. Le principe de base de l'algorithme consiste à faire un changement de variable de l'indice  $n$  sur deux dimensions entières. Par exemple, avec  $M$  pour les colonnes et  $L$  pour les lignes, on a :

$$N = ML \quad (2.16)$$

$$n = Ml + m; \quad 0 \leq l \leq L-1, \text{ et } 0 \leq m \leq M-1 \quad (2.17)$$

$$k = Mp + q; \quad 0 \leq p \leq L-1, \text{ et } 0 \leq q \leq M-1 \quad (2.18)$$

Avec ce changement de variable, les points de séquence à transformer seront représentés sous forme matricielle. Ainsi, l'équation de la DFT devient :

$$X[p, q] = \sum_{m=0}^{M-1} \sum_{l=0}^{L-1} X[l, m] W_N^{(Mp+q)(mL+l)} \quad (2.19)$$

Le terme  $W_N^{(Mp+q)(mL+l)}$  peut être simplifié de la manière suivante :

$$W_N^{(Mp+q)(mL+l)} = W_N^{MLmp} W_N^{mLq} W_N^{MpI} W_N^{lq} \quad (2.20)$$

Toutefois,  $W_N^{MLmp} = 1$ ,  $W_N^{mLq} = W_M^{mq} = W_{(N/L)}^{mq}$  et  $W_N^{MpI} = W_L^{lp} = W_{(N/M)}^{lp}$

De là on obtient l'équation :

$$X[p, q] = \sum_{l=0}^{L-1} \left\{ W_N^{lq} \left[ \underbrace{\sum_{m=0}^{M-1} X(l, m) W_M^{mq}}_{\substack{\text{DFT à M point} \\ \text{Rotation}}} \right] \right\} W_L^{lp} \quad (2.21)$$

L'équation (2.21) illustre le fonctionnement de la FFT. Soit la décomposition de la FFT à N points, en L FFT à M points. Pour résoudre l'équation (2.21), nous procérons d'abord à des

TFD de  $M$  points correspondant à la sommation à l'intérieur entre crochets. Ensuite, la matrice résultante subit une multiplication point à point par les facteurs de phase  $W_L^{lp}$  et enfin des TFD sur  $L$  points sont effectuées en suivant l'autre dimension. En effectuant ces étapes, la complexité passe de l'ordre  $N^2$  à l'ordre  $N(M+L)$ .

Nous pouvons aussi récursivement faire d'autres changements de variables, en prenant un nombre premier pour  $L$ . Par la suite, nous factorisons  $M$  jusqu'à obtenir seulement des TFD ayant des tailles de nombre premier [PRO96].

L'algorithme diviser pour régner peut se résumer dans les étapes suivantes [PRO96]:

1. Calcul de  $M$ -point DFT,  $F(l, q)$  de chaque ligne selon l'équation (2.22).

$$F(l, q) = \sum_{m=0}^{M-1} X(l, m) W_M^{mq} \quad (2.22)$$

2. Multiplier le tableau résultant par le facteur de phase  $W_N^{lq}$ , en obtient  $G(l, q)$  définit par :

$$G(l, q) = W_N^{lq} F(l, q) \quad (2.23)$$

3. Finalement, calcul de  $L$ -points DFT de chaque colonne selon l'équation (2.24):

$$X(p, q) = \sum_{l=0}^{L-1} G(l, q) W_L^{lp} \quad (2.24)$$

L'algorithme peut aussi être représenté graphiquement, en utilisant un exemple d'une FFT à 15 points, avec  $m = 3$  et  $l = 5$ . La figure 2.9 explique la méthodologie utilisée :

Figure 2.9: Décomposition de 15 points FFT en 3 points et 5 points TFD [PRO96]

### II.3. ARCHITECTURE PIPELINE POUR LE CALCUL DE LA FFT

L'algorithme FFT est simplement une DFT calculée selon un algorithme permettant de réduire le nombre d'opérations et, en particulier, le nombre de multiplications à effectuer. Cependant, le bon choix de l'architecture qui exécute le traitement, permet de réduire le nombre d'opérations arithmétiques et le temps d'exécution. Il existe une variété d'architecture pour la réalisation de la FFT proposée pour l'amélioration de la vitesse de calcul et la puissance consommée. Il s'agit principalement des architectures à base de mémoires [CHN04][BAA99], en pipeline [SHO98], et les architectures parallèles [ZHA90].

Tableau 2.2: Comparaison entre les architectures des processeurs FFT

| Architecture                   | Avantages                       | Désavantages                |

|--------------------------------|---------------------------------|-----------------------------|

| Architecture pipeline          | 1- Débit élevé<br>2- Régularité | coût d'implémentation élevé |

| Architecture à base de mémoire | Faible coût<br>d'implémentation | Faible débit                |

Parmi les aspects les plus importants dans l'étude des performances que pourrait obtenir un modulateur OFDM à très haut débit multi-standard, est la réalisation matérielle de la FFT. Chacun des algorithmes considérés pour la FFT peut être réalisé par différents types d'architectures. Par conséquent, une conception performante en termes de débit et de puissance consommée passe par une bonne adéquation algorithme-architecture. L'architecture pipeline est adoptée dans le présent travail, car elle est certainement la plus apprécié pour les systèmes MIMO-OFDM (MIMO-OFDM : Multi Input Multi Output OFDM) et peut atteindre un rendement relativement élevé avec des coûts modérés du matériel.

### II.3.1. Classification des algorithmes FFT

Les algorithmes FFT peuvent être classés en trois catégories, à savoir radix-r, split-radix et radix-mixte. Pour chaque algorithme, le principe fondamental de la FFT repose sur un processus de décomposition de la DFT à calculer en DFT plus courte. Selon la manière

dont ce principe est implanté, nous considérons la décomposition dans le temps connus aussi sous le nom de l'entrelacement temporel (*Decimation- In-Time DIT*), et celle basée sur la décomposition dans le domaine de la fréquence, est aussi appelé l'entrelacement en fréquence (*Decimation-In-Frequency DIF*). Ces deux transformation reposent sur une décomposition récursive d'une transformée de  $N$  points en une séquences successive plus petites.

### II.3.2. Papillon radix-r FFT

Pour une DFT à  $N$  points puissance de 2 (2, 4, 8, etc.), il existe au moins un facteur commun entre  $M$  et  $L$ , avec  $N = ML$ . Selon les valeurs de  $M$  et  $L$ , nous considérons plusieurs variantes appelées algorithmes radix-r (base-r). Dans chaque étage de radix-r FFT, nous trouvons un module appelé, opérateur papillon (en l'anglais *Butterfly*); en le notera BPE (*Butterfly Processing Element*), où  $r$  désigne le nombre de points d'entrée du BPE, pour réaliser une FFT complète à  $N$  points. Le BPE est le cœur de calcul de la FFT, il permet de réaliser le calcul du papillon de radix-recording de la FFT.

Figure 2.10: Papillon (BPE) radix- $r$

La Figure 2.10 illustre le schéma de base d'un BPE radix- $r$ . Il faut noter que le BPE radix- $r$  utilise les opérations de base comme la multiplication complexe et l'addition ou soustraction complexe pour calculer la FFT.

### II.3.3. Architecture pipeline radix-r FFT

L'architecture en pipeline radix-r FFT (figure 2.11) est caractérisée par un traitement continu des entrées séquentielles de la FFT. Une telle architecture est composée de  $\log_r N$  modules de calcul (MC), un par étage, qui correspondent aux opérateurs papillon. La valeur de  $r$  correspond au radix de l'algorithme utilisé. Chaque MC traite  $N/r$  opérations papillon successives. Par conséquent, la taille maximale réalisable pour ce type d'architecture est dictée par le nombre de MC. En effet, ce type d'architecture offre un bon compromis complexité matérielle/taux de traitement de données pour les systèmes de communication à haut débit [JUN03].

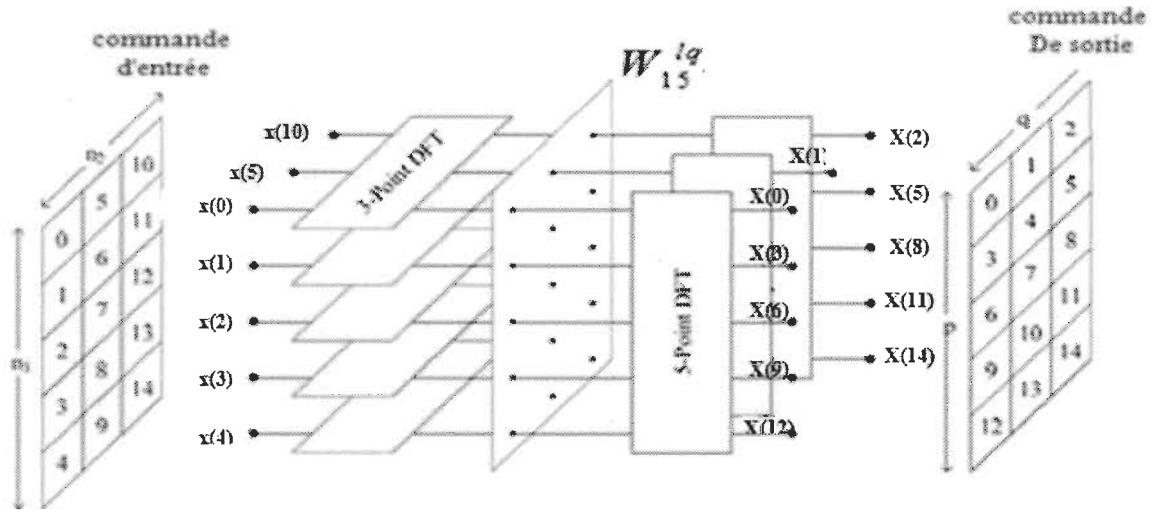

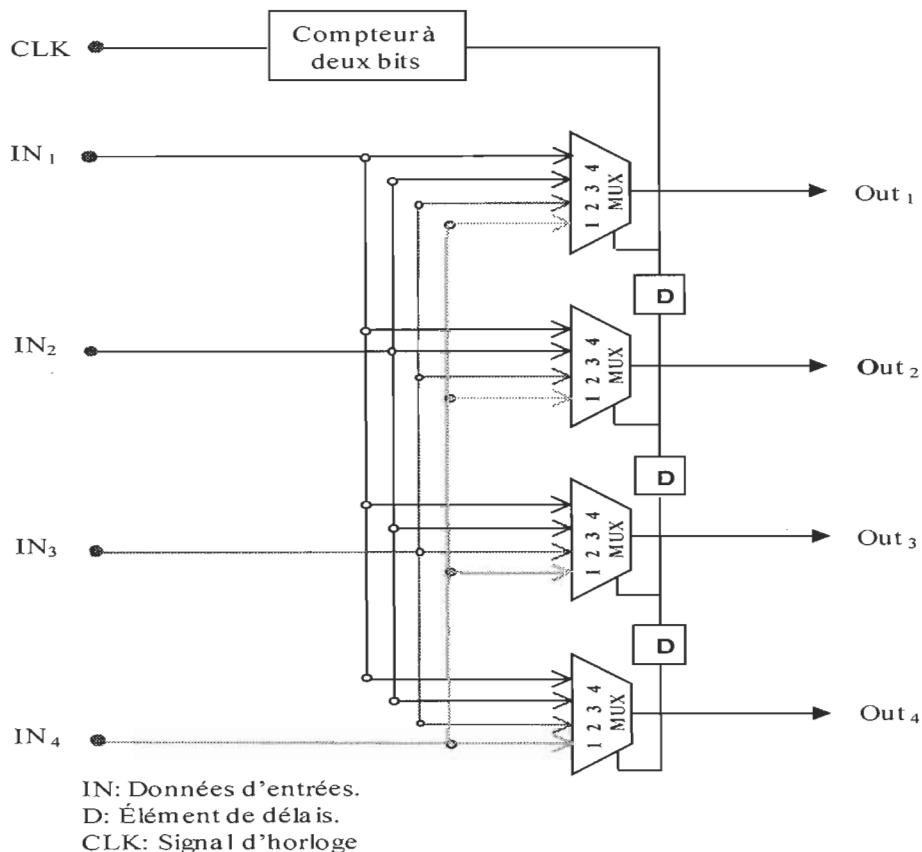

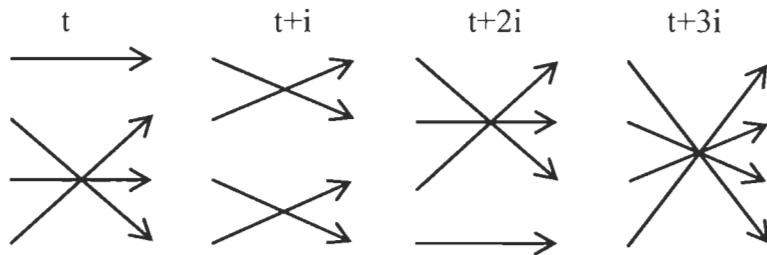

Figure 2.1: Architecture pipeline de  $S$  stages radix-r FFT [JAB09]

Selon la figure 2.11, une FFT de longueur  $N = r^S$  est exécuté d'une façon générale par  $S$  étages de calcul, constituées chacune de  $N/r$  ensembles de calcul élémentaires. Chacun de ces ensembles est effectué par un papillon radix- $r$ . Cela mène à  $\frac{N}{r} \log_r N$  ensembles de calculs élémentaires, dont les expressions différentes selon la version choisie de l'algorithme et sa base. Les blocs de commutation (en anglais : Switching) correspondent aux bus de données à partir de  $(S-1)^{\text{ième}}$  à  $(S)^{\text{ième}}$ , où  $S = \log_r N$ , pour  $s^{\text{ième}}$  itérations ( $s = 0, 1, \dots, S-1$ ). Lorsque  $r$  chemins de données sont utilisés, le BPE pipeline atteint un taux de données  $S$  fois la fréquence d'horloge inter-module. De plus, selon la figure 2.13 une FFT radix- $r$  pipeline de taille  $N$  produira les premières  $r$  sorties en  $S$  cycles. Donc, le nombre de cycles nécessaires pour compléter une FFT de taille  $N$  est par conséquent  $S + \left( \frac{n}{r} - 1 \right)$  cycles [JAB09].

Il existe plusieurs architectures en pipeline basées principalement selon deux points :

- Le premier point de différence est le nombre de chemins de données utilisés pour traiter les échantillons. Nous trouvons ainsi deux types d'architectures, à chemin unique (Single-path; S), ou à chemin multiple (Multi-path; M). Il est intéressant de noter qu'un plus grand nombre de chemins permet d'augmenter le débit de traitement au détriment d'une augmentation des ressources nécessaires.

- Le deuxième point de différence consiste en la stratégie de mémorisation pour créer les différents délais nécessaires à l'ordonnancement des échantillons.

Selon ces deux critères, nous pouvons diviser les architectures pipelines en trois types [SHO98] :

- Radix-r SDF: *Single-path Delay Feedback*.

- Radix-r SDC: *Single-path Delay Commutator*.

- Radix-r MDC: *Multi-path Delay Commutator*.

L’architecture radix-r MDC (Multi-path Delay Commutator) est l’une des approches les plus utilisées et les plus appréciées dans l’implémentation des systèmes de communication à haut débit binaire. Elle comprend un commutateur pour permuter les échantillons et des délais pour synchroniser les mêmes échantillons. Selon l’algorithme radix-r utilisé, nous aurons  $r - 1$  délais avant et après chaque module BPE. De plus, cette architecture nécessite  $r - 1$  multiplicateur par module BPE. Plusieurs architectures radix-r MDC existent, nous trouvons par exemple le R2MDC et le R4MDC qui sont les architectures les plus populaires, et aussi les radix-supérieures comme le radix- $2^2$  et radix- $2^3$ . Chacun de ces algorithmes est étudié de façon à être optimisé suivant certaines conditions. De plus, l’approche MDC est l’architecture la plus adaptée aux systèmes MIMO-OFDM parce qu’elle possède un multiple chemin d’entrées et de sorties [FU09]. Cette propriété permet aux modules FFT utilisant cette architecture d’opérer à haute vitesse avec un haut débit. Par contre, cette architecture utilise plus de surface silicium et par conséquent un cout plus élevé en matériel. Le choix d’algorithme de haut degré pour la FFT est en lui-même un choix permettant de réduire la consommation. Plus le degré est haut, plus le nombre de multiplications complexes triviales augmente. Dans ce travail, nous avons choisi

l'algorithme radix-4MDC pour le calcul de la FFT dans le but d'optimiser ces performances tel que la surface d'implémentation et la consommation d'énergie qui sont particulièrement important pour les communications sans fil basées sur les systèmes MIMO-OFDM.

### II.3.4. Algorithme FFT radix-4 MDC

Depuis l'algorithme initial [COO65], différentes architectures, plus ou moins rapides et plus ou moins coûteuses, ont été proposées pour effectuer le calcul et réduire davantage la complexité de la FFT. Dans la suite de ce travail, nous utiliserons l'algorithme de radix-4 détaillé dans [PRO96], où 4 factorise  $N$ .

#### II.3.4.1. Algorithme radix-4 DIT

Nous pouvons toujours utiliser l'algorithme radix-2 pour le calcul de la FFT. Toutefois, l'utilisation des algorithmes radix-r supérieurs permet de réduire le nombre d'étage pipeline et le nombre d'opérations. L'amélioration de la complexité de calcul nous a conduits à mettre en application le radix-4 FFT dont le nombre de points de données est une puissance de 4 c.-à-d.  $N = 4^v$  où  $v$  est un entier positif.

Brièvement, la description de l'algorithme radix-4 FFT DIT est obtenue en utilisant l'approche divisée pour régner décrite précédemment. Nous considérons les données des constantes suivantes :

$$\left\{ \begin{array}{l} L = 4, \quad M = \frac{N}{4} \\ l, p = 0, 1, 2, 3, 4 \\ m, q = 0, 1, \dots, \frac{N}{4} - 1 \\ n = 4m + 1, \quad k = \frac{N}{4} \end{array} \right. \quad (2.25)$$

Nous remplaçons les données de la relation (2.25) dans l'équation (2.21) tout en séparant une séquence de  $N$  points d'entrées en 4 sous-séquences  $X(4n), X(4n+1), X(4n+2), X(4n+3)$ ,

où  $n = 0, 1, \dots, \frac{N}{4} - 1$ . En obtient donc :

$$X(p, q) = \sum_{i=0}^4 [W_N^{iq} F(l, q)] W_4^{lp} \quad p = 0, 1, 2, 3, 4 \quad (2.26)$$

Avec  $F(l, q)$  est donné par l'équation (2.27) :

$$F(l, q) = \sum_{m=0}^{\frac{N}{4}} X(l, m) W_{N/4}^{mq} \quad \begin{array}{l} l = 0, 1, 2, 3, 4 \\ q = 0, 1, \dots, \frac{N}{4} - 1 \end{array} \quad (2.27)$$

$$\left\{ \begin{array}{l} x(l, m) = x(4m + l) \\ X(p, q) = X\left(\frac{N}{4}p + q\right) \end{array} \right. \quad (2.28)$$

Et :

Ainsi, la DFT à quatre  $N/4$  points  $F(l, q)$  est obtenus à partir de l'équation (2.26) sont organisés pour donner les  $N$  points DFT. L'expression pour arranger les  $N/4$  points DFT sont exprimés sous forme matricielle comme suite :

$$\begin{bmatrix} X(0,q) \\ X(1,q) \\ X(2,q) \\ X(3,q) \end{bmatrix} = \begin{bmatrix} 1 & 1 & 1 & 1 \\ 1 & -j & -1 & j \\ 1 & -1 & 1 & -1 \\ 1 & j & -1 & -j \end{bmatrix} \begin{bmatrix} W_N^0 F(0,q) \\ W_N^q F(1,q) \\ W_N^{2q} F(2,q) \\ W_N^{3q} F(3,q) \end{bmatrix} \quad (2.29)$$

L'algorithme FFT radix-4, est donc une décomposition de DFT en quatre sous transformés indépendants de taille  $N/4$ . La structure typique de BPE radix-4 suivant l'algorithme décrit dans l'équation 2.28 est représenté par la figure 2.12. Ainsi sa forme simplifiée est illustrée dans la figure 2.13.

Figure 2.22: Diagramme typique de papillon radix-4 DIT

Figure 2.3: la forme simplifiée de papillon radix-4 DIT

Il est à noter que chaque BPE implique 3 multiplications complexes et 12 additions complexes. Nous excluons les opérations impliquant les opérateurs triviaux  $j$  et  $-j$  pouvant être résolue par une simple manipulation de signes des partie réel et imaginaire. La figure 2.14 représente la structure de radix-4 DIT avec  $N=16$ , les entrées sont à bits inversées tandis que les sorties sont présentés dans un ordre normal.

Figure 2.4: Diagramme de la FFT à base de Butterfly Radix4 de type DIT N=16

#### II.3.4.2. Algorithme radix-4 DIF

si nous voulons avoir la structure de radix-4 DIF, nous remplaçons dans l'équation (2.21)  $L = N/4$  et  $M = 4$ . Nous dérivons l'algorithme radix-4 DIF en divisant les  $N$  données d'entrée en quatre petites séquences élémentaires, nous avons donc :

$$\begin{aligned}

X(k) &= \sum_{n=0}^{N-1} x(n) W_N^{kn} \\