UNIVERSITÉ DU QUÉBEC

MÉMOIRE PRÉSENTÉ À

L'UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

COMME EXIGENCE PARTIELLE

DE LA MAÎTRISE EN GÉNIE INDUSTRIEL

PAR

SERGE LAMBERT

IMPLANTATION D'UN SYSTÈME DE PRODUCTION À VALEUR AJOUTÉE (J.A.T.) ET DE

L'INGÉNIERIE SIMULTANÉE CHEZ LES SYSTÈMES ÉLECTRONIQUES MATROX LTÉE.

MAI 1997

Université du Québec à Trois-Rivières

Service de la bibliothèque

Avertissement

L'auteur de ce mémoire ou de cette thèse a autorisé l'Université du Québec à Trois-Rivières à diffuser, à des fins non lucratives, une copie de son mémoire ou de sa thèse.

Cette diffusion n'entraîne pas une renonciation de la part de l'auteur à ses droits de propriété intellectuelle, incluant le droit d'auteur, sur ce mémoire ou cette thèse. Notamment, la reproduction ou la publication de la totalité ou d'une partie importante de ce mémoire ou de cette thèse requiert son autorisation.

## RÉSUMÉ

Le présent projet origine du désir de LES SYSTÈMES ÉLECTRONIQUES MATROX LTÉE d'améliorer son système de production. Le Juste-à-Temps et l'Ingénierie Simultanée sont les deux méthodes proposées à l'entreprise pour atteindre ce but. La recherche décrite dans cet ouvrage est divisée en quatre parties. La première partie est une mise à niveau de l'entreprise pour pouvoir fonctionner en Juste-à-Temps. Les résultats de cette partie sont présentés dans un rapport confidentiel. Le système de production étudié dans les deux prochaines parties est une ligne d'assemblage SMT. La deuxième partie traite de la flexibilité et a été réalisée par un autre étudiant, M. Bernard Cyr. La troisième partie qui est présentée dans ce mémoire tente de déterminer les règles d'ordonnancement appropriées aux différentes conditions du système de production à l'étude. Finalement, la quatrième partie porte sur l'Ingénierie Simultanée et sera traitée par un autre étudiant de maîtrise. La recherche de la partie trois est divisée en deux expériences qui ont été réalisées par simulation. Les variables étudiées dans la première expérience sont la méthode de groupement des produits en famille, la capacité des machines pour recevoir des cassettes, le facteur de similarité entre les produits, la réduction du nombre de pièces par plaquette et les règles d'ordonnancement interfamilles et intrafamille. La deuxième expérience étudie l'effet de plusieurs règles d'ordonnancement interfamilles et intrafamille en fonction des deux méthodes de groupement. Les mesures de performance sont le niveau des en-

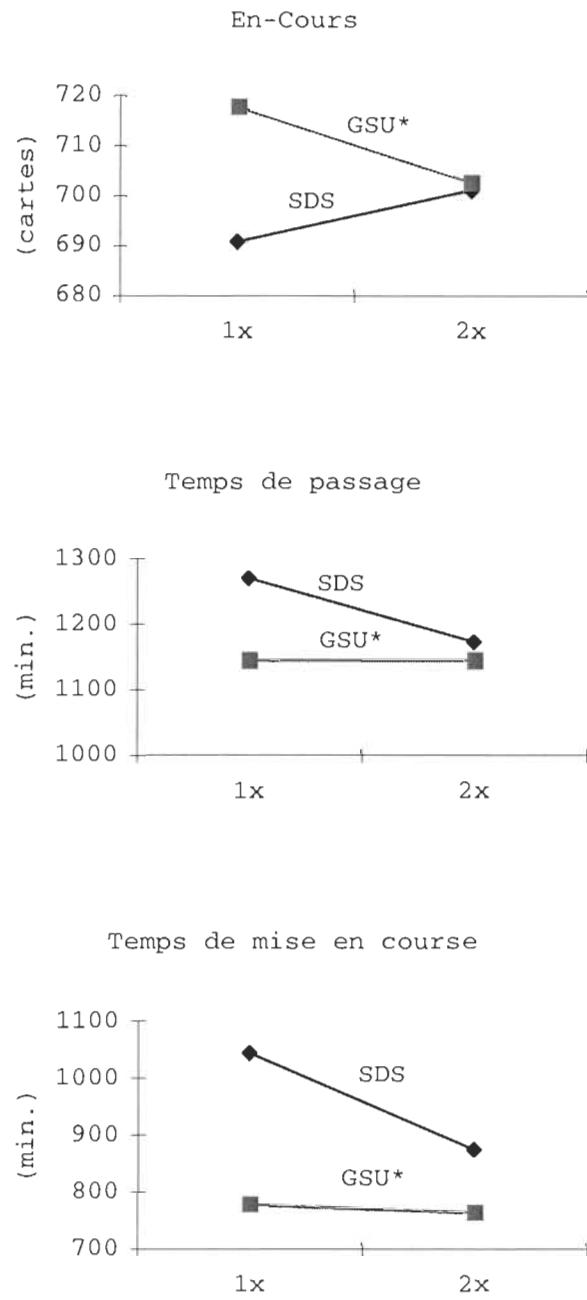

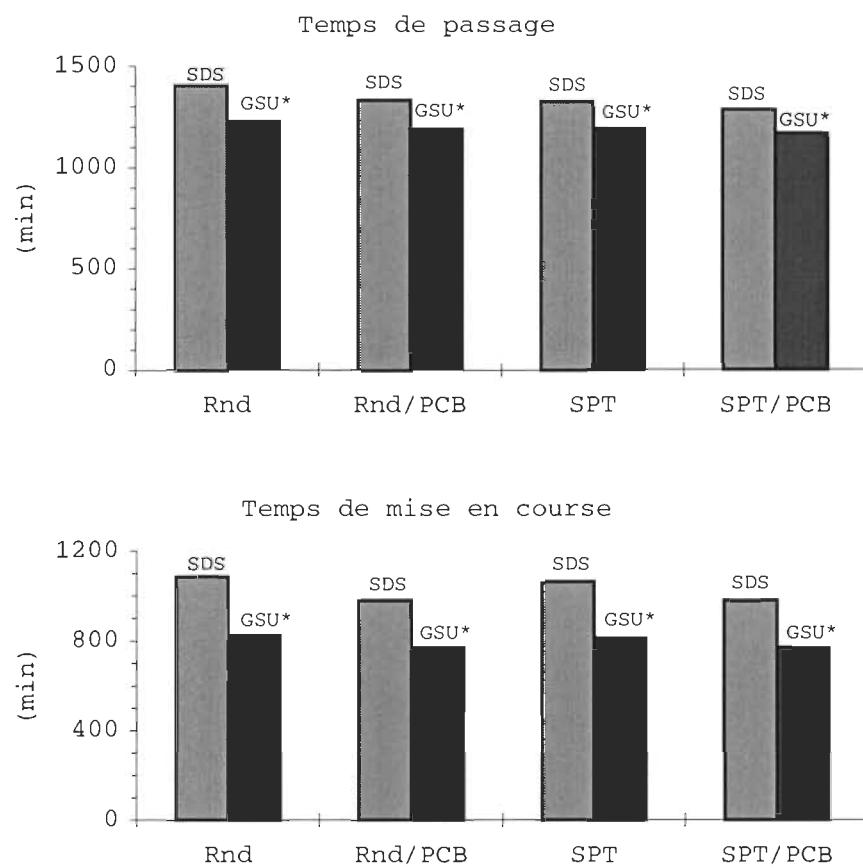

cours moyen, les temps de passage moyens et les temps de mise en course. Un modèle de simulation AWESIM comportant des ajouts écrits en C a été utilisé pour obtenir les résultats. La validation du modèle a été faite en comparant les résultats obtenus avec ceux du système réel. L'analyse des résultats a été faite par traitement statistique. Les résultats du modèle de simulation sont très significatifs pour chacune des mesures ( $r$ -carré > 0.919). La méthode de groupement GSU\* réduit de 19.9% le temps de mise en course par rapport à SDS. Les règles d'ordonnancement intrafamille SPT/PCB et interfamilles FSPT permettent de réduire le temps de passage peu importe la méthode de groupement utilisée malgré une légère augmentation du niveau des en-cours. Pour conclure, la recherche devrait être poursuivie concernant l'algorithme de formation des familles, la quantité optimale d'espace cassettes à allouer avec GSU\* et l'élimination du facteur de similarité.

## REMERCIEMENTS

Le Conseil de Recherches en Sciences Naturelles et Génie du Canada pour le soutien financier apporté par le biais d'une bourse à incidence industrielle.

MM. Nadim Bakhach et Bernard Cyr de Les Systèmes Électroniques Matrox Ltée pour avoir rendu cette recherche possible.

Les chercheurs Georges Abdulnour et Jocelyn Drolet de La Chaire Bombardier Sea-Doo/Ski-Doo en changement technologique de l'Université du Québec à Trois-Rivières pour leur appui durant la recherche.

## TABLE DES MATIÈRES

|                                         | PAGE |

|-----------------------------------------|------|

| RÉSUMÉ . . . . .                        | ii   |

| REMERCIEMENTS . . . . .                 | iv   |

| LISTE DES TABLEAUX . . . . .            | vii  |

| LISTE DES FIGURES . . . . .             | viii |

| LISTE DES ABRÉVIATIONS . . . . .        | x    |

| CHAPITRE                                |      |

| I. DÉFINITION DU PROJET. . . . .        | 1    |

| 1. Introduction . . . . .               | 1    |

| 2. Problématique. . . . .               | 2    |

| 3. Définition du problème . . . . .     | 3    |

| 4. Stratégie de solution. . . . .       | 4    |

| II. RECHERCHE BIBLIOGRAPHIQUE . . . . . | 7    |

| 1. Introduction . . . . .               | 7    |

| 2. Juste-à-Temps. . . . .               | 8    |

| 3. Technologie de groupe. . . . .       | 16   |

| 4. Ingénierie Simultanée. . . . .       | 18   |

| III. PLAN DE L'EXPÉRIENCE. . . . .      | 27   |

| 1. Description du système . . . . .     | 27   |

| 2. Expérimentation. . . . .             | 32   |

| 3. Approche de la recherche . . . . .   | 38   |

| IV. MODÈLE DE SIMULATION. . . . .       | 39   |

| 1. Description du modèle. . . . .       | 39   |

|                                          |     |

|------------------------------------------|-----|

| 2. Validation. . . . .                   | 40  |

| V. ANALYSE DES RÉSULTATS . . . . .       | 43  |

| 1. Expérience 1 . . . . .                | 43  |

| 2. Expérience 2 . . . . .                | 60  |

| VI. CONCLUSION. . . . .                  | 74  |

| 1. Discussion . . . . .                  | 74  |

| 2. Conclusion . . . . .                  | 76  |

| 3. Recommandations. . . . .              | 78  |

| BIBLIOGRAPHIE. . . . .                   | 80  |

| ANNEXES                                  |     |

| A. DESCRIPTIONS DES PROGRAMMES . . . . . | 84  |

| B. PROGRAMME DE SIMULATION . . . . .     | 102 |

| C. SAS EXPÉRIENCE 1. . . . .             | 124 |

| D. SAS EXPÉRIENCE 2. . . . .             | 142 |

## LISTE DES TABLEAUX

|                                                                           | PAGE |

|---------------------------------------------------------------------------|------|

| 1. Règles d'ordonnancement . . . . .                                      | 19   |

| 2. Caractéristiques de l'IS. . . . .                                      | 21   |

| 3. Espace cassettes des machines . . . . .                                | 28   |

| 4. Temps de mises en course. . . . .                                      | 30   |

| 5. Caractéristiques des composantes du système . . . . .                  | 30   |

| 6. Variables et niveaux de l'expérience 1. . . . .                        | 35   |

| 7. Variables et niveaux de l'expérience 2. . . . .                        | 37   |

| 8. Attributs de collecte de données. . . . .                              | 40   |

| 9. Attributs de contrôle de la simulation. . . . .                        | 41   |

| 10. Analyse de variance du niveau d'en-cours Expérience 1 . . . . .       | 47   |

| 11. Analyse de variance du temps de passage Expérience 1. . . . .         | 48   |

| 12. Analyse de variance du temps de mise en course Expérience 1 . . . . . | 49   |

| 13. Analyse de Duncan Expérience 1. . . . .                               | 50   |

| 14. Résultats sans groupement de produits . . . . .                       | 64   |

| 15. Résultats des méthodes de groupement Expérience 2 . . . . .           | 64   |

| 16. Analyse de Duncan Expérience 2. . . . .                               | 65   |

| 17. Analyse de variance du niveau d'en-cours Expérience 2 . . . . .       | 66   |

| 18. Analyse de variance du temps de passage Expérience 2. . . . .         | 67   |

| 19. Analyse de variance du temps de mise en course Expérience 2 . . . . . | 68   |

| 20. Effet des variables sur la méthode de groupement. . . . .             | 75   |

## LISTE DES FIGURES

|                                                                                                 | PAGE |

|-------------------------------------------------------------------------------------------------|------|

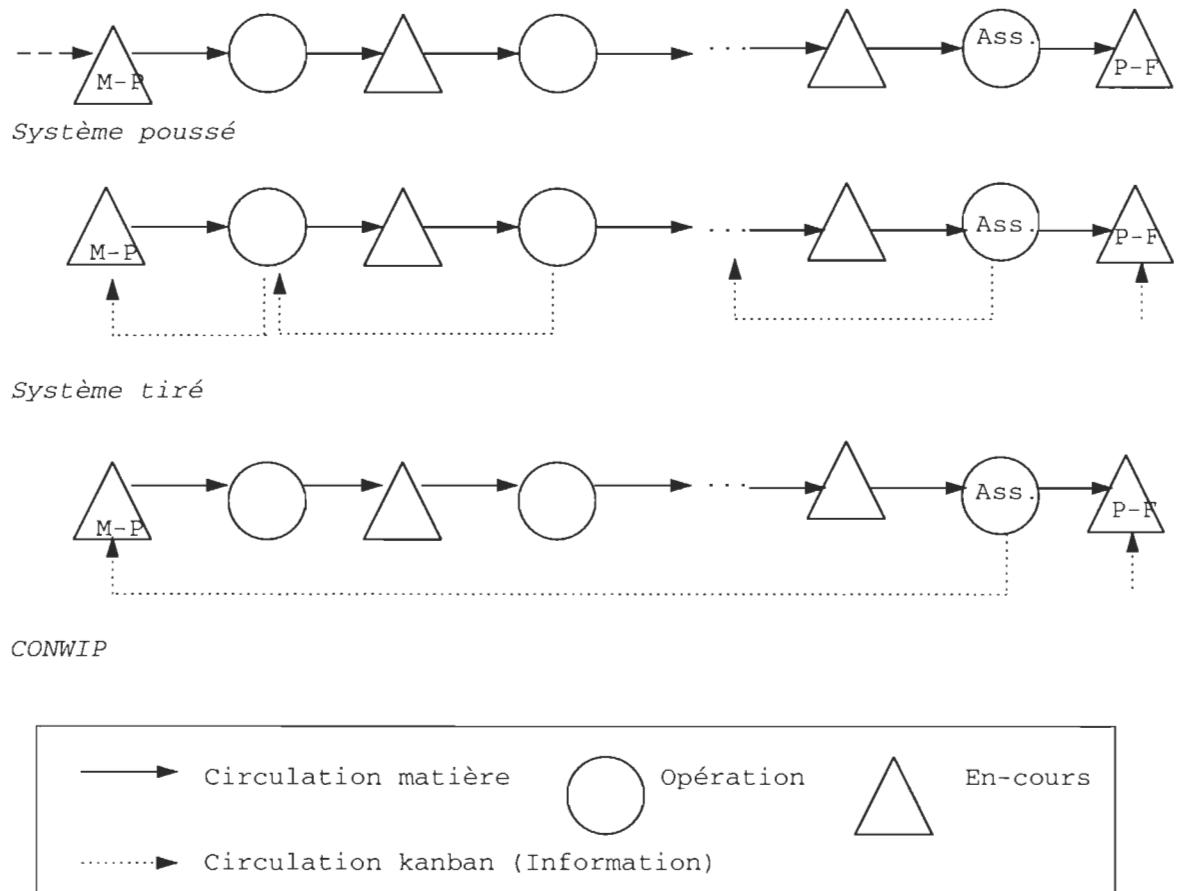

| 1. Système poussé, tiré et CONWIP. . . . .                                                      | 13   |

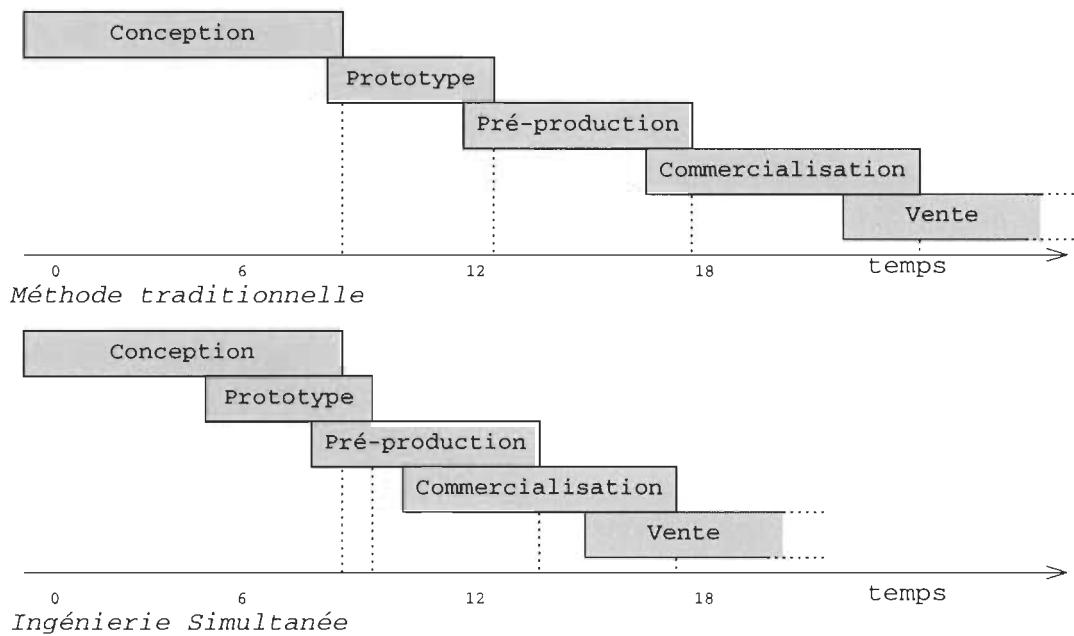

| 2. Méthode traditionnelle vs Ingénierie Simultanée . . . . .                                    | 20   |

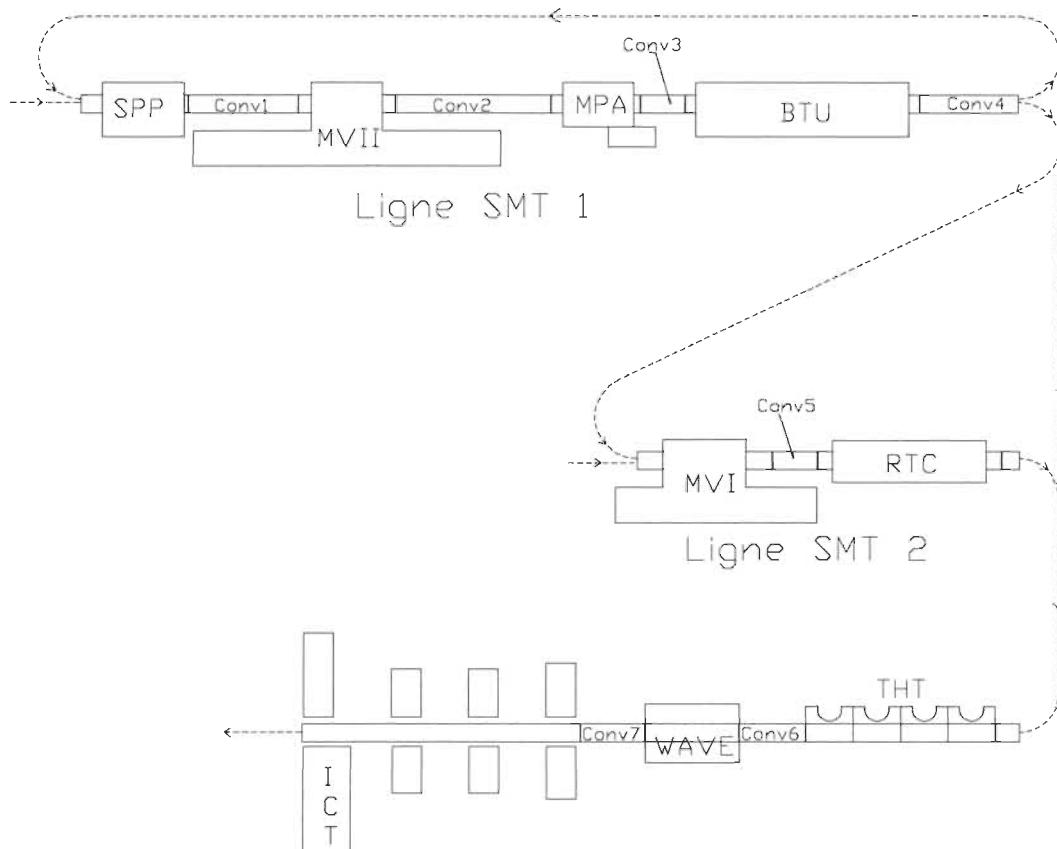

| 3. Disposition du système de production. . . . .                                                | 28   |

| 4. Modèle de simulation. . . . .                                                                | 42   |

| 5. Niveau des méthodes de groupement Expérience 1. . . . .                                      | 51   |

| 6. Niveau de capacités des cassettes Expérience 1. . . . .                                      | 52   |

| 7. Niveau du facteur de similarité Expérience 1. . . . .                                        | 53   |

| 8. Niveau de la réduction de pièces. . . . .                                                    | 54   |

| 9. Niveau de l'ordonnancement interfamilles Expérience 1 . . . . .                              | 54   |

| 10. Niveau de l'ordonnancement intrafamille Expérience 1. . . . .                               | 55   |

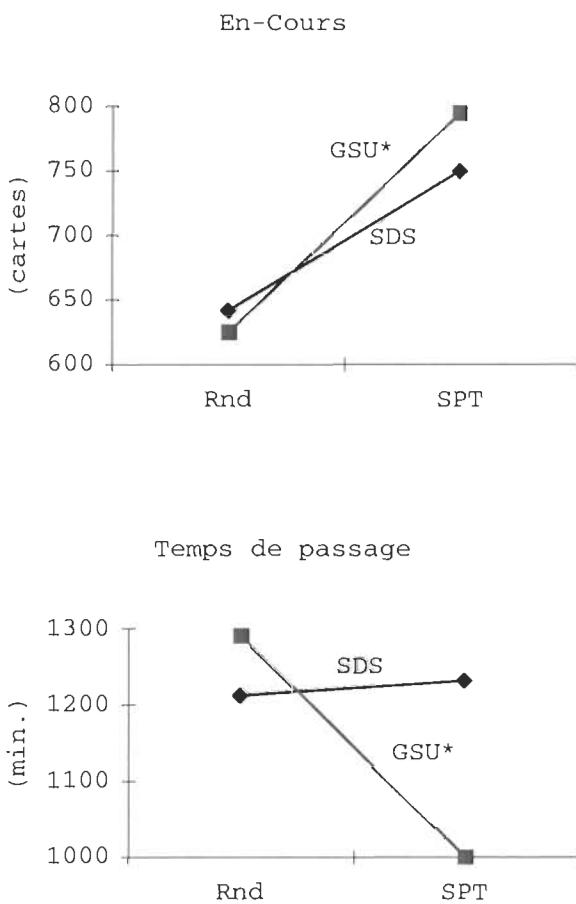

| 11. Interaction méthodes de groupement et capacités des cassettes . . . . .                     | 56   |

| 12. Interaction méthode de groupement et facteur de similarité. . . . .                         | 57   |

| 13. Interaction méthode de groupement et réduction de pièces. . . . .                           | 58   |

| 14. Interaction méthode de groupement et ordonnancement<br>interfamilles Expérience 1. . . . .  | 58   |

| 15. Interaction méthode de groupement et ordonnancement<br>intrafamille Expérience 1 . . . . .  | 59   |

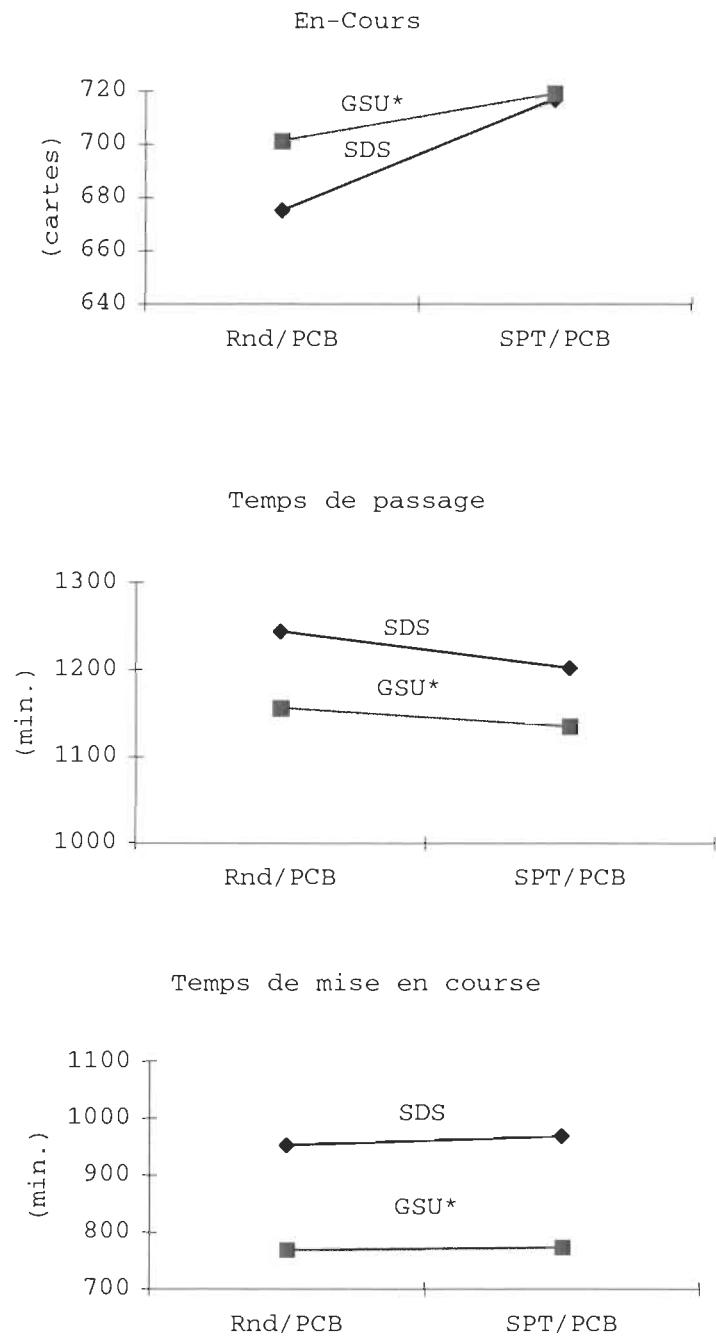

| 16. Niveau des méthodes de groupement Expérience 2. . . . .                                     | 69   |

| 17. Niveau de l'ordonnancement interfamilles Expérience 2 . . . . .                             | 70   |

| 18. Intrafamille sans formation de famille. . . . .                                             | 71   |

| 19. Interaction méthodes de groupement et ordonnancement<br>interfamilles Expérience 2. . . . . | 72   |

|                                                                                                 |    |

|-------------------------------------------------------------------------------------------------|----|

| 20. Interaction méthodes de groupement et ordonnancement<br>intrafamille Expérience 2 . . . . . | 73 |

| 21. Programme Setfam10. . . . .                                                                 | 86 |

## LISTE DES ABRÉVIATIONS

|        |                                                 |

|--------|-------------------------------------------------|

| JAT    | Juste-à-Temps                                   |

| MRP    | Planification des besoins matières              |

| MRPLXL | Planification des besoins matières lot pour lot |

| CONWIP | Constant work-in-process                        |

| M-P    | Matière première                                |

| Ass.   | Département d'assemblage                        |

| SDS    | Sequence dependent scheduling                   |

| GSU    | Group set-up                                    |

| SPT    | Shortest processing time                        |

| FCFS   | Fisrt-come, first served                        |

| MJ     | Most jobs                                       |

| EDD    | Earliest due date                               |

| SI     | Shortest imminent operation                     |

| ECON   | Economic tradeoff                               |

| MW     | Most work                                       |

| NJNL   | # jobs plus # late jobs                         |

| DK     | Due date switching                              |

| IS     | Ingénierie simultanée                           |

| PCB    | Printed circuit board                           |

| SMT    | Surface mount technology                        |

| THT    | Through hole technology                         |

| Rnd    | Random (Aléatoire)                              |

| FSPT   | Family with the shortest processing time        |

## CHAPITRE I

### DÉFINITION DU PROJET

#### Introduction

Le présent projet de recherche provient d'une demande d'une entreprise oeuvrant dans l'industrie électronique. Ce projet fait parti d'un ensemble de projets qui ont été menés conjointement par plusieurs étudiants de maîtrise et chercheurs de l'université.

En effet, le secteur électronique fait face depuis quelques années à une compétition féroce dans tous les domaines, en plus de l'internationalisation des marchés. La réduction de la durée de vie des produits et des marges bénéficiaires sont les principaux effets ressentis dans l'industrie. Comme si cela ne suffisait pas, ils doivent satisfaire des clients qui veulent plus d'options (variétés). La conséquence directe étant une plus grande variété de produits à assembler et à gérer et du même coup des plus petits lots de production.

En électronique, le procédé d'assemblage de circuits imprimés consiste à placer des pièces sur un circuit imprimé (Printed Circuit Board) pour ensuite les souder. Par contre, le procédé de fabrication varie en fonction du type de technologie de pièces à assembler. Peu importe la technologie, la distinction se fait au niveau du placement des composantes sur le PCB, soit le placement en surface des pièces (Surface Mount Technology, SMT) ou le placement à travers du PCB (Through Hole

Technology, THT). Ces deux technologies sont utilisées chez Matrox. Certains produits peuvent nécessiter l'utilisation des deux technologies à différents degrés. La division de fabrication de Matrox possède deux lignes de production. La première ligne est dédiée au SMT tandis que la deuxième ligne sert pour le THT.

### Problématique

Étant donné l'évolution constante et rapide des secteurs informatique et électronique, les produits conçus et fabriqués chez Matrox ont un cycle de vie réduit. Un autre point particulier à Matrox est qu'elle fabrique à la fois des produits à haut volume et plusieurs produits à bas volume. Ce phénomène a amené l'entreprise à faire des familles de produits pour minimiser les temps de mise en course. De plus, certaines composantes sont difficiles à obtenir puisqu'elles ont un délai de livraison de 6 à 12 mois. Ainsi, il devient primordial pour l'entreprise d'augmenter la flexibilité de ses lignes de production, de réduire ses stocks et le temps de passage de ses produits dans l'usine, de réduire le temps écoulé entre l'étape de conception, de production et de commercialisation en adoptant un système de gestion pro-actif pour faire face à la compétition internationale.

Pour répondre à ces exigences, deux systèmes de gestion semblent être désignés pour projeter l'entreprise vers l'amélioration continue et lui permettre de rester un chef de file dans ces domaines d'activités, ils sont le Juste-à-Temps et l'ingénierie simultanée.

## Définition du problème

### But

Développer un modèle générique d'implantation de nouvelles technologies par projet.

### Objectif

La recherche est divisée en quatre parties, la révision du système de production, la flexibilité, l'ordonnancement et l'ingénierie simultanée.

#### Partie 1: Révision du système de production (Benchmarking)

Avant d'implanter un système de production Juste-à-Temps, une analyse du système de production actuel a été effectuée. Suite aux résultats de cette première étape, une stratégie d'implantation basée sur une technique de gestion de projet et d'avancement par activités selon un réseau de préséance établi a été développée.

#### Partie 2: La flexibilité

Cette partie veut déterminer l'effet de l'application des technologies de groupe sur l'environnement de Matrox. Elle étudiera les différentes méthodes de groupement de produit et les variables pouvant affecter celles-ci.

#### Partie 3: L'ordonnancement

Cette partie de la recherche étudie l'impact des différentes politiques d'ordonnancement qui se prêtent bien au Juste-à-Temps et à l'environnement de Matrox. L'étude déterminera l'effet des règles d'ordonnancement sur des variables assurant la flexibilité au système de

production modélisé. La solution retenue sera intégrée aux outils du système de planification de la production de l'entreprise.

#### Partie 4: L'ingénierie simultanée

La première étape pour la mise en place de l'ingénierie simultanée consistera à évaluer les besoins en information, ses utilisateurs et à quel moment dans le temps ils ont besoin des informations. Suite à cela, un modèle de système d'information tenant compte de ces éléments sera élaboré avec une stratégie d'implantation.

#### Stratégie de solution

Pour la réussite de cette recherche, il est important d'adopter une stratégie bien définie avant de s'attaquer au problème. La simulation, la recherche appliquée, l'expérimentation (design expérimental) et les méthodes évaluatives seront utilisées durant ce projet. Les quatre parties seront traitées de façons différentes.

#### Juste-à-Temps

Cette partie de la recherche se veut une mise à niveau de l'entreprise pour pouvoir fonctionner en JAT. Au tout début, un questionnaire et une méthode de travail pour caractériser l'entreprise a été développés. Le questionnaire utilisé et la méthode de travail s'y rattachant tentent de répondre aux besoins particuliers de l'entreprise. Ensuite, l'évaluation de l'entreprise a été faite à l'aide de ce questionnaire. Les éléments soulevés comme devant être corrigés sont devenus des projets à l'implantation du Juste-à-Temps pour la composante production. Selon les secteurs, ces projets seront revus à l'aide d'outils de génie industriel, comme la fiabilité, l'ergonomie, la

qualité, la réduction des temps de mise en course, et bien d'autres. Chaque projet ou activité est positionné dans un réseau de préséance selon sa priorité et sa criticité. L'étude des réponses du questionnaire révèle aussi les besoins des gestionnaires de la production. Cette première partie a déjà été complétée et fait partie d'un rapport confidentiel présenté à l'entreprise (Lambert (1996)). Plusieurs des projets découlant des recommandations ont été réalisés ou sont en évaluation.

### Flexibilité

La partie sur la flexibilité et la partie sur l'ordonnancement ont été intégrées dans une seule expérience basée sur un plan factoriel d'expérimentation dans le but de cerner l'effet des variables choisies ainsi que leur interaction sur la performance du système. La description de la flexibilité et l'analyse des résultats portant sur la flexibilité sont présentées dans Cyr (1997).

### Ordonnancement

Cette partie est celle qui sera traitée dans le reste de ce rapport. Le Juste-à-Temps demande beaucoup de changement et l'ordonnancement n'y échappe pas non plus. Ainsi, plusieurs propositions de systèmes de planification de la production, de suivi et de contrôle seront élaborées en tenant compte de différentes règles d'ordonnancement. Les règles premier arrivé, premier servi, le temps le plus court et les dates dues le plus tôt seront analysées avec possiblement une seconde règle pour empêcher qu'une commande ne passe trop de temps en attente. Un modèle de simulation pour les différentes propositions de systèmes a été élaboré. En premier lieu, une simulation avec les différents modèles a été faite et a servi à établir les paramètres de base communs à tous les modèles.

La ligne de production actuelle a été simulée et sert comme point de référence lors de la comparaison et de l'analyse des résultats. Ensuite, l'évaluation des systèmes pour les paramètres expérimentaux retenus a été faite par simulation et comparée au système de production actuel. Les mesures de performance étudiées sont le temps de passage, le niveau d'en-cours, l'utilisation des machines et le niveau de service. Enfin, la solution retenue sera testée en production pour valider les résultats obtenus par la simulation.

#### Ingénierie Simultanée

Quant à l'ingénierie simultanée, le projet consiste à déterminer quels sont les éléments ayant de l'importance pour l'entreprise. Un des éléments-clés à la réussite, après l'engagement de la haute direction, est le système d'information. Pour ce faire, les besoins en information, les utilisateurs et à quel moment ils ont besoin de cette information seront recueillis à l'aide de questionnaires et d'entrevues. À partir des données obtenues, un nouveau système d'information sera proposé. Finalement, une stratégie d'implantation répondant aux besoins de Matrox sera développée. Compte tenu de son ampleur, seulement une brève recherche bibliographique sera faite puisque ce projet sera effectué ultérieurement par un autre étudiant de maîtrise.

Le chapitre suivant présente la recherche bibliographique pour les parties de la recherches décrites ci-dessus qui seront traitées par la suite.

CHAPITRE II

RECHERCHE BIBLIOGRAPHIQUE

Introduction

Pour réussir de nos jours l'entreprise n'a plus le choix, elle doit revoir sa façon de faire les choses. La philosophie de production dite Juste-à-Temps, l'optimisation de l'ordonnancement par de nouvelles méthodes et l'Ingénierie Simultanée sont des moyens à la disposition de l'entreprise pour assurer la continuité de son succès. Ces trois notions seront approfondies tout au long de ce chapitre.

Le succès des Japonais dans tous les secteurs n'a laissé personne indifférent. Une des raisons de leur réussite est attribuée à la philosophie de production dite Juste-à-Temps. L'étude portera sur plusieurs points; les éléments-clés du Juste-à-Temps, une comparaison du Juste-à-Temps avec les autres approches de production, les facteurs de succès en Juste-à-Temps et la stratégie d'implantation. L'assignation de pièces aux machines est un problème particulier au domaine de l'électronique. De plus, l'utilisation des technologies de groupe combinées à des règles d'ordonnancement est importante pour pouvoir offrir plus de diversités de produits et en petites quantités. Le dernier outil analysé est l'Ingénierie Simultanée. L'étude portera sur son importance et ses bénéfices, ses éléments, et finalement sur la stratégie et les étapes d'implantation.

### Juste-à-Temps

Le concept du Juste-à-Temps n'est pas nouveau. En effet, Henry Ford en 1926 dans son livre "Today and Tomorrow" expliquait une usine où les bateaux déchargeraient le minerai de fer pour fabriquer l'acier et que 48 heures plus tard au bout d'une ligne de production roulerait une voiture prête à être vendue. C'est exactement ce que les Japonais ont fait après la deuxième guerre mondiale et le reste de l'histoire, tout le monde la connaît.

Le Juste-à-Temps est défini par Wantuck (1989) comme étant une stratégie de production qui demande de nouvelles valeurs pour permettre de continuellement améliorer la qualité et la productivité, c'est-à-dire donner à l'entreprise une nouvelle philosophie ou culture d'entreprise. Fisher (1995), quant à lui, mentionne que c'est une philosophie de production basée sur l'élimination des pertes au niveau des ressources et l'amélioration continue de la productivité.

Dans les prochaines sections une stratégie en 7 points sera expliquée, ensuite le Juste-à-Temps sera comparé avec les autres méthodes traditionnelles, des outils de travail en Juste-à-Temps suivront et finalement une stratégie d'implantation sera présentée.

### Stratégie du JAT

Cette section présente 7 principes de base pour réussir et les pièges à éviter.

Le Juste-à-Temps met l'accent sur la simplicité et la flexibilité. Pour ce faire Wantuck (1989) définit les sept principes suivants:

1. Produire ce que le client désire: Ce principe demande de la flexibilité de la part de l'entreprise. Elle doit être en mesure de répondre rapidement à une commande d'un client. Il ne sert à rien de produire selon les prévisions de vente, il est préférable d'investir dans la flexibilité manufacturière que dans des stocks qui ne seront pas vendus si les prévisions sont erronées.

2. Éliminer toutes les pertes: Les pertes sont définies comme tous les efforts superflus au niveau de l'usine, des matières et des travailleurs que ceux requis par la production. Il y a plusieurs sources de pertes, comme le non-équilibrage des tâches (machine ou opérateur), la mauvaise synchronisation des activités, les opérateurs en trop, l'excédent de capacité pour un équipement, une maintenance préventive insuffisante, les défauts et retouches et la surproduction.

3. Produire un à la fois: À long terme, l'entreprise doit chercher à produire des lots unitaires. Ce changement demande beaucoup de temps et d'autres éléments doivent être améliorés pour atteindre cet objectif. Les avantages seront la diminution des inventaires, du temps de passage des commandes et des délais de livraison.

4. Amélioration continue: L'amélioration continue est un projet sans fin. Elle consiste à se fixer des objectifs. Lorsqu'un objectif est atteint, un nouvel objectif doit être défini. C'est un processus sans fin.

5. Respect des gens: En Juste-à-Temps, tout le monde contribue et participe à l'amélioration continue. Chacun a du potentiel et doit se sentir comme faisant partie de l'entreprise.

6. Aucune contingence: L'entreprise ne doit pas ajouter des inventaires au cas où, car c'est de la perte. Ainsi, chaque ressource doit être utilisée à sa capacité requise.

7. Mettre l'accent sur le long terme: Avoir une vision long terme est très important, car le Juste-à-Temps est une stratégie qui demande du temps pour son implantation.

La qualité à la source est très importante et vise à ne produire que des bonnes pièces. Ainsi, la personne qui ajoute la valeur est entièrement responsable de la qualité de son produit.

Zygmont (1989) mentionne qu'il existe toujours des perceptions erronées sur ce qu'est le Juste-à-Temps. Une première est que certaines personnes le voient seulement comme un outil de gestion des inventaires qui prend la forme d'un kanban. Aussi, d'autres personnes disent qu'il ne peut pas fonctionner en Amérique à cause de la différence de culture qu'il y a avec celle des Japonais. Enfin, il y a des personnes qui pensent que ça touche seulement le secteur de la fabrication. Pourtant les politiques d'approvisionnement et le partenariat avec les fournisseurs sont également des facteurs de réussite.

#### Comparaison

Il existe deux types de systèmes de production qui sont caractérisés par la façon dont l'approvisionnement aux postes de travail est fait, le système à flux poussé et le système à flux tiré.

Le système de production le plus rencontré en Amérique est celui dit à flux poussé. Ce système fait en sorte que lorsqu'une commande est relâchée en production elle commence au premier poste et celui-ci pousse les lots de production au poste suivant, ainsi de suite jusqu'à ce qu'elle atteigne l'expédition. À la base du système, il y a un système de prévision et de planification des besoins matières (MRP) qui éclate la

demande jusqu'au plus bas niveau de la nomenclature du produit pour déterminer les ordres d'achats et de fabrication.

La méthode de planification des besoins matières lot pour lot (MRPLXL) est un cas spécial du MRP, Rees et al. (1989) explique qu'elle utilise comme taille de lot la demande et non pas une méthode basée sur le lot économique. Le système MRPLXL utilise généralement une période de planification d'une semaine.

Le Juste-à-Temps est généralement supporté par un système à flux tiré. Un système dit à flux tiré est un système où le poste en aval demande d'avoir des pièces du poste en amont lorsqu'il en a besoin. Pour approvisionner un poste, l'opérateur envoie une carte, appelée kanban au poste précédent. Les avantages du système Kanban sont une plus grande flexibilité, la simplicité, la qualité de l'information, il est peu dispendieux à utiliser et réduit le personnel requis pour faire la planification et le contrôle. De plus, Berkley et Kiran (1991) ajoutent que le JAT permet aux employés de prendre des décisions de contrôle et suivi de la production sans les délais associés à un système de planification traditionnel.

Berkley et Kiran (1991) expliquent deux types de systèmes Kanban. Le premier est un système Kanban à quantité constante. Ainsi, un poste envoie un certain nombre de kanbans de manutention au poste en amont lorsque son inventaire atteint le point de commande. Le deuxième est un système Kanban à intervalle de manutention constant. Pour celui-ci, un poste envoie à intervalle fixe au poste en amont les kanbans de manutention qu'il a utilisés pendant la période. Ces systèmes représentent des systèmes tirés périodiquement (periodic pull system).

Le système peut être à une ou deux cartes. Pour un système à une carte, la carte sert pour la production et la manutention. Tandis qu'un système à deux cartes a un kanban pour la production et un autre pour la manutention. Le kanban de production sert d'ordre de travail pour un contenant de produits finis. Le kanban de manutention sert de réquisition de matériel entre deux stations. Le système Kanban à deux cartes est un système tiré périodiquement et est plus approprié pour les ateliers qui fabriquent par lots où les opérations de manutention sont effectuées périodiquement. De plus, Monden (1993) fait mention que le nombre de kanbans par produit est fonction du temps de cycle et de l'intervalle de manutention.

Une nouvelle approche est proposée par Spearman et Zazanis (1992). Ce système possède des caractéristiques des deux systèmes précédents et est appelé le "constant work-in-process" (CONWIP). Son fonctionnement est simple. Ainsi, les nouvelles commandes sont acheminées au département d'assemblage qui ensuite signale le magasin de préparer les lots à produire. Ces lots seront ensuite poussés entre les stations. La figure 1 présente les trois stratégies énumérées plus haut.

Baker et al. (1990) ont comparé la performance du système tiré et du système poussé pour une ligne de production en série. Ils concluent qu'il n'est pas supposé y avoir de différence entre les deux systèmes dans la mesure où les deux systèmes opèrent dans les mêmes conditions.

Rees et al. (1989) , quant à eux, comparent l'utilisation de MRPLXL avec le kanban dans un atelier désorganisé au niveau de l'aménagement. Plusieurs des principes énumérés plus haut ont été utilisés dans

l'atelier sauf le regroupement technologique. Ils concluent que MRPLXL est beaucoup plus économique que les kanbans, que les inventaires sont plus bas et qu'il y a moins de mises en course des machines. La raison attribuée est qu'un système kanban, pour fonctionner, requiert d'avoir un contenant devant chaque poste dans l'atelier. De plus, le système MRPLXL se comporte mieux lorsque la demande est variable.

Figure 1. Système poussé, tiré et CONWIP

Co et Jacobson (1990) présentent une fonction récursive pour calculer le nombre de kanbans nécessaires à chacun des postes d'une ligne de production en série. Ils mentionnent que le fait de changer le nombre

de kanbans régulièrement en fonction de la demande est équivalent à la stratégie MRPLXL.

Spearman et Zazanis (1992) dans leur étude du CONWIP mentionne que le CONWIP est préférable au kanban dans un environnement où il y a une multitude de pièces parce qu'il n'est pas nécessaire d'avoir des en-cours pour chacune de ces pièces. Par contre, cela impose comme contrainte que le routage soit le même pour tous les produits.

#### Outils du JAT

Plusieurs techniques de génie industriel sont nécessaires à la mise en place du Juste-à-Temps. La première technique utilisée consiste à réduire les temps de mise en course. Aussi, il y a l'équilibrage de ligne, la révision de l'aménagement, la standardisation des produits, la qualité pour ne nommer que ceux-là. Wantuck (1989) donne les bénéfices suivant au JAT: l'augmentation de productivité, la réduction du temps de passage, la réduction des en-cours, une meilleure utilisation de la capacité de production et une plus grande flexibilité et qualité. Pour ce faire l'entreprise doit utiliser différentes techniques qui sont:

1. Cercles de qualité

2. Lignes dédiées

3. Technologie de groupe

4. Conception pour l'automatisation

5. Réduction des temps de mise en course

6. Équilibrage de ligne uniforme

7. Relation avec les fournisseurs

8. Innovation en transport

Fisher (1995), Monden (1993), Wantuck (1989), Wedderburn (1985) et plusieurs autres auteurs mentionnent comme condition critique à l'implantation du Juste-à-Temps que la demande soit nivélée pour produire tout le temps le même mixte de produits pendant une période donnée.

#### Stratégie d'implantation

La première étape consiste à informer les employés des changements et des raisons qui les justifient. Ensuite, des formations sur le Juste-à-Temps doivent être données au personnel clé pour qu'ils comprennent très bien ce qui sera fait par la suite. Wantuck (1989) et Fisher (1995) disent que pour vendre l'idée au reste de l'entreprise il est préférable de commencer avec le département qui a le plus grand potentiel de succès. Après avoir trouvé un département ou une unité propice, une stratégie d'implantation est requise. Hegstad (1990) présente une approche par étapes qui a été appliquée à la division Lake Stevens Instrument Division d'Hewlett-Packard. Cette entreprise produit une grande variété de produits à bas volume. La première étape d'implantation utilisée a été le CONWIP comme situation intermédiaire entre le système actuel et celui vers lequel il aspire. Ce système de transition utilise toujours les bons de travail pour pousser la matière sur le plancher et un système avec des kanbans a été mis en place pour la gestion de l'assemblage. Comme deuxième étape, l'entreprise a éliminé les bons de travail pour la matière et l'approvisionnement est maintenant fait par kanban. La dernière étape a été d'éliminer le magasin. Maintenant, la livraison est effectuée directement au point d'utilisation de la matière. Ceci a permis à H-P de réduire son temps de passage de 47 jours à 5.4 jours pour la production des appareils de mesure.

### Technologie de groupe

En électronique, le procédé de fabrication utilise un nombre limité de machines. Un problème survient au moment de l'ordonnancement des commandes. Il y a plusieurs considérations qui doivent être tenues en compte comme les cadences, la variété des pièces, les pièces alternatives potentielles et les méthodes de travail. Aussi, les classes de machines sont fonction de la rapidité, de la précision, de la flexibilité, de la capacité pour charger les pièces, etc. L'ordre de passage des commandes déterminé influence directement le temps de chargement de la machine avec les composantes. Plusieurs solutions ont été proposées en utilisant le principe technologie de groupe. Ainsi, cette section traite de différentes techniques de formation de familles et des règles d'ordonnancement appropriées.

### Formation de familles

Une première technique, expliquée dans Shtub et Maimon (1992), consiste à former des groupes de produits ou familles basés sur la similarité des composantes utilisées par les produits. La formation de familles vise à minimiser la somme des temps de mise en course pour augmenter l'utilisation des machines mentionnent Bhaskar et Naredran (1996). Deux techniques de formation de familles en électronique sont présentées dans la littérature: l'ordonnancement basé sur la séquence (SDS) et les mises en course groupées (GSU).

L'approche SDS (Sequence Dependent Scheduling) présentée dans Maimon et al. (1993) essaie de minimiser le changement de composants entre les produits. Hashiba et Chang (1991) expliquent que SDS consiste à regrouper en familles les produits en fonction des pièces nécessaires selon un

algorithme. Une mise en course majeure est effectuée sur les machines pour chaque nouvelle famille. Le passage entre différents produits à l'intérieur d'une famille requiert des mises en courses mineures.

La technique des mises en course groupées, appelée grouped set-up (GSU), présentée par Carmon et al. (1989) cherche à minimiser le nombre de mises en course en faisant passer tous les produits qui utilisent les composantes chargées sur une machine. Un avantage de GSU est qu'elle limite le nombre de fois qu'une pièce est chargée à une seule fois, disent Maimon et Shtub (1991). Un produit peut passer plusieurs fois sur la ligne avant d'être complètement assemblé. Ceci occasionnera une accumulation de produits partiellement assemblés en attente pour être complétés. Les en-cours générés sont ainsi plus élevés avec GSU et plus complexes à gérer, explique Carmon (1989). De plus, GSU favorise un environnement où il y a beaucoup de produits avec plusieurs pièces communes entre eux.

#### Règles d'ordonnancement

Plusieurs articles ont été écrits sur l'ordonnancement. Panwalkar et Iskander (1977) ont répertorié 113 règles d'ordonnancement en trois catégories. Des études de simulation ont démontré qu'il n'existe pas une règle d'ordonnancement universelle, c'est-à-dire, une règle qui donne les meilleurs résultats dans toutes les situations.

En effet, l'ordonnancement dans un système Kanban diffère d'un système de planification des besoins matières (MRP) qui recherche principalement à rencontrer les dates dues, mentionne Lee (1987). Des règles d'ordonnancement ne demandant pas de dates dues sont nécessaires pour un système Kanban. La performance des règles doit être mesurée par

des mesures autres que le retard ou l'avance d'une commande. Berkley (1993) compare deux règles couramment utilisées, le temps de production le plus court (SPT) et le premier venu, premier servi (FCFS). Une étude faite par Lee (1987) conclut que SPT/LATE, la seconde règle tenant compte du retard, est définitivement plus efficace que FCFS. Pourtant, Berkley (1993) mentionne qu'en entreprise, c'est FCFS qui est le plus utilisé. Finalement, il mentionne aussi qu'un système Kanban a des files d'attentes de capacités finies qui peuvent entraîner le blocage et leurs effets sur l'ordonnancement sont peu connus.

Après la formation des familles, les produits doivent être mis en ordre, mentionnent Hashiba et Chang (1991). L'ordonnancement peut être fait à deux niveaux, parmi les familles (interfamilles) et à l'intérieur des familles (intrafamille). Frazier (1996) présente 14 règles d'ordonnancement dont 11 sont de type interfamilles et intrafamille pour une cellule manufacturière (Tableau 1).

#### Ingénierie Simultanée (IS)

Un article récent dans IIE Solutions (mai 1996) indique que les compagnies oeuvrant dans le domaine de la haute technologie veulent diminuer le temps de développement d'un produit. Enfin, l'auteur mentionne que l'objectif de réduction moyen de ce délai pour les entreprises du secteur électronique est de 23.1%.

Plusieurs définitions de l'ingénierie simultanée (IS) ont été proposées au cours des dernières années, en voici deux. Broughton (1990) donne la définition suivante: "L'ingénierie simultanée tente d'optimiser la conception et la fabrication d'un produit pour obtenir une réduction

Tableau 1

## Règles d'ordonnancement

| Règles    | Interfamilles                                 | Intrafamille                           | Remarque                                        |

|-----------|-----------------------------------------------|----------------------------------------|-------------------------------------------------|

| FCFS/FCFS | Premier arrivé, premier servi                 | Premier arrivé, premier servi          | Arrivent toutes ensemble                        |

| MJ/SPT    | Le plus de lots                               | Temps de passage le plus court         | La plus performante selon Frazier               |

| EDD/SI    | Date due le plus tôt                          | Opération imminente la plus courte     | Mêmes dates dues                                |

| ECON/SI   | Compromis économique                          | Opération imminente la plus courte     |                                                 |

| MJ/SI     | Le plus de lots                               | Opération imminente la plus courte     |                                                 |

| MW/SI     | Le plus de travail                            | Opération imminente la plus courte     |                                                 |

| MJ/Slack  | Le plus de lots                               | La tâche qui a le moins de temps libre | Demande information sur les étapes subséquentes |

| MS/SPT    | Temps de mise en course le plus court         | Temps de passage le plus court         |                                                 |

| NJNL/SI   | Nombre de tâches + nombre de tâches en retard | Opération imminente la plus courte     | Demande information sur les étapes subséquentes |

| DK/SI     | Interchanger en fonction des dates dues       | Opération imminente la plus courte     | Mêmes dates dues                                |

| SPT/SPT   | Temps de passage le plus court                | Temps de passage le plus court         |                                                 |

du temps de cycle et une amélioration en qualité et coût en intégrant les activités de conception et de fabrication et en maximisant le parallélisme des tâches à accomplir". Quant à Eversheim (1990), il dit que " l'IS est une stratégie organisationnelle. L'idée est de réduire le temps de design d'un produit en planifiant simultanément le produit et la production."

Figure 2. Méthode traditionnelle vs Ingénierie Simultanée

#### Importance et bénéfices de l'ingénierie simultanée

Carter (1994) mentionne que l'IS permet de réduire le temps entre la phase de la conception d'un nouveau produit et son lancement en production. La figure 2 montre la méthode traditionnelle et celle que l'IS propose sur un diagramme de Gantt. Brooks (1994) mentionne que l'IS permet d'améliorer la qualité et la conformité aux attentes du client, et apporte en plus une réduction des coûts de développement, de livraison et de support du produit. Le plus grand bénéfice de l'IS selon Carter (1994)

est un produit de meilleure qualité étant donné qu'il y a moins de modifications ou révisions apportées au produit. L'IS utilise plusieurs bases de connaissance et permet de prendre de meilleures décisions plus rapidement concernant tous les stades du cycle de vie du produit (de sa conception au déclin) fait remarquer Brooks (1994).

### Éléments

L'IS fait appel à plusieurs techniques comme la qualité totale, le déploiement de la fonction qualité ou la conception pour la fabrication et l'assemblage. Brooks (1994) énumère neuf éléments qui indiquent que l'entreprise fait de l'IS. Le chapitre 21 du livre de Kusiak (1992) présente 10 caractéristiques avec un peu plus de détail que Brooks. Ces éléments donnent une bonne idée de ce que signifie faire de l'IS. Le tableau 2 montre ces caractéristiques et ce qui est requis.

Tableau 2

Caractéristiques de l'IS

| No | Caractéristiques                                                                               | Ce qui est requis                                                                                                                                                                                                                                                                                                                |

|----|------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | Une approche de conception "top-down" basée sur un système d'ingénierie des procédés maîtrisés | <ul style="list-style-type: none"> <li>- Support autoritaire et participatif de la haute direction pour bâtir un consensus.</li> <li>- Développement d'un plan de gestion des systèmes d'ingénierie.</li> <li>- Un système d'information intégré par ordinateur pour permettre la gestion et le contrôle automatisés.</li> </ul> |

| 2  | Une bonne interface avec les clients                                                           | <ul style="list-style-type: none"> <li>- Méthode pour traduire la voix du client en un produit-clé ou caractéristiques du procédé.</li> <li>- Rester en contact avec le client durant l'évolution du produit.</li> </ul>                                                                                                         |

Tableau 2 (Suite)

| No | Caractéristiques                                                                                      | Ce qui est requis                                                                                                                                                                                                                                                                               |

|----|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3  | Des équipes multifonctionnelles et multidisciplinaires                                                | <ul style="list-style-type: none"> <li>- Membres d'équipe de toutes les disciplines et fonctions, design, fabrication et support.</li> <li>- Tout le monde accepte l'opinion de chacun des membres.</li> <li>- La capacité d'analyse de tous les membres est égale ou presque égale.</li> </ul> |

| 4  | La continuité des équipes                                                                             | <ul style="list-style-type: none"> <li>- Les équipes doivent être formées très tôt dans la phase de conception.</li> <li>- Le membre-clé devrait suivre le produit.</li> <li>- Former, accepter et donner des incitatifs aux membres qui suivent.</li> </ul>                                    |

| 5  | L'optimisation des pratiques d'ingénierie au niveau des caractéristiques des produits et des procédés | <ul style="list-style-type: none"> <li>- Des méthodes pour incorporer des procédures d'optimisation de nature qualitative et quantitative.</li> <li>- Sélection des valeurs d'optimisation des produits et procédés-clés basées sur une analyse de sensibilité paramétrique.</li> </ul>         |

| 6  | Évaluation des design et prototypes grâce à la création d'un modèle digital du produit                | <ul style="list-style-type: none"> <li>- La méthode de conception par caractéristiques.</li> <li>- Standardiser la façon de définir le produit et l'échange de données.</li> </ul>                                                                                                              |

Tableau 2 (Suite)

| No | Caractéristiques                                                                                       | Ce qui est requis                                                                                                                                                                                                                                       |

|----|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7  | Simulation de la performance du produit, de la fabrication et du support aux procédés                  | <ul style="list-style-type: none"> <li>- Capacité de simuler par distribution.</li> <li>- Niveaux variés de fidélité de la simulation pour supporter l'évolution du produit pendant les étapes.</li> </ul>                                              |

| 8  | Expérimentation pour confirmer ou changer les prédictions à haut risque trouvées lors de la simulation | <ul style="list-style-type: none"> <li>- Méthode de design expérimental pour la réduction de la variabilité des produits et procédés à haut risque.</li> <li>- Validation et vérification des composantes, pièces et technologies critiques.</li> </ul> |

| 9  | Implication très tôt des sous-contractants et des vendeurs                                             | <ul style="list-style-type: none"> <li>- Décomposition organisationnelle pour identifier les chemins critiques et le parallélisme requis.</li> <li>- Acceptation de la participation des sous-contractants et des vendeurs.</li> </ul>                  |

| 10 | Accent de la direction sur l'amélioration continue et les leçons apprises                              | <ul style="list-style-type: none"> <li>- Méthodes pour suivre le design et d'obtention des leçons apprises.</li> <li>- Base de données et connaissances informatisées partagées et accessibles par les personnes-clés d'une équipe.</li> </ul>          |

L'IS englobe plusieurs outils de travail. Brooks (1994) énumère ceux-ci: les équipes multidisciplinaires, le déploiement de la fonction qualité, la conception assistée par ordinateur, la réingénierie du processus d'affaires, un système d'information global, etc.

#### Stratégie et les étapes d'implantation

La stratégie pour l'implantation de l'IS est progressive. Par contre, pour réussir elle doit débuter avec l'engagement total de la haute direction, mentionne Brooks (1994). Un sondage dont les résultats sont présentés dans Kusiak (1992) démontre que les entreprises considèrent la caractéristique numéro un du tableau précédent comme la plus importante. De plus, Brooks (1994) dit que l'IS est adoptée par des entreprises suite à des initiatives des hauts dirigeants qui l'amènent progressivement à l'utiliser.

La stratégie proposée par Brooks (1994) est un modèle basé sur le cycle de vie. La première étape consiste à reconnaître qu'il y a un besoin de l'IS dans l'entreprise. Les étapes suivantes sont des étapes de développement de l'IS, la maturation du processus.

Ainsi, la deuxième étape constitue le premier pas en avant, c'est le projet pilote. Ici, des ressources sont allouées, les objectifs et mesures sont identifiés et communiqués, les membres de l'équipe sont choisis, un plan est développé, les outils et systèmes pour supporter l'IS sont identifiés, et finalement de nouvelles méthodes de travail sont développées et essayées.

À l'étape trois, des résultats commencent à être visibles. Le procédé est changé. Les membres ne travaillent plus de façon

traditionnelle. Il y a une diminution dans les barrières et les murs entre les fonctions et les départements. La performance dans les tâches est améliorée grâce au changement des comportements. Les processus commencent à prendre de nouvelles formes et la réponse est plus rapide.

La quatrième étape est celle de la croissance où plusieurs projets pilotes amènent le changement. Les procédés sont continuellement améliorés à l'aide des rétro-actions suite à l'implantation des mesures proposées par le projet initial. Il y a des rencontres pour revoir les projets et identifier les leçons apprises. La direction et les membres des projets croient en l'approche de l'IS et développent un plan à long terme.

La dernière étape est l'implantation totale de l'IS. L'implication organisationnelle de l'IS doit être prise en compte par la direction. De nouvelles façons de faire pour les systèmes de support doivent être définies et mises en place. L'implication des clients et des fournisseurs par la participation et la communication est maintenant ajoutée. Aussi, il y a l'ajout de programmes de formation sur les outils et techniques pour développer l'esprit d'équipe, l'évaluation et les processus efficents. L'approche de l'IS et de l'amélioration continue devient la norme pour tous les nouveaux projets.

Ces étapes reprennent les points mentionnés dans Kusiak (1992) et montrent comment atteindre une approche globale à l'entreprise en commençant par des petits projets au départ.

La revue de la littérature a permis de constater que très peu d'articles traitent de l'effet de l'ordonnancement dans l'assemblage de

circuits imprimés à l'aide de technologie de groupe. De plus, elle a démontré que l'IS est un très gros projet en lui-même.

Les prochains chapitres traiteront seulement de la portion retenue de la recherche, soit les parties deux et trois.

## CHAPITRE III

### PLAN DE L'EXPÉRIENCE

#### Description du système

Le système de production de Matrox est un système comportant plusieurs postes fonctionnant en série. La figure 3 montre la disposition des machines et des convoyeurs. L'espace pour les en-cours entre chacun des postes n'est pas égal. De plus, le transfert entre les différentes lignes est fait manuellement, à l'aide d'un chariot qui contient le lot.

La première ligne (SMT 1) comporte quatre machines principales. La première machine (SPP) sert à étendre la pâte à souder sur les tampons de la carte. La SPP est suivie d'une machine à placement rapide (MVII) qui dépose des pièces sur la carte. Ensuite, une machine de placement de précision (MPA) vient placer des pièces demandant un alignement précis. La MPA est une machine flexible. En effet, elle peut aussi placer des pièces requérant peu de précision sauf que sa vitesse n'est pas comparable à la MVII. Finalement, les cartes assemblées passent dans un four à convection (BTU) avant d'être soudées.

La seconde ligne (SMT 2) comporte seulement deux machines. La première machine (MVI) comporte deux têtes. Une tête dépose de la colle sur le PCB tandis que la seconde pose les composantes. La carte passera ensuite dans un four radiant (RTC) pour cuire la colle. La connexion

électrique entre les composantes et la carte est faite en passant sur la vague à souder (WAVE) par la suite.

Figure 3. Disposition du système de production

Le tableau 3 montre les différents formats de composants et l'espace disponible sur chacune des machines décrites ci-dessus.

Tableau 3

Espace cassettes des machines

| Types de cassettes | MPA | MVI | MVII |

|--------------------|-----|-----|------|

| Rouleau            | 60  | 150 | 150  |

| Tube               | 20  | 0   | 0    |

| Plateau            | 40  | 0   | 0    |

### Observations

Les observations concernant le fonctionnement du système de production et qui serviront dans la simulation sont les suivantes:

Principalement, Matrox possède deux lignes de production automatisée (SMT 1 et SMT 2) et une ligne d'assemblage manuel. La ligne SMT 1 est fortement sollicitée puisque presque tous les produits doivent passer par ces machines. Quant à la ligne SMT 2, sa sollicitation est plus faible, car elle sert surtout à assembler les produits avec des composantes sous la carte.

Les mises en course sont de trois types, soit le changement de famille, le changement de produit et le changement de variation. Le changement de famille demande d'enlever toutes les cassettes de pièces de la machine, les ranger, poser les cassettes requises par la nouvelle famille, s'assurer que la mise en course est bien faite, faire la mise en course du produit et finalement la mise en course de la variation. La mise en course du produit consiste à ajuster les convoyeurs, enseigner les coordonnées de la carte à la machine et faire la mise en course de la variation. La mise en course de la variation charge le programme de fabrication dans la machine et une première carte est assemblée et inspectée. Le tableau 4 montre le temps nécessaire selon le type de formation de familles utilisée.

Le tableau 5 donne les caractéristiques des composantes du système de production. Les caractéristiques données pour chacun des éléments sont sa longueur et l'espace dédié aux en-cours à l'entrée et à la sortie.

Pour certaines machines, une description plus détaillée est présentée dans les observations.

Tableau 4

## Temps de mises en course

| Temps de mise en course: (min.)      | Aucune | SDS | GSU*               |

|--------------------------------------|--------|-----|--------------------|

| Majeur                               | 75     | 75  | 75/35 <sup>†</sup> |

| Mineur Différent PCB                 | 25     | 25  | 25                 |

| Mineur même PCB différente variation | 15     | 15  | 15                 |

| Mineur même PCB même variation       | 0      | 0   | 0                  |

<sup>†</sup>75 minutes pour les premiers et 35 minutes pour les autres.

Tableau 5

## Caractéristiques des composantes du système

| Nom   | Description                       | Longueur | Tampon     |

|-------|-----------------------------------|----------|------------|

|       |                                   | (PCB)    |            |

| SPP   | Machine pour étendre la pâte      | 9.00'    | 1 in 1 out |

| Conv1 | 1 <sup>er</sup> convoyeur         | 9.25'    | 4          |

| MVII  | Machine à placement haute vitesse | 8.00'    | 1 in 1 out |

| Conv2 | 2 <sup>ième</sup> convoyeur       | 13.00'   | 3          |

| MPA   | Machine à placement de précision  | 7.50'    | 1 in       |

| Conv3 | 3 <sup>ième</sup> convoyeur       | 3.75'    | 1          |

| BTU   | Four à convection                 | 20.00'   | Aucun      |

| Conv4 | 4 <sup>ième</sup> convoyeur       | 8.33     | 4          |

| MVI   | Machine à placement haute vitesse | 11.00'   | 1 in 1 out |

| Conv5 | 5 <sup>ième</sup> convoyeur       | 3.75'    | 1          |

| RTC   | Four radiant                      | 13.00'   | Aucun      |

La machine goulot est celle qui détermine le débit de la ligne. Ainsi, il n'y aucune accumulation d'en-cours devant une machine autre que les tampons prévus.

#### Autres

- La mise en course est le temps total pour toutes les machines que comporte la ligne SMT.

- Certains produits requièrent un retour en arrière sur une portion de la ligne SMT. Le transfert est fait pour le lot complet.

- La planification de la production est hebdomadaire.

- Un produit est un PCB.

- Une variation de produit représente un assemblage distinct sur un même PCB.

#### Hypothèses

- Les commandes de la semaine ne peuvent être changées une fois que la planification est faite pour la semaine.

- Les temps de production à chaque poste sont les temps standard de l'entreprise. Le coefficient de variation de ces temps est considéré négligeable.

- Les machines ne produisent que des bonnes pièces.

- Environnement de production mixte, c'est-à-dire produits à bas volume et produits à haut volume dans une même semaine.

- Les prototypes ne sont pas assemblés durant les heures de production.

- Les pannes de machines ne sont pas considérées ici.

- Le temps de transfert des chariots est considéré nul.

### Expérimentation

Le système de production de Matrox est la planification des besoins matières lots pour lots(MRPLXL). Ce système de production ne produit que les quantités requises par les commandes et ne se base pas sur la quantité du lot économique. Les commandes à assembler sont données au premier poste et elles sont ensuite poussées sur le plancher de production. L'étude portera seulement sur la ligne SMT 1 étant donné qu'elle est la plus sollicitée.

#### Expérience 1:

La première expérience englobe plusieurs éléments de flexibilité manufacturière et cherche à déterminer les conditions propices au système. Pour ce faire, six variables ont été retenues.

Depuis quelques années, Matrox pratique la formation de familles. Elle utilise la technique SDS et a réduit les temps de mises en course grâce à cela. L'entreprise veut connaître les avantages de GSU pour son système. Un premier problème avec la façon traditionnelle de faire GSU est la gestion des en-cours dû à la multitude de retours en arrière et de programmes des machines. Une proposition faite par M. Bernard Cyr, planificateur de la production, est de dédier la moitié des espaces cassettes sur les machines pour mettre les pièces les plus utilisées parmi les commandes de la semaine. Le reste des espaces est traité avec la technique SDS. Cette nouvelle approche a été nommée GSU\* et est celle qui va être comparée à SDS.

La deuxième variable vient de l'existence sur le marché des cassettes doubles qui permettent de doubler le nombre de pièces

différentes par machine. Le coût actuel d'une cassette simple est d'environ 1 500\$ tandis que la cassette double coûte autour de 3 000\$. Son principal avantage est que les familles devraient pouvoir contenir plus de produits et ainsi diminuer le nombre de familles. Ceci se traduirait par moins de mises en course majeures.

La troisième variable tente de répondre à la question suivante: Quel est le niveau de similarité minimum pour inclure un produit dans la famille? Des essais avec différents niveaux de similarité ont été faits pour connaître son effet. En fait, il n'y pas ou très peu de changement dans la constitution des familles lorsqu'un niveau de 10% de pièces communes est imposé par rapport à aucun. Par contre, le nombre de familles commence à doubler lorsque le niveau de similarité dépasse les 30%.

Une étude interne a démontré que la liste de pièces principales de l'entreprise pourrait être réduite de près de 20% en standardisant les pièces. Par contre, cette standardisation entraînera souvent une reconception du produit. Avant de suggérer la reconception des produits, il est important de déterminer son influence sur la formation des familles et la production.

Les deux dernières variables sont liées à l'ordonnancement des commandes. Il y a deux niveaux possibles, interfamilles et intrafamille. Les règles interfamilles n'ont aucune influence sur les temps de mises en course puisque les temps de mise en course sont déterminés par l'ordre des produits à l'intérieur des familles. Par contre, elles auront une influence sur les en-cours et le temps de passage. Seulement deux règles sont étudiées ici: la première règle choisit les familles de façon

aléatoire et servira de base pour la comparaison; la seconde règle ordonnera les familles selon le temps de production le plus court (FSPT) en excluant les temps de mises en courses.

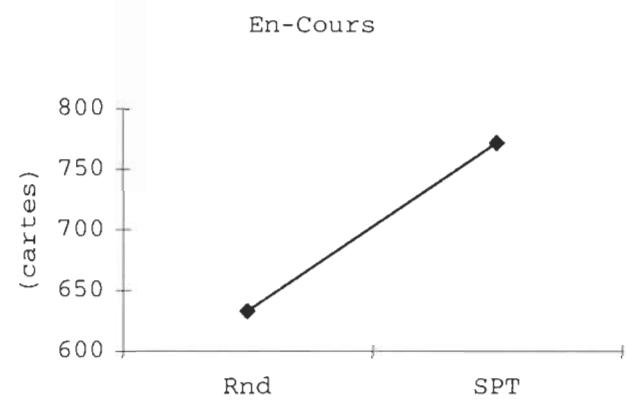

Au niveau de l'ordonnancement intrafamille, plusieurs règles peuvent être utilisées. L'utilisation de la règle premier arrivé, premier servi (FCFS) ne s'applique pas dans cette expérience puisque toutes les commandes arrivent au même moment en début de semaine. De plus, une règle en fonction de la date due ne peut être utilisée étant donné que toutes les commandes doivent être en inventaire deux semaines après leur lancement sur la ligne. Il pourrait être intéressant d'utiliser une règle basée sur le temps d'opération restant dans les autres départements et soit choisir la commande demandant le moins de temps total ou la tâche qui a le moins de temps libre pour éviter les commandes en retard. Étant données la nature des opérations et la complexité de l'affectation de la main d'œuvre, ces règles n'ont pas été retenues. La règle du temps de production le plus court (SPT) donne généralement de bons résultats. Elle a été retenue et sera comparée à la règle aléatoire. Afin d'éviter de faire plusieurs mises en course semblables, les produits ont été regroupés par PCB. De plus, Matrox procède déjà de cette manière. La première est aléatoire (RND/PCB) tandis que la seconde est selon le temps de production le plus court (SPT/PCB).

#### Variables

Le tableau 6 présente les variables de l'expérience 1 avec chacun des niveaux retenus.

Tableau 6

Variables et niveaux de l'expérience 1

| Variables             | Niveaux                         |                                                            |

|-----------------------|---------------------------------|------------------------------------------------------------|

|                       | 1                               | 2                                                          |

| Formation de familles | SDS (Sequence dependent set-up) | GSU* (Group set-up)                                        |

| Cassette              | Simple (1x)                     | Double (2x)                                                |

| Facteur de similarité | Au moins 10%                    | Au moins 30%                                               |

| Réduction de pièces   | Aucune réduction                | Réduction de 20% de la liste de pièces.                    |

| Ordre Interfamilles   | Aléatoire (RND)                 | SPT pour la famille (FSPT) sans le temps de mise en course |

| Ordre Intrafamille    | Aléatoire par PCB (RND/PCB)     | Temps le plus court par PCB (SPT/PCB)                      |

Mesures de performance

Les données relatives aux trois mesures de performance suivantes seront collectées au cours des simulations et seront par la suite analysées.

- Le niveau d'en-cours moyen (Cartes)

- Le temps de passage des commandes (minutes)

- Le temps de mise en course total (minutes)

Expérience 2

La deuxième expérience vient enrichir la première avec d'autres règles d'ordonnancement et mesure la performance d'un système qui ne fait

pas de formation de familles de produits. SDS et GSU\* sont conservées. Cette deuxième expérience tentera de répondre à certaine question laissée par la première expérience.

Pour ce qui est des règles d'ordonnancement interfamilles, Frazier (28) présente plusieurs autres règles. Une première règle est de choisir les familles basées sur le temps minimum de mise en course (MS). Dans la première partie, les familles sont choisies sur le temps de production sans tenir compte des temps de mise en course. Ainsi, leur effet est inconnu. La règle choisie est de prendre la famille avec la somme des temps de production et de mise en course la plus petite (FSPTS).

De plus, y a-t-il un effet d'avoir groupé les produits par PCB pour les règles intrafamille? Afin de répondre à cette question, l'ordonnancement des produits aléatoirement et selon le temps de production le plus court sera évalué sans les regrouper cette fois.

Les variables suivantes ne seront pas étudiées dans la partie 2. D'abord, l'utilisation des cassettes doubles en raison de leur coût élevé et du faible gain démontré dans la première expérience. Aussi, un niveau de similarité élevé ne sera pas utilisé, car il ne favorise pas le système à l'étude en créant trop de familles. Finalement, la réduction de 20% de la liste principale de pièce se traduit par une diminution d'environ 1% du nombre de pièces utilisées dans une semaine et n'affecte que très peu le système.

#### Variables

Le tableau 7 présente les variables de l'expérience avec chacun des niveaux retenus de l'expérience 2.

Tableau 7

Variables et niveaux de l'expérience 2

| Variables             | Niveaux                                         |

|-----------------------|-------------------------------------------------|

| Formation de familles | Aucune                                          |

|                       | SDS (Sequence dependent set-up)                 |

|                       | GSU* (Group set-up)                             |

| Ordre Interfamilles   | Aléatoire (RND)                                 |

|                       | SPT pour la famille (FSPT) sans mise en course  |

|                       | Temps de mise en course minimum (MS)            |

|                       | SPT pour la famille avec mise en course (FSPTS) |

| Ordre Intrafamille    | Aléatoire (RND)                                 |

|                       | Temps le plus court (SPT)                       |

|                       | Aléatoire par PCB (RND/PCB)                     |

|                       | Temps le plus court par PCB (SPT/PCB)           |

Mesures de performance

Une quatrième mesure de performance a été ajoutée pour mesurer la variation entre les différentes façons de former des familles. Les mesures de performances sont:

- Le niveau d'en-cours moyen (Cartes)

- Le temps de passage des commandes (minutes)

- Le temps de mise en course (minutes)

- Le ratio temps de mise en course/temps de production et de mises en course

### Approche de la recherche

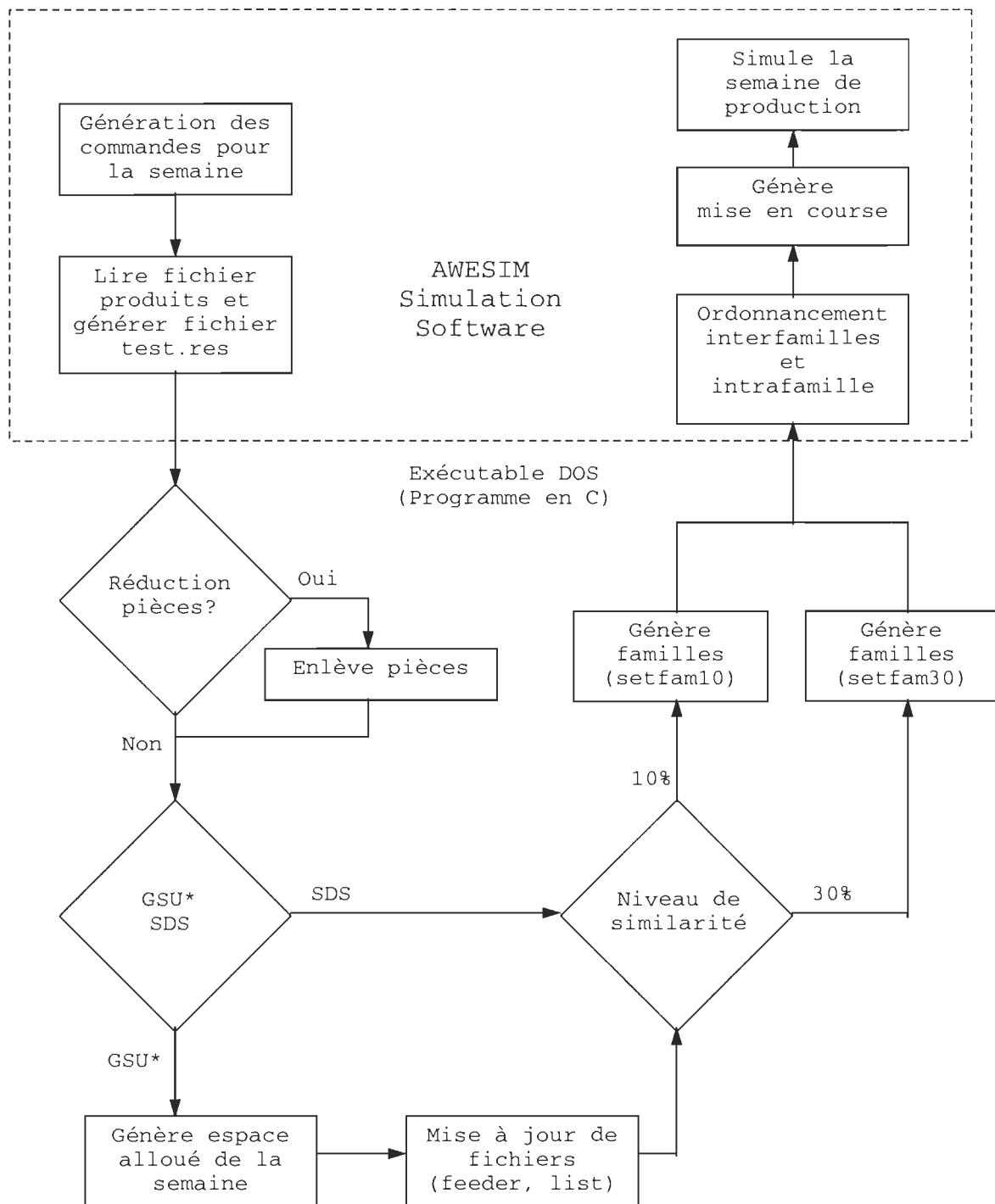

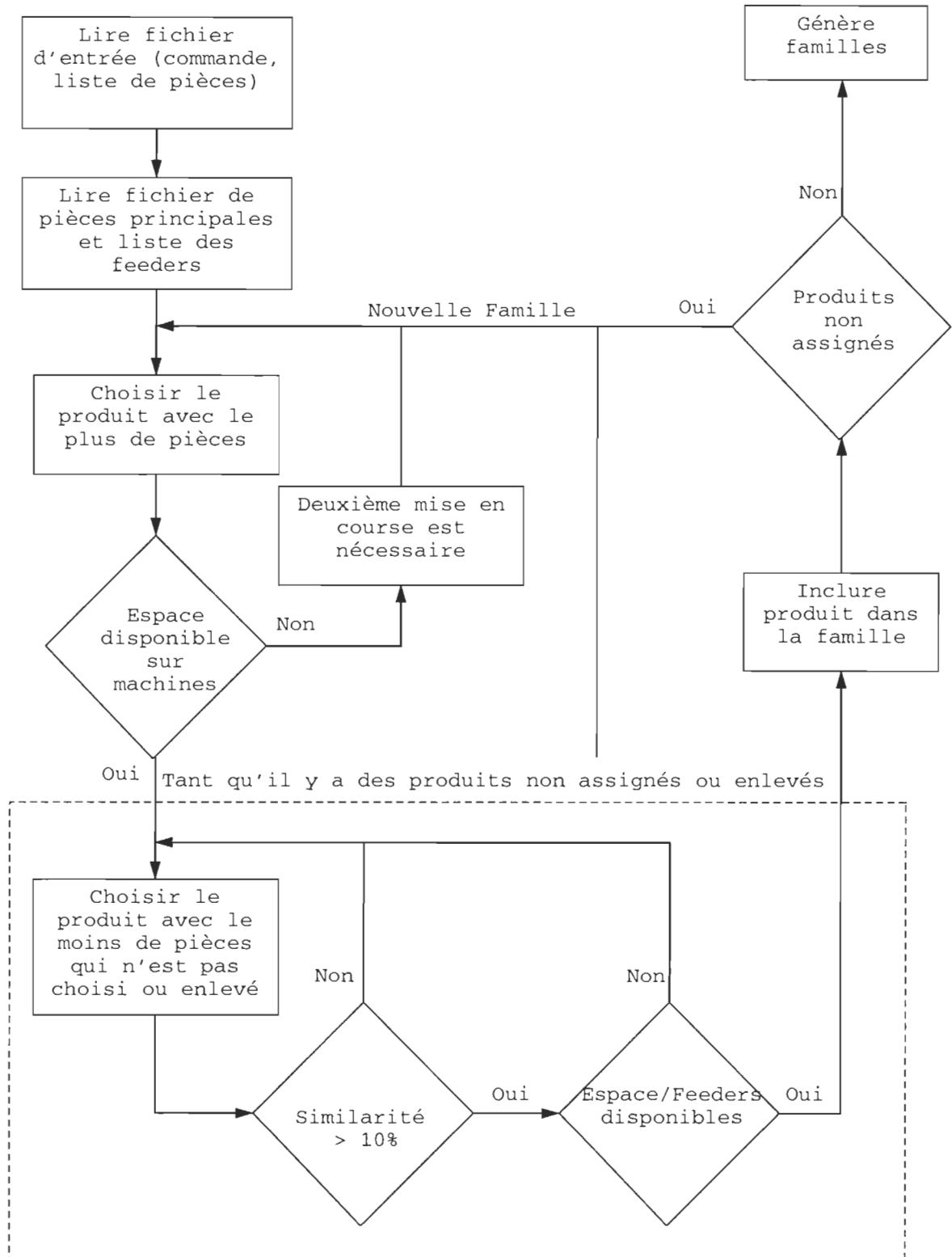

Un modèle de simulation global a été construit à l'aide du logiciel de simulation AweSim. Des fonctions en langage C ont été ajoutées dans le modèle de simulation. Elles servent à la formation des familles et à trouver les structures de produits, entre autres.

L'effet des différentes variables sur les mesures de performance sera étudié par l'analyse de variance pour chacune des expériences. Le niveau de signification ( $\alpha$ ) pour les expériences est fixé à 5%.

#### Expérience 1:

64 ( $2^6$ ) modèles de simulation  $\times$  5 répétitions

= 320 mesures.

#### Expérience 2:

36 ( $2^1 \times 4^2 + 1^1 \times 4^1$ ) modèles de simulation  $\times$  5 répétitions

= 180 mesures.

## CHAPITRE IV

### MODÈLE DE SIMULATION

#### Description du modèle

Le modèle de simulation est écrit en langage SLAMII du logiciel Awesim. Il a été choisi à cause de sa facilité de programmation, sa possibilité d'ajouter des segments de code en complément au réseau et la qualité des générateurs d'aléas de plusieurs types de distributions de probabilité.

La simulation génère une seule entité au début et termine lorsque l'horloge a atteint 500 000 minutes. Ce temps représente environ quatre années de production lorsqu'il y a de la formation de familles sinon il est d'environ deux années. L'entité boucle à l'intérieur de la simulation pour la semaine en cours de production. L'information sur le produit à assembler est obtenue à l'aide de la fonction Userf(2). Lorsque toutes les commandes de la semaine ont été assemblées l'entité retourne dans la fonction Userf(1) pour générer une nouvelle semaine. Cette fonction crée des commandes, attribue une taille de lots, calcule le temps de production, génère les familles de produits et ordonne les produits et les familles. Le premier noeud ASSIGN du réseau SLAMII sert à déterminer les paramètres de l'expérience. Le tableau 8 donne la description des différents attributs utilisés pour la collecte de données et les unités. Le tableau 9 donne les attributs utilisés dans la simulation pour déterminer quelle expérience faire. L'annexe 1 donne la description de

chacun des programmes et l'annexe 2 donne le modèle de simulation et la fonction Userf. La figure 4 montre le fonctionnement de la simulation et l'intégration des fonctions C.

Tableau 8

Attributs de collecte de données

| Attributs | Description                                                  | Unité   |

|-----------|--------------------------------------------------------------|---------|

| ATRIB[1]  | Nombre de lots                                               |         |

| ATRIB[2]  | Taille du lot                                                | Cartes  |

| ATRIB[3]  | Temps de mise en course du lot                               | Minutes |

| ATRIB[4]  | Temps d'opérations                                           | Minutes |

| ATRIB[12] | En-cours en début de semaine                                 | Cartes  |

| ATRIB[13] | Mise en course totale de la semaine                          | Minutes |

| ATRIB[14] | Temps de passage                                             | Minutes |

| ATRIB[15] | <u>Ratio mise en course</u><br>(mise en course + production) |         |

### Validation

La validation des données du système a été faite à l'aide de la fenêtre interactive d'environnement qui permet de suivre en temps réel les différentes variables de la simulation. Chacun des événements pour deux semaines de production a été suivi pas à pas pour chaque variable (ATRIB[]) et mesure de performances (COLCT) afin de valider le modèle et les ajouts en langage C. Ceci a été fait pour chaque expérience. Le système modélisé est un système à capacité infinie, c'est-à-dire que lors de la planification aucune vérification de la demande est faite avec la capacité disponible. Ainsi, il n'y aura pas d'accumulation d'encours à la

fin d'une semaine. De plus, aucune étude pour déterminer à quel moment le régime permanent débute est nécessaire pour ce genre de système.

Tableau 9

Attributs de contrôle de la simulation

| Attributs  | Description            | Valeur | Niveau  |

|------------|------------------------|--------|---------|

| ATTRIB[5]  | Formation de familles  | 0      | Aucune  |

|            |                        | 1      | SDS     |

|            |                        | 2      | GSU*    |

| ATTRIB[6]  | Capacité des cassettes | 1      | 1x      |

|            |                        | 2      | 2x      |

| ATTRIB[7]  | Facteur de similarité  | 1      | 10%     |

|            |                        | 2      | 30%     |

| ATTRIB[8]  | Réduction de pièces    | 1      | Aucune  |

|            |                        | 2      | 20%     |

| ATTRIB[9]  | Groupement Intra       | 1      | Non     |

|            |                        | 2      | Par PCB |

| ATTRIB[10] | Ordre Interfamilles    | 1      | RND     |

|            |                        | 2      | FSPT    |

|            |                        | 3      | MS      |

|            |                        | 4      | FSPTS   |

| ATTRIB[11] | Ordre Intrafamille     | 1      | RND     |

|            |                        | 2      | FSPT    |

Figure 4. Modèle de simulation

## CHAPITRE V

### ANALYSE DES RÉSULTATS

#### Expérience 1

Les tableaux 10 à 12 présentent l'analyse de variance pour la première expérience. Les résultats sont très significatifs pour les trois mesures de performance puisque leurs r-carrés respectifs sont très élevés. Le tableau 13 présente l'analyse de similarité à l'aide du test de Duncan des niveaux des variables pour les trois mesures de performance.

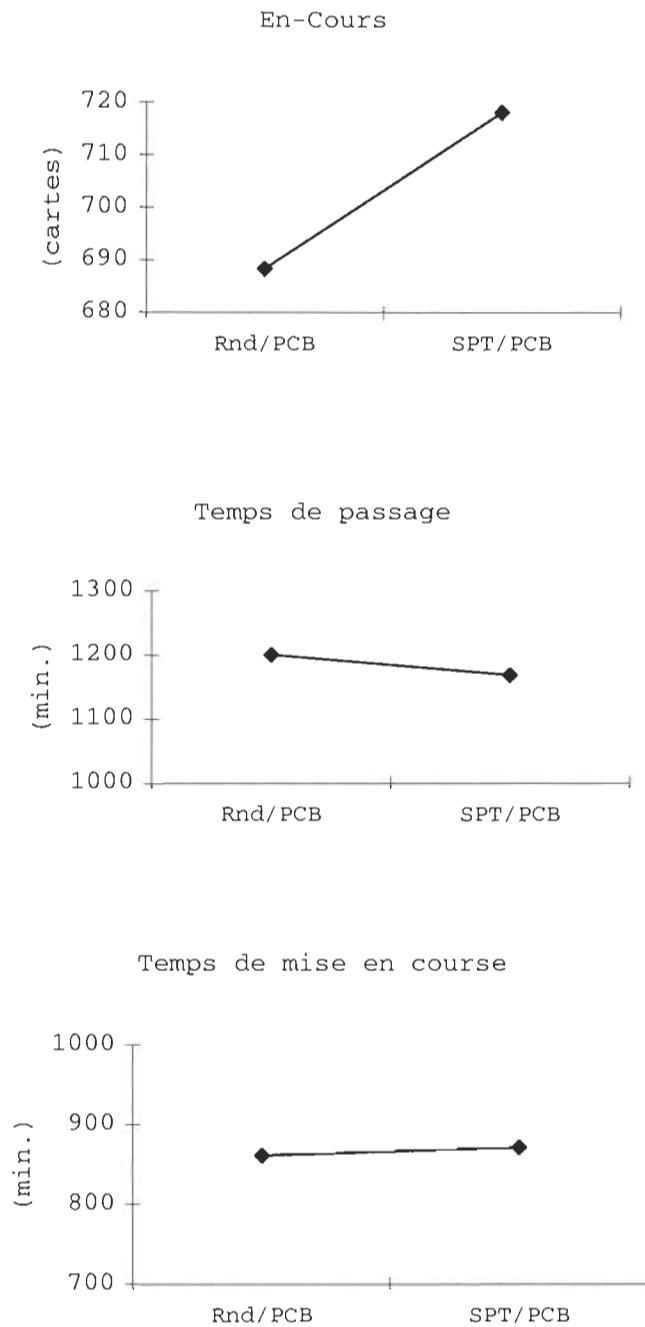

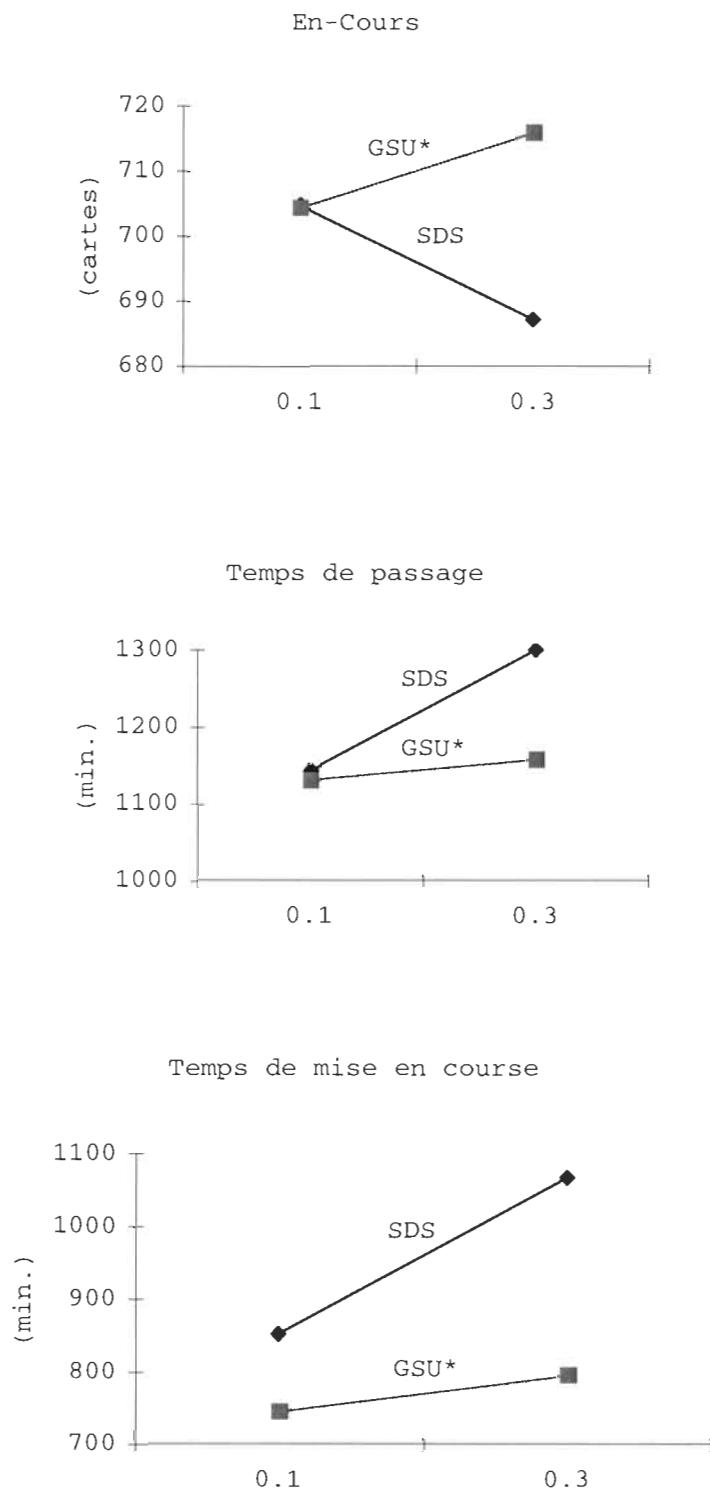

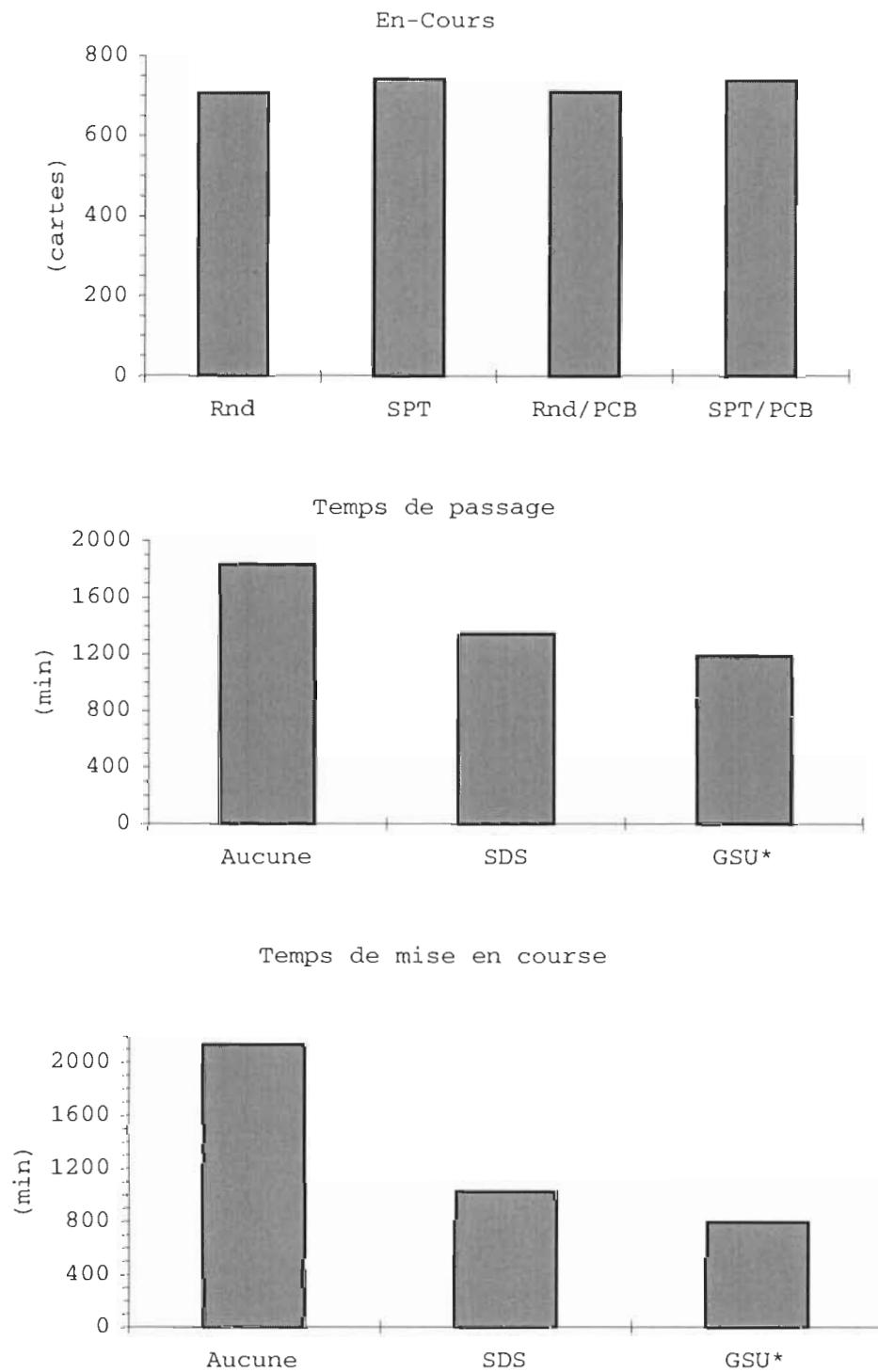

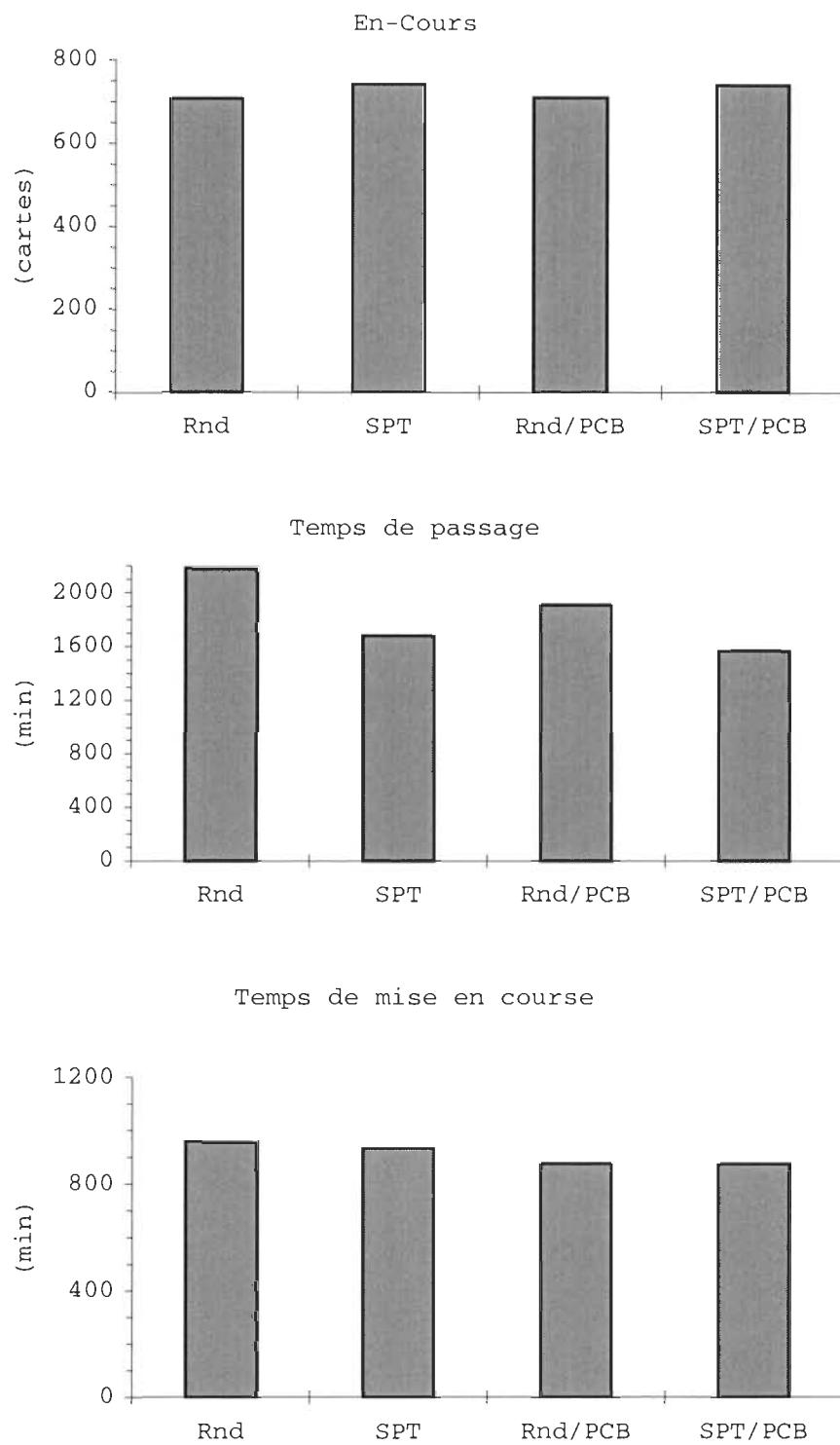

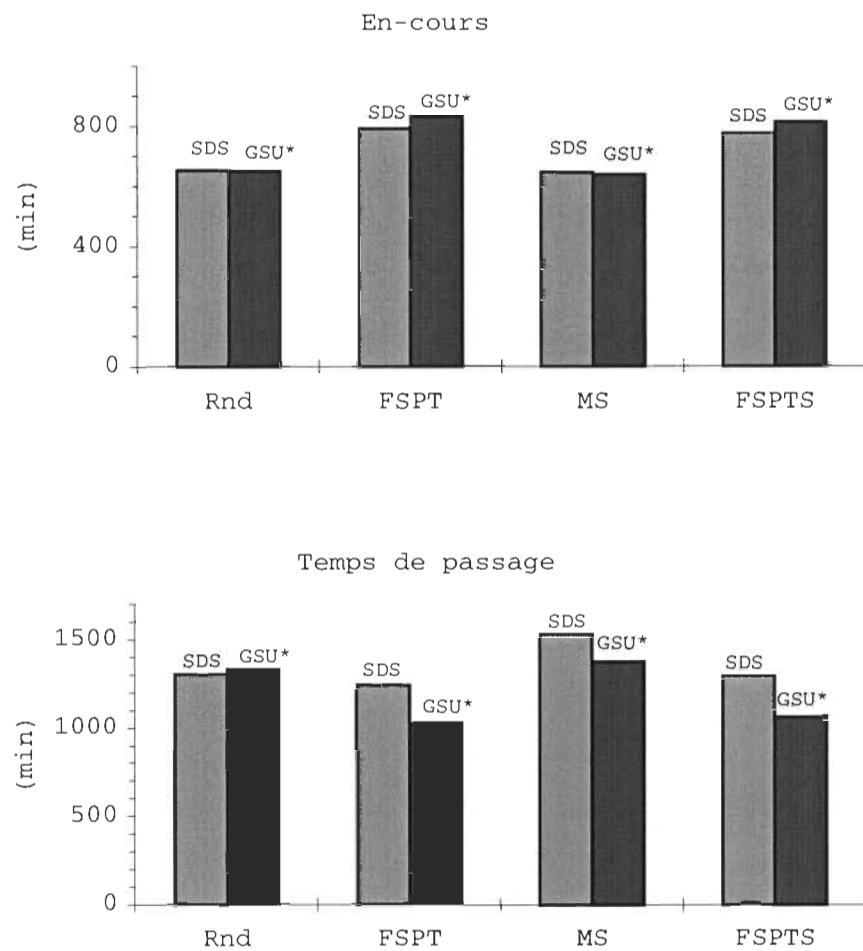

#### Méthode de groupement

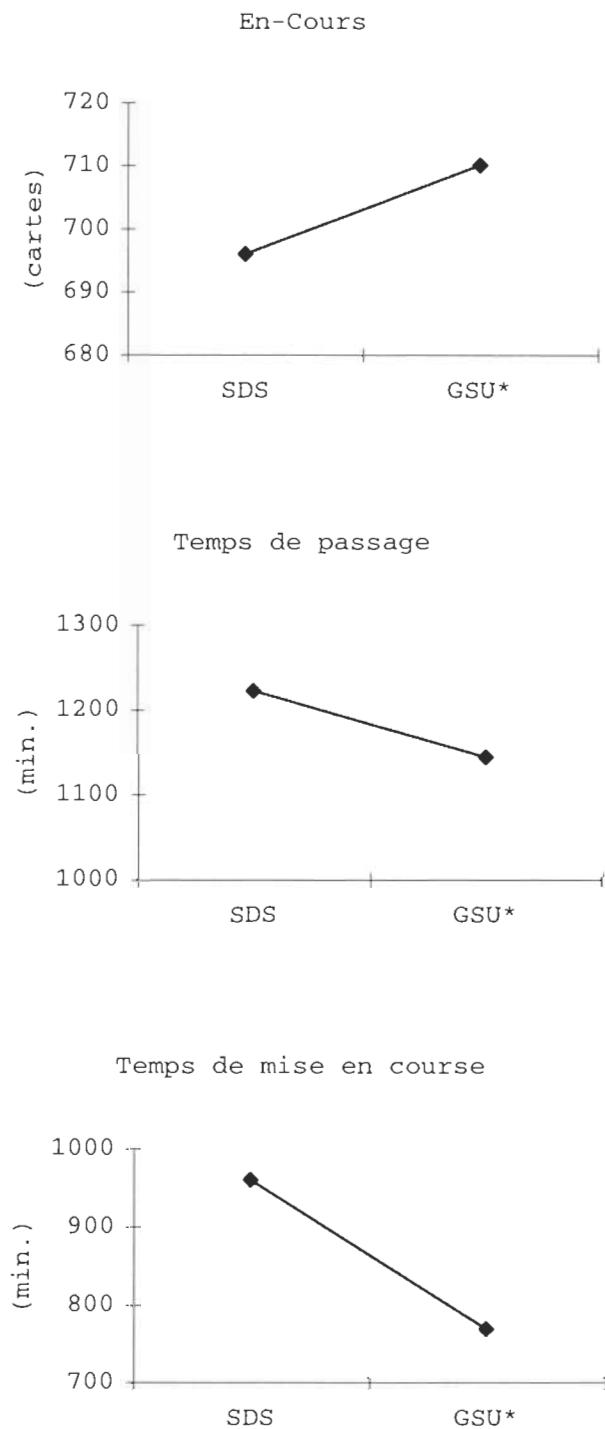

Les résultats pour la méthode de groupement sont significatifs pour les trois mesures de performance. En effet, la méthode de groupement GSU\* a pour effet d'augmenter légèrement le niveau moyen des en-cours d'environ 14 cartes, soit 2%, par rapport à SDS. De plus, le temps de passage moyen des commandes est significativement influencé par la méthode de groupement. Ainsi, GSU\* diminue de près de 78 minutes ou 6.4% le temps de passage moyen des commandes. Le plus gros gain est au niveau du temps de mise en course. En effet, GSU\* le diminue de près de 200 minutes c'est-à-dire 19.9%. (voir figure 5).

#### Capacité des cassettes

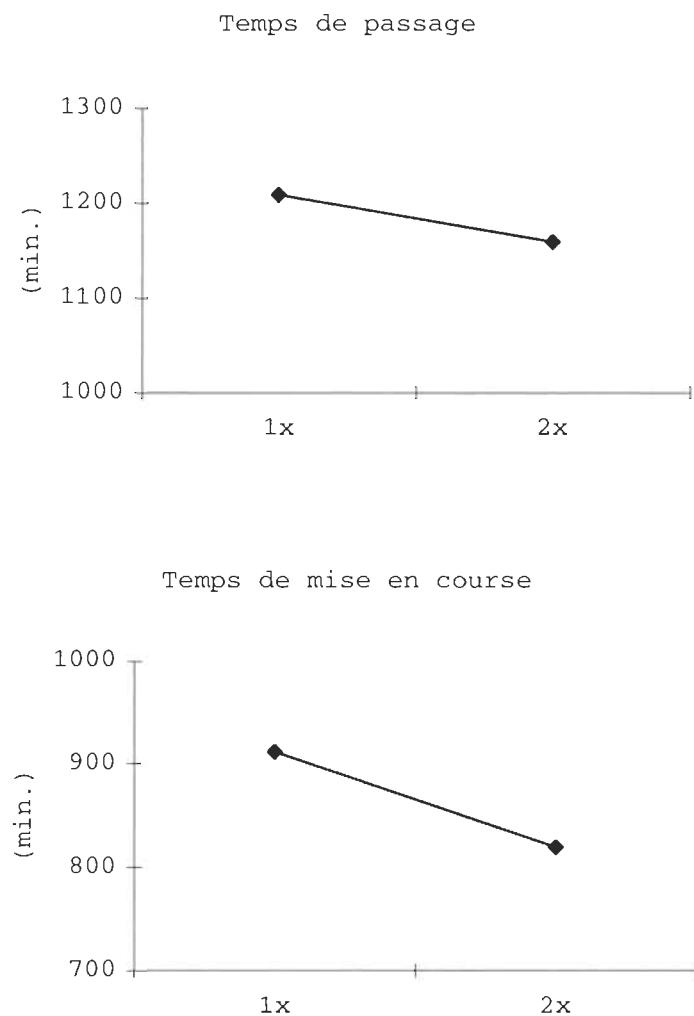

L'utilisation des cassettes doubles réduit d'environ 92 minutes, soit 10%, le temps nécessaire pour les mises en course. La figure 6

montre que le gain est moindre avec 4% pour le temps de passage. L'effet sur les en-cours est non significatif puisque la taille de lot n'est pas affectée par la réduction de pièces.

#### Facteur de similarité

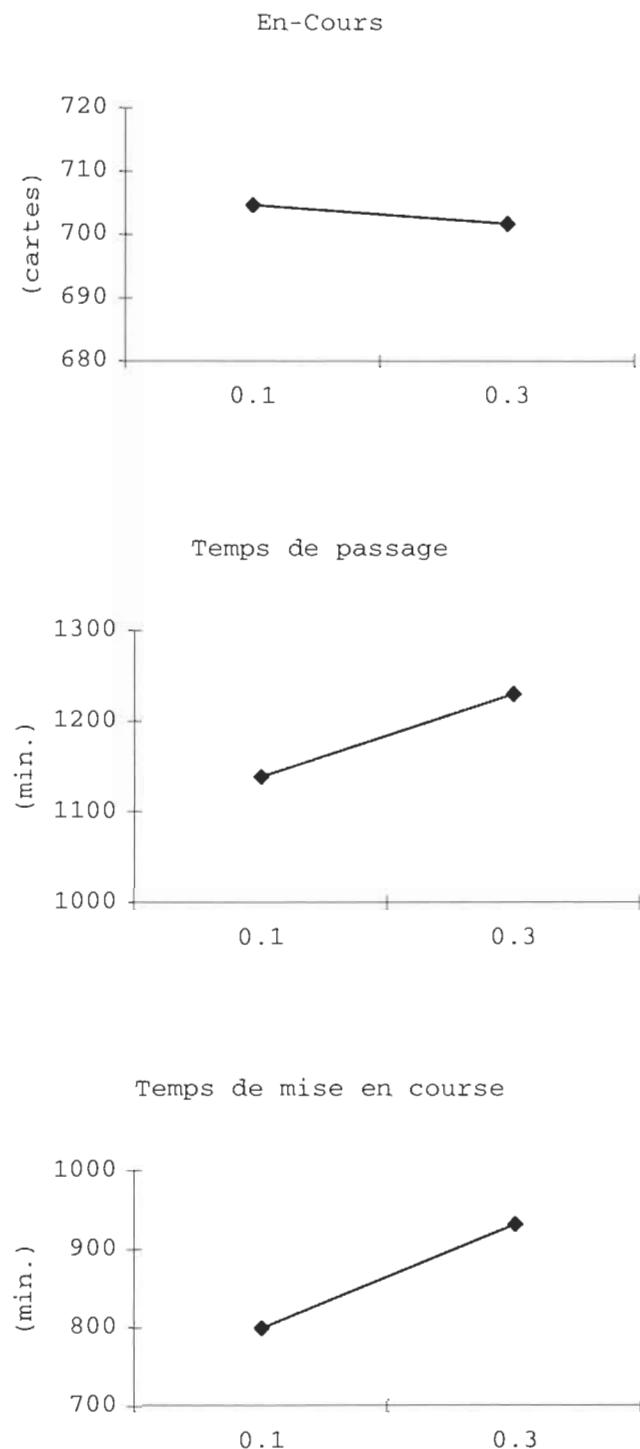

L'utilisation d'un facteur de similarité a pour effet de fixer un niveau de similarité entre les produits lors de la formation de familles. Le fait de le fixer à un niveau plus élevé force la création de plus de familles. Elle n'entraîne aucune réduction statistiquement significative des en-cours puisque la taille des lots n'est pas affectée. La figure 7 montre que plus son niveau est élevé plus il y aura de familles, donc plus de mises en course majeures. Ceci a pour effet d'augmenter le temps moyen de mise en course de plus de 16.5% ou 132 minutes et le temps de passage de 8% ou 92 minutes. L'augmentation du temps est équivalente à l'ajout de 2 mises en course majeures et l'élimination de 2 mises en course mineures environ.

#### Réduction de pièces

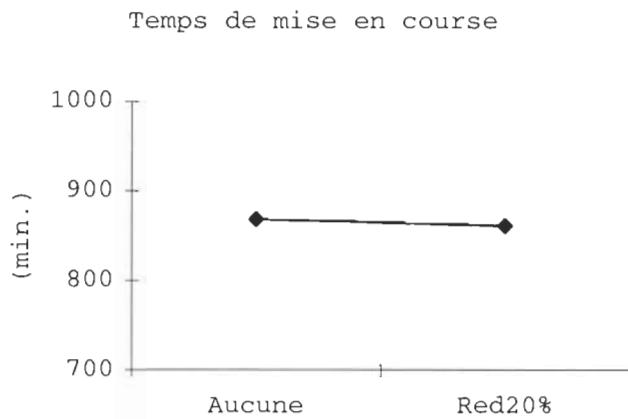

La réduction de pièces est seulement significative pour le temps de mise en course bien que la diminution soit de seulement 8 minutes ce qui représente moins de 1%. (figure 8).

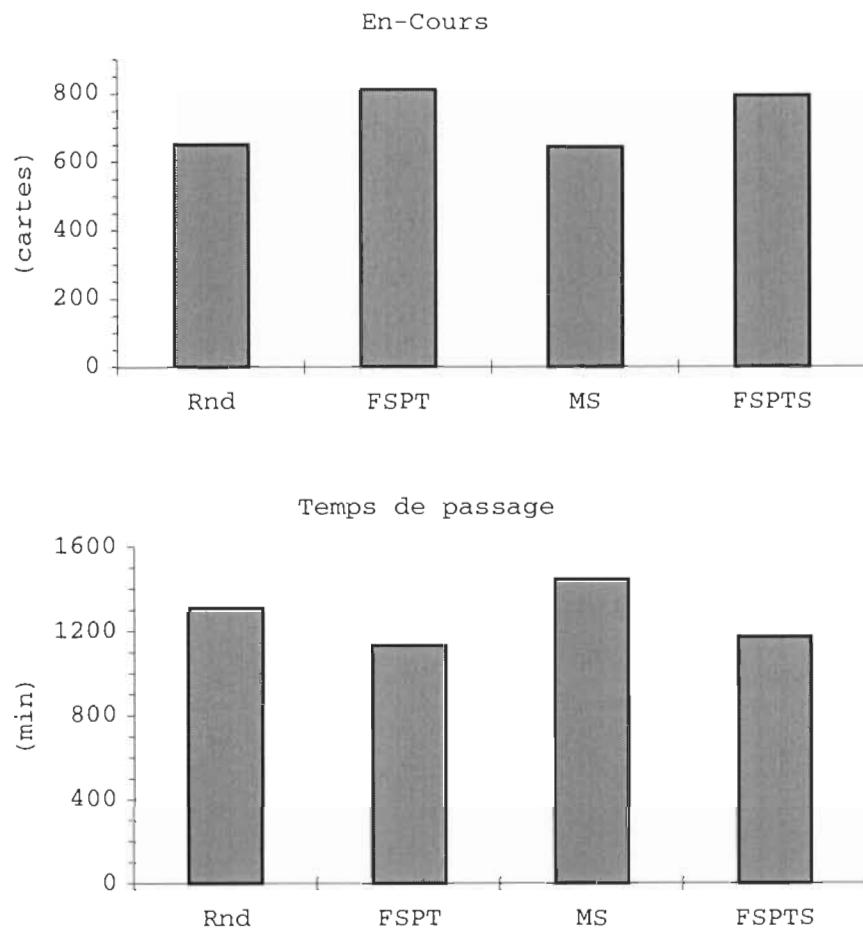

#### Ordonnancement interfamilles

L'ordre attribué aux familles n'a aucun effet statistiquement significatif sur le temps de mise en course. Cela est bien normal puisque les temps de mise en course sont indépendants de l'ordre des familles. La figure 9 montre que l'utilisation de la règle d'ordonnancement des familles FSPT permet de réduire le temps de passage d'environ 135 minutes

soit 10.8%. Par contre, il augmente le niveau des en-cours de 139 cartes (22%) par rapport à Rnd.

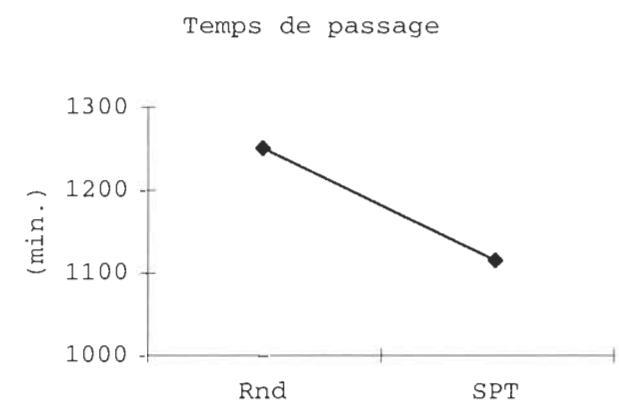

#### Ordonnancement intrafamille

L'ordonnancement à l'intérieur de la famille est significatif pour les trois mesures de performance. La règle SPT/PCB augmente de 30 cartes ou de 4% le niveau des en-cours comparativement à Rnd. Aussi, elle réduit le temps de passage de 32 minutes ou 2.7%. Les temps de mise en course sont dépendants de l'ordre des produits. Quant au temps de mise en course, il augmente de 10 minutes c'est-à-dire près de 1.2% avec l'utilisation de SPT/PCB. (figure 10.)

#### Interactions

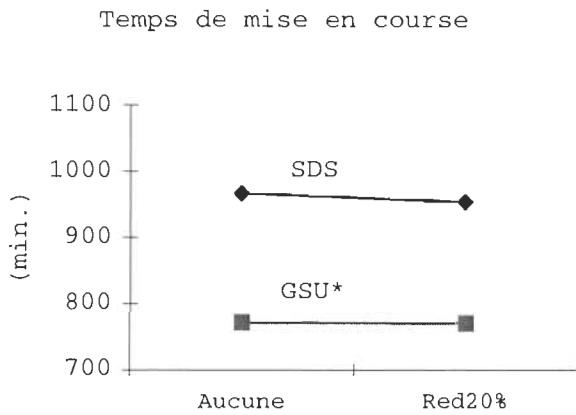

L'interaction entre la méthode de groupement et la capacité des cassettes est présentée à la figure 11. L'utilisation de cassettes simples ou doubles avec GSU\* n'affecte pas beaucoup la performance du système.

La méthode de groupement GSU\* semble moins affectée par le facteur de similarité au niveau du temps de passage et du temps de mise en course. (figure 12.)