## UNIVERSITÉ DU QUÉBEC

# THÈSE DE DOCTORAT PRÉSENTÉE À L'UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

## COMME EXIGENCE PARTIELLE DU DOCTORAT EN GÉNIE ÉLECTRIQUE

### PAR MOHAMMED BOUGATAYA

ÉTUDE ET DÉVELOPPEMENT D'UN CAPTEUR THERMOMÉCANIQUE IN SITU EN MICROÉLECTRONIQUE APPLIQUÉ AUX CIRCUITS VLSI

**AOÛT 2010**

# Université du Québec à Trois-Rivières Service de la bibliothèque

#### Avertissement

L'auteur de ce mémoire ou de cette thèse a autorisé l'Université du Québec à Trois-Rivières à diffuser, à des fins non lucratives, une copie de son mémoire ou de sa thèse.

Cette diffusion n'entraîne pas une renonciation de la part de l'auteur à ses droits de propriété intellectuelle, incluant le droit d'auteur, sur ce mémoire ou cette thèse. Notamment, la reproduction ou la publication de la totalité ou d'une partie importante de ce mémoire ou de cette thèse requiert son autorisation.

## UNIVERSITÉ DU QUÉBEC À TROIS-RIVIÈRES

DOCTORAT EN GÉNIE ÉLECTRIQUE (PH.D.)

Programme offert par l'Université du QUÉBEC À TROIS-RIVIÈRES

ÉTUDE ET DÉVELOPPEMENT D'UN CAPTEUR THERMOMÉCANIQUE *IN SITU* EN MICROÉLECTRONIQUE APPLIQUÉ AUX CIRCUITS VLSI

#### PAR

#### MOHAMMED BOUGATAYA

| Ahmed Lakhssassi, directeur de recherche    | Université du Québec en Outaouais     |

|---------------------------------------------|---------------------------------------|

| Adel Omar Dahmane, président du jury        | Université du Québec à Trois-Rivières |

| Daniel Massicotte, codirecteur de recherche | Université du Québec à Trois-Rivières |

| Adam Skorek, évaluateur                     | Université du Québec à Trois-Rivières |

| Youcef Fouzar, évaluateur externe           | Synopsys Inc.                         |

Thèse soutenue le 15 juillet 2010

À mon père, à ma mère À ma sœur Fatna À mes frères : Sghir, Rachid et Radouane À toute ma grande famille À tous mes amis et amies aux Maroc, Algérie, Europe et au Canada À titre de reconnaissance, d'amour et d'affection

## Résumé

L'objectif principal de cette thèse est dédié aux aspects des contraintes en régime dynamique dans les circuits VLSI (*Very Large Scale Integration*) pour le développement d'un capteur thermomécanique *in situ* en microélectronique appliquée aux circuits ASIC (*Application-Specific Integrated Circuit*), MEMS (*Micro Electro Mechanical System*) et WSI (*Wafer Scale Integration*).

En effet, le contrôle du gradient de température et la prédiction de la contrainte thermomécanique à partir du premier pas de la conception du circuit intégré sont essentiels.

Le sujet de cette thèse répond aux exigences croissantes des applications en microélectronique nécessitant une densité de puissance élevée et une différence de gradient thermique causée par l'implémentation de différents systèmes sur la même puce. De plus, il s'oriente vers la modélisation, la réalisation et le test d'un capteur *in situ* intelligent à haute performance. Ce dernier sera basé sur l'implémentation d'une configuration en réseau de cellules (capteurs thermiques) permettant le développement d'une unité de contrôle intégrée de la contrainte thermomécanique. La variation de la fréquence de sortie d'un réseau d'oscillateurs en anneau RO (Ring Oscillator) face a la chaleur et les contraintes mécaniques (thermomechanical stress) sera utilisée pour caractériser la distribution surfacique de contrainte au niveau d'une puce VLSI. Dans cette optique, un capteur thermomécanique sera élaboré pour jauger le niveau des contraintes dans un circuit FPGA.

Le système de contrôle intelligent a pour objectif principal d'aider le concepteur à augmenter le seuil de fonctionnement des microsystèmes VLSI à haute densité. D'une façon pratique, le réseau de capteurs va nous permettre de valider expérimentalement nos résultats de caractérisation de la dynamique thermique pour prédire le comportement thermomécanique d'un circuit intégré en opération.

L'originalité du sujet repose sur l'utilisation d'un réseau de capteurs thermiques pour caractériser la contrainte thermomécanique. La méthodologie adoptée est basée sur le développement d'un algorithme utilisant la technique GDS (gradient Direction Sensor) pour la prédiction des pics et l'évaluation de la contrainte thermomécanique associée.

## Remerciements

Je remercie tout d'abord Monsieur le professeur Ahmed LAKHSSASSI, directeur du Laboratoire LIMA (Laboratoire d'Ingénierie des Microsystèmes Avancés), pour m'avoir accueilli au sein de son laboratoire et pour l'honneur qu'il me fait en acceptant l'encadrement de ce projet.

J'exprime toute ma gratitude pour son encadrement efficace, ses précieux conseils, son support moral, la confiance qu'il m'a témoignée et son assistance bienveillante m'ont permis de passer à travers toutes les difficultés et par la même occasion je rends hommage à sa rigueur scientifique et technique.

Mes remerciements s'adressent ensuite à Monsieur le professeur **Daniel MASSICOTTE**, mon co-directeur de thèse, responsable de laboratoire de signal et de système intégré à UQTR pour ses précieux conseils.

Je remercie très sincèrement les professeurs Adel Omar Dahmane, Adam SKOREK et Youcef Fouzar pour avoir accepté d'être membres du jury de ma thèse.

À tous ceux et celles qui de près ou de loin m'ont permis de bien mener à terme ces recherches.

# Table des matières

| RÉSUMÉ<br>REMERCIEMENTS                                                                                                                        | III<br>V |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| LISTE DES FIGURES                                                                                                                              | ΙX       |

| LISTE DES TABLEAUX                                                                                                                             | XII      |

| LISTE DES SYMBOLES                                                                                                                             | XIII     |

|                                                                                                                                                |          |

| Chapitre I                                                                                                                                     |          |

| Introduction générale                                                                                                                          |          |

| I.I Évolution de la microélectronique                                                                                                          | 1        |

| 1.2 Évolution de la mise en boîtier                                                                                                            | 2        |

| 1.3 Problématique et objectifs                                                                                                                 | 3        |

| 1.4 Contribution                                                                                                                               | 6        |

| I.5 Méthodologie                                                                                                                               | 7<br>7   |

| <ul><li>1.5.1 Caractérisation de la dynamique thermique</li><li>1.5.2 Développement d'un algorithme de détection des pics thermiques</li></ul> | 7        |

| 1.5.3 Analyse et établissement d'une configuration d'un réseau de cellules                                                                     | 8        |

| 1.5.4 Algorithme de détection et de localisation des pics thermiques                                                                           | 8        |

| 1.5.5 Validation sur un FPGA                                                                                                                   | 9        |

|                                                                                                                                                |          |

| Chapitre II                                                                                                                                    |          |

| Modélisation thermique                                                                                                                         |          |

| Introduction                                                                                                                                   | 11       |

| II.I Problématique thermique                                                                                                                   | 13       |

| II.1.1 Effets de la température sur l'opération du circuit intégré (CI)                                                                        | 14       |

| II.1.2 Effets de température sur la structure physique                                                                                         | 14<br>16 |

| 11.1.3 Méthodologie pour la caractérisation de la dynamique thermique II.1.3.1 Puissance dissipée                                              | 16       |

| II.1.3.2 Types des Consommations statiques et dynamiques                                                                                       | 18       |

| II.1.3.3 Analyse de la dissipation thermique                                                                                                   | 19       |

| II.1.3.4 Choix de radiateur et de boîtier électronique                                                                                         | 20       |

| II.1.3.5 Conditions aux limites thermiques                                                                                                     | 22       |

| II.2 Analyse de transfert de la chaleur                                                                                                        | 23       |

| II.2.1 Flux d'énergie thermique                                                                                                                | 23       |

| II.2.2 Conduction de chaleur                                                                                                                   | 25       |

| II.3 Circuit thermique équivalent                                                                                                              | 27       |

| II.4 Analyse de la dynamique thermique par FEM II.5 Conditions aux limites thermiques                                                          | 29<br>32 |

| II.6 Analyse d'écoulement de fluide                                                                                                            | 35       |

| II.7 Analyse numérique de transfert de la chaleur                                                                                              | 37       |

| II.8 Résultats et discussions                                                                                                                  | 38       |

| Conclusion                                                                                                                                     | 42       |

| Développement d'un algorithme de détection et de localisation des pics thermiques                    |      |  |

|------------------------------------------------------------------------------------------------------|------|--|

| Introduction                                                                                         | 44   |  |

| III.1 Choix de la méthode                                                                            | 45   |  |

| III.1.1 Méthodes analytiques conventionnelles                                                        | 45   |  |

| III.1.2 Méthode nodale                                                                               | 46   |  |

| III.1.3 Méthodes numériques                                                                          | 47   |  |

| III.2 Algorithmes de solutions des problèmes inverses                                                | 47   |  |

| III.2.1 Les méthodes de résolution des problèmes inverses                                            | 48   |  |

| III.2.2 Méthode de spécification des fonctions                                                       | 49   |  |

| III.2.3 Méthode de régularisation                                                                    | 49   |  |

| III.3 Développement d'un algorithme de détection des pics thermiques                                 | 49   |  |

| III.4 Analyse numérique                                                                              | 56   |  |

| III.4.1 Développement des modèles éléments finis                                                     | 56   |  |

| III.4.2 Définition des modèles et maillages                                                          | 56   |  |

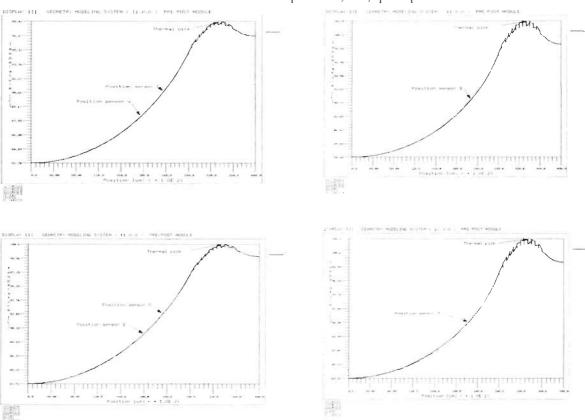

| III.4.3 Résultats et discussions                                                                     | 61   |  |

| III.5 Analyse analytique                                                                             | 63   |  |

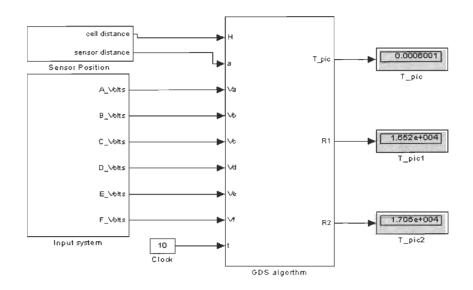

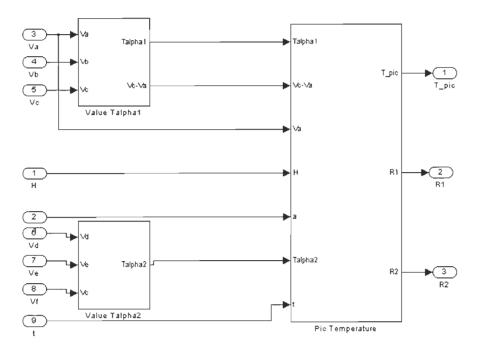

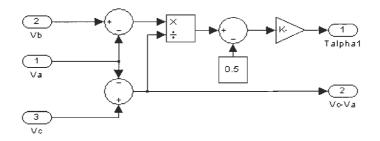

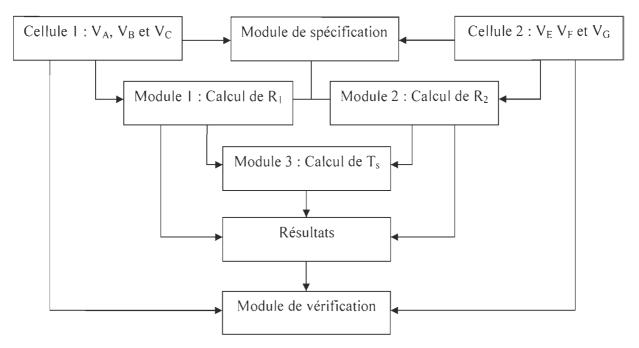

| III.5.1 Modèle de l'algorithme en Simulink                                                           | 63   |  |

| III.5.2 Sous-système d'entrée de l'algorithme                                                        | 66   |  |

| III.5.3 Résultats et discussions                                                                     | 67   |  |

| Conclusion                                                                                           | 68   |  |

| Chapitre IV<br>Implantation d'un algorithme de détection et de localisation des pics thermi<br>SPTDA | ques |  |

| Introduction                                                                                         | 70   |  |

| IV.1 Méthodologie d'implantation                                                                     | 72   |  |

| IV.2 Conception modulaire de l'algorithme SPTDA                                                      | 73   |  |

| IV.3 Décomposition modulaire                                                                         | 75   |  |

| IV.3.1 Architecture en pipeline                                                                      | 76   |  |

| IV.3.2 Architectures parallèles                                                                      | 77   |  |

| IV.3.3 architecture SIMD et MIMD                                                                     | 78   |  |

| IV.3.4 Architectures systoliques                                                                     | 79   |  |

| IV.3.5 Architecture Systolique de l'algorithme proposé                                               | 79   |  |

| IV.4 La plateforme Xilinx                                                                            | 80   |  |

| IV.5 Navigateur du projet                                                                            | 83   |  |

| IV.6 Résultats de validation par rapport à la méthode FEM                                            | 85   |  |

| Conclusion                                                                                           | 85   |  |

Chapitre III

## Chapitre V Implémentation d'un capteur de la température en oscillateurs en anneaux

| Introduction                               | 87  |

|--------------------------------------------|-----|

| V.1 Les différents circuits oscillateurs   | 88  |

| V.1.1 Les oscillateurs harmoniques         | 88  |

| V.1.1.1 Les oscillateurs basse fréquences  | 88  |

| V.1.1.2 Les oscillateurs hautes fréquences | 89  |

| V.1.2 Les oscillateurs à relaxation        | 92  |

| V.1.3 Les oscillateurs à portes            | 94  |

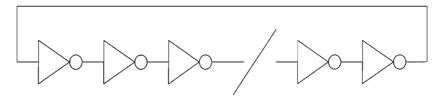

| V.1.4 L'oscillateur en anneau              | 96  |

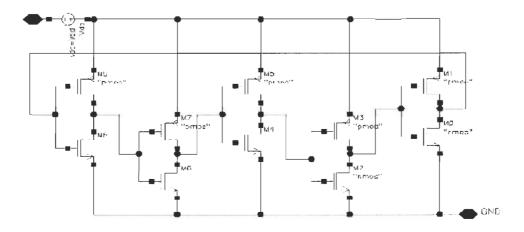

| V.2 Capteur en oscillateur en anneau       | 98  |

| V.3 Méthodologie de la conception          | 99  |

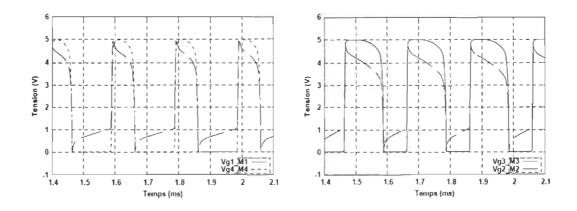

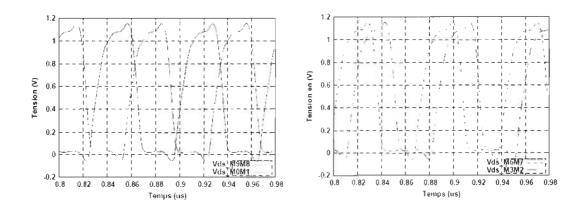

| V.4 Résultats de l'implémentation          | 102 |

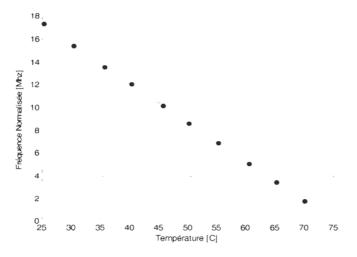

| V.5 Étalonnage du capteur                  | 104 |

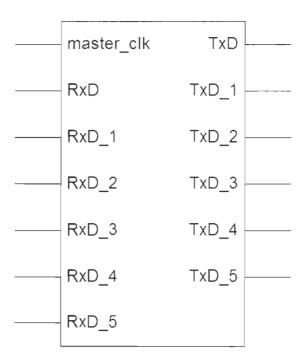

| V.6 Implémentation d'un réseau de capteurs | 105 |

| V.7 Résultats et validation pratique       | 109 |

| V.8 Contrainte thermomécanique             | 110 |

| V.9 Étude thermomécanique                  | 111 |

| Conclusion                                 | 113 |

| Chapitre VII                               |     |

| Conclusion générale                        | 115 |

| PUBLICATIONS DANS LE CADRE DE CETTE THÈSE  | 118 |

| BIBLIOGRAPHIE                              | 120 |

#### LISTE DES FIGURES

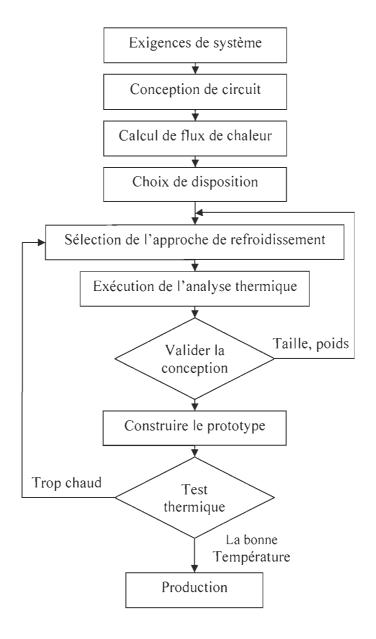

- Figure 2.1 : Organigramme général pour la conception d'un système électrothermique

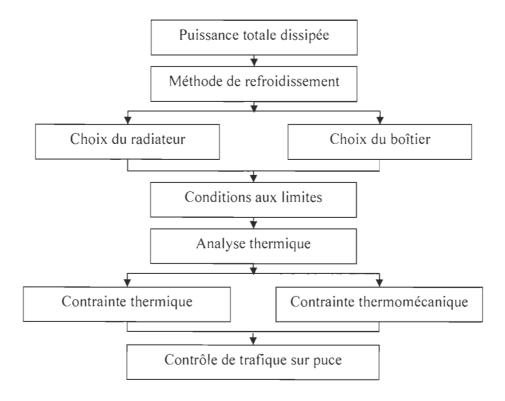

- Figure 2.2 : Méthodologie pour la caractérisation de la dynamique thermique

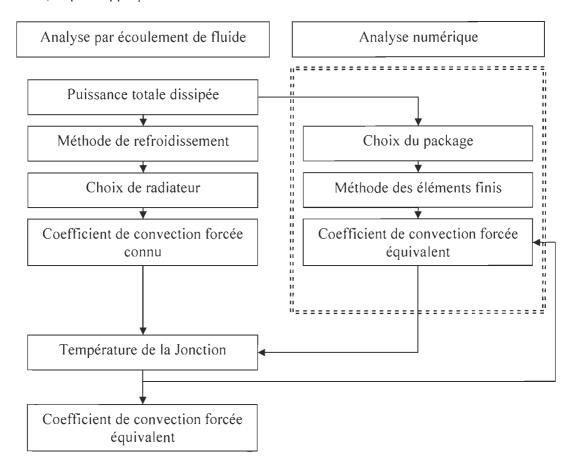

- Figure 2.3 : Approche pour déterminer le coefficient de convection forcée équivalente

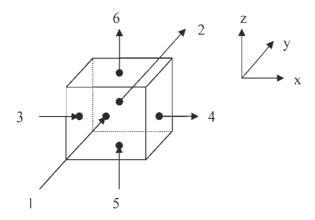

- **Figure 2.4** : Élément de volume ( $\Delta V$ )

- Figure 2.5 : Modèle thermique statique I-D

- Figure 2.6 : Analogies électriques équivalente entre la jonction et le radiateur

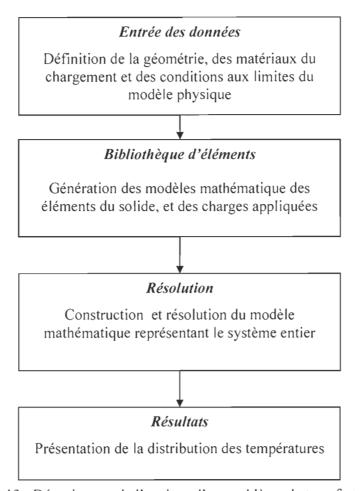

- Figure 2.7 : Organigramme pour exécuter une analyse par éléments finis.

- Figure 2.8 : Élément triangulaire

- **Figure 2.9**: Coordonnées locales définies par trois superficies  $\lambda_1$ ,  $\lambda_2$ ,  $\lambda_3$

- Figure 2.10 : Systèmes des coordonnées globales et locales

- Figure 2.11: Conditions aux limites thermiques au niveau de la jonction (BC) 43

- Figure 2.12 : Schémas d'un radiateur

- **Figure 2.13**: Évolution de la température du radiateur AAVID\_61540 en fonction de la puissance dissipée pour une source de 16mm×20mm

- Figure 2.14 : Déroulement de l'analyse d'un problème de transfert de chaleur.

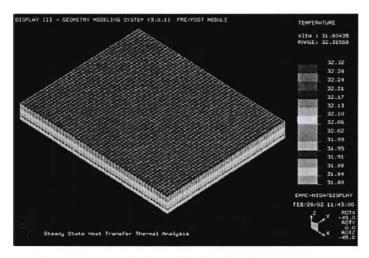

- **Figure 2.15**: Modèle en éléments finis et distribution de la température pour la source 16mm×20mm

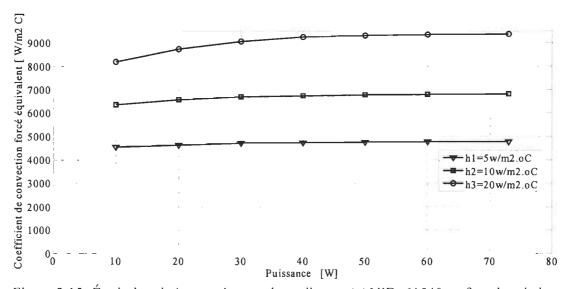

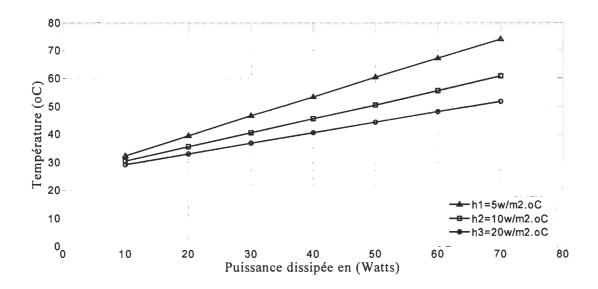

- **Figure 2.16**: Évolution du coefficient de convection forcé équivalent  $h_{eq}^{l^*conv}$  avec la puissance dissipée pour différents h.

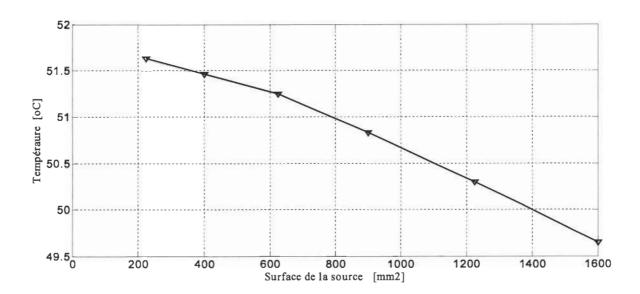

- Figure 2.17 : Évolution de la température avec la surface de la source pour  $h = 20 \text{W/m}^2 * {}^{\circ}\text{C}$ .

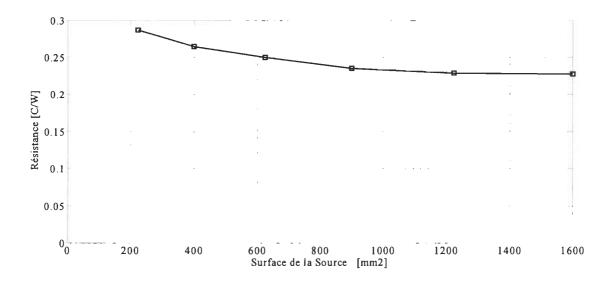

- **Figure 2.18**: Évolution de la résistance équivalente du radiateur avec l'évolution de la surface pour h =20W/m<sup>2</sup>\* °C.

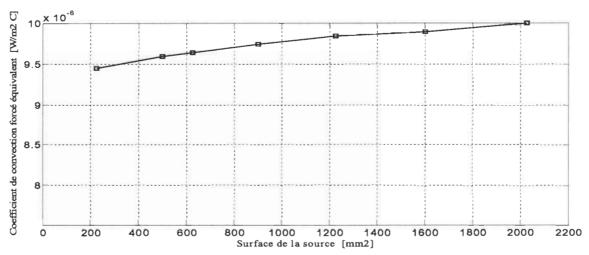

- **Figure 2.19** : Évolution du coefficient de convection forcé équivalent  $h_{eq}^{Fconv}$  avec la surface de la source pour h =20W/m<sup>2</sup>\* °C.

- Figure 3.1: Méthode nodale

- Figure 3.2: Répartition classique

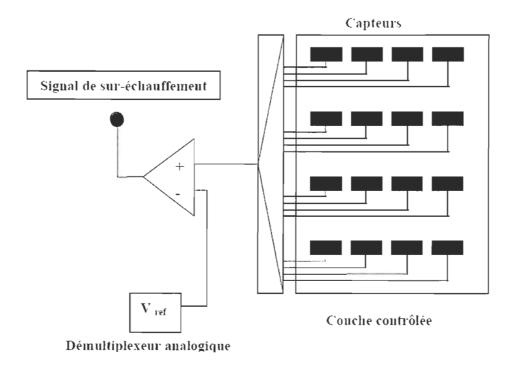

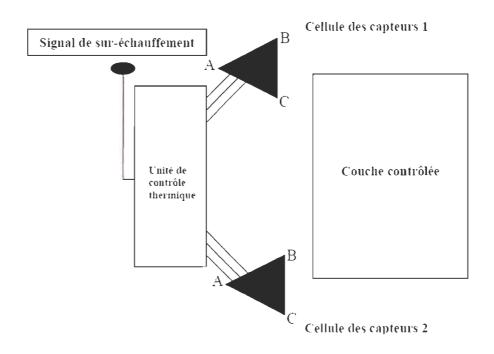

- Figure 3.3 : Répartition suggérée avec l'unité de contrôle.

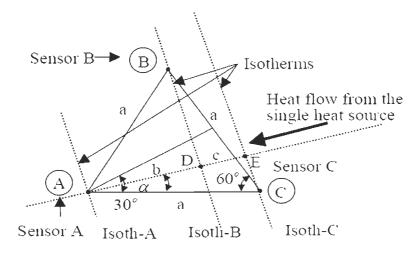

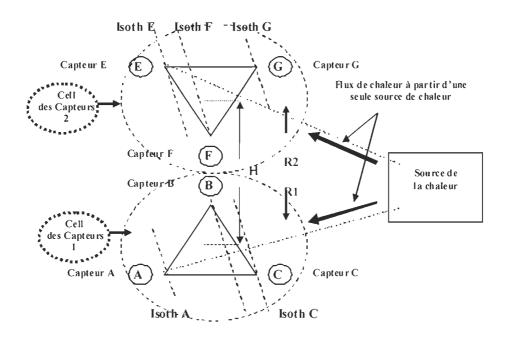

- **Figure 3.4**: Construction d'une cellule de capteur  $\alpha \in (0^{\circ}, 30^{\circ})$

- **Figure 3.5**: Description du problème pour une seule source de chaleur avec la méthode de GDS

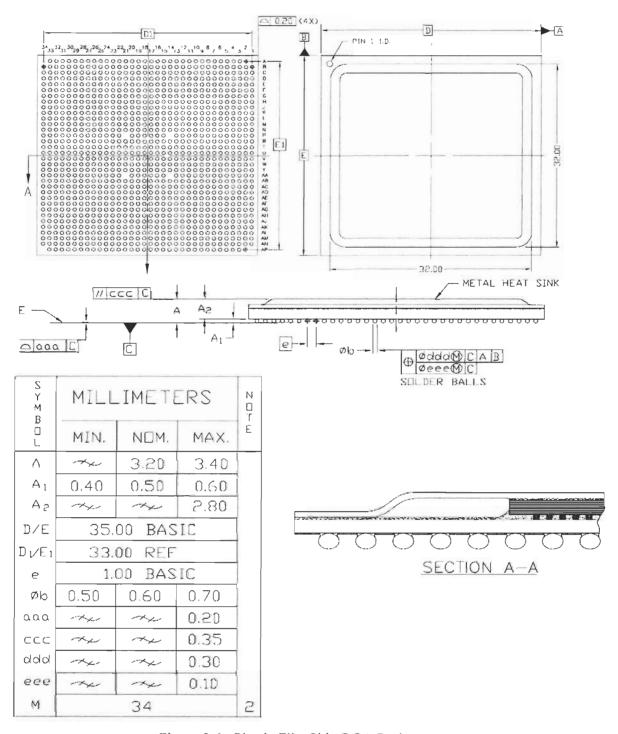

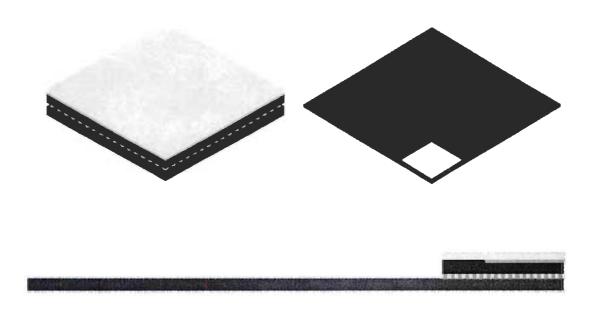

- Figure 3.6: Plastic Flip-Chip BGA Package

- Figure 3.7 : Maillage du boîtier en 3D (package)

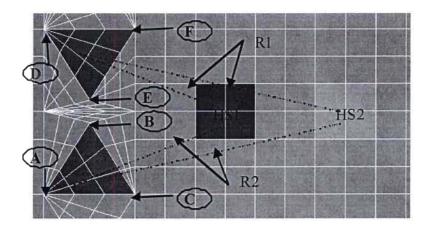

- **Figure 3.8 :** Configuration physique de deux cellules et la source de chaleur dans le modèle en éléments finis

- **Figure 3.9** : la distribution de la température pour différents choix de placement des capteurs

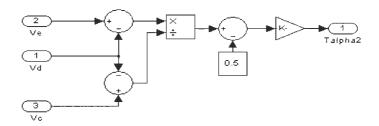

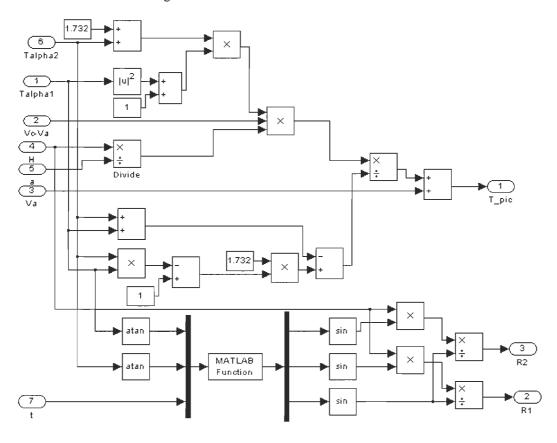

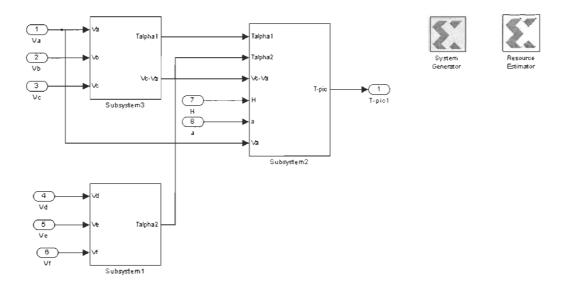

- Figure 3.10 : Système du calcul avec Simulink

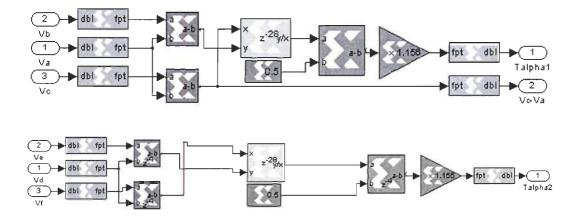

- Figure 3.11: Les blocs Simulink des trois modules

- Figure 3.12: Les blocs Simulink du module 1

- Figure 3.13: Les blocs Simulink du module 2

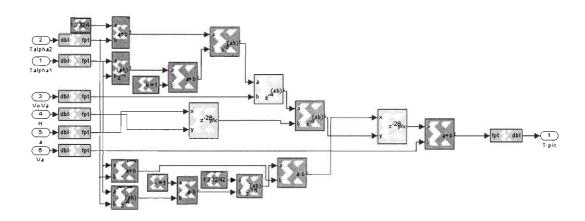

- Figure 3.14: Les blocs Simulink du module 3

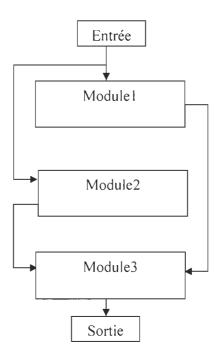

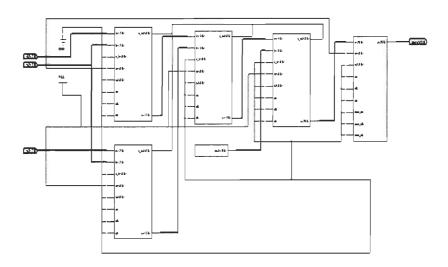

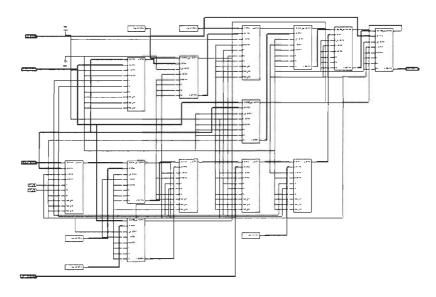

- Figure 4.1 : Modèle architectural de l'algorithme SPTDA

- Figure 4.2: Interconnexion des modules

- Figure 4.3: Interface Xilinx niveau 1 de l'algorithme sous Simulink

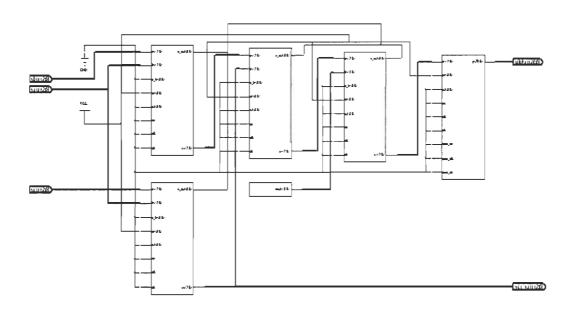

- Figure 4.4 : Module 1 et module 2 modélisés par les blocs de Xilinx ISE

- Figure 5.5: Modules 3 modélisé avec les blocs de Xilinx ISE

- **Figure 4.6** : Structure du module 1 de l'algorithme de détection sous XST

- **Figure 4.7**: Structure module 2 de l'algorithme de détection sous XST

- Figure 4.8: Structure du module 3 de l'algorithme.

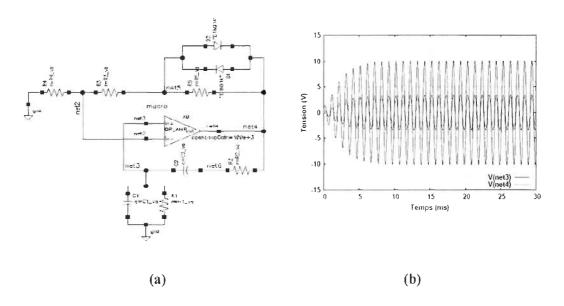

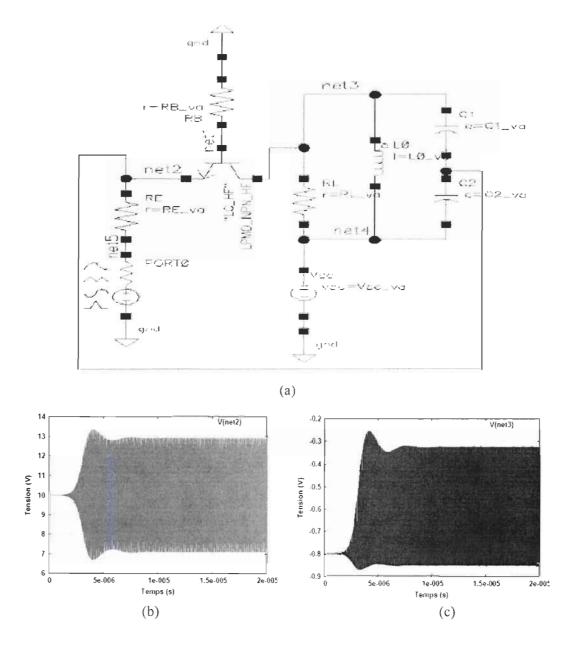

- **Figure 5.1** : Oscillateur basses fréquences à pont de WIEN : (a) schéma électrique pratique, (b) tensions d'entrée et de sortie.

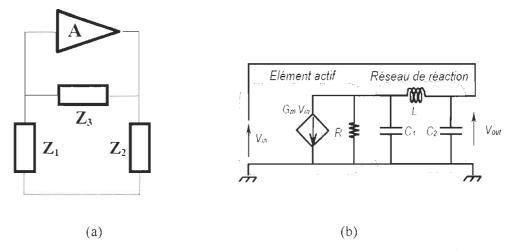

- **Figure 5.2** : Schéma de base d'un oscillateur LC : (a) schéma réduit, (b) schéma équivalent d'un oscillateur de type COLPITTS.

- **Figure 5.3**: Oscillateur COLPITTS RF: (a) schéma électrique, (b) forme d'onde de la tension de l'émetteur, (c) forme d'onde de la tension de collecteur.

- Figure 5.4 : Multivibrateur astable réalisé en technologie bipolaire.

- **Figure 5.5**: Forme du signal aux différents nœuds d'un multivibrateur astable réalisé en technologie bipolaire.

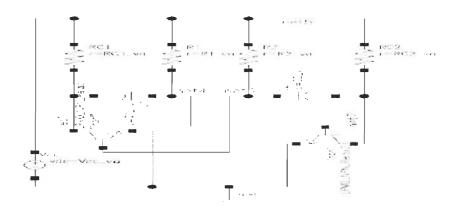

- Figure 5.6 : Schéma de base d'un multivibrateur astable réalisé en technologie NMOS.

- **Figure 5.7** : Forme du signal aux différents nœuds d'un multivibrateur astable réalisé en technologie NMOS.

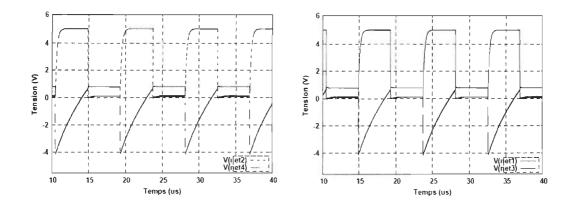

- Figure 5.8 : Schéma d'un oscillateur en anneaux réalisé par 5 inverseurs CMOS.

- **Figure 5.9**: Forme du signal aux différents nœuds d'un oscillateur en anneaux à base de 5 inverseurs CMOS.

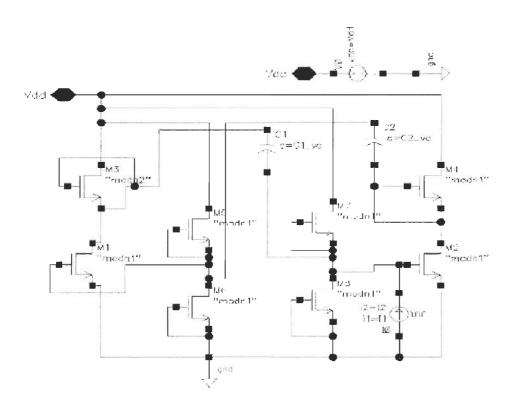

- Figure 5.10: Structure générale d'un oscillateur en anneau à base d'inverseurs MOS

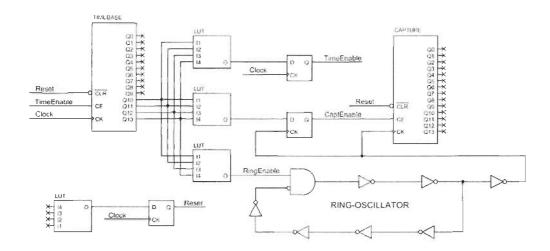

- Figure 5.11 : Schéma de capteur en oscillateurs en anneaux

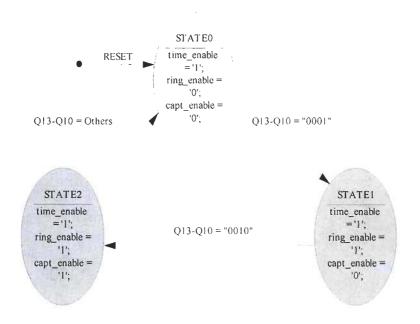

- Figure 5.12 : Machine d'état permettant la sélection des différents signaux activés

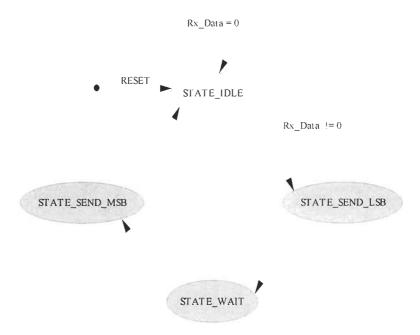

- **Figure 5.13**: Machine d'état permettant la lecture de la sortie du compteur de capture de la température

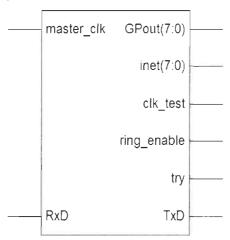

- Figure 5.14 : Structure haut niveau du capteur en oscillateurs en anneaux

- Figure 5.15: La structure du capteur avec Xilinx XST

- Figure 5.16: Placement du capteur sur la carte Xilinx

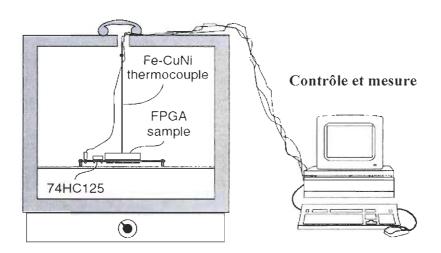

- **Figure 5.17**: Procédures de la calibration des capteurs avec le four VWR Sientific model 1310

- Figure 5.18 : La variation de la température en fonction de la fréquence normalisée

- Figure 5.19: Structure haut niveau du capteur en oscillateurs en anneaux

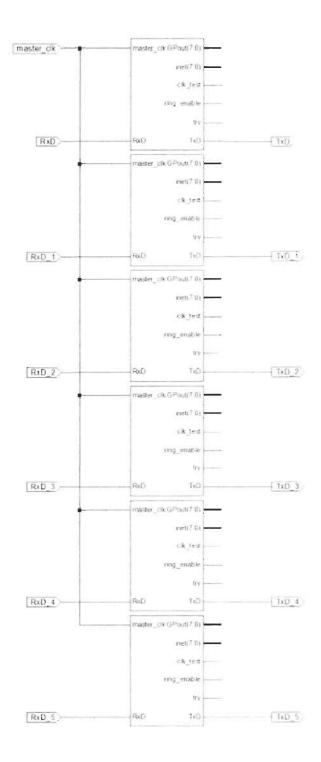

- Figure 5.20 : La structure du routage de six capteurs

- Figure 5.21: Placement des six capteurs sur la carte Xilinx

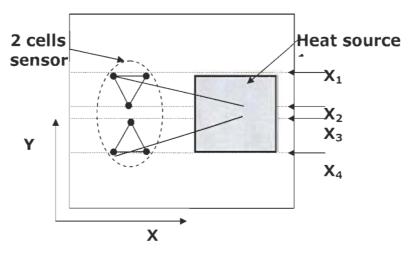

- **Figure 5.22 :** Positions physique des cellules avec l'emplacement des capteurs et la source de chaleur

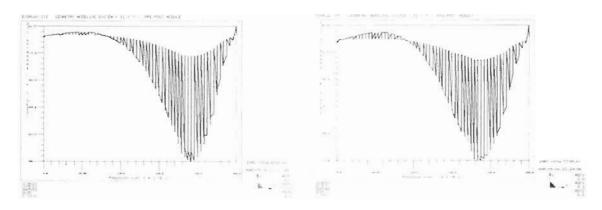

- **Figure 5.23**: (a)  $\sigma_{xx}$  les contraintes surfaciques au niveau de XI

- (b)  $\sigma_{xx}$  les contraintes surfaciques au niveau de X2

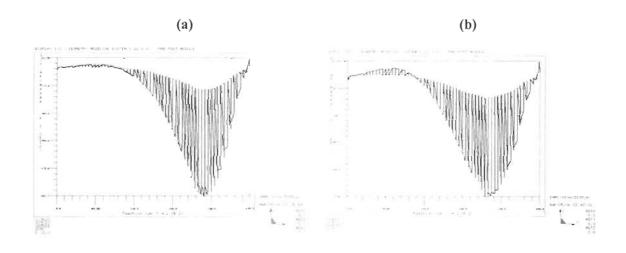

- (c)  $\sigma_{xx}$  les contraintes surfaciques au niveau de X3

- (d)  $\sigma_{xx}$  les contraintes surfaciques au niveau de X4

#### LISTE DES TABLEAUX

- **Tableau 2. 1** : Coefficients de transfert de chaleur typiques pour différents types de refroidissement par convection

- **Tableau 2.2**: Comparaison entre les différents paramètres avec l'analyse d'écoulement de fluide (Qfin) et le transfert de la chaleur (NISA)

- Tableau 3.1 : Propriétés des matériaux pour les simulations thermomécaniques

- Tableau 3.2: Résultat avec le model en éléments finis 3D

- **Tableau 3.3**: Résultat analytique avec la méthode GDS pour différentes sources de chaleur

- **Tableau 4.1**: Comparaison entre températures générées par FEM, SPTDA (float), SPTDA (fix)

#### LISTE DES SYMBOLES

ASIC Application Specific Integrated Circuit

WSI Wafer Scale Integration

VLSI Very Large Scale Integration

**GDS** Gradient Direction Sensor

DIP Dual In line Package

**SOP** Small Outline Package

LCC Leaded Ceramic chip Carrier

QFP Quad Flat Pack

**PGA** Pin Grid Array

**BGA** Ball Grid Array

**TAB** Tape Automated Bonding

LAIC Large Area Integrated Circuit

**SoC** System on a Chip

MOS Metal-Oxide Semiconductor

**FPGA** Field Programmable Gate Array

**CFD** Computational Fluid Dynamics

**HTA** Heat Transfer Analysis

**SPTDA** Surface Peaks Thermal Detector Algorithm

**DVS** Dynamic Voltage Scaling

MEMS Micro Electro Mechanical System

TCE Thermal Coefficient of Expansion

**FEM** Finite Element Method

CLB Configurable Logic Blocs

**DFD** Data Flow Diagram

**DSP** Digital Signal Processing

**DTM** Dynamic Thermal Management

**EDIF** Electronic Design Interchange Format

**FF** Flip Flops

HIL Hardware In the Loop

IOB Input Output Blocs

**ISE** Integrated Simulation Environment

ITRS International Technology Roadmap for Semiconductors

LUT Look Up Table

LIMA Laboratoire d'Ingénierie des Microsystèmes Avancés

MIMD Multiple Input Multiple Data

**NGD** Native Generic Database

PE Process Element

SLPS System Level Prototyping Station

SIMD Single Input Multiple Data

**SPTDA** Surface Peaks Thermal Detector Algorithm

VHDL Very Large Scale Integration Circuit Hardware Description Language

VLSI Very Large Scale Integration

XST Xilinx Synthesis Tool

IC Integrated Circuit

# Chapitre I Introduction générale

#### I.1 Évolution de la microélectronique

L'industrie des semi-conducteurs est une plaque tournante dans le domaine de la haute technologie. Pour les cinquante dernières années, les produits microélectronique ont envahi notre vie, avec la pénétration massive en santé, sécurité et identification, communications, éducation et pratiquement dans tous les aspects de la vie humaine.

Le domaine des semi-conducteurs a commencé en 1959, lorsque Jack S. Kilby (Texas Instruments) a présenté une demande de brevet sur des circuits électroniques miniaturisés. Son invention a démontré la faisabilité de réaliser des résistances et des condensateurs fondés sur la technologie des semi-conducteurs avec des transistors sur un seul et même substrat. Avec cela, le circuit intégré (CI) est né et Jack S. Kilby a reçu le prix Nobel en physique en 2000, conjointement avec Zhores I. Alferov and Herbert Kroemer. Quelques années plus tard, en 1965, l'ingénieur Gordon E. Moore prédit la croissance exponentielle dans l'industrie des semi-conducteurs [Moore, 1965]. Au fil des années, la complexité de cette croissance est devenue connue sous le nom de Loi Moore. Toutefois, cette loi n'est pas une loi physique, mais plutôt un argument économique. Aujourd'hui, la loi de Moore est le principal mécanisme derrière les grandes tendances technologiques de l'industrie microélectronique : la miniaturisation et l'intégration des fonctions. De point de vue affaires, la miniaturisation et l'intégration des fonctions signifient plus de fonctionnalités, une petite taille, moins de ressources d'emploi, une plus grande mobilité à faible prix.

La technologie moderne des semi-conducteurs se caractérise par des exigences telles que la rapidité, l'optimisation des coûts de fabrication à une qualité élevée. Mais avec l'augmentation de la densité d'interconnexion et l'augmentation de la puissance dissipée, la densité de puissance dissipée augmente. La combinaison de la miniaturisation

et l'intégration des fonctions dérivent la technologie microélectronique à un niveau inconnu de la complexité, caractérisée par la miniaturisation continue vers la nanoéchelle, hétérogène et multifonctionnelle, multidisciplinaire, multiéchelles, multitechnologie, multiprocessus, multi-matérialise/interface multidommages et multimode de défaillance. Comme conséquences, nous ne sommes jamais confrontés à une augmentation de telle complexité de la conception, augmentation des chances des échecs, augmentation du fossé entre la technologie et les connaissances fondamentales du développement et des difficultés accrues d'avoir une bonne qualité, robustesse et fiabilité. Si l'industrie va diminuer rapidement la taille de la technologie pour une production élevée au cours des 15 prochaines années, alors nous devons faire face aux défis de concevoir des produits suffisamment fiables aujourd'hui.

#### I.2 Évolution de la mise en boîtier

Depuis la mise au point des premiers boîtiers d'encapsulation de transistors, boîtier cylindrique à 3 broches, de nombreuses familles différentes de boîtiers ainsi que leurs variantes ont été développées comme support de circuits de plus en plus complexes. Ces familles sont répertoriées par l'acronyme de leur définition anglaise :

- DIP pour Dual In line Package, boîtier à l'origine en céramique, ayant ses broches reportées par brasure de chaque côté.

- SOP pour Small Outline Package, boîtier développé à l'origine par Philips pour des applications d'horlogerie, c'est un boîtier DIP plastique optimisé en termes d'encombrement.

- LCC pour Leaded Ceramic chip Carrier, Boîtier développé pour les besoins de la défense U.S., initialement prévu Leadless, mais qui s'est avéré plus facile d'assemblage en surface dans sa version avec broches. Les sorties sont alors situées à la périphérie du boîtier et les puces peuvent être montées « cavity up » ou bien « cavity down » afin d'optimiser les performances thermiques de l'ensemble puce boîtier.

- QFP pour Quad Flat Pack, boîtiers proches dans leur conception et dans leur réalisation des boîtiers LCC, développés par les Japonais pour

répondre aux besoins d'augmentation du nombre de broches des circuits intégrés, en version céramique puis en version plastique. Les broches situées à la périphérie des boîtiers sont courbées vers l'extérieur (gull wing).

- PGA pour Pin Grid Array, boîtiers dans lesquels les broches sont disposées en réseau sur toute la surface du boîtier, les conducteurs étant répartis sur plusieurs couches de céramique, ce qui permet d'atteindre toutes entrées sorties des circuits. Solution coûteuse, mais répondant bien aux besoins de nombre de sorties des circuits ASIC et des processeurs.

- BGA pour Ball Grid Array, Boîtiers identiques aux précédents, mais possédant des sorties sous forme de boules permettant un montage en surface.

- TAB pour Tape Automated Bonding, ce n'est pas un boîtier proprement parlé, mais plutôt une technique de câblage automatique des puces que l'on veut reporter sur un support (PCB, MCM, autre), la protection de la puce s'effectue généralement par enrobage plastique.

#### 1.3 Problématique et objectif

Notre thèse introduit une nouvelle orientation pour la caractérisation de la dynamique thermique dans les microsystèmes VLSI (*Very Large Scale Integration*) à haute densité. De plus, il reconnaît l'importance grandissante des microsystèmes sur puce qui constituent la convergence de plusieurs dispositifs, systèmes et technologies de la microéchelle et bientôt à la nanoéchelle comme solution d'intégration du futur pour l'industrie de la microélectronique. Cependant, l'ampleur de l'intégration des microsystèmes électroniques complets sur seule puce et l'augmentation de la vitesse d'opération amènent des problèmes insurmontables de contrainte thermomécanique. Si ces aspects ne sont pas traités convenablement cela représentera une menace sérieuse pour le design des microsystèmes du futur. Plus spécifiquement, ces aspects deviennent critiques lors du design des circuits VLSI, LAIC (*Large Area Integrated Circuit*), WSI et les SoC (*System on a Chip*) concernant la sécurité et la garantie de la fiabilité de ces nouveaux dispositifs microélectroniques.

Pour ces derniers, l'idée principale de cette thèse couvre les aspects de la caractérisation de la contrainte thermomécanique. Bien que les microsystèmes sur puce couvrent différents domaines physiques, la caractérisation de la dynamique thermique représente le cœur des préoccupations actuelles et futures de l'industrie de la microélectronique. De plus, ces domaines partagent différents aspects dont la température est la principale préoccupation commune et qui pose des défis énormes pour les méthodologies de design des microsystèmes. Dans cette thèse, la méthodologie adoptée pour la caractérisation de la dynamique thermique des microsystèmes sur puce sera basée sur la généralisation des concepts de couplage électrothermique. Cette méthodologie a donné des résultats très encourageants pour la caractérisation des aspects de la dynamique thermique dans les circuits VLSI. Ces concepts seront alors généralisés aux microsystèmes pour créer une nouvelle méthode de caractérisation de la dynamique thermique dans les microsystèmes électroniques à haute densité dans une perspective de développement d'une unité de contrôle intégrée de la contrainte thermomécanique.

L'évolution de l'industrie des circuits intégrés (CI) durant la dernière décennie a été tellement rapide qu'il est possible d'intégrer actuellement des systèmes complexes sur une seule puce SoC. Cette évolution vers des niveaux d'intégration de plus en plus élevés est motivée par les besoins de systèmes de plus en plus performants, et par conséquent produisant d'énormes densités de puissance. Cependant, cela a créé des nouveaux problèmes qui sont reliés à la contrainte thermomécanique (*Thermo-Mecanical Stress*) formée de la combinaison de la contrainte mécanique résiduelle (*Static Stress*) causée par le processus d'encapsulation et de la contrainte thermique (*Thermal-Stress*) causée par la densité de puissance dissipée [1-7].

Le sujet de cette thèse répond aux exigences croissantes des applications en microélectronique nécessitant une densité de puissance élevée et une différence de gradient de la température causée par l'implémentation de différent système sur la même puce. De plus, il s'oriente vers la modélisation, la réalisation et le test d'un capteur *in situ* intelligent à haute performance. Ce dernier sera basé sur l'implémentation d'une

configuration en réseau de cellules (capteurs thermiques) et d'une unité de contrôle intégrée de la contrainte thermomécanique.

Par sa nature, notre problématique exige l'utilisation d'une grande variété de disciplines telles que les systèmes de mesures, le couplage électro-thermo-mécanique et l'implémentation en microélectronique. Le développement d'un système de capteur *in situ* intelligent a pour objectif principal d'aider le concepteur à pousser les limites d'opération des nouveaux microsystèmes VLSI en intégrant le contrôle de la distribution de la contrainte thermomécanique. La performance de ce dernier dépend vigoureusement de la qualité individuelle des composantes qui le constituent et des différentes sources de bruit et leurs interactions. Le développement de tel capteur nécessite l'étude et la maîtrise de différentes étapes technologiques compatibles issues de la microélectronique. De plus, la connaissance et la modélisation des propriétés électro-thermo-mécaniques au niveau de silicium et le comportement des couches en déformation sont nécessaires. Cette connaissance se heurte au fait qu'il n'existe pas encore de techniques de caractérisation standard des matériaux utilisés au niveau de la puce.

La caractérisation de la dynamique thermique et le contrôle de la contrainte thermomécanique deviendront embarrassants s'ils ne sont pas implantés sur la puce. L'idée d'implémenter un algorithme sur puce devient la solution qui garantit leurs bons fonctionnements. On retrouve dans la littérature des approches qui proposent d'utiliser un réseau de cellules de transistors MOS (*Metal-Oxide Semiconductor*) exploitant le phénomène de la piézorésistivité (variation de la résistance du canal face à la contrainte) [4, 11]. Ces approches se limitent à prédire la contrainte statique après le processus de mise en boîtier [9, 10]. D'autres approches utilisent des capteurs piézorésistifs pour prédire la distribution de la contrainte thermomécanique en statique [6, 8,11]. Cependant, l'intégration sur la puce de ces approches nécessite une large proportion du circuit leur soit dédiée pour une prédiction acceptable. Ceci n'est pas approprié pour les microsystèmes VLSI à haute densité d'intégration et restent applicables pour des cas de calibration des nouveaux types de boîtiers électroniques [6,8].

Dans le cadre de cette thèse, nous visons de développer et de réaliser une nouvelle méthode de caractérisation de la dynamique thermique et du contrôle de la contrainte thermomécanique dans les microsystèmes VLSI à haute densité. La méthode proposée sera utilisée pour les microsystème rapides en tenant compte d'une plus large gamme de densité de puissance et une large différence de gradient de la température causée par l'implémentation de différents systèmes sur la même puce, tout en maintenant en opération un niveau de contrainte acceptable pour le CI à développer, ce qui représente une nouvelle approche pour les microsystèmes VLSI.

Le but essentiel de la méthode développée est de fournir aux concepteurs un moyen adéquat pour agir à temps et durant les premiers pas de la conception et cela pour contrôler la contrainte thermomécanique sans détériorer les caractéristiques du système en fonctionnement. Nous présenterons dans cette thèse les techniques utilisées pour qu'un système de capteur *in situ* intelligent performant réalise un meilleur compromis entre ces différents aspects, souvent interreliés, en particulier :

- Caractérisation de la dynamique thermique;

- Développement d'un algorithme de détection des pics thermiques;

- Analyse et établissement d'une configuration d'un réseau de cellules;

- Contrôle de la contrainte thermomécanique;

- Validation du système sur un FPGA;

- Validation expérimentale du modèle de simulation par éléments finis du comportement thermomécanique d'un circuit intégré.

#### I.4 Contribution

Le but de cette thèse consiste à résoudre les problèmes cités précédemment. Nous proposons une nouvelle orientation pour la caractérisation de la dynamique thermique dans les microsystèmes VLSI à haute densité. C'est une nouvelle méthode de contrôle de la contrainte thermomécanique basée sur un réseau de capteurs avec compensation thermique permettant le bon fonctionnement des microsystèmes VLSI. L'idée d'utiliser

un réseau de capteurs pour caractériser la contrainte est devenue un atout central pour cette problématique ayant comme résultat une promesse d'un contrôle assuré.

#### I.5 Méthodologie

#### I.5.1 Caractérisation de la dynamique thermique

Il s'agit dans cette première étape de procéder à une caractérisation complète de la dynamique thermique dans un circuit-test VLSI avec un boîtier de type BGA (*Ball Grid Array*) qui tiendra compte d'une seule source de chaleur [12-16]. La caractérisation est basée sur deux techniques numériques soit le CFD (*Computational Fluid Dynamics*) et l'autre HTA (*Heat Transfer Analysis*) [15]. La technique de CFD qui tient déjà compte de la force du mécanisme d'écoulement de chaleur spécifique au boîtier électronique et des propriétés physiques s'articulera avec l'aspect temporel et spatial de la HTA pour traiter les conditions aux limites et la distribution de la température en régime dynamique. Ainsi, la distribution de la température sur la surface de la puce servira pour la prédiction de la contrainte thermomécanique localisée aux emplacements des capteurs. C'est ainsi que notre approche sera guidée pour la caractérisation de la dynamique thermique représentant l'état de la contrainte thermomécanique.

#### 1.5.2 Développement d'un algorithme de détection des pics thermiques

Nous avons procédé à l'étude des techniques de détection de pics en analysant leur efficacité à prédire correctement la dynamique thermique. Ainsi, nous avons appliqué la méthode GDS (*Gradient Direction Sensor*) pour la détection des pics thermiques dans les microsystèmes VLSI [12]. Cette technique a été utilisée pour le développement de notre algorithme. Parmi les facteurs nécessitant une attention particulière lors de son développement, nous pouvons citer le nombre de capteurs, leur proximité, leur distribution spatiale et leurs interconnexions en réseau. L'application de la méthode GDS sera à la base du développement de l'algorithme de détection que nous avons développé dans la deuxième étape.

#### 1.5.3 Analyse et établissement d'une configuration d'un réseau de cellules

La troisième étape traitera de la conception et de la configuration en réseau d'un certain nombre de capteurs pour prédire la dynamique thermique représentant l'état de la contrainte thermomécanique. Le choix de l'emplacement sera fait de façon à répondre aux exigences de l'algorithme de détection du pic thermique et à la configuration du réseau. Dans cette étape les résultats de prédictions thermiques des différents scénarios seront étudiés et analysés en termes de nombre de cellules, précision, espace requis sur la puce et limite de fréquence d'application.

#### 1.5.4 L'algorithme de détection et de localisation des pics thermiques.

Le prototypage rapide et la tendance à la programmation des modèles qui tient compte de la concurrence des processus élémentaires, sont aujourd'hui de plus en plus utilises compte tenu de leur efficacité en termes du temps développement et du temps de mise en marché.

La conception et l'implantation en technologie d'intégration à très grande échelle (VLSI – Very Large Scale Integration) d'un algorithme de détection et de localisation des pics thermiques SPTDA (*Surface Peaks Thermal Detector Algorithm*) sera développé. L'algorithme mis en œuvre sera formulé de façon à faciliter le développement d'architecture en vue de leur implantation en VLSI. Cette architecture sera modélisée en langage de haut niveau, simulée afin d'évaluer sa performance et implantée sur un FPGA.

La proposition d'une architecture parallèle nous permettra d'avoir un très bon débit afin de répondre aux besoins des calculs excessifs de la gestion de la dynamique thermique en temps réel tout en diminuant les opérations des consignes d'horloge (*Clock Gating*) et l'échelonnement dynamique de la tension DVS (*Dynamic Voltage Scaling*) généralement utilisés dans des cas similaires pour optimiser la performance générale ainsi que la durée de vie du système.

Nous avons supposé que les fonctions thermiques étudiées ont une caractéristique linéaire, ce qui n'est pas toujours le cas, car dans la pratique une linéarisation autour d'un point avec un calibrage est nécessaire.

Cette unité développée peut prendre des entrées directement des capteurs suivant une certaine constante. Les détecteurs peuvent être implantés sous forme de 6 oscillateurs en anneau et placer soigneusement sur le même FPGA. Des compteurs connectés aux oscillateurs fournissent les entrées à l'algorithme. Étant donné que la position ponctuelle des capteurs et les dimensions du puce sont connues, on peut alors établir une vérification matérielle de l'algorithme avec une grande précision.

#### I.5.5 Validation sur un FPGA

Pour valider et corroborer les résultats de la caractérisation, nous nous attarderons à la construction d'un prototype du circuit-test sur FPGA. Essentiellement, la variation de la fréquence de sortie d'un réseau d'oscillateurs en anneau RO (Ring Oscillator) face à la chaleur et les contraintes mécaniques (thermomechanical stress) sera utilisée pour caractériser la distribution surfacique de contrainte au niveau d'une puce VLSI. Dans cette optique, un capteur thermomécanique sera élaboré pour jauger le niveau des contraintes dans un circuit FPGA.

Ainsi, une cellule de capteur thermique sera synthétisée et configurée par la suite en réseau pour jauger le niveau des contraintes sur la grandeur du prototype du circuit VLSI-test. Nous avons étudié les modes de circuits proposés dans la littérature pour les mesures de la contrainte thermomécanique pour choisir le plus approprié pour notre implémentation. D'un autre côté, une caractérisation complète passe par les mesures de la température en régime dynamique. Ainsi, pour s'assurer d'un bon fonctionnement, l'information sur l'état de la distribution de contrainte sur la puce pourrait servir au contrôle général des activités par une gestion des activités des modules dans le cas d'un microsystème VLSI à haute densité.

Dans cette optique, un capteur thermomécanique synthétisé pour jauger le niveau des contraintes dans un circuit FPGA. Un système de contrôle intelligent a pour objectif principal d'aider le concepteur à augmenter le seuil de fonctionnement des microsystèmes VLSI à haute densité. D'une façon pratique, le réseau de capteurs nous permet de valider expérimentalement nos résultats de caractérisation de la dynamique thermique pour prédire le comportement thermomécanique d'un circuit intégré en opération.

# Chapitre II Modélisation thermique

#### Introduction

Depuis de nombreuses années, les techniques de simulation connaissent un développement considérable. Les mises au point expérimentales, longues et coûteuses, sont progressivement remplacées par des études dans lesquelles les outils de simulation prennent une place de plus en plus importante. Les impératifs industriels de rapidité et de limitation des coûts sont pour l'essentiel responsables de cette évolution. Dans ces conditions, le développement d'outils permettant la modélisation et l'optimisation des composants utilisés en microélectronique constitue un enjeu important. Cette remarque s'applique également aux composants de refroidissement qui représentent une part importante, en termes de volume, de poids et de prix des équipements [19].

Tous les domaines du Génie Electrique, à des degrés divers sont concernés par les problèmes thermiques. Les machines électriques, moteurs et alternateurs, compte tenu des puissances mises en jeu et des échauffements dus aux pertes ont été les premiers dispositifs étudiés d'un point de vue thermique. Depuis de nombreuses années, des études similaires portent sur les composants de microélectronique, et en particulier les composants semi-conducteurs. Certains travaux plus spécifiques concernent l'électronique haute température pour des applications comme la recherche pétrolifère par exemple. D'une façon générale, tous les composants sont concernés. Les premiers travaux relatifs aux phénomènes thermiques utilisés en microélectronique sont assez anciens et peu nombreux [18]. Depuis quelques années, avec le développement des outils de simulation, les besoins en modélisation se sont fortement accrus. On assiste à une augmentation très significative des travaux dans ce domaine.

Pour être utilisables dans un contexte industriel, les outils de simulation doivent répondre à certains critères. Ils permettent des économies de temps de mise au point qui intéressent les concepteurs en microélectronique. Simplicité, faible nombre de paramètres, mise en oeuvre aisée et rapidité constituent les principales qualités d'outils industriels. La modélisation de la dynamique thermique utilisée comporte deux aspects différents :

- La conception de modèles s'insérant dans des logiciels de CAO en microélectronique, intéresse plus particulièrement le concepteur. Dans ce cas chaque composant, chaque sous-ensemble doit être modélisé avec le même degré d'approximation. L'outil de simulation permet d'analyser le fonctionnement de circuit intégré, de fournir le comportement thermique, les contraintes thermomécaniques sur chaque composant en régime permanent comme en régime transitoire. Il peut également fournir les températures de fonctionnement, car elle constitue un paramètre essentiel pour le choix du composant. Cela justifie la nécessité de développer des modèles thermiques compatibles avec l'ensemble des outils de simulation [19]. Ainsi, la simplicité du modèle, les temps de calcul et le nombre de paramètres nécessaires à l'identification du modèle constituent les critères de choix incontournables.

- L'aide à la modélisation thermomécanique représente le deuxième aspect de notre travail. Dans ce cas, la température demeure généralement la grandeur déterminante.

Les circuits intégrés modernes à haute vitesse consomment une quantité d'énergie électrique appréciable qui se transforme en chaleur. L'augmentation de l'intégration des fonctions conduit à produire des circuits de petits taille et nombre élevés des interconnexions. Avec des tailles très petites et des circuits plus denses, la quantité de chaleur produite sur les circuits CMOS à haute commutation peut être très importante. À titre d'exemple, le dernier haut de gamme des dispositifs FPGA de Xilinx insère de multiples processeurs, plusieurs émetteurs de gigabit, des impédances contrôlées numériquement et des I/O capables de supporter différents courants élevés en vigueur. Une attention particulière doit être accordée pour répondre aux besoins de chaleur élevée de ces dispositifs. La nécessité de gérer la chaleur produite dans un dispositif moderne de la logique CMOS ne concerne pas uniquement les FPGA. Il s'agit de l'industrie de

microsystème en général. Plus spécifiquement, ces aspects deviennent critiques lors du design des circuits VLSI, LAIC (Large Area Integrated Circuit), ASIC (Application-Specific Integrated Circuit), MEMS (Micro Electro Mechanical System), WSI (Wafer Scale Integration) et les SoC (System on a Chip) concernant la qualité et la garantie de la fiabilité de ces nouveaux dispositifs microélectroniques. C'est là que réside le défi de prévoir les besoins en matière de gestion thermique.

Il n'existe pas un moyen sûr de mesure réelle pour la prévision de la dissipation de puissance exacte dans les circuits intégrés. Plusieurs logiciels de l'estimation d'énergie ont été développés pour aider l'utilisateur final de prédire la consommation d'énergie. Les outils peuvent être utiles dans un premier temps. Comme la plupart des outils, les prévisions de sortie dépendent du travail mis en évidence. Donc pour chaque circuit développé il y a un boîtier typique pour l'utilisation et la gestion thermique fonctionne bien à l'intérieur, sans aucune source externe pour la gestion de la chaleur. Mais, avec de plus en plus de l'augmentation de niveau d'intégration des besoins des clients, il nous faut des circuits au-delà des circuits intégrés typiques. C'est pour ces cas que la nécessité de gérer la chaleur avec des moyens intelligents devient essentielle.

#### II.1 Problématique thermique

Au cours du développement et la conception des circuits intégrés, l'aspect thermique est crucial pour leur bon fonctionnement. Le problème du surchauffe de la jonction demeure un obstacle majeur devant les performances les plus recherchées des systèmes électroniques soit : l'augmentation de la vitesse d'opération et la miniaturisation des composants. Dans les deux cas, cela se traduit par une augmentation de la température des composants électroniques causée respectivement par l'accumulation d'un résidu thermique d'un cycle à l'autre et l'augmentation de la densité de puissance dissipée. La chaleur est une conséquence inévitable de chaque dispositif électronique, elle doit être réduite au minimum. La problématique thermique est généralement mentionnée comme la gestion thermique, elle n'est pas bien maîtrisée par la plupart des ingénieurs, à part le praticien régulier. Cette section fournit une description des approches diverses aux questions de la gestion thermique dans les boîtiers électroniques lors de la conception des

circuits intégrés au niveau de silicium. L'accent sera mis sur les principes de base et les outils disponibles pour résoudre la majorité des problèmes thermiques.

#### II.1.1 Effets de la température sur le fonctionnement du circuit intégré (CI)

L'augmentation de la température d'un dispositif actif change typiquement ses paramètres électriques comme le gain, les fuites et la compensation. Ces variations des paramètres avec la température sont bien documentées et incorporées dans la plupart des simulateurs de circuits. La plupart des concepteurs de circuits sont conscients que le courant de fuite dans les dispositifs actifs (diode, transistor MOS) double approximativement chaque augmentation de 10 °C. La réduction de la température réduit ainsi l'effet des courants de fuite. Si la température d'un dispositif actif augmente trop, il excédera les spécifications du fabricant et altérera le fonctionnement normal du circuit intégré.

Le changement de la température des dispositifs passifs change typiquement leurs valeurs. Par exemple, les résistances de film ont des coefficients de température qui s'étendent de la gamme de plusieurs parties par million par degré °C de différence jusqu'aux plusieurs centaines. En pratique on ne désire pas typiquement ces changements de paramètres électriques. Si l'augmentation de la température est assez haute, le dispositif actif ou passif étant chauffé peut de manière permanente se dégrader, même se briser totalement ou se déformer d'une manière plastique. Donc, une bonne conception thermique doit réduire au minimum n'importe quelles augmentations de température et surtout le gradient thermique local. En tant que concepteur on ne peut pas avoir le contrôle de changements de l'environnement du circuit intégré, mais nous avons le contrôle de l'auto chauffage spatial du dispositif (distribution de la densité de puissance dissipée)

#### II.1.2 Effets de température sur la structure physique

Avec peu d'exceptions, les métaux s'étendent quand leur température augmente et se contracte quand ils sont refroidis. Le coefficient d'expansion thermique (TCE) est un paramètre très critique pour la conception de boîtier électronique. Des contraintes

thermiques se produisent quand un matériau prend de l'expansion ou de la contraction. Comme exemple, dans le cas d'un radiateur de cuivre soudé à un substrat de céramique métallisé, la céramique a un TCE de 6.4ppm/°C, tandis que le cuivre a un TCE de 16.8ppm/°C. Ainsi, pendant un cycle de température dans lequel il y a un certain nombre de périodes d'échauffement et de refroidissement, le cuivre s'étend et se contracte à un taux plus rapide que la céramique induisant une contrainte thermique qui augmente, et se multiplie d'un cycle de température à l'autre. De cette façon, le joint entre eux se soude, et il provoque une déformation dans la céramique [17]. D'un autre côté, réduire ou éliminer les contraintes thermiques exige le choix des métaux bien spécifique avec une gestion du trafique poussée pour minimiser les gradients thermiques causés par l'auto-chauffage au niveau du silicium.

La conception d'un microsystème fiable et performant nécessite le recours à une étude thermomécanique aux particularités géométriques et structurelles au niveau de la jonction. En effet durant l'exécution des étapes de conception thermique, nous devons nous assurer d'évacuer la chaleur résiduelle. Dans le cas d'un processeur, la température de l'ensemble doit rester en dessous de la température maximale d'opération qui en fait représente une barrière difficile à respecter dans le cas des microsystèmes à haute densité de puissance (Figure 2.1). Ainsi, notre approche pour la caractérisation de la dynamique thermique permet d'aider le concepteur dès le premier pas de la conception afin de passer le test thermique et les exigences de la fonderie.

Figure 2.1 : Organigramme général pour la conception d'un système électrothermique

#### II.1.3 Méthodologie pour la caractérisation de la dynamique thermique

#### II.1.3.1 Puissance dissipée

La caractérisation de la dynamique thermique débute par la connaissance de la quantité de puissance qui sera dissipée dans chacun des parties d'un circuit intégré

(Figure 2.2). Cependant, on doit connaître le pire ou le cas critique représentant des conditions d'utilisation du circuit, sa taille maximale et son poids et la disponibilité ou non de liquides de refroidissement.

Figure 2.2 : Méthodologie pour la caractérisation de la dynamique thermique

L'intégration élevée de circuits dans un boîtier électronique plus petit abouti à une densité de chaleur plus élevée, qui met la gestion thermique à une haute priorité dans le processus de conception des circuits intégrés afin de maintenir la performance et la stabilité des systèmes VLSI. Cependant, l'augmentation de taux d'horloge augmente la puissance dissipée dans les semi-conducteurs et par conséquent, la commutation qui évolue à un taux linéaire proportionnel à la fréquence :

$$P = CV^2f/2$$

$O\dot{u}$ :  $C = Capacit\'{e}$  d'entr\'{e} en farads

V= Signal d'oscillation de la tension crête à crête en volts

#### f= Fréquence de commutation en hertz

Si les valeurs de la capacité d'entrée et l'oscillation de signal étaient restées les mêmes tandis que la fréquence d'horloge a augmenté, la quantité de la puissance dissipée aurait grandi dans un taux exponentiel et serait ingérable. Heureusement, le concepteur a la possibilité d'aider à réduire la capacité d'entrée pour chaque nouvelle génération de semi-conducteurs. De plus, les oscillations de tension, qui sont directement liées aux tensions d'alimentation de la logique, ont subi une réduction drastique de cinq à un volts[17].

#### II.1.3.2 Types de consommations statiques et dynamiques

La consommation dynamique étant liée aux paramètres tension d'alimentation, fréquence de fonctionnement et capacité commutée, ce sont ces paramètres qu'il va falloir réduire principalement de manière architecturale : abaissement local de la tension d'alimentation, conditionnement des horloges pour n'activer que la partie nécessaire d'un circuit et réduction des capacités en utilisant des transistors de taille juste nécessaire pour la vitesse requise. Les différents types de consommations sont :

#### • Consommation liée à la charge et à la décharge d'une capacité

La consommation dynamique dans la technologie CMOS apparaît à chaque commutation d'au moins une des entrées d'une porte.

#### • Consommation liée au courant de court-circuit

Lors de la commutation d'une porte CMOS, il arrive un moment où les transistors des réseaux PMOS et NMOS sont passant en même temps ce qui crée un courant de court-circuit entre l'alimentation et la masse.

#### • Sources de la consommation statique

Jusqu'à présent, la puissance consommée liée aux courants de fuite a été négligée dans les études globales de puissance puisqu'elle était quantitativement faible visà-vis des autres sources de consommation. Avec l'apparition conjointe des nouvelles technologies submicroniques, et des dispositifs embarqués, alimentés sur batteries, les courants de fuite deviennent une source de préoccupations majeures. Il s'agit d'un nouveau défi, et ce particulièrement pour la conception des mémoires. Les courants de fuite deviennent critiques quand le circuit est suppose être en mode repos ou bien lorsque son activité dynamique est faible. En revanche, si toutes les parties d'un circuit sont constamment activées, la consommation statique reste faible devant la consommation dynamique.

Les courants de fuite peuvent se décomposer en cinq catégories :

- Le courant de polarisation de diode en inverse (Reverse biased pn junction current).

- Le courant sous le seuil (Subthreshold current).

- Courant de Drain induit par la Grille (Gate Induced Drain Leakage (GIDL)).

- Le courant de perçage (Drain source punch through current).

- Le courant à travers la grille (Gate tunelling current).

#### II.1.3.3 Analyse de la dissipation thermique

Depuis quelques années, l'analyse de la dissipation thermique en microélectronique connaît un regain d'intérêt en raison même de la densité toujours croissante des composants sur des substrats dont les dimensions connaissent une progression inverse. Les problèmes de dissipation thermique revêtent une grande importance dans le boîtier des circuits intégrés. Ne pas les considérer et ne pas les maîtriser revient à fabriquer des modules n'offrant pas toutes les garanties de fonctionnement et de fiabilité. Une mauvaise ou insuffisante évacuation de la chaleur peut avoir des effets néfastes sur le bon fonctionnement du circuit. La chaleur est le résultat d'une puissance électrique développée par les éléments actifs et passifs. Les effets thermiques peuvent se manifester de manières différentes, par une dérive en température des composants entraînant des variations importantes des performances électriques, ou par une rupture de soudure reliant le composant au substrat en raison des variations dimensionnelles différentes pour chacun d'eux, entraînant soit une défaillance partielle, soit une défaillance totale.

La chaleur dégagée par les composants atteint le boîtier par l'intermédiaire du substrat. Ce transfert de chaleur se fait presque entièrement par conduction. Il se fait par convection et rayonnement du boîtier vers l'air ambiant. Il importe par conséquent au concepteur du système électronique de bien cerner les modes de transfert thermique et de prévoir, après étude, le moyen d'évacuer cette chaleur en dehors du boîtier, pour ne pas détériorer les composants. Ce transfert thermique peut s'effectuer de trois façons :

- La conduction thermique demeure la plus importante dans notre domaine. Elle est principalement caractérisée par une dissipation de chaleur à l'intérieur d'un ou de plusieurs solides en contact. Ce phénomène fait intervenir la conductivité thermique des matériaux.

- La convection thermique est très semblable à la conduction, mais concerne le transfert thermique d'un fluide. Les convections naturelle et forcée sont à distinguer. Elles sont souvent rencontrées dans les boîtiers de circuits intégrés qui dissipent de grandes quantités de chaleur.

- Le rayonnement thermique, comme son nom l'indique, correspond à un transfert de chaleur sous forme d'onde électromagnétique (dans l'infrarouge). Tout corps, de température non nulle (0°K), rayonne de l'énergie. Cependant, dans le domaine de la mise en boîtier, ce type de dissipation thermique est souvent négligé, à juste titre, devant la conduction et la convection thermiques.

#### II.1.3.4 Choix de radiateur et de boîtier électronique

Dans le cas pratique des circuits WSI deux types de refroidissement par circulation d'air sont envisageables, la convection naturelle et la convection forcée. Dans des applications où la dissipation de puissance est faible, le refroidissement par convection naturelle est plus économique et facile pour mettre en œuvre. Cependant, à cause du niveau élevé de puissance dissipée dans le WSI, le refroidissement par convection forcée est la façon la plus efficace pour évacuer cette quantité de chaleur hors

du boîtier. Le tableau 1 nous montre les différents coefficients de convection associés pour différents types de refroidissement (Tableau 2.1).

| Type de refroidissement     | Coefficient de transfert de    | Commentaires          |

|-----------------------------|--------------------------------|-----------------------|

|                             | chaleur h (W/m <sup>2</sup> K) |                       |

| Convection naturelle (air)  | 3-12                           | Typiquement 5         |

| Convection forcée (air)     | 10-100                         | Typiquement 50        |

| Convection nat (liquide)    | 200-2000                       | Fluorocarbures        |

| Convection forcée (liquide) | 2000-7000                      | Eau Mélangé de glycol |

| Bouillonnement (F)          | 2000-6000                      | Fluorocarbures        |

| Bouillonnement (Eau)        | 50000                          | Eau                   |

Tableau 2.1 : Coefficients de transfert de chaleur typiques pour différents types de refroidissement par convection

Dans le cas des circuits WSI il est évidemment hors de question d'utiliser les quatre derniers types de refroidissement puisqu'ils sont basés sur un réfrigérant liquide. Alors que le premier type est insuffisant 5 W/m² K pour évacuer convenablement l'énergie accumulée. Cependant, la convection forcée peut répondre convenablement en la combinant avec une configuration de radiateur à haut rendement et un boîtier de résistance totale jonction-boîtier moins de 0.01 °C/W. Cette valeur de résistance thermique assure un refroidissement convenable du circuit WSI en régime permanent.

Pour savoir si un boîtier est adapté thermiquement à un circuit intégré, il est nécessaire d'estimer sa capacité à évacuer la chaleur vers l'extérieur. Dans ce but, l'étude thermique d'un système électronique peut se décomposer en trois parties :

- Le boîtier de chaque source thermique est modélisé thermiquement. Un groupe de résistances thermiques est alors associé à chaque boîtier.

- Chaque modèle thermique de boîtier est étudié sur son support (ex: PCB).

(L'environnement extérieur de ce sous-système doit être identique à celui du système entier)

• Une synthèse des résultats précédents est effectuée, afin d'étudier le comportement thermique du système entier.

Le but d'une telle étude est de prévoir les risques de surchauffe dans un système de composants. Chaque source de chaleur (c'est-à-dire la puce) dissipe une puissance calorifique supposée connue. La température de celle-ci peut être estimée lorsque son environnement (boîtier, support, milieu extérieur) est modélisé thermiquement. Si cette estimation n'appartient pas au domaine de températures, à l'intérieur duquel le circuit intégré fonctionne correctement, le boîtier étudié est alors considéré comme inadapté du point de vue thermique.

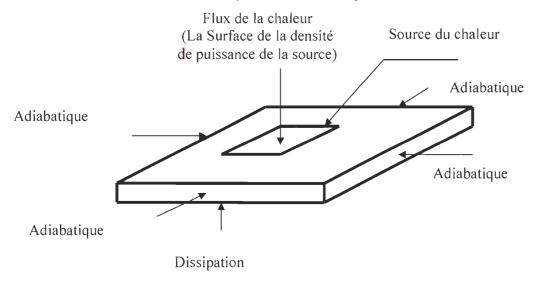

## II.1.3.5 Conditions aux limites thermiques

L'un des problèmes majeurs qui se pose lorsqu'on veut faire une étude thermique au niveau du boîtier d'un CI est de déterminer les conditions aux limites. Ainsi, à cet effet une nouvelle approche a été établie pour la détermination d'un coefficient de convection équivalent h<sub>équi</sub> au niveau de la jonction; afin d'éviter la spécification de la température au-dessous de boîtier, qui introduit un court-circuit thermique entre la surface et la jonction. Cependant, pour pallier à ce problème, il faut mailler toute la structure jusqu'au radiateur. Cela nécessite l'utilisation d'un modèle qui peut atteindre des dizaines de millions d'éléments rendant l'analyse complexe voir même impossible.

Cette technique est connue et appliquée pour résoudre des problèmes inverses de transfert de chaleur (*Inverse Heat Transfer Problem*) durant l'application de la méthode des mesures indirectes. Dans ce cas l'approche utilisée est basée sur l'analyse par la méthode des éléments finis (FEM) combinant l'écoulement de fluide et le transfert de chaleur (Figure 2.3). Elle se résume on deux étapes : la première utilise par exemple le logiciel QFin (analyse thermique par écoulement de fluide ou CFD *Compulation fluid dynamics*) pour déterminer la température de la jonction avec un coefficient de convection forcée connu. La deuxième utilise par exemple le logiciel NISA (analyse numérique pour le transfert de la chaleur) pour obtenir la même température avec le nouveau coefficient de convection forcée équivalent. Cette technique est connue et

appliquée pour résoudre des problèmes inverses en transfert de chaleur (*Inverse Heat Problem*) et pour appliquer la méthode des mesures indirectes.

Figure 2.3: Approche pour déterminer le coefficient de convection forcée équivalente

## II.2 Analyse de transfert de la chaleur

## II.2.1 Flux d'énergie thermique

En état d'équilibre, aucun stockage d'énergie de sorte que, pour un volume élémentaire  $\Delta V$  Figure 1.4 (la chaleur entrée définie en tant que positif).

Figure 1.4: Élément de volume ( $\Delta V$ )

$$\left(-k_{x}\Delta y \Delta z \frac{\partial T}{\partial x}\right)_{3} - \left(-k_{x}\Delta y \Delta z \frac{\partial T}{\partial x}\right)_{4}$$

$$\left[\left(-k_{x}\Delta x \Delta z \frac{\partial T}{\partial y}\right)_{1} - \left(-k_{y}\Delta x \Delta z \frac{\partial T}{\partial y}\right)_{2}\right]$$

$$+ \left[\left(-k_{x}\Delta x \Delta y \frac{\partial T}{\partial z}\right)_{5} - \left(-k_{x}\Delta y \Delta z \frac{\partial T}{\partial z}\right)_{6}\right] + Q_{x}\Delta x \Delta y \Delta z = 0$$

(2.1)

Le flux immergeant les deux côtés de l'équation par le volume  $\Delta V = \Delta x \Delta y \Delta z$  est donné par

$$\left[ \left( \frac{1}{\Delta x} \right) \left( k_X \frac{\partial T}{\partial x} \right) \right]_{3}^{4} + \left[ \left( \frac{1}{\Delta Y} \right) \left( k_Y \frac{\partial T}{\partial Y} \right) \right]_{1}^{2} + \left[ \left( \frac{1}{\Delta Z} \right) \left( k_Z \frac{\partial T}{\partial Z} \right) \right]_{5}^{6} = -Q_{V} \quad (2.2)$$

Pour des éléments de volume très petit, prenant la limite  $\Delta V \rightarrow 0$  à la direction de x. Et en répétant ce processus dans les directions de y et de z, le résultat on trois dimensions (3D) de la conduction de la chaleur pour le régime permanent est :

$$\frac{1}{\Delta x} \left( k_x \frac{\partial T}{\partial x} \right) + \frac{1}{\Delta y} \left( k_y \frac{\partial T}{\partial y} \right) + \frac{1}{\Delta z} \left( k_z \frac{\partial T}{\partial z} \right) = Q \tag{2.3}$$

Ainsi, l'équation peut s'écrire :

$$dT = -\left(\frac{Q_{i}}{kA}\right) dx \qquad (2.4)$$

En intégrant l'équation devient :

$$\int_{t_{1}}^{T_{2}} dT = -Q_{k} \int_{x_{1}}^{x_{2}} \frac{dx}{kA_{k}}$$

(2.5)

En supposant que la conductivité thermique k ne change pas au-dessus de la longueur  $L=x_2-x_1$  l'équation se réduit à :

$$\Delta T = T_2 - T_1 = Q_k \frac{L}{kA}$$

(2.6)

Où  $\Delta T = T_2 - T_1$  est la différence de température à travers la longueur L.

#### II.2.2 Conduction de chaleur

En analysant le problème de transfert de la chaleur dans le CI, il est très important de considérer l'effet des sources de chaleur à la proximité. Nous considérons un corps trois dimensionnel (jonction), du volume V et lié par une superficie S. Nous supposons que le matériel obéit à la loi de Fourier de la conduction de la chaleur [14].

$$q = -K.\frac{\partial T}{\partial x} \tag{2.7}$$

Ou sous la forme matricielle :

$$\begin{cases}

q_{x} \\

q_{y} \\

q_{z}

\end{cases} = - \begin{cases}

k_{xx} & k_{xy} & k_{xz} \\

k_{yx} & k_{yy} & k_{yz} \\

k_{zx} & k_{zy} & k_{zz}

\end{cases} \begin{cases}

\frac{\partial \Gamma}{\partial x} \\

\frac{\partial \Gamma}{\partial y} \\

\frac{\partial \Gamma}{\partial y}

\end{cases} (2.8)$$

Où  $q_i$  est le taux du flux de chaleur conduit par unité de surface dans la direction i, K et la conductivité thermique des matériaux, et  $\partial I / \partial x$  et le vecteur gradient dans les cordonnées cartésiennes. Dans la principale direction des matériaux l'équation (2.7) se réduit sur la forme diagonale;

$$\begin{cases}

q_1 \\ q_2 \\ q_3

\end{cases} = -\begin{cases}

k_{11} & 0 & 0 \\ 0 & k_{22} & 0 \\ 0 & 0 & k_{33}

\end{cases} \begin{cases}

\frac{\partial T}{\partial x_1} \\

\frac{\partial T}{\partial x_2} \\

\frac{\partial T}{\partial x_3}

\end{cases} (2.9)$$

Ou simplement,

$$q_n = -k_n \cdot \frac{\partial T}{\partial q} \tag{2.10}$$

Ainsi, la matrice de la conductivité thermique de l'équation (2.8) peut être obtenue à partir de l'équation (2.9) par une simple transformation de tenseur de deuxième degré :

$$Kxyz = T^T K_{1,2,3} T$$

(2.11)

Où T est le tenseur de transformation du deuxième degré entre les deux axes simultanément x, y, z et 1, 2,3. Il est à noter que le principe de la thermodynamique irréversible permet au tenseur K d'être symétrique. Si les matériaux sont homogènes et isotropes (le cas d'un CI), alors :

$$k_{xy} = k_{yz} = k_{zx}$$

, et  $k_{xx} = k_{yy} = k_{zz} = k$  (2.12)

Assumant que la conductivité thermique k ne change pas au-dessus de la longueur  $L=x_2-x_1$ , l'équation est réduite à :

$$\Delta T = T_2 - T_1 = Q_k \frac{L}{kA} \quad (2.13)$$

Où  $\Delta T = T_2 - T_1$  est la différence de la température à travers la longueur L et A est la coupe normale moyenne d'écoulement de chaleur en  $m^2$ .

La résistance thermique peut être définie par :

$$R = \frac{L}{kA}$$

,  $R = \frac{\Delta T}{Q_k}$

$\Delta T$ : c'est la différence de la température entre la source de chaleur et le radiateur Figure 2.5

$$\Delta T = T_{\text{source de chaleur}} - T_{\text{Radiateur}}$$

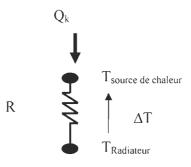

Figure 2.5 : Modèle thermique statique I-D

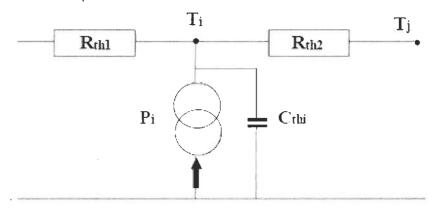

## II.3 Circuit thermique équivalent.

Les paramètres qui caractérisent le circuit intégré au niveau thermique sont très nombreux. On peut les classer en deux catégories qui sont les paramètres statiques et les paramètres dynamiques. Ils nous renseignent sur le comportement du dispositif lorsque celui-ci est ou non en fonctionnement. Certains de ces paramètres sont indiqués dans les spécifications des constructeurs, d'autres ne le sont pas.

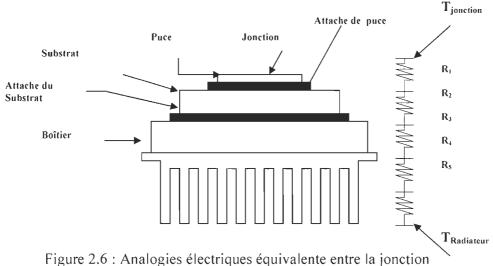

Avant de parler de la dissipation de la chaleur au niveau d'un circuit intégré, il est nécessaire de définir tous les facteurs et les paramètres thermiques. Ces paramètres vont nous permettre de faire une étude détaillée sur l'évacuation de flux de chaleur sur toute la structure du circuit (Figure 2.6).

La résistance thermique équivalente R<sub>Equiv</sub> est :

$$R_{Equiv} = R_1 + R_2 + R_3 + R_4 + R_5$$

Où:

R1 : résistance thermique de la puce

R2 : résistance thermique de l'attache de la puce

R3: résistance thermique du substrat

R4 : résistance thermique de l'attache du substrat

R5 : résistance thermique du boîtier

T<sub>j</sub>: température de la jonction en <sup>0</sup>C

T<sub>Radiateur</sub>: température du radiateur.

Cette température est de l'ordre de <125 °C pour les applications typiques en microélectronique en générale, et pour les applications militaires elle est de l'ordre de 65 °C à 80 °C [14]. Dans certains cas, on utilise une matière au niveau du contacte entre le boîtier et le radiateur pour la dissipation de la chaleur sur toute la surface de circuit (*Thermal Pad Spreader*)[14].

D'un autre côté, le mauvais contrôle de la température au sein du processeur peut l'endommager ou il peut se produire une dégradation de ses performances, surtout sa durée de vie. De sorte que la puissance maximale indiquée par le constructeur doit être respectée à tout instant pendant le fonctionnement du dispositif. On sait qu'une élévation de température trop importante du matériau semi-conducteur peut détruire le réseau cristallin. Les calories développées à l'intérieur du cristal doivent être évacuées à l'extérieur par l'intermédiaire du boîtier et du radiateur [15]. Ainsi, la température maximale de jonction  $T_{jmax}$  est un paramètre qui Figure toujours dans les spécification ; elle ne doit jamais être atteinte par le dispositif en régime permanent. C'est seulement dans le cas d'une surcharge que l'on admet un dépassement de  $T_{jmax}$ . Habituellement, la température maximale de jonction  $T_{jmax}$  est limitée entre 100 et 150 °C, à cause de la contrainte thermique instantanée induite dans la jonction.

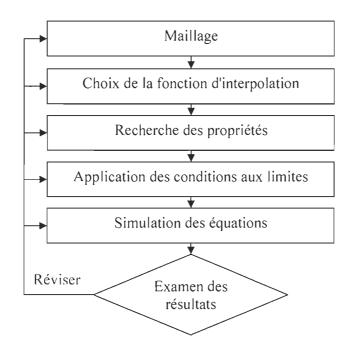

## II.4 Analyse de la dynamique thermique par FEM

La modélisation des phénomènes physiques est aujourd'hui très présente dans les métiers de l'Ingénieur. Celui-ci est en effet amené à utiliser de plus en plus couramment des méthodes de calcul numérique face à la complexité sans cesse croissante des problèmes qu'il rencontre. Par ailleurs, le développement des modèles et le progrès de l'informatique font qu'aujourd'hui la simulation numérique est plus réaliste. Ainsi, les outils numériques deviennent à notre portée et constituent un atout majeur. Le développement des méthodes de simulation touche actuellement un large éventail de disciplines scientifiques et de nombreux secteurs techniques ou technologiques.

La méthode des éléments finis est l'une des méthodes de simulation numérique les plus pratiquées de nos jours. Elle consiste à utiliser une approximation simple de la géométrie et des variables décrivant le phénomène physique tel que le déplacement, la vitesse, la pression, la température. Afin de ramener le problème continu comportant une infinité d'inconnues vers un système algébrique à un nombre fini de degrés de liberté. Elle fait appel aux trois domaines suivants :

- les sciences de l'ingénieur pour la formulation mathématique du problème physique.

- les méthodes numériques pour la construction du système algébrique à résoudre.

- les techniques informatiques pour l'exécution des calculs de simulation.

L'emploi de la méthode des éléments finis (FEM) s'est développé depuis une soixantaine d'années à travers l'analyse des structures via des assemblages de barres ou de poutres dont le comportement était dicté par les hypothèses de la résistance des matériaux. L'apparition de l'informatique et les besoins industriels ont provoqué un développement rapide de la méthode à travers une re-formulation à partir de considérations énergétiques d'une part, et la création d'éléments de haute précision géométrique et physique d'autre part. Dès 1960, la méthode des éléments finis est reconnue comme un outil général de résolution de problèmes physiques linéaires ou non-linéaires, stationnaires ou instationnaires non seulement dans le domaine des structures,

mais aussi dans d'autres domaines tels que la mécanique des sols, la mécanique des fluides, la thermique, l'électromagnétisme et bien d'autre domaine.

L'utilisation de cette méthode s'est donc répandue, au cours des dernières décennies, dans divers secteurs industriels tels que l'aéronautique, la construction navale, l'industrie automobile et dans des domaines liés, entre autres, à la mécanique des matériaux et des structures. Parmi les nombreux programmes généraux basés sur la FEM et disponibles pour l'utilisation industrielle citons, principalement dans les domaines de la mécanique des solides, NISA, ABAQUS, ANSYS, MARC, NASTRAN, SAMCEF, SYSTUS. Bien que ces logiciels soient initialement conçus pour des gros ordinateurs, ils ont été adaptés ces dernières années pour exploitation sur micro-ordinateurs au même titre que des programmes modulaires permettant la résolution de problèmes de taille moyenne tels que CADSAP, ACORD.

Par ailleurs, une nouvelle génération de codes s'est développée récemment. Il s'agit des codes d'éléments finis explicites destinés à la simulation des problèmes en dynamique rapide. Parmi les plus connus, citons ABAQUS EXPLICIT, PAM-CRASH, RADIOSS, LS-DYNA.